# ACS21MS

### Data Sheet

## July 1999 File Number 4757

# Radiation Hardened Dual 4-Input AND Gate

The Radiation Hardened ACS21MS is a Dual 4-Input AND Gate. For each gate, a HIGH level on all inputs results in a HIGH level on the Y output. A LOW level on any input results in a LOW level on the Y output. All inputs are buffered and the outputs are designed for balanced propagation delay and transition times.

The ACS21MS is fabricated on a CMOS Silicon on Sapphire (SOS) process, which provides an immunity to Single Event Latch-up and the capability of highly reliable performance in any radiation environment. These devices offer significant power reduction and faster performance when compared to ALSTTL types.

Specifications for Rad Hard QML devices are controlled by the Defense Supply Center in Columbus (DSCC). The SMD numbers listed below must be used when ordering.

Detailed Electrical Specifications for the ACS21MS are contained in SMD 5962-98629. A "hot-link" is provided on our homepage for downloading. www.intersil.com/spacedefense/newsafclasst.asp

### Features

- QML Qualified Per MIL-PRF-38535 Requirements

- 1.25 Micron Radiation Hardened SOS CMOS

- Radiation Environment

- Latch-Up Free Under Any Conditions

- SEU Immunity.....<1 x 10<sup>-10</sup> Errors/Bit/Day

- SEU LET Threshold .....>100MeV/(mg/cm<sup>2</sup>)

- Input Logic Levels. . . .  $V_{IL}$  = (0.3)(V\_{CC}),  $V_{IH}$  = (0.7)(V\_{CC})

- Output Current ......±12mA (Min)

- Quiescent Supply Current ......5.0µA (Max)

- Propagation Delay ......15ns (Max)

### Applications

- High Speed Control Circuits

- Sensor Monitoring

- Low Power Designs

### Ordering Information

| ORDERING NUMBER  | INTERNAL MARKETING<br>NUMBER | TEMP. RANGE ( <sup>O</sup> C) | PACKAGE        | DESIGNATOR |

|------------------|------------------------------|-------------------------------|----------------|------------|

| 5962F9862901VCC  | ACS21DMSR-03                 | -55 to 125                    | 14 Ld SBDIP    | CDIP2-T14  |

| ACS21D/SAMPLE-03 | ACS21D/SAMPLE-03             | 25                            | 14 Ld SBDIP    | CDIP2-T14  |

| 5962F9862901VXC  | ACS21KMSR-03                 | -55 to 125                    | 14 Ld Flatpack | CDFP3-F14  |

| ACS21K/SAMPLE-03 | ACS21K/SAMPLE-03             | 25                            | 14 Ld Flatpack | CDFP3-F14  |

| 5962F9862901V9A  | ACS21HMSR-03                 | 25                            | Die            | NA         |

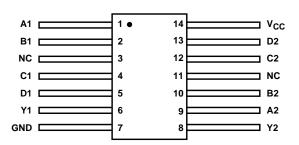

# Pinouts

| Г     | $\neg \neg \neg$ |                   |

|-------|------------------|-------------------|

| A1 1  | 1                | 4 V <sub>CC</sub> |

| B1 2  | 1                | 3 D2              |

| NC 3  | 1                | 2 C2              |

| C1 4  | -                | 11 NC             |

| D1 5  | 1                | 0 B2              |

| Y1 6  |                  | 9 A2              |

| GND 7 |                  | 8 Y2              |

| L     |                  |                   |

#### ACS21MS (FLATPACK) TOP VIEW

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. 1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999

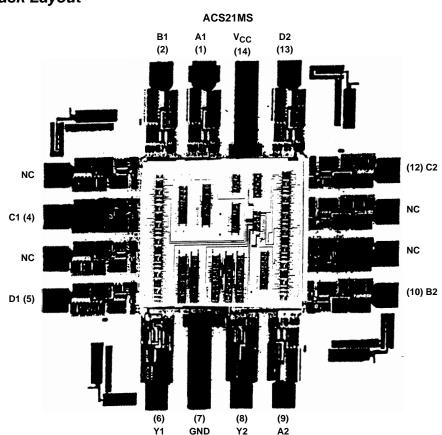

### **Die Characteristics**

#### DIE DIMENSIONS:

Size: 2390μm x 2390μm (94 mils x 94 mils) Thickness: 525μm ±25μm (20.6 mils ±1 mil) Bond Pad: 110μm x 110μm (4.3 x 4.3 mils)

#### **METALLIZATION: AI**

Metal 1 Thickness:  $0.7\mu m \pm 0.1\mu m$ Metal 2 Thickness:  $1.0\mu m \pm 0.1\mu m$

#### SUBSTRATE POTENTIAL

Unbiased Insulator

## Metallization Mask Layout

### **PASSIVATION:**

Type: Phosphorous Silicon Glass (PSG) Thickness:  $1.30\mu m \pm 0.15\mu m$

#### SPECIAL INSTRUCTIONS

Bond V<sub>CC</sub> First

#### ADDITIONAL INFORMATION:

Worst Case Current Density:  $<2.0 \times 10^5 \text{ A/cm}^2$ Transistor Count: 92

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site www.intersil.com

# Sales Office Headquarters

NORTH AMERICA Intersil Corporation P. O. Box 883, Mail Stop 53-204 Melbourne, FL 32902 TEL: (321) 724-7000 FAX: (321) 724-7240 EUROPE Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05 ASIA Intersil (Taiwan) Ltd. 7F-6, No. 101 Fu Hsing North Road Taipei, Taiwan Republic of China TEL: (886) 2 2716 9310 FAX: (886) 2 2715 3029

2