# VIPer20/SP/DIP VIPer20A/ASP/ADIP

# SMPS PRIMARY I.C.

| TYPE              | V <sub>DSS</sub> | In    | R <sub>DS(on)</sub> |

|-------------------|------------------|-------|---------------------|

| VIPer20/SP/DIP    | 620V             | 0.5 A | 16 Ω                |

| VIPer20A/ASP/ADIP | 700V             | 0.5 A | 18 Ω                |

- ADJUSTABLE SWITCHING FREQUENCY UP TO 200 kHz

- **CURRENT MODE CONTROL**

- SOFT START AND SHUT DOWN CONTROL

- AUTOMATIC BURST MODE OPERATION IN STAND-BY CONDITION ABLE TO MEET "BLUE ANGEL" NORM (<1W TOTAL POWER CONSUMPTION)

- INTERNALLY TRIMMED ZENER REFERENCE

- UNDERVOLTAGE LOCK-OUT WITH HYSTERESIS

- INTEGRATED START-UP SUPPLY

- AVALANCHE RUGGED

- OVERTEMPERATURE PROTECTION

- LOW STAND-BY CURRENT

- ADJUSTABLE CURRENT LIMITATION

#### **DESCRIPTION**

VIPer20/20A, made using VIPower M0 Technology, combines on the same silicon chip a state-of-the-art PWM circuit together with an optimized high voltage avalanche rugged Vertical Power MOSFET (620V or 700V / 0.5A).

Typical applications cover off line power supplies with a secondary power capability of 10W in wide range condition and 20W in single range or with doubler configuration. It is compatible from both primary or secondary regulation loop despite using around 50% less components when compared with a discrete solution. Burst mode operation is an additional feature of this device, offering the possibility to operate in stand-by mode without extra components.

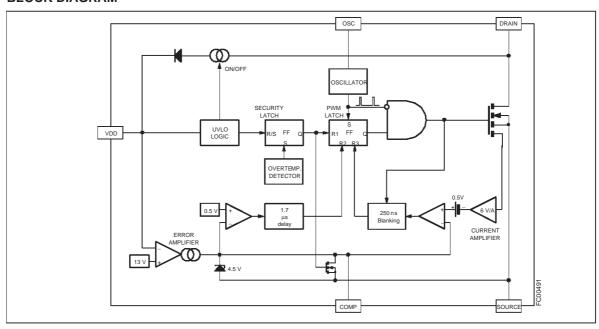

### **BLOCK DIAGRAM**

April 2002 1/25

#### **ABSOLUTE MAXIMUM RATING**

| Symbol             | Parameter                                                                            | Value                | Unit |

|--------------------|--------------------------------------------------------------------------------------|----------------------|------|

|                    | Continuous Drain-Source Voltage (T <sub>j</sub> =25 to 125°C)                        |                      | .,   |

| $V_{DS}$           | for VIPer20/SP/DIP                                                                   | -0.3 to 620          | V    |

|                    | for VIPer20A/ASP/ADIP                                                                | -0.3 to 700          | V    |

| I <sub>D</sub>     | Maximum Current                                                                      | Internally limited   | А    |

| V <sub>DD</sub>    | Supply Voltage                                                                       | 0 to 15              | V    |

| Vosc               | Voltage Range Input                                                                  | 0 to V <sub>DD</sub> | V    |

| V <sub>COMP</sub>  | Voltage Range Input                                                                  | 0 to 5               | V    |

| I <sub>COMP</sub>  | Maximum Continuous Current                                                           | ± 2                  | mA   |

| V <sub>esd</sub>   | Electrostatic Discharge (R =1.5kΩ; C=100pF)                                          | 4000                 | V    |

|                    | Avalanche Drain-Source Current, Repetitive or Not Repetitive                         |                      |      |

| I <sub>D(AR)</sub> | $(T_C=100^{\circ}C; \text{ Pulse width limited by } T_j \text{ max; } \delta < 1\%)$ | 0.5                  | Α    |

| D(AIX)             | for VIPer20/SP/DIP                                                                   | 0.4                  | A    |

|                    | for VIPer20A/ASP/ADIP                                                                |                      |      |

| P <sub>tot</sub>   | Power Dissipation at T <sub>c</sub> =25°C                                            | 57                   | W    |

| Tj                 | Junction Operating Temperature                                                       | Internally limited   | °C   |

| T <sub>stg</sub>   | Storage Temperature                                                                  | -65 to 150           | °C   |

#### THERMAL DATA

| Symbol                | Parameter                        |     | PENTAWATT | PowerSO-10 <sup>TM</sup> (*) | DIP-8  | Unit |

|-----------------------|----------------------------------|-----|-----------|------------------------------|--------|------|

| R <sub>thj-pin</sub>  | Thermal Resistance Junction-pin  | Max |           |                              | 20     | °C/W |

| R <sub>thj-case</sub> | Thermal Resistance Junction-case | Max | 2.0       | 2.0                          |        | °C/W |

| R <sub>thj-amb.</sub> | Thermal Resistance Ambient-case  | Max | 70        | 60                           | 35 (#) | °C/W |

<sup>(\*)</sup> When mounted using the minimum recommended pad size on FR-4 board. (#) On multylayer PCB.

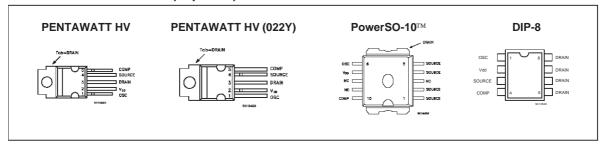

CONNECTION DIAGRAMS (Top View)

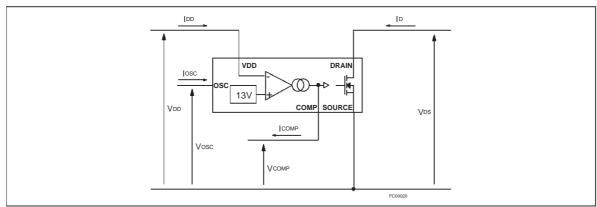

# **CURRENT AND VOLTAGE CONVENTIONS**

57

2/25

#### **ORDERING NUMBERS**

| PENTAWATT HV | PENTAWATT HV (022Y) | PowerSO-10™ | DIP-8       |

|--------------|---------------------|-------------|-------------|

| VIPer20      | VIPer20 (022Y)      | VIPer20SP   | VIPer20DIP  |

| VIPer20A     | VIPer20A (022Y)     | VIPer20ASP  | VIPer20ADIP |

#### PINS FUNCTIONAL DESCRIPTION

#### **DRAIN PIN:**

Integrated Power MOSFET drain pin. It provides internal bias current during start-up via an integrated high voltage current source which is switched off during normal operation. The device is able to handle an unclamped current during its normal operation, assuring self protection against voltage surges, PCB stray inductance, and allowing a snubberless operation for low output power.

#### **SOURCE Pin:**

Power MOSFET source pin. Primary side circuit common ground connection.

#### **VDD Pin:**

This pin provides two functions:

- It corresponds to the low voltage supply of the control part of the circuit. If  $V_{DD}$  goes below 8V, the start-up current source is activated and the output power MOSFET is switched off until the  $V_{DD}$  voltage reaches 11V. During this phase, the internal current consumption is reduced, the  $V_{DD}$  pin sources a current of about 2mA and the COMP pin is shorted to ground. After that, the current source is shut down, and the device tries to start up by switching again.

- This pin is also connected to the error amplifier, in order to allow primary as well as secondary regulation configurations. In case of primary regulation, an internal 13V trimmed reference voltage is used to maintain V<sub>DD</sub> at 13V. For secondary regulation, a voltage between 8.5V and 12.5V will be put on V<sub>DD</sub> pin by transformer design, in order to stick the output of the transconductance amplifier to the high state. The COMP pin behaves as a constant current

source, and can easily be connected to the output of an optocoupler. Note that any overvoltage due to regulation loop failure is still detected by the error amplifier through the  $V_{DD}$  voltage, which cannot overpass 13V. The output voltage will be somewhat higher than the nominal one, but still under control.

#### **COMP PIN:**

This pin provides two functions:

- It is the output of the error transconductance amplifier, and allows for the connection of a compensation network to provide the desired transfer function of the regulation loop. Its bandwidth can easily be adjusted to the needed value with usual components value. As stated above, secondary regulation configurations are also implemented through the COMP pin.

- When the COMP voltage goes below 0.5V, the shut-down of the circuit occurs, with a zero duty cycle for the power MOSFET. This feature can be used to switch off the converter, and is automatically activated by the regulation loop (whatever is the configuration) to provide a burst mode operation in case of negligible output power or open load condition.

#### OSC PIN:

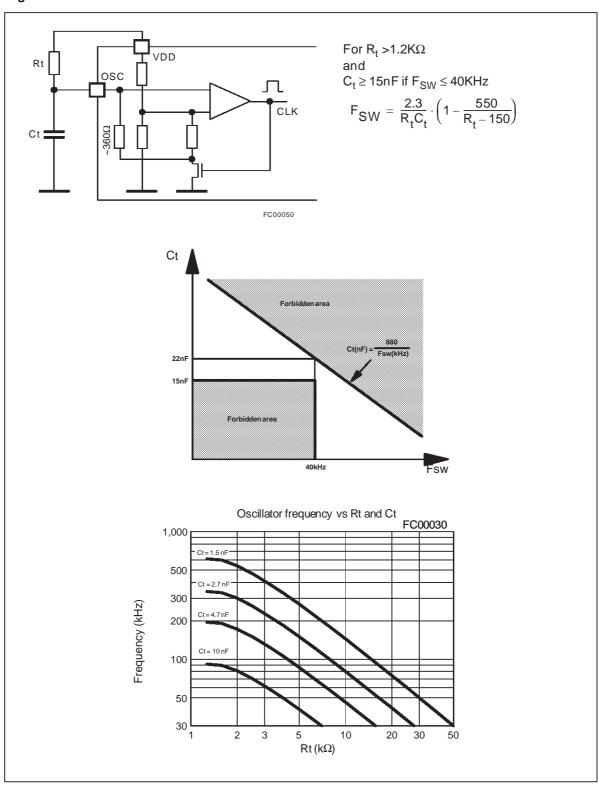

An  $R_t$ - $C_t$  network must be connected on that pin to define the switching frequency. Note that despite the connection of  $R_t$  to  $V_{DD}$ , no significant frequency change occurs for  $V_{DD}$  varying from 8V to 15V. It also provides a synchronization capability, when connected to an external frequency source.

3/25

### **AVALANCHE CHARACTERISTICS**

| Symbol             | Parameter                                                                                                                                  | Max Value    | Unit       |        |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|--------|

| I <sub>D(AR)</sub> | Avalanche Current, Repetitive or Not Repetitive (pulse widht limited by $T_j$ max; $\delta$ < 1%) for VIPer20/SP/DIP for VIPer20A/ASP/ADIP | (see fig.12) | 0.5<br>0.4 | A<br>A |

| E <sub>(ar)</sub>  | Single Pulse Avalanche Energy (starting $T_j = 25^{\circ}C$ , $I_D = I_{D(ar)}$ )                                                          | (see fig.12) | 10         | mJ     |

# $\textbf{ELECTRICAL CHARACTERISTICS} \ (T_j \!\!=\!\! 25^{\circ}C; \ V_{DD} \!\!=\!\! 13V, \ unless \ otherwise \ specified)$

POWER SECTION

| Symbol              | Parameter                            | Test Conditions                                                                                                                                                   | Min        | Тур          | Max                  | Unit        |

|---------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|----------------------|-------------|

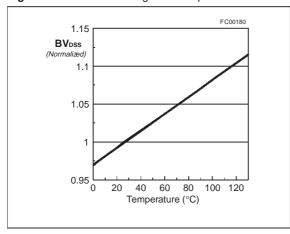

| BV <sub>DSS</sub>   | Drain-Source Voltage                 | I <sub>D</sub> =1mA; V <sub>COMP</sub> =0V<br>for <b>VIPer20/SP/DIP</b><br>for <b>VIPer20A/ASP/ADIP</b> (see fig.5)                                               | 620<br>700 |              |                      | V<br>V      |

| I <sub>DSS</sub>    | Off-State Drain Current              | $V_{COMP}$ =0V; $T_j$ =125°C<br>$V_{DS}$ =620V for <b>VIPer20/SP/DIP</b><br>$V_{DS}$ =700V for <b>VIPer20A/ASP/ADIP</b>                                           |            |              | 1.0<br>1.0           | mA<br>mA    |

| R <sub>DS(on)</sub> | Static Drain-Source<br>On Resistance | I <sub>D</sub> =0.4A<br>for VIPer20/SP/DIP<br>for VIPer20A/ASP/ADIP<br>I <sub>D</sub> =0.4A; T <sub>j</sub> =100°C<br>for VIPer20/SP/DIP<br>for VIPer20A/ASP/ADIP |            | 13.5<br>15.5 | 16<br>18<br>29<br>32 | Ω<br>Ω<br>Ω |

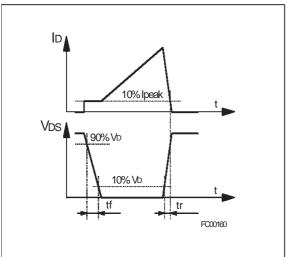

| t <sub>f</sub>      | Fall Time                            | I <sub>D</sub> =0.2A; V <sub>IN</sub> =300V (1)<br>(See fig. 3)                                                                                                   |            | 100          |                      | ns          |

| t <sub>r</sub>      | Rise Time                            | I <sub>D</sub> =.4A; V <sub>IN</sub> =300V (1)<br>(See fig. 3)                                                                                                    |            | 50           |                      | ns          |

| C <sub>oss</sub>    | Output Capacitance                   | V <sub>DS</sub> =25V                                                                                                                                              |            | 90           |                      | pF          |

<sup>(1)</sup> On Inductive Load, Clamped.

## SUPPLY SECTION

| Symbol              | Parameter                    | Test Conditions                                             | Min | Тур | Max | Unit |

|---------------------|------------------------------|-------------------------------------------------------------|-----|-----|-----|------|

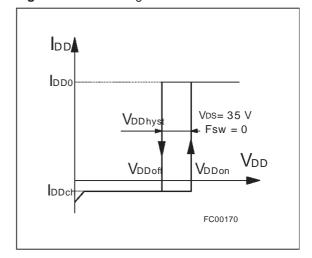

| I <sub>DDch</sub>   | Start-Up Charging<br>Current | $V_{DD}$ =5V; $V_{DS}$ =35V (see fig. 2 and fig. 15)        |     | -2  |     | mA   |

| I <sub>DD0</sub>    | Operating Supply Current     | V <sub>DD</sub> =12V; F <sub>SW</sub> =0kHz<br>(see fig. 2) |     | 12  | 16  | mA   |

| I <sub>DD1</sub>    | Operating Supply Current     | V <sub>DD</sub> =12V; F <sub>sw</sub> =100kHz               |     | 13  |     | mA   |

| I <sub>DD2</sub>    | Operating Supply Current     | V <sub>DD</sub> =12V; F <sub>sw</sub> =200kHz               |     | 14  |     | mA   |

| $V_{DDoff}$         | Undervoltage Shutdown        | (See fig. 2)                                                | 7.5 | 8   | 9   | V    |

| V <sub>DDon</sub>   | Undervoltage Reset           | (See fig. 2)                                                |     | 11  | 12  | V    |

| V <sub>DDhyst</sub> | Hysteresis Start-up          | (See fig. 2)                                                | 2.4 | 3   |     | V    |

<u> 577</u>

# VIPer20/SP/DIP - VIPer20A/ASP/ADIP

# **ELECTRICAL CHARACTERISTICS** (continued)

### **OSCILLATOR SECTION**

| Symbol             | Parameter                               | Test Conditions                                                                                                                                                                                                               | Min | Тур | Max | Unit |

|--------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| F <sub>SW</sub>    | Oscillator Frequency<br>Total Variation | $\begin{array}{l} R_t \!\!=\! 8.2 K\Omega; \ C_t \!\!=\! 2.4 \text{nF} \\ V_{DD} \!\!=\! 9 \text{ to } 15 \text{V}; \\ \text{with } R_t \!\!\!\pm\! 1\%; \ C_t \!\!\!\pm\! 5\% \\ \text{(see fig. 6 and fig. 9)} \end{array}$ | 90  | 100 | 110 | kHz  |

| V <sub>OSCih</sub> | Oscillator Peak Voltage                 |                                                                                                                                                                                                                               |     | 7.1 |     | V    |

| V <sub>OSCil</sub> | Oscillator Valley Voltage               |                                                                                                                                                                                                                               |     | 3.7 |     | V    |

# **ERROR AMPLIFIER SECTION**

| Symbol              | Parameter                         | Test Condition                                         | s                                    | Min  | Тур  | Max  | Unit |

|---------------------|-----------------------------------|--------------------------------------------------------|--------------------------------------|------|------|------|------|

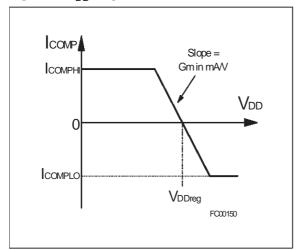

| V <sub>DDreg</sub>  | V <sub>DD</sub> Regulation Point  | I <sub>COMP</sub> =0mA                                 | (see fig. 1)                         | 12.6 | 13   | 13.4 | V    |

| $\Delta V_{DDreg}$  | Total Variation                   | T <sub>j</sub> =0 to 100°C                             |                                      |      | 2    |      | %    |

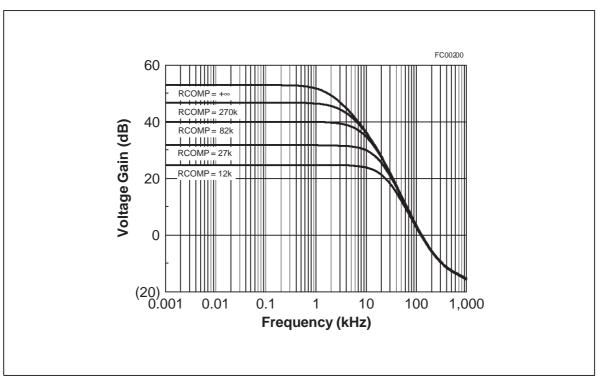

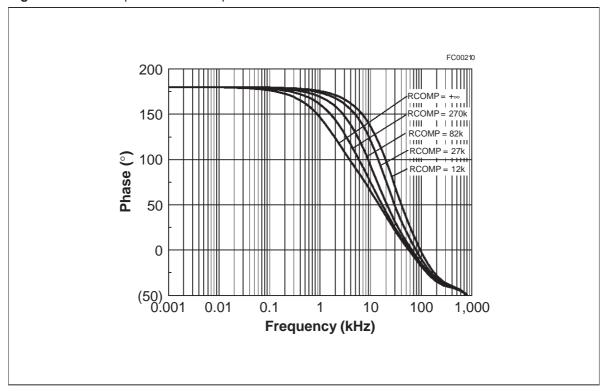

| G <sub>BW</sub>     | Unity Gain Bandwidth              | From Input =V <sub>DD</sub> to Output COMP pin is open | = V <sub>COMP</sub><br>(see fig. 10) |      | 150  |      | kHz  |

| A <sub>VOL</sub>    | Open Loop Voltage Gain            | COMP pin is open                                       | (see fig. 10)                        | 45   | 52   |      | dB   |

| G <sub>m</sub>      | DC Transconductance               | V <sub>COMP</sub> =2.5V                                | (see fig. 1)                         | 1.1  | 1.5  | 1.9  | mA/V |

| V <sub>COMPLO</sub> | Output Low Level                  | I <sub>COMP</sub> = -400μA; V <sub>DD</sub> =14V       |                                      |      | 0.2  |      | V    |

| V <sub>COMPHI</sub> | Output High Level                 | I <sub>COMP</sub> =400μA; V <sub>DD</sub> =12V         |                                      |      | 4.5  |      | V    |

| I <sub>COMPLO</sub> | Output Low Current<br>Capability  | V <sub>COMP</sub> =2.5V; V <sub>DD</sub> =14V          |                                      |      | -600 |      | μА   |

| I <sub>COMPHI</sub> | Output High Current<br>Capability | V <sub>COMP</sub> =2.5V; V <sub>DD</sub> =12V          |                                      |      | 600  |      | μА   |

### PWM COMPARATOR SECTION

| Symbol               | Parameter                                | Test Conditions                     | Min | Тур  | Max | Unit |

|----------------------|------------------------------------------|-------------------------------------|-----|------|-----|------|

| H <sub>ID</sub>      | ΔV <sub>COMP</sub> / ΔI <sub>DPEAK</sub> | V <sub>COMP</sub> =1 to 3 V         | 4.2 | 6    | 7.8 | V/A  |

| V <sub>COMPoff</sub> | V <sub>COMP</sub> Offset                 | I <sub>DPEAK</sub> =10mA            |     | 0.5  |     | V    |

| I <sub>Dpeak</sub>   | Peak Current Limitation                  | V <sub>DD</sub> =12V; COMP pin open | 0.5 | 0.67 | 0.9 | Α    |

| t <sub>d</sub>       | Current Sense Delay to Turn-Off          | I <sub>D</sub> =1A                  |     | 250  |     | ns   |

| t <sub>b</sub>       | Blanking Time                            |                                     |     | 250  | 360 | ns   |

| t <sub>on(min)</sub> | Minimum On Time                          |                                     |     | 350  |     | ns   |

### SHUTDOWN AND OVERTEMPERATURE SECTION

| Symbol              | Parameter                    | Test Conditions | Min | Тур | Max | Unit |

|---------------------|------------------------------|-----------------|-----|-----|-----|------|

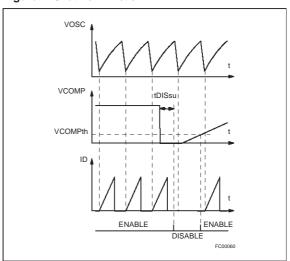

| V <sub>COMPth</sub> | Restart Threshold            | (see fig. 4)    |     | 0.5 |     | V    |

| t <sub>DISsu</sub>  | Disable Set Up Time          | (see fig. 4)    |     | 1.7 | 5   | μs   |

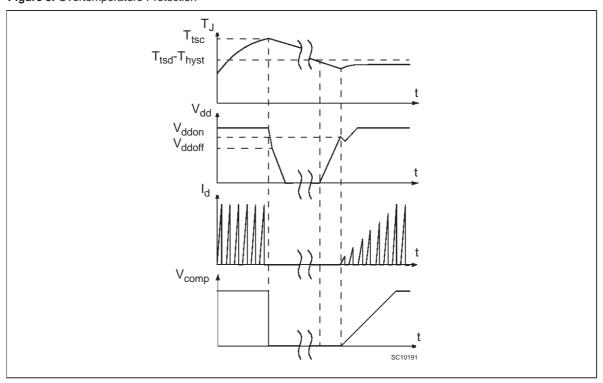

| T <sub>tsd</sub>    | Thermal Shutdown Temperature | (See fig. 8)    | 140 | 170 | 190 | °C   |

| T <sub>hyst</sub>   | Thermal Shutdown Hysteresis  | (See fig. 8)    |     | 40  |     | °C   |

57/

Figure 1: V<sub>DD</sub> Regulation Point

Figure 3: Transition Time

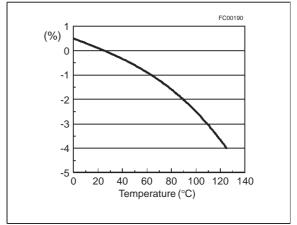

Figure 5: Breakdown Voltage Vs. Temperature

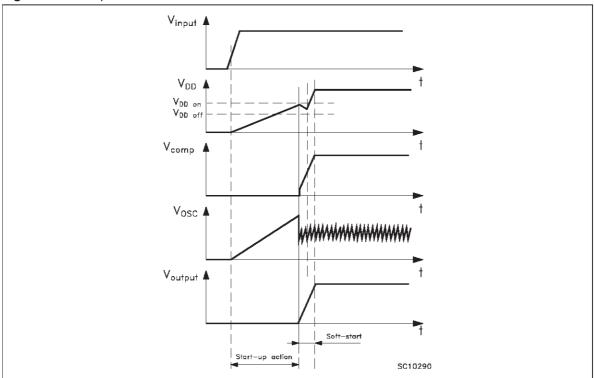

Figure 2: Undervoltage Lockout

Figure 4: Shut Down Action

Figure 6: Typical Frequency Variation

Figure 7: Start-Up Waveforms

Figure 8: Overtemperature Protection

Figure 9: Oscillator

Figure 10: Error Amplifier Frequency Response

Figure 11: Error Amplifier Phase Response

5/

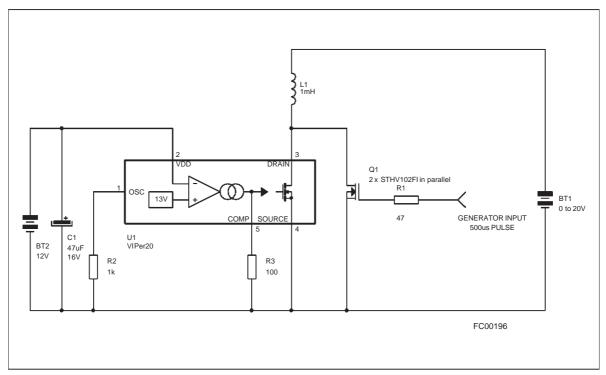

Figure 12: Avalanche Test Circuit

<u>57</u>

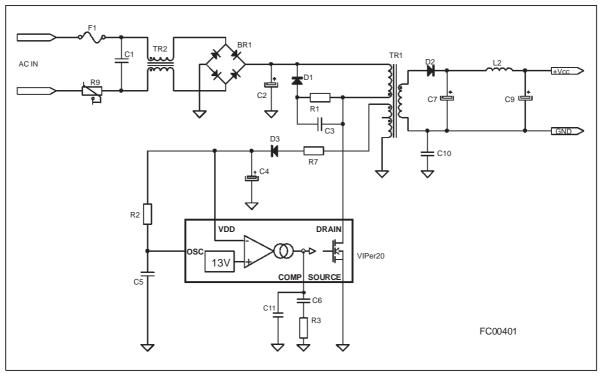

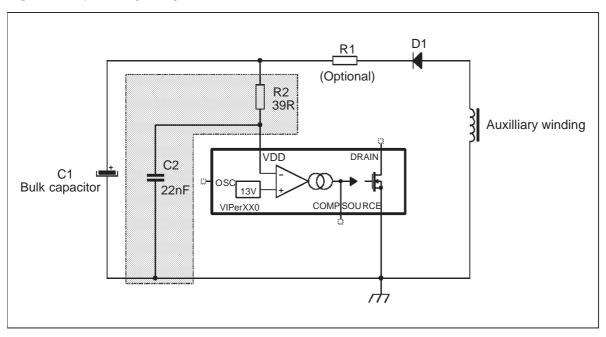

Figure 13: Off Line Power Supply With Auxiliary Supply Feedback

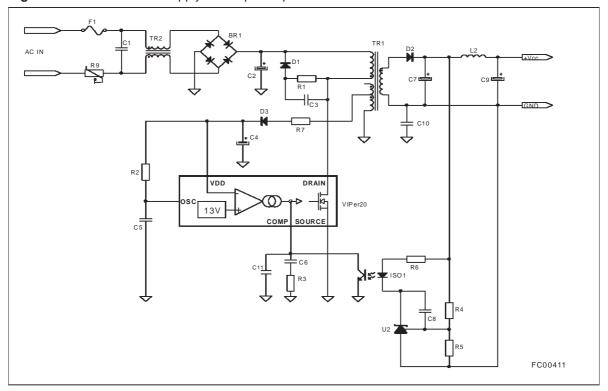

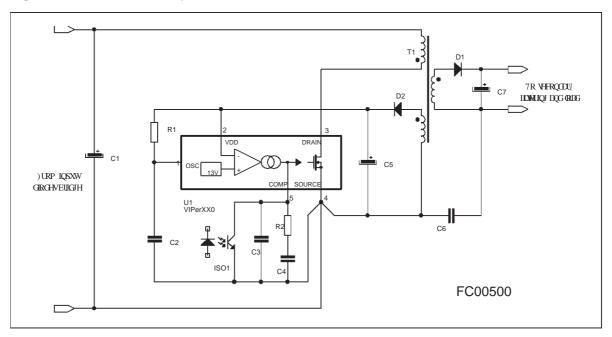

Figure 14: Off Line Power Supply With Optocoupler Feedback

#### **OPERATION DESCRIPTION:**

#### **CURRENT MODE TOPOLOGY**

The current mode control method, like the one integrated in the VIPer20/20A uses two control loops - an inner current control loop and an outer loop for voltage control. When the Power MOSFET output transistor is on, the inductor current (primary side of the transformer) is monitored with a SenseFET technique and converted into a voltage  $\rm V_S$  proportional to this current. When  $\rm V_S$  reaches  $\rm V_{COMP}$  (the amplified output voltage error) the power switch is switched off. Thus, the outer voltage control loop defines the level at which the inner loop regulates peak current through the power switch and the primary winding of the transformer.

Excellent D.C. open loop and dynamic line regulation is ensured due to the inherent input voltage feedforward characteristic of the current mode control. This results in an improved line regulation, instantaneous correction to line changes and better stability for the voltage regulation loop.

Current mode topology also ensures good limitation in the case of short circuit. During the first phase the output current increases slowly following the dynamic of the regulation loop. Then it reaches the maximum limitation current internally set and finally stops because the power supply on V<sub>DD</sub> is no longer correct. For specific applications the maximum peak current internally set can be overridden by limiting the voltage excursion externally on the COMP pin. An integrated blanking filter inhibits the PWM comparator output for a short time after the integrated Power MOSFET is switched on. This function prevents anomalous or premature termination of the switching pulse in the case of current spikes caused by primary side capacitance or secondary side rectifier reverse recovery time.

#### STAND-BY MODE

Stand-by operation in nearly open load condition automatically leads to a burst mode operation allowing voltage regulation on the secondary side. The transition from normal operation to burst mode operation happens for a power P<sub>STBY</sub> given by:

$$P_{STBY} = \frac{1}{2}L_P I^2 STBYF_{SW}$$

Where:

L<sub>P</sub> is the primary inductance of the transformer.

F<sub>SW</sub> is the normal switching frequency.

$I_{STBY}$  is the minimum controllable current, corresponding to the minimum on time that the device is able to provide in normal operation. This current can be computed as:

$$I_{STBY} = \frac{(t_b + t_d) V_{IN}}{L_P}$$

$t_b$  +  $t_d$  is the sum of the blanking time and of the propagation time of the internal current sense and comparator, and roughly represents the minimum on time of the device. Note that  $P_{STBY}$  may be affected by the efficiency of the converter at low load, and must include the power drawn on the primary auxiliary voltage.

As soon as the power goes below this limit, the auxiliary secondary voltage starts to increase above the 13V regulation level forcing the output voltage of the transconductance amplifier to low state ( $V_{COMP}$  <  $V_{COMPth}$ ). This situation leads to the shutdown mode where the power switch is maintained in the off state, resulting in missing cycles and zero duty cycle. As soon as  $V_{\mbox{\scriptsize DD}}$  gets back to the regulation level and the V<sub>COMPth</sub> threshold is reached, the device operates again. The above cycle repeats itself indefinitely, providing a burst mode of which the effective duty cycle is much lower than the minimum one when in normal operation. The equivalent switching frequency is also lower than the normal one, leading to a reduced consumption on the input mains lines. This mode of operation allows the VIPer20/20A to meet the new German "Blue Angel" Norm with less than 1W total power consumption for the system when working in stand-by. The output voltage remains regulated around the normal level, with a low frequency ripple corresponding to the burst mode. The amplitude of this ripple is low, because of the output capacitors and because of the low output current drawn in such conditions. The normal operation resumes automatically when the power gets back levels which are higher than P<sub>STBY</sub>.

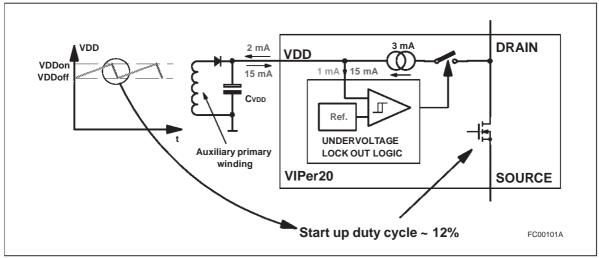

# HIGH VOLTAGE START-UP CURRENT SOURCE

An integrated high voltage current source provides a bias current from the DRAIN pin during the start-up phase. This current is partially absorbed by internal control circuits which are placed into a standby mode with reduced consumption and are also provided to the external capacitor connected to the  $V_{\mbox{\scriptsize DD}}$  pin. As soon as the voltage on this pin reaches the high voltage threshold  $V_{\mbox{\scriptsize DDon}}$  of the

<u>577</u>

UVLO logic, the device turns into active mode and starts switching.

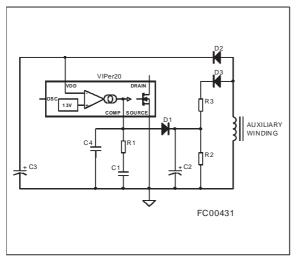

The start up current generator is switched off, and the converter should normally provide the needed current on the  $V_{DD}$  pin through the auxiliary winding of the transformer, as shown on figure 15.

In case of abnormal condition where the auxiliary winding is unable to provide the low voltage supply current to the V<sub>DD</sub> pin (i.e. short circuit on the output of the converter), the external capacitor discharges itself down to the low threshold voltage V<sub>DDoff</sub> of the UVLO logic, and the device gets back to the inactive state where the internal circuits are in standby mode and the start up current source is activated. The converter enters an endless start up cycle, with a start-up duty cycle defined by the ratio of charging current towards discharging when the VIPer20/20A tries to start. This ratio is fixed by design from 2 to 15, which gives a 12% start up duty cycle while the power dissipation at start up is approximately 0.6 W, for a 230 Vrms input voltage. This low value of start-up duty cycle prevents the stress of the output rectifiers and of the transformer when in short circuit.

The external capacitor  $C_{VDD}$  on the  $V_{DD}$  pin must be sized according to the time needed by the converter to start up, when the device starts switching. This time  $t_{SS}$  depends on many parameters, among which transformer design, output capacitors, soft start feature and compensation network implemented on the COMP pin. The following formula can be used for defining the minimum capacitor needed:

$$C_{VDD} > \frac{I_{DD}^{t}SS}{V_{DDhyst}}$$

where:

$I_{DD}$  is the consumption current on the  $V_{DD}$  pin when switching. Refer to specified  $I_{DD1}$  and  $I_{DD2}$  values.

$t_{\rm SS}$  is the start up time of the converter when the device begins to switch. Worst case is generally at full load.

$V_{\text{DDhyst}}$  is the voltage hysteresis of the UVLO logic. Refer to the minimum specified value.

Soft start feature can be implemented on the COMP pin through a simple capacitor which will also be used as the compensation network. In this case, the regulation loop bandwidth is rather low, because of the large value of this capacitor. In case of a large regulation loop bandwidth is mandatory, the schematics in figure 16 can be used. It mixes a high performance compensation network together with a separate high value soft start capacitor. Both soft start time and regulation loop bandwidth can be adjusted separately.

If the device is intentionally shut down by putting the COMP pin to ground, the device is also performing start-up cycles, and the  $V_{DD}$  voltage is oscillating between  $V_{DDon}$  and  $V_{DDoff}$ .

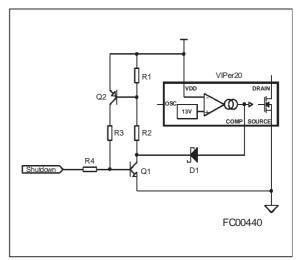

This voltage can be used for supplying external functions, provided that their consumption doesn't exceed 0.5mA. Figure 17 shows a typical application of this function, with a latched shut down. Once the "Shutdown" signal has been activated, the device remains in the off state until the input voltage is removed.

Figure 15: Behavior of the high voltage current source at start-up

#### TRANSCONDUCTANCE ERROR AMPLIFIER

The VIPer20/20A includes a transconductance error amplifier. Transconductance Gm is the change in output current ( $I_{COMP}$ ) versus change in input voltage ( $V_{DD}$ ). Thus:

$$G_m = \frac{\partial I_{COMP}}{\partial V_{DD}}$$

The output impedance  $Z_{COMP}$  at the output of this amplifier (COMP pin) can be defined as:

$$Z_{COMP} = \frac{\partial V_{COMP}}{\partial I_{COMP}} = \frac{1}{G_{m}} \times \frac{\partial V_{COMP}}{\partial V_{DD}}$$

This last equation shows that the open loop gain  $A_{VOL}$  can be related to  $G_m$  and  $Z_{COMP}$ :

$$A_{VOL} = G_m \times Z_{COMP}$$

where  $\ensuremath{G_{m}}$  value for VIPer50/50A is 1.5 mA/V typically.

$G_{m}$  is well defined by specification, but  $Z_{COMP}$  and therefore  $A_{VOL}$  are subject to large tolerances. An impedance  $\,Z\,$  can be connected between the COMP pin and ground in order to define more accurately the transfer function F of the error amplifier, according to the following equation, very similar to the one above:

$$F_{(S)} = Gm \times Z(S)$$

The error amplifier frequency response is reported in figure 10 for different values of a simple resistance connected on the COMP pin. The unloaded transconductance error amplifier shows an internal  $Z_{\text{COMP}}$  of about 330 K $\Omega$ . More complex impedance can be connected on the COMP pin to

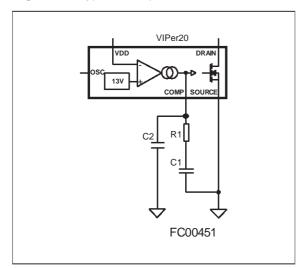

Figure 16: Mixed Soft Start and Compensation

achieve different compensation laws. A capacitor will provide an integrator function, thus eliminating the DC static error, and a resistance in series leads to a flat gain at higher frequency, insuring a correct phase margin. This configuration is illustrated in figure 18.

As shown in figure 18 an additional noise filtering capacitor of 2.2 nF is generally needed to avoid any high frequency interference.

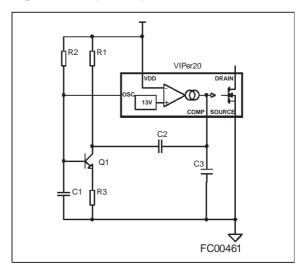

It can also be interesting to implement a slope compensation when working in continuous mode with duty cycle higher than 50%. Figure 19 shows such a configuration. Note that R1 and C2 build the classical compensation network, and Q1 is injecting the slope compensation with the correct polarity from the oscillator sawtooth.

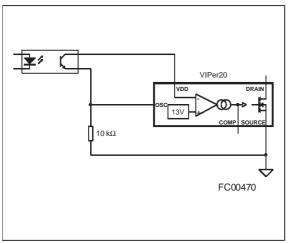

#### **EXTERNAL CLOCK SYNCHRONIZATION**

The OSC pin provides a synchronisation capability, when connected to an external frequency source. Figure 20 shows one possible schematic to be adapted depending on the specific needs. If the proposed schematic is used, the pulse duration must be kept at a low value (500ns is sufficient) for minimizing consumption. The optocoupler must be able to provide 20mA through the optotransistor.

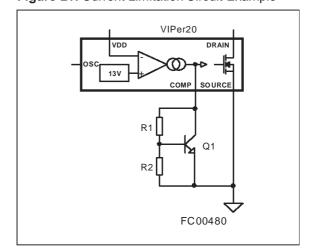

#### PRIMARY PEAK CURRENT LIMITATION

The primary  $I_{DPEAK}$  current and, as resulting effect, the output power can be limited using the simple circuit shown in figure 21. The circuit based on Q1,  $R_1$  and  $R_2$  clamps the voltage on the

Figure 17: Latched Shut Down

COMP pin in order to limit the primary peak current of the device to a value:

$$I_{DPEAK} = \frac{V_{COMP} - 0.5}{H_{ID}}$$

where:

$$V_{COMP} = 0.6 \times \frac{R_1 + R_2}{R_2}$$

The suggested value for  $\mbox{R}_1 + \mbox{R}_2$  is in the range of 220K  $\!\Omega.$

#### **OVER-TEMPERATURE PROTECTION:**

Over-temperature protection is based on chip temperature sensing. The minimum junction temperature at which over-temperature cut-out occurs is 140°C while the typical value is 170°C. The device is automatically restarted when the junction temperature decreases to the restart temperature threshold that is typically 40°C below the shutdown value (see figure 8).

Figure 18: Typical Compensation Network

Figure 20: External Clock Synchronization

Figure 19: Slope Compensation

Figure 21: Current Limitation Circuit Example

Figure 22: Input Voltage Surges Protection

#### **ELECTRICAL OVER STRESS RUGGEDNESS**

The VIPer may be submitted to electrical over stress caused by violent input voltage surges or lightning. Following the enclosed Layout Considerations chapter rules is the most of the time sufficient to prevent catastrophic damages, however in some cases the voltage surges coupled through the transformer auxiliary winding

can overpass the  $V_{DD}$  pin absolute maximum rating voltage value. Such events may trigger the  $V_{DD}$  internal protection circuitry which could be damaged by the strong discharge current of the  $V_{DD}$  bulk capacitor. The simple RC filter shown in figure 22 can be implemented to improve the application immunity to such surges.

Figure 23: Recommended Layout

#### LAYOUT CONSIDERATIONS

Some simple rules insure a correct running of switching power supplies. They may be classified into two categories:

- To minimize power loops: the way the switched power current must be carefully analyzed and the corresponding paths must present the smallest possible inner loop area. This avoids radiated EMC noises, conducted EMC noises by magnetic coupling, and provides a better efficiency by eliminating parasitic inductances, especially on secondary side.

- To use different tracks for low level signals and power ones. The interferences due to a mixing of signal and power may result in instabilities and/or anomalous behavior of the device in case of violent power surge (Input overvoltages, output short circuits...).

In case of VIPer, these rules apply as shown in figure 23. The loops C1-T1-U1, C5-D2-T1, C7-D1-T1 must be minimized. C6 must be as close as possible to T1. The signal components C2, ISO1, C3 and C4 use a dedicated track to be connected directly to the source of the device.

<u>577</u>

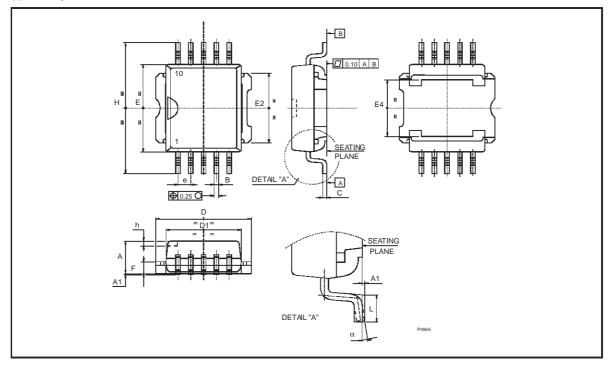

# PowerSO-10<sup>TM</sup> MECHANICAL DATA

| DIM.   |       | mm.  |       |       | inch  |        |

|--------|-------|------|-------|-------|-------|--------|

| DIN.   | MIN.  | TYP  | MAX.  | MIN.  | TYP.  | MAX.   |

| А      | 3.35  |      | 3.65  | 0.132 |       | 0.144  |

| A (*)  | 3.4   |      | 3.6   | 0.134 |       | 0.142  |

| A1     | 0.00  |      | 0.10  | 0.000 |       | 0.004  |

| В      | 0.40  |      | 0.60  | 0.016 |       | 0.024  |

| B (*)  | 0.37  |      | 0.53  | 0.014 |       | 0.021  |

| С      | 0.35  |      | 0.55  | 0.013 |       | 0.022  |

| C (*)  | 0.23  |      | 0.32  | 0.009 |       | 0.0126 |

| D      | 9.40  |      | 9.60  | 0.370 |       | 0.378  |

| D1     | 7.40  |      | 7.60  | 0.291 |       | 0.300  |

| Е      | 9.30  |      | 9.50  | 0.366 |       | 0.374  |

| E2     | 7.20  |      | 7.60  | 0.283 |       | 300    |

| E2 (*) | 7.30  |      | 7.50  | 0.287 |       | 0.295  |

| E4     | 5.90  |      | 6.10  | 0.232 |       | 0.240  |

| E4 (*) | 5.90  |      | 6.30  | 0.232 |       | 0.248  |

| e      |       | 1.27 |       |       | 0.050 |        |

| F      | 1.25  |      | 1.35  | 0.049 |       | 0.053  |

| F (*)  | 1.20  |      | 1.40  | 0.047 |       | 0.055  |

| H      | 13.80 |      | 14.40 | 0.543 |       | 0.567  |

| H (*)  | 13.85 |      | 14.35 | 0.545 |       | 0.565  |

| h      |       | 0.50 |       |       | 0.002 |        |

| L      | 1.20  |      | 1.80  | 0.047 |       | 0.070  |

| L (*)  | 0.80  |      | 1.10  | 0.031 |       | 0.043  |

| α      | 00    |      | 8º    | 00    |       | 8º     |

| α (*)  | 2º    |      | 80    | 20    |       | 8°     |

(\*) Muar only POA P013P

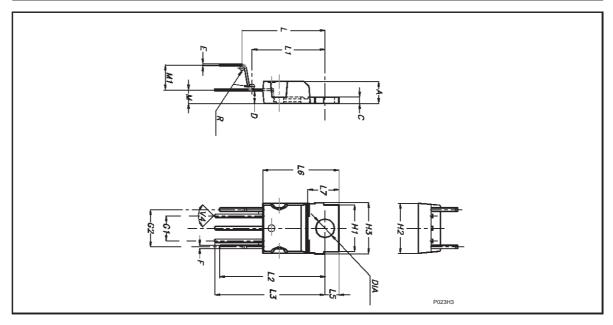

| PENTAW  | ATT UV     | MECHA  | NICAL  | DVIV |

|---------|------------|--------|--------|------|

| PENIAVV | <b>AII</b> | WIEGHA | INICAL | DAIA |

| DIM  | mm.   |       | inch  |       |       |       |

|------|-------|-------|-------|-------|-------|-------|

| DIM. | MIN.  | TYP   | MAX.  | MIN.  | TYP.  | MAX.  |

| Α    | 4.30  |       | 4.80  | 0.169 |       | 0.189 |

| С    | 1.17  |       | 1.37  | 0.046 |       | 0.054 |

| D    | 2.40  |       | 2.80  | 0.094 |       | 0.11  |

| Е    | 0.35  |       | 0.55  | 0.014 |       | 0.022 |

| F    | 0.60  |       | 0.80  | 0.024 |       | 0.031 |

| G1   | 4.91  |       | 5.21  | 0.193 |       | 0.205 |

| G2   | 7.49  |       | 7.80  | 0.295 |       | 0.307 |

| H1   | 9.30  |       | 9.70  | 0.366 |       | 0.382 |

| H2   |       |       | 10.40 |       |       | 0.409 |

| H3   |       | 10.05 | 10.40 |       | 0.396 | 0.409 |

| L    | 15.60 |       | 17.30 | 6.14  |       | 0.681 |

| L1   | 14.60 |       | 15.22 | 0.575 |       | 0.599 |

| L2   | 21.20 |       | 21.85 | 0.835 |       | 0.860 |

| L3   | 22.20 |       | 22.82 | 0.874 |       | 0.898 |

| L5   | 2.60  |       | 3     | 0.102 |       | 0.118 |

| L6   | 15.10 |       | 15.80 | 0.594 |       | 0.622 |

| L7   | 6     |       | 6.60  | 0.236 |       | 0.260 |

| М    | 2.50  |       | 3.10  | 0.098 |       | 0.122 |

| M1   | 4.50  |       | 5.60  | 0.177 |       | 0.220 |

| R    | 0.50  |       |       | 0.02  |       |       |

| V4   |       |       | 90°   | (typ) |       |       |

| Diam | 3.65  |       | 3.85  | 0.144 |       | 0.152 |

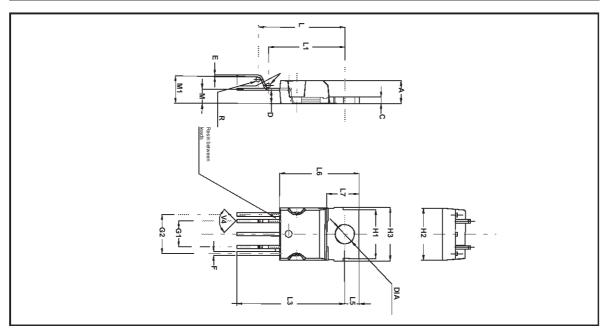

# PENTAWATT HV 022Y (VERTICAL HIGH PITCH) MECHANICAL DATA

| DIM. mm. |       | inch |       |       |       |       |

|----------|-------|------|-------|-------|-------|-------|

| DIIVI.   | MIN.  | TYP  | MAX.  | MIN.  | TYP.  | MAX.  |

| А        | 4.30  |      | 4.80  | 0.169 |       | 0.189 |

| С        | 1.17  |      | 1.37  | 0.046 |       | 0.054 |

| D        | 2.40  |      | 2.80  | 0.094 |       | 0.110 |

| Е        | 0.35  |      | 0.55  | 0.014 |       | 0.022 |

| F        | 0.60  |      | 0.80  | 0.024 |       | 0.031 |

| G1       | 4.91  |      | 5.21  | 0.193 |       | 0.205 |

| G2       | 7.49  |      | 7.80  | 0.295 |       | 0.307 |

| H1       | 9.30  |      | 9.70  | 0.366 |       | 0.382 |

| H2       |       |      | 10.40 |       |       | 0.409 |

| H3       | 10.05 |      | 10.40 | 0.396 |       | 0.409 |

| L        | 16.42 |      | 17.42 | 0.646 |       | 0.686 |

| L1       | 14.60 |      | 15.22 | 0.575 |       | 0.599 |

| L3       | 20.52 |      | 21.52 | 0.808 |       | 0.847 |

| L5       | 2.60  |      | 3.00  | 0.102 |       | 0.118 |

| L6       | 15.10 |      | 15.80 | 0.594 |       | 0.622 |

| L7       | 6.00  |      | 6.60  | 0.236 |       | 0.260 |

| М        | 2.50  |      | 3.10  | 0.098 |       | 0.122 |

| M1       | 5.00  |      | 5.70  | 0.197 |       | 0.224 |

| R        |       | 0.50 |       |       | 0.020 |       |

| V4       |       | 90°  |       |       | 90°   |       |

| Diam.    | 3.70  |      | 3.90  | 0.146 |       | 0.154 |

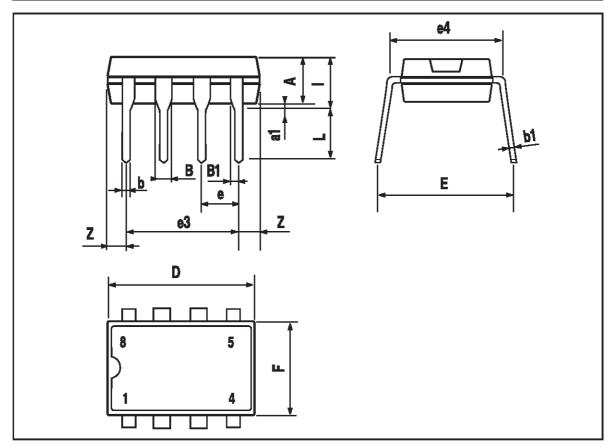

# Plastic DIP-8 MECHANICAL DATA

| DIM  | DIM. mm. |      | inch |       |       |       |

|------|----------|------|------|-------|-------|-------|

| DIM. | MIN.     | TYP  | MAX. | MIN.  | TYP.  | MAX.  |

| А    |          | 3.3  |      |       | 0.130 |       |

| a1   | 0.7      |      |      | 0.028 |       |       |

| В    | 1.39     |      | 1.65 | 0.055 |       | 0.065 |

| B1   | 0.91     |      | 1.04 | 0.036 |       | 0.041 |

| b    |          | 0.5  |      |       | 0.020 |       |

| b1   | 0.38     |      | 0.5  | 0.015 |       | 0.020 |

| D    |          |      | 9.8  |       |       | 0.386 |

| E    |          | 8.8  |      |       | 0.346 |       |

| е    |          | 2.54 |      |       | 0.100 |       |

| e3   |          | 7.62 |      |       | 0.300 |       |

| e4   |          | 7.62 |      |       | 0.300 |       |

| F    |          |      | 7.1  |       |       | 0.280 |

| I    |          |      | 4.8  |       |       | 0.189 |

| L    |          | 3.3  |      |       | 0.130 |       |

| Z    | 0.44     |      | 1.6  | 0.017 |       | 0.063 |

#### PowerSO-10™ SUGGESTED PAD LAYOUT

#### 146-149 108-11 6.30 9.5 108-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11 109-11

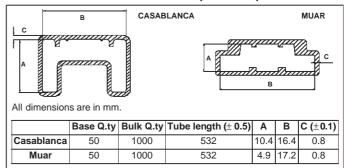

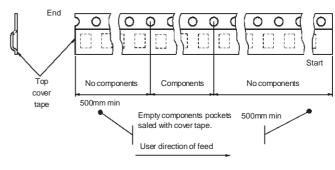

### **TUBE SHIPMENT (no suffix)**

# TAPE AND REEL SHIPMENT (suffix "13TR")

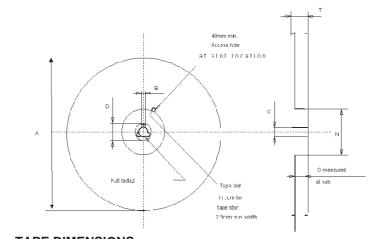

#### **REEL DIMENSIONS**

| Base Q.ty    | 600  |

|--------------|------|

| Bulk Q.ty    | 600  |

| A (max)      | 330  |

| B (min)      | 1.5  |

| C (± 0.2)    | 13   |

| F            | 20.2 |

| G (+ 2 / -0) | 24.4 |

| N (min)      | 60   |

| T (max)      | 30.4 |

All dimensions are in mm.

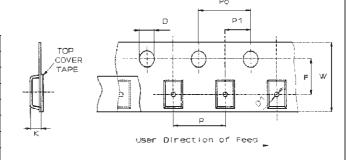

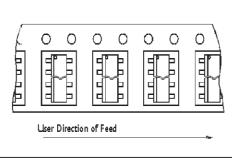

# **TAPE DIMENSIONS**

According to Electronic Industries Association (EIA) Standard 481 rev. A, Feb. 1986

| Tape width        | W            | 24   |

|-------------------|--------------|------|

| Tape Hole Spacing | P0 (± 0.1)   | 4    |

| Component Spacing | Р            | 24   |

| Hole Diameter     | D (± 0.1/-0) | 1.5  |

| Hole Diameter     | D1 (min)     | 1.5  |

| Hole Position     | F (± 0.05)   | 11.5 |

| Compartment Depth | K (max)      | 6.5  |

| Hole Spacing      | P1 (± 0.1)   | 2    |

All dimensions are in mm.

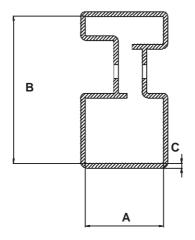

# PENTAWATT HV TUBE SHIPMENT (no suffix)

| Base Q.ty           | 50   |

|---------------------|------|

| Bulk Q.ty           | 1000 |

| Tube length (± 0.5) | 532  |

| Α                   | 18   |

| В                   | 33.1 |

| C (± 0.1)           | 1    |

All dimensions are in mm.

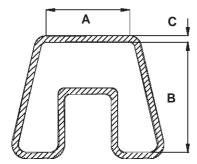

# DIP-8 TUBE SHIPMENT (no suffix)

| Base Q.ty           | 20   |

|---------------------|------|

| Bulk Q.ty           | 1000 |

| Tube length (± 0.5) | 532  |

| Α                   | 8.4  |

| В                   | 11.2 |

| C (± 0.1)           | 0.8  |

All dimensions are in mm.

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may results from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a trademark of STMicroelectronics

© 2002 STMicroelectronics - Printed in ITALY- All Rights Reserved.

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com