# SPI CONTROLLED H-BRIDGE

**PRELIMINARY DATA**

- OPERATING SUPPLY VOLTAGE 5V TO 28V

- TYPICAL R<sub>DSon</sub> = 150 mΩ FOR EACH OUTPUT TRANSISTOR (AT 25°C)

- CONTINOUS DC LOAD CURRENT 5A (T<sub>case</sub> < 100 °C)

- OUTPUT CURRENT LIMITATION AT TYP. 6A

- SHORT CIRCUIT SHUT DOWN FOR OUTPUT CURRENTS OVER 8A

- LOGIC- INPUTS TTL/CMOS-COMPATIBLE

- OPERATING-FREQUENCY UP TO 30 kHz

- OVER TEMPERATURE PROTECTION

- SHORT CIRCUIT PROTECTION

- UNDERVOLTAGE DISABLE FUNCTION

- DIAGNOSTIC BY SPI OR STATUS-FLAG (CONFIGURABLE)

- ENABLE AND DISABLE INPUT

- SO20 POWER PACKAGE

#### **DESCRIPTION**

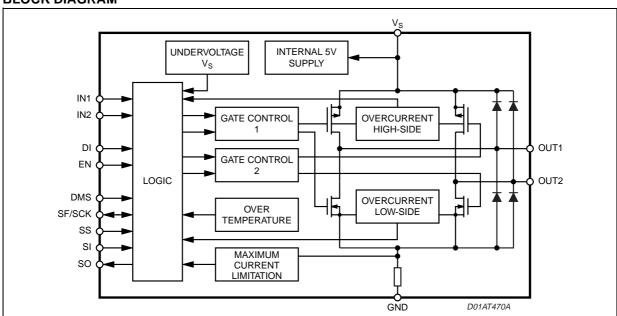

The L9230 is an SPI controlled H-Bridge, designed for the control of DC and stepper motors in safety critical applications and under extreme environmental conditions.

The H-Bridge is protected against over temperature and short circuits and has an under voltage lockout for all the supply voltages "V<sub>S</sub>" (Main DC power supply). All malfunctions cause the output stages to go tristate.

The H-Bridge contains integrated free-wheel diodes. In case of free-wheeling condition, the lowside transistor is switched on in parallel of its diode to reduce the current injected into the substrate.

Switching in parallel is only allowed, if the voltagelevel of the according output-stage is below the ground-level.In this case it must be ensured, that the upper transistor is switched off.

#### **BLOCK DIAGRAM**

March 2003 1/25

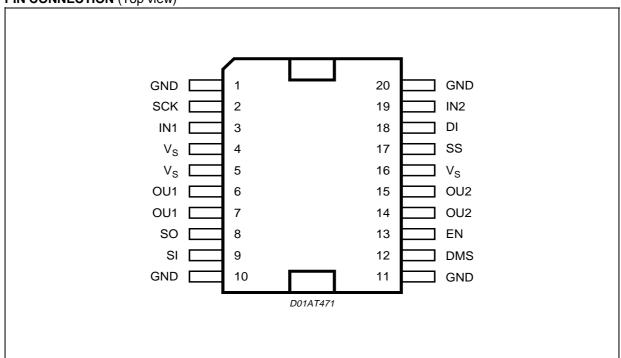

# **PIN FUNCTION**

| N° | Pin    | Description                                                    |

|----|--------|----------------------------------------------------------------|

| 1  | GND    | Ground                                                         |

| 2  | SCK/SF | SPI-Clock/Status-flag                                          |

| 3  | IN1    | Input 1                                                        |

| 4  | Vs     | Supply voltage                                                 |

| 5  | Vs     | Supply voltage                                                 |

| 6  | OU1    | Output 1                                                       |

| 7  | OU1    | Output 1                                                       |

| 8  | SO     | serial out                                                     |

| 9  | SI     | serial in                                                      |

| 10 | GND    | Ground                                                         |

| 11 | GND    | Ground                                                         |

| 12 | DMS    | Diagnostic-Mode selection (+ Supply Voltage for SPI-Interface) |

| 13 | EN     | Enable                                                         |

| 14 | OU2    | Output 2                                                       |

| 15 | OU2    | Output 2                                                       |

| 16 | Vs     | Supply voltage                                                 |

| 17 | SS     | Slave select                                                   |

| 18 | DI     | Disable                                                        |

| 19 | IN2    | Input 2                                                        |

| 20 | GND    | Ground                                                         |

# PIN CONNECTION (Top view)

# **ABSOLUTE MAXIMUM RATINGS**

The integrated circuit must not be destroyed by use at the limit values. Each limit value can be used, as long as no other limit is violated.

Voltage reference point: All values are, if not otherwise stated, relative to ground.

Direction of current flow: Current flow into a pin is positive.

Rise-, fall- and delaytimes: If not otherwise stated, all rise times are between 10% and 90%, fall times

between 90% and 10% and delay times at 50% of the relevant steps.

| Symbol          | Parameter                                         | Test Condition                                              | Min. | Тур. | Max. | Unit |

|-----------------|---------------------------------------------------|-------------------------------------------------------------|------|------|------|------|

| Vs              | Supply voltage                                    | static destruction proof                                    | -1   |      | 40   | V    |

|                 |                                                   | dynamic destruction proof t <0.5s (single pulse, Tj < 85°C) | -2   |      | 40   | V    |

| V <sub>LI</sub> | Logic inputs<br>IN1, IN2, DI, EN, SS, SI, SCK,DMS |                                                             | -0.5 |      | 7    | V    |

| ILI             | Logic inputs<br>IN1, IN2, DI, EN, SS, SI, SCK,DMS |                                                             |      |      | -20  | mA   |

| V <sub>LO</sub> | Logic outputs SF, SO                              | $R \ge 10k\Omega$                                           | -0.5 |      | 7    | V    |

#### THERMAL DATA

| Symbol                 | Parameter                                          | Test Condition  | Min. | Тур. | Max.         | Unit |

|------------------------|----------------------------------------------------|-----------------|------|------|--------------|------|

| Tj                     | Junction temperature                               | dynamic t < 1 s | -40  |      | +150<br>+175 | ο̈́ο |

| T <sub>stg</sub>       | Storage temperature                                |                 | -55  |      | +125         | °C   |

| T <sub>amb</sub>       | Ambient temperature                                |                 | -40  |      | +125         | °C   |

| R <sub>th j-case</sub> | Thermal resistance junction to case <sup>(2)</sup> |                 |      |      | 3            | °C/W |

| T <sub>j_sd</sub>      | Thermal Shutdown Junction<br>Temperature Threshold |                 | 165  | 175  |              | °C   |

# **ELECTRICAL CHARACTERISTCS** ( $T_j = -40 \text{ to } +150^{\circ}\text{C}$ ; $V_S = 5 \text{ to } 28\text{V}$ )

| Symbol   | Parameter             | Test Condition                                                     | Min. | Тур. | Max.     | Unit     |

|----------|-----------------------|--------------------------------------------------------------------|------|------|----------|----------|

| Power Su | ipply                 | ,                                                                  | •    | •    | •        | ·        |

| Vs       | Supply Voltage        | Static Condition                                                   | 5    |      | 28       | V        |

|          |                       | Dynamic Condition (t < 500ms)                                      |      |      | 40       | V        |

|          | Undervoltage Shutdown | (at least down to 2.5V) (1)                                        |      | 4.7  | 5        | V        |

|          | Switch OFF voltage    |                                                                    |      | 4.5  | 5        | V        |

|          | Switch ON voltage     |                                                                    |      | 4.7  | 5        | V        |

|          | Hysteresis            |                                                                    |      | 200  |          | mV       |

| Is       | Supply current        | f = 0 kHz, I <sub>O</sub> = 0 A<br>f = 20kHz, I <sub>O</sub> = 0 A |      |      | 13<br>30 | mA<br>mA |

Note: 1. For supply voltages down to 2.5V the output stages are in tristate condition and the status flag is set to low. Below 2.5V the device operates in undefined condition

2. Guaranteed by design and package characterization

# **ELECTRICAL CHARACTERISTCS** ( $T_j = -40 \text{ to } +150^{\circ}\text{C}$ ; $V_S = 5 \text{ to } 28\text{V}$ ) (continued)

| Symbol                                                                | Parameter                                                 | Test Condition                                                                              | Min. | Тур.     | Max. | Unit   |

|-----------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------|------|----------|------|--------|

| Logic inp                                                             | uts                                                       |                                                                                             |      | ı        |      | ı      |

| VI                                                                    | Logic Input Voltage<br>IN1, IN2, DI, EN                   |                                                                                             | 1    | 1.5      | 2    | V      |

| lı                                                                    | Logic Input Current<br>IN1, IN2, DI                       | $V_1 \le 1V$                                                                                | -200 | -125     |      | μА     |

| I <sub>EN</sub>                                                       | Input Current EN                                          | $V_{IEN} \ge 2V$                                                                            |      | 75       | 100  | μΑ     |

| t <sub>dt</sub>                                                       | Detection Time EN, DI                                     |                                                                                             |      | 3        | 4    | μs     |

| Power Ou                                                              | itputs (OUT1, OUT2)                                       |                                                                                             |      |          |      |        |

| $R_S$                                                                 | Switch on Resistance LS                                   | $R_{OUT-Vs}$ , $V_S > 5 V$                                                                  |      | 150      | 250  | mΩ     |

|                                                                       | Switch on Resistance HS                                   | R <sub>OUT-GND</sub> , V <sub>S</sub> > 5 V                                                 |      | 150      | 250  | mΩ     |

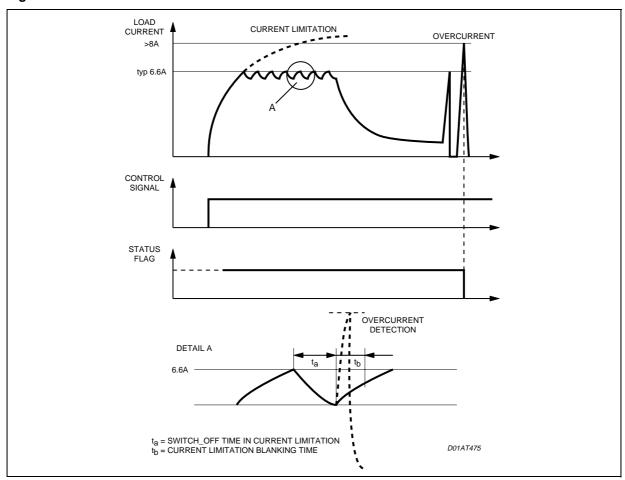

|                                                                       | Current Limitation                                        | Peak value controlled inductive load $L=0.8$ to 5 mH resistive load $R=0.8$ to 1.8 $\Omega$ |      |          |      |        |

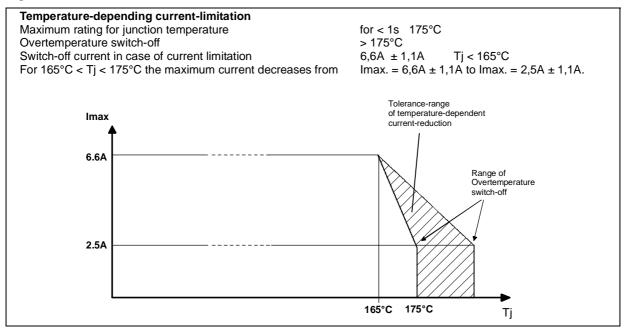

| I <sub>OU</sub>   <sub>max</sub><br> I <sub>OU</sub>   <sub>max</sub> | Switch-off Current                                        | -40 °C < T <sub>j</sub> < 165 °C<br>T <sub>j</sub> < 175 °C                                 | 5.5  | 6<br>2.5 | 7.7  | A<br>A |

| ta                                                                    | Switch-off time (2)                                       |                                                                                             | 12   | 17       | 22   | μs     |

| t <sub>b</sub>                                                        | Blanking time <sup>(2)</sup>                              |                                                                                             | 8    | 11.5     | 15   | μs     |

| t <sub>a</sub> /t <sub>b</sub>                                        | Tracking <sup>(2)</sup>                                   |                                                                                             | 1.4  | 1.5      | 1.6  |        |

| I <sub>OUK</sub>                                                      | Short circuit detection current (1)                       | see figure 1                                                                                | 5.5  |          | 11   | А      |

| Δ Ιουκ                                                                | Short Circuit Current Trecking (1)                        |                                                                                             |      | 1600     |      | mA     |

| t                                                                     | Reactivation time after internal shut down <sup>(2)</sup> | Overcurrent- or overtemperature shut down to reactivation of the output stage               |      |          | 1    | ms     |

| ΙL                                                                    | Leakage Current                                           | Output stage switched off                                                                   |      |          | 1    | mA     |

| $V_{FD}$                                                              | Free-wheel diode forward voltage                          | I <sub>O</sub> = 3A, V <sub>S</sub> = 0V                                                    |      |          | 2    | V      |

| t <sub>rr</sub>                                                       | Free-wheel diode reverse recovery time <sup>(2)</sup>     |                                                                                             |      |          | 100  | ns     |

| VsFHigh                                                               | Output,,high" (SF not set) (*)                            | $V_S = 5V$ , $R_{Pull\_up} = 27K\Omega$                                                     |      | 4.1      |      | V      |

| I <sub>ou</sub>   <sub>max</sub>                                      | Switch OFF Current                                        | Tj = -40 to 165°C                                                                           |      | 6        |      | А      |

|                                                                       |                                                           | Tj = < 175°C                                                                                |      | 2.5      |      | А      |

| I <sub>SF</sub>                                                       | Output,,high" (SF not set) (2)                            | V <sub>SF</sub> = 5V                                                                        |      |          | 20   | μΑ     |

| I <sub>SF</sub>                                                       | Output,,low" (SF set) (3)                                 | V <sub>SF</sub> = 1V                                                                        | 300  |          |      | μΑ     |

|                                                                       |                                                           | V <sub>SF</sub> = 0.5V                                                                      | 100  |          |      | μΑ     |

|                                                                       |                                                           | V <sub>SF</sub> = 0.8V                                                                      | 500  |          |      | μΑ     |

# **ELECTRICAL CHARACTERISTCS** ( $T_j = -40 \text{ to } +150^{\circ}\text{C}$ ; $V_S = 5 \text{ to } 28\text{V}$ ) (continued)

| Symbol                          | Parameter                                     | Test Condition                                                                                                                                                    | Min. | Тур. | Max. | Unit |

|---------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Timing                          |                                               |                                                                                                                                                                   |      |      | •    |      |

| f                               | PWM Frequency                                 | min. operating time 10μs                                                                                                                                          |      | 2    | 30   | kHz  |

| f <sub>S</sub>                  | Switching Frequency during current limitation |                                                                                                                                                                   |      | 5    | 30   | kHz  |

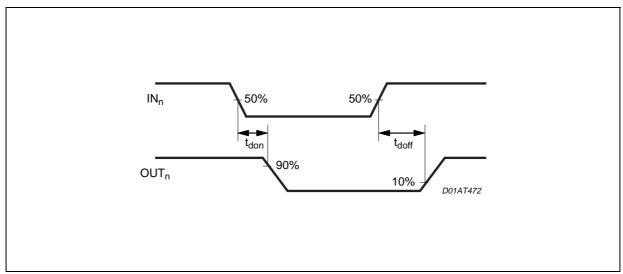

| t <sub>don</sub>                | Output ON-delay                               | IN1> OUT1 or IN2> OUT2                                                                                                                                            |      | 3    | 5    | μs   |

| t <sub>doff</sub>               | Output OFF-delay                              |                                                                                                                                                                   |      | 3    | 5    | μs   |

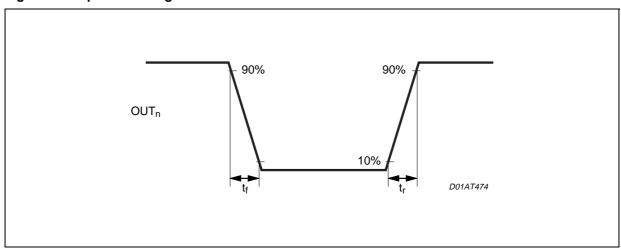

| t <sub>r</sub> , t <sub>f</sub> | Output rise-, fall Time                       | OUT1H> OUT1L, OUT2H> OUT2L, IOUT = 3 A OUT1L> OUT1H, OUT2L> OUT2H                                                                                                 | 0.2  | 0.4  | 1    | μs   |

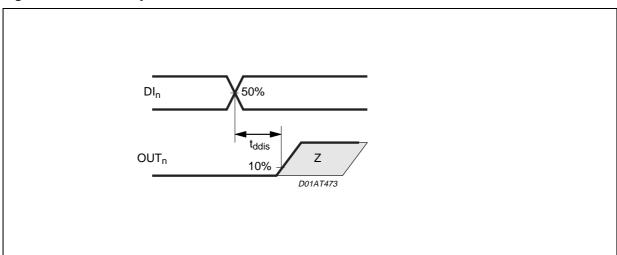

| t <sub>ddis</sub>               | Disable Delay Time                            | DIn> OUTn, En> OUTn                                                                                                                                               |      | 3    | 4    | μs   |

| t <sub>dp</sub>                 | Power on Delay Time                           | V <sub>S</sub> = on> output stage active                                                                                                                          |      |      | 15   | ms   |

|                                 | Delay time for fault detection                |                                                                                                                                                                   | 5    |      | 15   | μs   |

| ΔΙ                              | Effect of reverse current at power supply     | $\begin{array}{l} 4,5V < V_{DMS} < 5,5V \\ -I_{VS} \leq 3A \\ \Delta I \text{ for } I_{SI,} I_{SO,} I_{SS,} I_{SCK,} I_{IN1,} I_{IN2,} I_{EN,}I_{DI} \end{array}$ |      |      | 100  | μА   |

<sup>(\*)</sup> For lower pull up resistances than  $27k\Omega$  the specified value of xxxV (minimum) is guaranteed by design

Note: 1. In case of SC OUTx to Vs the switch off current is always higher than the start value of current regulation ( $\Delta |I_{OUK}| = |I_{OUM}| - |I_{OUmax}|$

- 2. Guaranteed by design

- 3. Value is tested down to 6V. For supply voltage below 6V on increased current can be fed back in the device via a protection path

Figure 1. Output delay time

Figure 2. Disable delay time

Figure 3. Output switching time

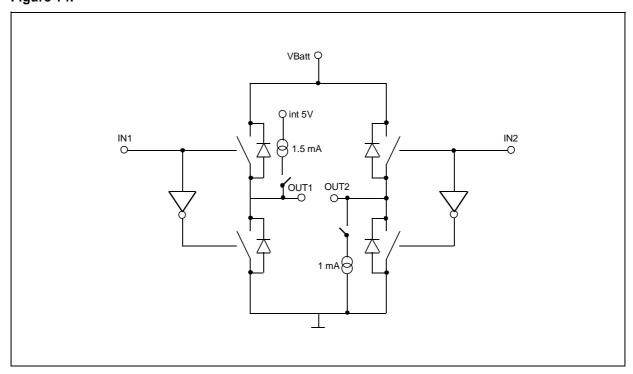

Figure 4.

Figure 5.

# **ELECTRICAL CHARACTERISTICS** (continued) **SPI INTERFACE**

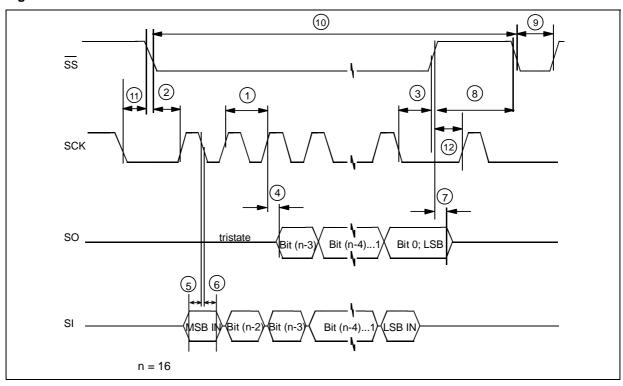

The timing of L9230 is defined as follows:

- The change at output (SO) is forced by the rising edge of the SCK signal.

- The input signal (SI) is taken over on the falling edge of the SCK signal.

- $\overline{SS}$  = active without any clocks at SCK is not allowed

- The data received during a writing access is taken over into the internal registers on the rising edge of the SS signal, if exactly 16 SPI clocks have been counted during SS = active.

Figure 6.

# **ELECTRICAL CHARACTERISTCS** (continued)

| Symbol            | Parameter                           | Test Condition | Min. | Тур. | Max. | Unit |

|-------------------|-------------------------------------|----------------|------|------|------|------|

| Input SCI         | (SPI clock input 4.5V < DMS < 5.5V) |                |      |      |      |      |

| VSCKL             | Low Level                           |                |      |      | 1    | V    |

| V <sub>SCKH</sub> | High Level                          |                | 2    |      |      | V    |

| $\Delta V_{SCK}$  | Hysteresis                          |                | 0.1  |      | 0.4  | V    |

| Csck              | Input Capacity                      |                |      |      | 10   | pF   |

# **ELECTRICAL CHARACTERISTICS** (continued)

| Symbol           | Parameter                                | Test Condition                                     | Min.                       | Тур.      | Max. | Unit   |

|------------------|------------------------------------------|----------------------------------------------------|----------------------------|-----------|------|--------|

| -ISCK            | Input Current                            | Pull up current source connected to V <sub>S</sub> |                            | 20        | 50   | μΑ     |

| Input SS         | (Slave select signal)                    |                                                    | <u>I</u>                   |           | l    |        |

| V <sub>SSL</sub> | Low Level                                | L9230 is selected                                  |                            |           | 1    | V      |

| Vssh             | High Level                               |                                                    | 2                          |           |      | V      |

| ΔVSS             | Hysteresis                               |                                                    | 0.1                        |           | 0.4  | V      |

| C <sub>SS</sub>  | Input Capacity                           |                                                    |                            |           | 10   | pF     |

| -I <sub>SS</sub> | Input Current                            | Pull up current source connected to VDD            |                            | 20        | 50   | μΑ     |

| Input SI (       | SPI data input)                          |                                                    |                            |           |      |        |

| V <sub>SIL</sub> | Low Level                                |                                                    |                            |           | 1    | V      |

| VsiH             | High Level                               |                                                    | 2                          |           |      | V      |

| ΔV <sub>SI</sub> | Hysteresis                               |                                                    | 0.1                        |           | 0.4  | V      |

| C <sub>SI</sub>  | Input Capacity                           |                                                    |                            |           | 10   | pF     |

| -I <sub>SI</sub> | Input Current                            | Pull up current source connected to VDD            |                            | 20        | 50   | μΑ     |

| Output S         | O (Tristate output of the L9230 (SPI     | output); On active reset (DI) output               | SO is in t                 | ristate.) |      |        |

| V <sub>SOL</sub> | Low Level                                | I <sub>SO</sub> = 2mA                              |                            |           | 0.4  | V      |

| Vsон             | High Level                               | I <sub>SO</sub> = -2mA                             | V <sub>VDD</sub><br>- 0.75 |           |      | V      |

| C <sub>SO</sub>  | Capacity                                 | Capacity of the pin in tristate                    |                            |           | 10   | pF     |

| Iso              | Leakage Current                          | In tristate                                        | -10                        |           | 10   | μΑ     |

| Input DM         | S (Supply-Input for the SPI-Inteface     | and Selection Pin for SPI- or SF-Mo                | ode)                       |           |      |        |

| Vi               | Input Voltage                            | SPI-Mode<br>Status-Flag-Mode                       | 3.5                        |           | 0.8  | V<br>V |

| Ic               | Input Current                            | SPI-Mode                                           |                            |           | 10   | mA     |

| Timing           |                                          | '                                                  |                            |           | 1    |        |

| t <sub>cyc</sub> | Cycle-Time (referred to master)          |                                                    | 200                        |           |      | ns     |

| t lead           | Enable Lead Time<br>(referred to master) |                                                    | 100                        |           |      | ns     |

| t lag            | Enable Lag Time (referred to master)     |                                                    | 150                        |           |      | ns     |

|                  |                                          | •                                                  |                            |           | •    |        |

| Symbol                                  | Parameter                                                            | Test Condition                                 | Min.        | Тур.         | Max.                  | Unit     |

|-----------------------------------------|----------------------------------------------------------------------|------------------------------------------------|-------------|--------------|-----------------------|----------|

| t <sub>V</sub>                          | Data Valid CL = 40pF<br>Data Valid CL = 200pF<br>(referred to L9230) |                                                |             |              | 40<br>150             | ns<br>ns |

| t <sub>SU</sub>                         | Data Setup Time<br>(referred to master)                              |                                                | 50          |              |                       | ns       |

| t h                                     | Data Hold Time<br>(referred to master)                               |                                                | 20          |              |                       | ns       |

| t dis                                   | Disable Time<br>(referred to L9230)                                  |                                                |             |              | 100                   | ns       |

| t dt                                    | Transfer Delay (referred to master)                                  |                                                | 150         |              |                       | ns       |

| t SCKH                                  | Serial clock high time (referred to master)                          |                                                | 50          |              |                       | μs       |

| t SCKL                                  | Access time (referred to master)                                     |                                                | 8.35        |              |                       | ns       |

|                                         | Clock inactive before chipselect becomes valid                       |                                                | 200         |              |                       | ns       |

|                                         | Clock inactive after chipselect becomes valid                        |                                                | 200         |              |                       | ns       |

| t <sub>rs</sub>                         | rise-, fall time                                                     | Load on SO 50pF                                | 20          |              |                       | ns       |

| DIAGNOS                                 | STIC                                                                 |                                                |             |              | •                     |          |

|                                         | Diagnostic Threshold (Open Lo                                        | ad Detection DMS > 4,5V, EN < 0                | 0,8V)       |              |                       |          |

| V <sub>OUT1</sub>                       |                                                                      | Load is available                              | 0.8<br>0.8  |              |                       | V<br>V   |

| V <sub>OUT1</sub>                       |                                                                      | Load is missing                                | 1           |              | V <sub>S</sub><br>0.8 | V        |

| I <sub>OUT2</sub><br>-I <sub>OUT1</sub> | Diagnostic Current                                                   | DMS > 4.5V, EN < 0.8V<br>DMS > 4.5V, EN < 0.8V | 700<br>1000 | 1000<br>1500 | 1300<br>2000          | μA<br>μA |

|                                         | Tracking Diagnostic Current                                          | I <sub>OUT1</sub> / I <sub>OUT2</sub>          | 1.4         | 1.5          | 1.6                   |          |

| t <sub>D</sub>                          | Delay Time                                                           |                                                | 30          |              | 100                   | ms       |

#### **TRUTH TABLE**

| Pos.                               | DI | EN | IN1 | IN2 | OUT1 | OUT2 | SF <sup>3)</sup> | SPI <sup>4)</sup><br>DIA_REG |

|------------------------------------|----|----|-----|-----|------|------|------------------|------------------------------|

| 1. forward                         | L  | Н  | Н   | L   | Н    | L    | Н                |                              |

| 2. reverse                         | L  | Н  | L   | Н   | L    | Н    | Н                |                              |

| 3. Free-wheeling low               | L  | Н  | L   | L   | L    | L    | Н                |                              |

| 4. Free-wheeling high              | L  | Н  | Н   | Н   | Н    | Н    | Н                |                              |

| 5. Disable                         | Н  | Х  | Х   | Х   | Z    | Z    | L                |                              |

| 6. Enable                          | Х  | L  | Х   | Х   | Z    | Z    | L                |                              |

| 7. IN1 disconnected                | L  | Н  | Z   | Х   | Н    | Х    | Н                | See                          |

| 8. IN2 disconnected                | L  | Н  | Х   | Z   | Х    | Н    | Н                | Page<br>17                   |

| 9. DI disconnected                 | Z  | Х  | Х   | Х   | Z    | Z    | L                |                              |

| 10. EN disconnected                | Х  | Z  | Х   | Х   | Z    | Z    | L                |                              |

| 11. Current limit. active          | L  | Н  | Х   | Х   | Z    | Z    | Н                |                              |

| 12. Undervoltage 1.)               | Х  | Х  | Х   | Х   | Z    | Z    | L                |                              |

| 13. Overtemperature <sup>2.)</sup> | Х  | Х  | Х   | Х   | Z    | Z    | L                |                              |

| 14. Overcurrent <sup>2.)</sup>     | Х  | Х  | Х   | Х   | Z    | Z    | L                |                              |

- 1.) In case of undervoltage tristate and status-flag are reset automatically.

- 2.) Whenever overcurrent or overtemperature is detected, the fault is stored (i.e. status-flag remains low). The tristate conditions and the status-flag <sup>3)</sup> are reset via DI or EN.

L = Low

H = High

X = High or Low

Z = High impedance

(all output stage transistors are switched off in static state. For more inform. see next page )

Overcurrent: I<sub>OUT1,2</sub> >8,0 A

Overtemperature:  $T_j$  >175 $^{\circ}$ C

Undervoltage:  $V_{Vs-GND}$  <5.0 V (at least down to 2,5V)

- 3.) If Mode "Status-Flag" is selected (see 1.5)

- 4.) If Mode "SPI-Diagnosis is selected (see 1.5)

# Description of the state "Z"

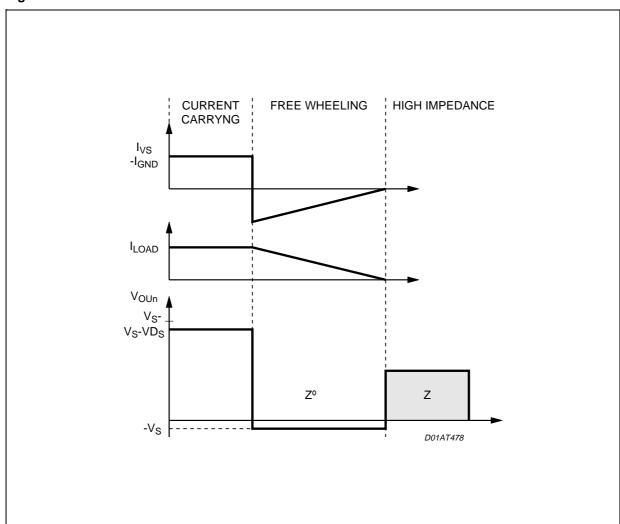

The state "Z" has, depending on the previous operating condition different meaning.

# 1. dynamical

I. e. the inductive load is current carrying and is switched off according to Pos. 5, 6, 9, 10, 11, 12, 13, or 14 of the truth table

- a.) All output stage transistors are switched off.

- b.) The current flow is continued via the free wheeling diodes.

- c.) Free wheeling is detected by a negative voltage-level at OUn.

- d.) Switch on of the parallel-transistor of the current carrying diode.

- f.) Free wheeling is finshed, if the voltage-level on OUn is positive again.

#### 2. statical

g.) all output-stages switched off.

Figure 7.

#### **DIAGNOSTIC**

The Diagnosis-Mode can be selected between SPI-Diagnosis and Status-Flag Diagnosis.

The choise of the Diagnosis-Mode is selected by the voltage-level on pin 12 (DMS Diagnosis Mode Selection).

DMS = GND Status-Flag

DMS = Vcc SPI-Diagnostic

For the connection of pins SI, SO, SS and SCK/SF see Fig. 10 respectively Fig. 11.

#### Status-Flag

The Status-Flag showes the condition "tristate".

At the following fault-cases the output-stages switches in tristate and set the status-flag from high to low.

- Short circuit of OUT1 or OUT2 against  $V_S$  or GND

- Short circuit between OUT1 and OUT2

- Overcurrent

- Overtemperature

- Undervoltage on Vs

In cause of short circuit or overcurrent, the fault will be stored.

The output stage switches in tristate and the status-flag is set from high level to low-level if the specified value is exceeded.

If the voltage level changes from high to low on DI or from low to high on EN, the output stage switches on again and the status-flag is reset to high-level.

In cause of overtemperature the fault will be stored.

The output stage switches in tristate and the status-flag is set from high level to low-level if the specified value is exceeded.

the voltage level changes from high to low on DI or from low to high on EN, the output stage switches on again and the status-flag is reset to high-level.

In cause of undervoltage on  $V_{Batt}$  the output stage switches in tristate and the status-flag is set from high level to low-level if the specified value is fallen. If the voltage has risen about the specified value again, the output stage switches on again and the status-flag is reset to high-level.

The maximum current which can flow under normal operating conditions is limited to typical  $I_{max.} = 6.6A$ . When the maximum current value is reached, the output stages are switched tristate for a fixed time. According to the time-constant the current decreases exponentially until the next switch-on occurs.

At the end if the fixed time the output stage switches on again and the status-flag is reset to high-level.

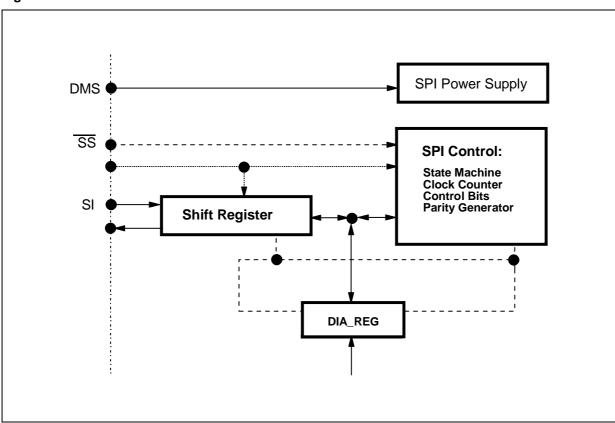

#### **SPI-INTERFACE**

#### **General Discription**

The serial SPI interface establishes a communication link between L9230 and the systems microcontroller. L9230 always operates in slave mode whereas the controller provides the master function.

The maximum baud rate is 2 MBaud (200pF).

Applying an active slave select signal at  $\overline{SS}$  L9230 is selected by the SPI master. SI is the data input (Slave In), SO the data output (Slave Out). Via SCK (Serial Clock Input) the SPI clock is provided by the master.

In case of inactive slave select signal (High) the data output SO goes into tristate.

Figure 8.

Depending on the application the first two bits of an instruction may be used to estabish an <u>ext</u>ended device-addressing. This gives the opportunity to operate up to 4 Slave-devices sharing one common SS signal from the Master-Unit

# Power Supply of the SPI-Interface

SPI-Logic and I/O-Pins are alternativ supplied from DMS or Vcc internal, depending on which voltage is higher. That is why diagnosis of the EN-/DI-Pins is always possible, even in case of missing H-Bridge-power supply e.g. during "Vorlauf/Nauchlauf".

#### Characteristics of the SPI Interface

- When DMS is > 3,5V, the SPI is active, independent of the state of EN or DI and the voltage on V<sub>S</sub>.

During active reset conditions (DMS < 3,5V) the SPI is driven into its default state.</li>

When reset becomes inactive, the state machine enters into a waitstate for the next instruction.

- 2) If the slave select signal at  $\overline{SS}$  is inactive (high), the state machine is forced to enter the waitstate, i.e. the state machine waits for the following instruction.

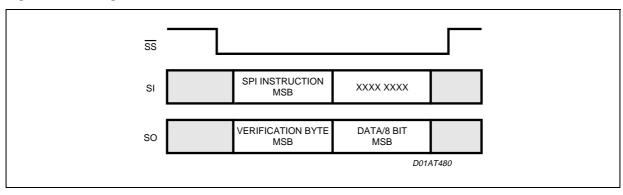

- 3) During active (low) state of the select signal  $\overline{SS}$  the falling edge of the serial clock signal SCK will be used to latch the input data at SI. Output data at SO are driven with the rising edge of SCK. Further processing of the data according to the instruction (i.e. modification of internal registers) will be triggered by the rising edge of the  $\overline{SS}$  signal. (-> See Note)

#### 3) Chipaddress:

In order to establish the option of extended addressing the uppermost two bits of the instruction-byte (i.e the first two SI-bits of a Frame) are reserved to send a chipaddress. To avoid a busconflict the output SO must stay high impedant during the addressing phase of a frame (i.e. until the addressbits are recognised as valid chipaddress). This tristate behavior should be realised in any case, regardless wether the extended addressoption is used or not.

If the chipaddress does not match, the according access will be ignored and SO remains high impedant for the complete frame regardless which frametype is applied.

# 5) Check byte:

Simultaneously to the receipt of an SPI instruction L9230 transmitts a check byte via the output SO to the controller. This byte indicates regular or irregular operation of the SPI. It contains an initial bitpattern and a flag indicating an invalid instruction of the previous access.

- 6) On the read access the databits at the SPI input SI are rejected.

- 7) Invalid instruction/access:

An instruction is invalid, if one of the following conditions is fulfilled:

- an unused instruction code is detected (see tables with SPI instructions).

- in case the previous transmission is not completed in terms of internal data processing. (Violation of the minimum Access-Time.)

If an invalid instruction is detected, any modifications on  $\ registers$  of L9230 are  $\ not$  allowed. In case an unused instruction code occured the databyte "ff<sub>hex</sub>" will be transmitted after having sent the check byte.

In addition any access is invalid if the number of SPI clock pulses (falling edge) counted during active  $\overline{SS}$  differs from exactly 16 clock pulses (-> See Note).

# **SPI Communication**

Figure 9. Reading access / 8 bit

#### **SPI Instruction**

The uppermost 2 bit of the instruction byte contains the chipadress. The individual chipadress is a mask-option and must be defined in accordance to the SPI-Members sharing on SS line.

# SPI Instruction-Format

| MSB |   |        |        |        |        |       |      |

|-----|---|--------|--------|--------|--------|-------|------|

| 7   | 6 | 5      | 4      | 3      | 2      | 1     | 0    |

| 0   | 0 | INSTR4 | INSTR3 | INSTR2 | INSTR1 | INSR0 | INSW |

| Bit | Name        | Description                      |  |  |  |

|-----|-------------|----------------------------------|--|--|--|

| 7,6 | CPAD1,0     | Chip Adress (has to be '0', '0') |  |  |  |

| 5-1 | INSTR (4-0) | SPI instruction (encoding)       |  |  |  |

| 0   | INSW        | Don't care                       |  |  |  |

# **SPI Instruction-Bytes**

|                 | Encoding           |                            |       |                 |  |

|-----------------|--------------------|----------------------------|-------|-----------------|--|

| SPI Instruction | bit 7,6<br>CPAD1,0 | bit 5,4,3,2,1<br>INSTR(40) | Bit 0 | Description     |  |

| RD_IDENT        | 00                 | 00000                      | 0     | read identifier |  |

| RD_VERSION      | 00                 | 00001                      | 1     | read version    |  |

|                 |                    |                            |       |                 |  |

| RD_DIA          | 00                 | 00100                      | 1     | read DIA_REG    |  |

|                 |                    | all others                 |       | no function     |  |

# Reset of the Diagnostic Register DIA\_REG

On the following conditions DIA\_REG is reset:

- DI high

- EN low

- With the rising edge of the SS-signal after the SPI-Instruction RD\_DIA.

- When the voltage on DMS exceeds the threshold for detecting SPI-Mode. (after undervoltage condition)

- Undervoltage on V<sub>S</sub> (< 5,0V) sets Bit 0 .... Bit 3 of DIA\_REG to 0000.

- If UB rises over about the undervoltage level, the Bits of DIA\_REG are restored (when  $V_S$  internal or DMS > 3,5V)

# Verification byte:

| MSB |   |   |   |   |   |   |         |

|-----|---|---|---|---|---|---|---------|

| 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0       |

| Z   | Z | 1 | 0 | 1 | 0 | 1 | TRANS_F |

| Bit | Name    | Description                                                                                         |

|-----|---------|-----------------------------------------------------------------------------------------------------|

| 0   | TRANS_F | Bit = 1: error detected during previous transfer Bit = 0: previous transfer was recognised as valid |

| 1   |         | Fixed to High                                                                                       |

| 2   |         | Fixed to Low                                                                                        |

| 3   |         | Fixed to High                                                                                       |

| 4   |         | Fixed to Low                                                                                        |

| 5   |         | Fixed to High                                                                                       |

| 6   |         | send as high impedance                                                                              |

| 7   |         | send as high impedance                                                                              |

# **Diagnostics/Encoding of Failures**

Description of the SPI Registers (SPI Instructions: RD\_DIA)

| Register:           | DIA_REG       |         |                                                                  |                     |             |       |       |  |

|---------------------|---------------|---------|------------------------------------------------------------------|---------------------|-------------|-------|-------|--|

| 7                   | 6             | 5       | 4 3 2 1                                                          |                     |             |       |       |  |

| DI                  | ОТ            | CurrRe  | ed CurrLim                                                       | DIA21               | DIA20       | Dia11 | DIA10 |  |

| State of Reset: FFH |               |         |                                                                  |                     |             |       |       |  |

| Access by           | y Controller: | Read or | nly                                                              |                     |             |       |       |  |

| Bit                 | Nam           | е       |                                                                  |                     | Description |       |       |  |

| 0                   | DIA 1         | 10      | Diagnosis-Bit1 of OUT1                                           |                     |             |       |       |  |

| 1                   | DIA 1         | 11      | Diagnosis-Bit2 of                                                | OUT1                |             |       |       |  |

| 2                   | DIA 2         | 20      | Diagnosis-Bit1 of                                                | OUT2                |             |       |       |  |

| 3                   | DIA 2         | 21      | Diagnosis-Bit2 of                                                | OUT2                |             |       |       |  |

| 4                   | CurrL         | im      | is set to "0" in case of current limitation                      |                     |             |       |       |  |

| 5                   | CurrRe        | ed      | is set to "0" in case of temperature dependet current limitation |                     |             |       |       |  |

| 6                   | OT            |         | is set to "0" in case of overtemperature                         |                     |             |       |       |  |

| 7                   | DI            | :       | shows the wired-                                                 | or state of the Pin | s EN and DI |       |       |  |

|       | Encoding of the Diagnostic Bits of the Output-Stages OUT1 and OUT2 |       |       |                                         |  |  |  |  |

|-------|--------------------------------------------------------------------|-------|-------|-----------------------------------------|--|--|--|--|

| DIA21 | DIA20                                                              | DIA11 | DIA10 |                                         |  |  |  |  |

| -     | -                                                                  | 0     | 0     | Short circuit over load (SCOL)          |  |  |  |  |

| -     | -                                                                  | 0     | 1     | Short circuit to battery on OUT1 (SCB1) |  |  |  |  |

| -     | -                                                                  | 1     | 0     | Short circuit to ground on OUT1 (SCG1)  |  |  |  |  |

| -     | -                                                                  | 1     | 1     | No error detected on OUT1               |  |  |  |  |

| 0     | 0                                                                  | -     | -     | Open load (OL)                          |  |  |  |  |

| 0     | 1                                                                  | -     | -     | Short circuit to battery on OUT2 (SCB2) |  |  |  |  |

| 1     | 0                                                                  | -     | -     | Short circuit to ground on OUT2 (SCG2)  |  |  |  |  |

| 1     | 1                                                                  | -     | -     | No error detected on OUT2               |  |  |  |  |

|       |                                                                    | •     |       |                                         |  |  |  |  |

| 0     | 0                                                                  | 0     | 0     | Undervoltage on Pin UB                  |  |  |  |  |

# Description of DIA\_REG Bit7

| EN | DI | DIA_REG Bit7 |

|----|----|--------------|

| 0  | 0  | 0            |

| 0  | 1  | 0            |

| 1  | 0  | 1            |

| 1  | 1  | 0            |

#### **Device Identifier**

The IC's identifier is used for production test purposes and features plug & play functionality depending on the systems software release. It is made up on a device-number and a revision number each one read-only accessible via standardised instructions.

The Device number is defines once to allow indentification of different IC-Types by software.

The Revision number may be utilised to distinguish different states of hardware. The contents is divided into an upper 4 bit field reserved to define revisions correspondending to specific software releases.

The lower 4 bit field is utilised to indentify the actual maskset.

Both (SWR and MSR) will start with 0000<sub>b</sub> and are increased by 1 every time an according modification of the hardware is introduced.

# Reading the IC Identifier (SPI Instruction: RD\_IDENT):

| IC Identifier1 (Device ID) |     |      |             |                    |     |     |     |  |

|----------------------------|-----|------|-------------|--------------------|-----|-----|-----|--|

| 7                          | 6   | 5    | 4           | 3                  | 2   | 1   | 0   |  |

| ID7                        | ID6 | ID5  | ID4         | ID3                | ID2 | ID1 | ID0 |  |

| Bit                        | N   | lame | Description |                    |     |     |     |  |

| 70                         | ID  | (70) | ID-No.: 10  | 0100001 <b>L92</b> | 230 |     |     |  |

# Reading the IC revision number (SPI Instruction: RD\_VERSION):

| IC's revisi | ion number |       |                                                  |                 |                |      |      |  |

|-------------|------------|-------|--------------------------------------------------|-----------------|----------------|------|------|--|

| 7           | 6          | 5     | 4                                                | 3               | 2              | 1    | 0    |  |

| SWR3        | SWR2       | SWR1  | SWR0                                             | MSR3            | MSR2           | MSR1 | MSR0 |  |

|             |            |       |                                                  |                 |                |      |      |  |

| Bit         | N          | lame  | Description                                      |                 |                |      |      |  |

| 74          | SW         | R(30) | Revision corresponding to Software release: 0Hex |                 |                |      |      |  |

| 30          | MS         | R(30) | Revision of                                      | corresponding t | o Maskset: 0He | ex   |      |  |

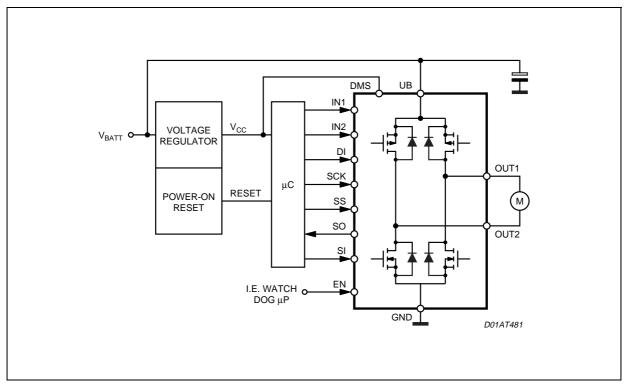

Figure 10. Application example with SPI-Interface

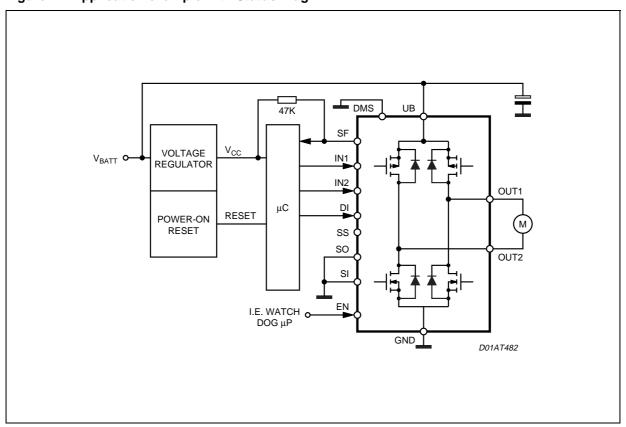

Figure 11. Application example with Status-Flag

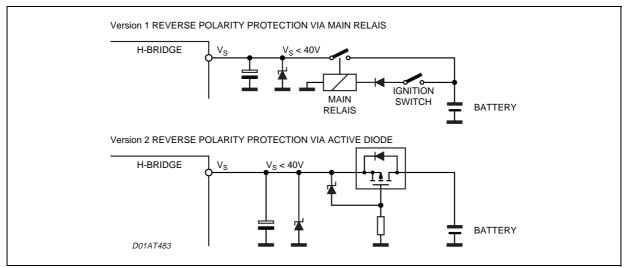

Figure 12. Application examples for Overvoltage- and Reverse-Voltage Protection

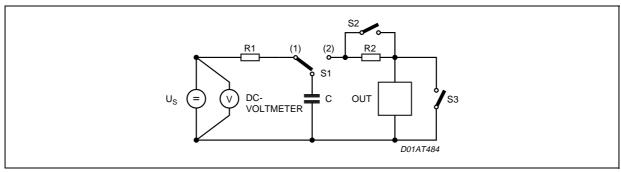

#### **ESD-SOLIDITY**

The connection pins of the IC have to be protected against Electrostatic Discharge ESD) by suitable integrated protection structures.

The integrated circuit has to meet the demand of the "Human-Body-Model" with  $V_C = \pm 4kV$

C = 100 pF and  $R2 = 1.5 k\Omega$  (330 $\Omega$  for OUT1 and OUT2).

Thereby any defect or destruction of the integrated circuit must not occur.

The protection structures realized to reach the ESD-strength have to be coordinated.

The ESD-strength has to be verified by the test circuit given as below.

Figure 13.

For the Pins 4, 5, 6, 7, 14 and 15

$U_C = \pm 4kV$

$R_1 = 100k\Omega$

$R_2=330\Omega$

C = 100pF

Number of pulses each pin: 18

Frequency: 1Hz

Arrangement and performance:

The requirements of MIL883D Methode 3015 have to be fulfilled.

# **ISO-PULSES**

In the main-power-supply-system disturbance transients according to ISO 7637-1 First Edition 1990-06-01 may occur.

By means of external components (see Fig. 12) the following maximum ratings of the IC will not be exceeded.

statical -1V ...... +40V dynamical for t < 500 ms -2V ...... +40V

# **APPENDIX A**

|                             | OUT1 | OUT2 |                                 |

|-----------------------------|------|------|---------------------------------|

| Load available              | 1    | 1    |                                 |

| Open Load                   | 1    | 0    |                                 |

| SC -> GND on OUT1 with Load | 0    | 0    | SC detected on normal operation |

| SC -> GND on OUT2 with Load | 0    | 0    | SC detected on normal operation |

| SC -> UB on OUT1 with Load  | 1    | 1    | SC detected on normal operation |

| SC -> UB on OUT2 with Load  | 1    | 1    | SC detected on normal operation |

| SC -> GND on OUT1 Open Load | 0    | 0    | OL not detected Double Fault    |

| SC -> GND on OUT2 Open Load | 1    | 0    | OL detected                     |

| SC -> UB on OUT1 Open Load  | 1    | 0    | OL detected                     |

| SC -> UB on OUT2 Open Load  | 1    | 1    | OL not detected Double Fault    |

Figure 14.

# **APPENDIX B**

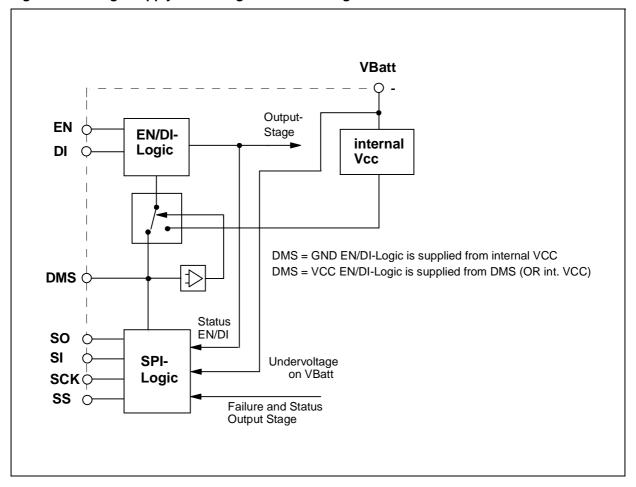

Figure 15. Voltage Supply of SPI-Logic and EN/DI-Logic

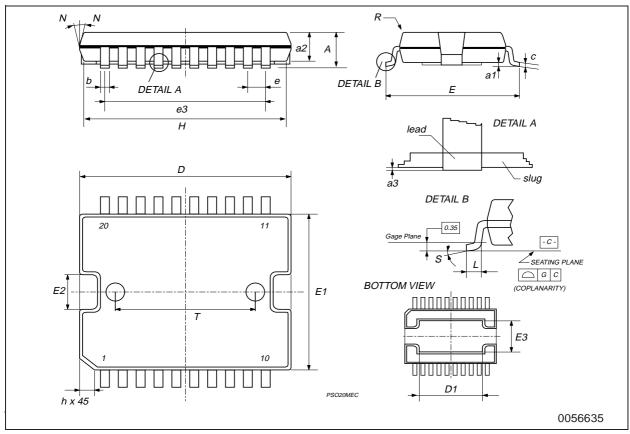

| DIM    |           | mm    |       | inch  |       |       |  |

|--------|-----------|-------|-------|-------|-------|-------|--|

| DIM.   | MIN.      | TYP.  | MAX.  | MIN.  | TYP.  | MAX.  |  |

| Α      |           |       | 3.6   |       |       | 0.142 |  |

| a1     | 0.1       |       | 0.3   | 0.004 |       | 0.012 |  |

| a2     |           |       | 3.3   |       |       | 0.130 |  |

| а3     | 0         |       | 0.1   | 0.000 |       | 0.004 |  |

| b      | 0.4       |       | 0.53  | 0.016 |       | 0.021 |  |

| С      | 0.23      |       | 0.32  | 0.009 |       | 0.013 |  |

| D (1)  | 15.8      |       | 16    | 0.622 |       | 0.630 |  |

| D1     | 9.4       |       | 9.8   | 0.370 |       | 0.386 |  |

| Е      | 13.9      |       | 14.5  | 0.547 |       | 0.570 |  |

| е      |           | 1.27  |       |       | 0.050 |       |  |

| e3     |           | 11.43 |       |       | 0.450 |       |  |

| E1 (1) | 10.9      |       | 11.1  | 0.429 |       | 0.437 |  |

| E2     |           |       | 2.9   |       |       | 0.114 |  |

| E3     | 5.8       |       | 6.2   | 0.228 |       | 0.244 |  |

| G      | 0         |       | 0.1   | 0.000 |       | 0.004 |  |

| Н      | 15.5      |       | 15.9  | 0.610 |       | 0.626 |  |

| h      |           |       | 1.1   |       |       | 0.043 |  |

| L      | 8.0       |       | 1.1   | 0.031 |       | 0.043 |  |

| N      | 8° (typ.) |       |       |       |       |       |  |

| S      |           |       | 8° (n | nax.) |       |       |  |

| Т      |           | 10    |       |       | 0.394 |       |  |

- (1) "D and E1" do not include mold flash or protusions.

Mold flash or protusions shall not exceed 0.15mm (0.006")

Critical dimensions: "E", "G" and "a3".

# **OUTLINE AND MECHANICAL DATA**

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics ® 2003 STMicroelectronics - All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.

http://www.st.com

477