# PROGRAMMABLE AUDIO FRONT END FOR DIGITAL PHONES AND ISDN TERMINALS

### FEATURES:

#### Complete CODEC and FILTER system including:

- PCM ANALOG TO DIGITAL AND DIGITAL TO ANALOG CONVERTERS

- POWERFUL ANALOG FRONT END CAPA-BLE TO INTERFACE DIRECTLY:

- Microphone Dynamic or Electrete

- Earpiece down to  $100\Omega$  or up to 150nF

- Loudspeaker down to  $50\Omega$  or Buzzer up to 600nF.

- TRANSMIT BAND-PASS FILTER

- ACTIVE RC NOISE FILTER

- RECEIVE LOW-PASS FILTER WITH SIN X/X CORRECTION

- MU-LAW OR A-LAW SELECTABLE COM-PANDING CODER AND DECODER

- PRECISION VOLTAGE REFERENCE

#### **Phones Features:**

- DUAL SWITCHABLE MICROPHONE AMPLI-FIER INPUTS. GAIN PROGRAMMABLE: 15 dB RANGE, 1 dB STEP.

- LOUDSPEAKER AMPLIFIER OUTPUT. SWITCHABLE MAXIMUM GAIN: +9dB/+27dB WITH AUTOMATIC DIGITAL ANTICLIPPING SYSTEM. aTTENUATION PROGRAMMABLE: 30dB RANGE, 2dB STEP.

- SEPARATE EARPIECE AMPLIFIER OUTPUT. ATTENUATION PROGRAMMABLE: 15 dB RANGE, 1 dB STEP.

- AUXILIARY TAPE RECORDER ANALOG IN-TERFACE: Tx + Rx COMBINED OUTPUT.

- AUXILIARY SWITCHABLE EXTERNAL RING INPUT (EAIN).

- TRANSIENT SUPRESSION SIGNAL DURING POWER ON.

- INTERNAL PROGRAMMABLE SIDETONE CIRCUIT. ATTENUATION PROGRAMMABLE: 15 dB RANGE, 1 dB STEP, INDEPENDENT FROM Rx CONTROL.

- INTERNAL RING OR TONE GENERATOR IN-CLUDING DTMF TONES, SINEWAVE OR SQUAREWAVE WAVEFORMS. ATTENU-ATION PROGRAMMABLE: 27 dB RANGE, 3 dB STEP.

- RINGER CONTROL PROGRAMMABLE IN-

TERNALLY (µP) OR EXTERNALLY (pin AT)

- COMPATIBLE WITH HANDS-FREE CIRCUIT TEA7540.

- ON CHIP SWITCHABLE ANTI-ACOUSTIC FEED-BACK CIRCUIT (ANTI-LARSEN).

#### **General Features:**

- EXTENDED TEMPERATURE RANGE OP-ERATION (\*) – 25°C TO +85°C.

- EXTENDED POWER SUPPLY RANGE 5V±10%.

- 60 mW OPERATING POWER (TYPICAL).

- 1.0 mW STANDBY POWER (TYPICAL).

- CMOS DIGITAL INTERFACES.

- SINGLE + 5V SUPPLY.

- DIGITAL LOOPBACK TEST MODE.

- PROGRAMMABLE DIGITAL AND CONTROL INTERFACES:

- Digital PCM Interface associated with separate serial Control Interface MI-CROWIRE™ compatible.

- -GCI interface compatible.

- (\*) Functionality guaranteed in the range 25°C to +85°C; Timing and Electrical Specifications are guaranteed in the range -5°C to +70°C.

#### **APPLICATIONS:**

- ISDN TERMINALS.

- DIGITAL TELEPHONES

- CT2 AND GSM APPLICATIONS

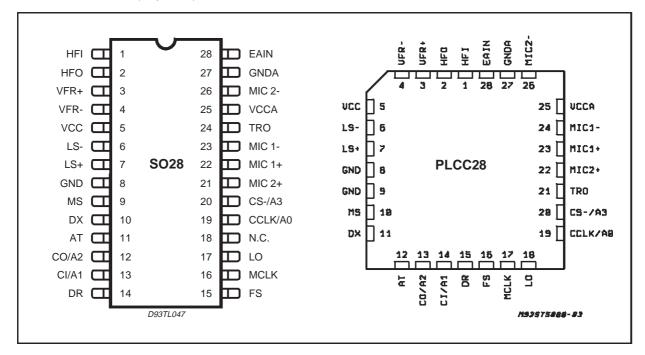

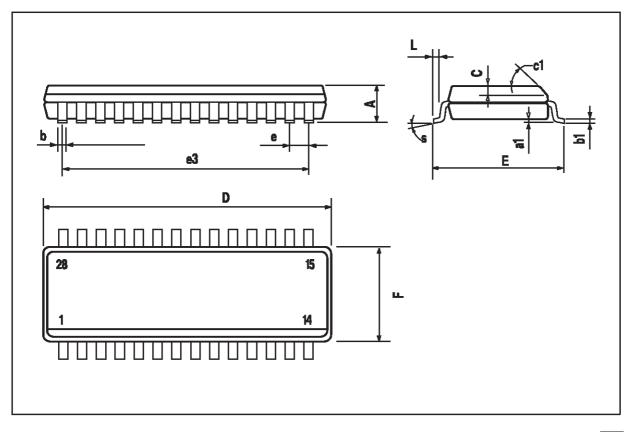

#### **PIN CONNECTION** (Top view)

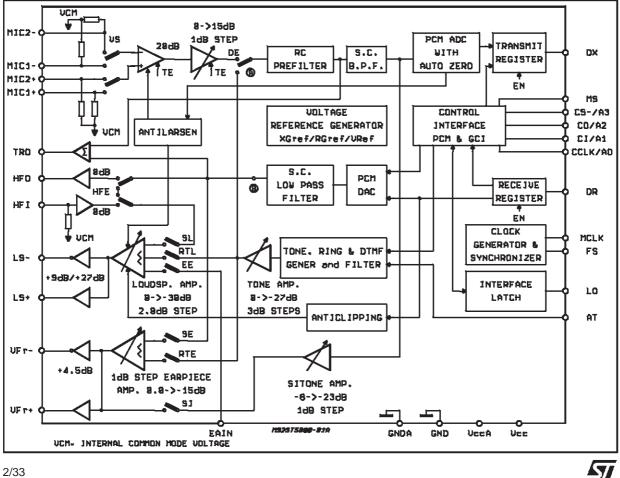

#### **BLOCK DIAGRAM**

2/33

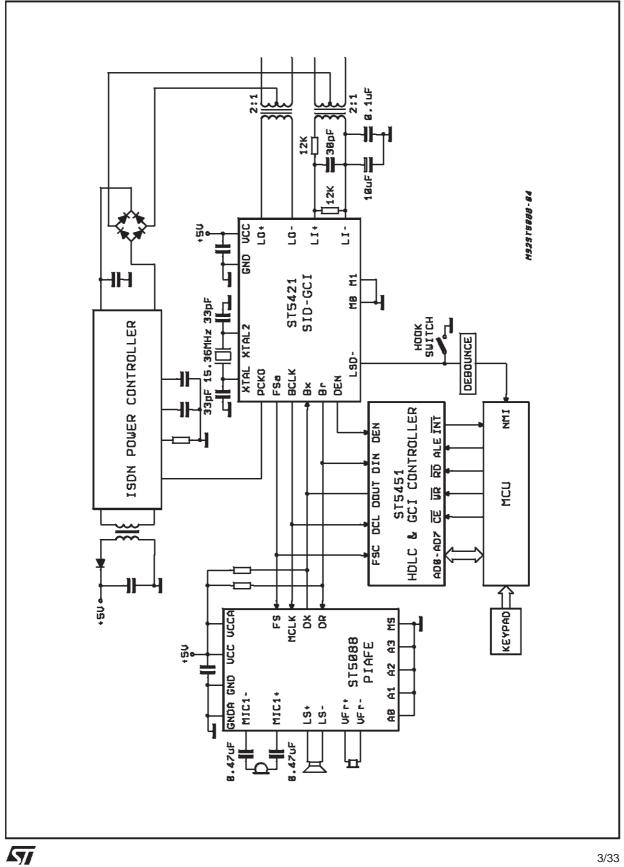

## **TYPICAL ISDN TELEPHONE SET APPLICATION**

#### **GENERAL DESCRIPTION**

ST5088 PIAFE is a combined PCM CODEC/FIL-TER device optimized for ISDN Terminals and Digital Telephone applications. This device is A-law and Mu-law selectable and offers a number of programmable functions accessed through a serial control channel.

Depending on mode selected, channel control is provided by means of a separate serial channel control MICROWIRE compatible or multiplexed with the PCM voice data channel in a GCI compatible format requiring only 4 digital interface pins. When separate serial control interface is selected, PCM interface is compatible with Combo I and Combo II families of devices such as ETC5057/54, TS5070/71.

PIAFE is built using SGS-THOMSON's advanced HCMOS process.

Transmit section of PIAFE consists of an amplifier with switchable high impedance inputs followed by a programmable gain amplifier, an active RC antialiasing pre-filter to provide attenuation of high frequency noise, an 8th order switched capacitor band pass transmit filter and an A-law/Mu-law selectable compandig encoder.

Receive section consist of an A-law/Mu-law selectable expanding decoder which reconstructs the analog sampled data signal, a 3400 Hz low pass filter with sin X/X correction followed by two separate programmable attenuation blocks and two power amplifiers: one can be used to drive an earpiece, and the other to drive a 50  $\Omega$  loudspeaker or a piezo transducer up to 600nF.

When the loudspeaker section is set up with maximum gain (+27dB) the device provide internally a programmable digital anticlipping system to avoid output distortion.

Programmable functions on PIAFE include a Ring/Tone generator which provides one or two tones and can be directed to earpiece or to loud-speaker (or buzzer).

A simple ringer control interface can bypass  $\mu P$  control of sweep frequency and ring ON/OFF phases.

A separate programmable gain amplifier allows gain control of the signal injected. Ring/Tone generator provides sinewave or squarewave signal with precise frequencies which may be also directed to the input of the Transmit amplifier for DTMF tone generation.

An auxiliary analog input (EAIN) is also provided to enable for example the output of an external band limited Ring signal to the Loudspeaker. Transmit signal may be fed back into the receive ampifier with a programmable attenuation to provide a sidetone circuitry.

A switchable anti-accoustic feed-back system cancels the larsen effect in speech monitoring application.

Two additional pins are provided for insertion of an external Handfree function in the Loudspeaker receive path.

An output latch controlled by register programming permits external device control.

| PIN FUNCTIONS | PIN FUNCTIONS |  |

|---------------|---------------|--|

|---------------|---------------|--|

| SO  | PLCC | Name                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,2 | 1,2  | HFI, HFO                            | Hands free I/Os:<br>These two pins can be used to insert an external Handfree circuit<br>such as the TEA 7540 in the receive path. HFO is an output which<br>provides the signal issued from output of the receive low pass filter<br>while HFI is a high impendance input which is connected directly to<br>one of the inputs of the Loudspeaker amplifier.                                                                                 |

| 3,4 | 3,4  | V <sub>Fr+</sub> , V <sub>Fr-</sub> | Receive analog earpiece amplifier complementary<br>outputs, capable of driving load impedances between 100<br>and 400 $\Omega$ or a piezo ceramic transducer up to 150nF.<br>These outputs can drive directly earpiece transductor. The<br>signal at this output can drive be the summ of:<br>- Receive Speech signal from D <sub>R</sub> ,<br>- Internal Tone Generator,<br>- Sidetone signal.                                              |

| 5   | 5    | V <sub>CC</sub>                     | Positive power supply input for the digital section. +5 V $\pm$ 10%.                                                                                                                                                                                                                                                                                                                                                                         |

| 6,7 | 6,7  | LS-,LS+                             | Receive analog loudspeaker amplifier complementary outputs, intended for driving a Loudspeaker: 80 mW on $50\Omega$ load impedance can be provided at low distorsion meeting specifications.<br>Alternatively this stage can drive a piezo transducer up to 600nF. The signal at these outputs can be the sum of:<br>- Receive Speech signal from D <sub>R</sub> ,<br>- Internal Tone generator,<br>- External input signal from EAIN input. |

## PIN FUNCTIONS (continued)

| SO | PLCC | Name             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|----|------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 8  | 8,9  | GND              | Ground: All digital signals are referenced to this pin.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 9  | 10   | MS               | Mode Select: This input selects COMBO I/II interface mode<br>with separate MICROWIRE Control interface when tied high<br>and GCI mode when tied low.                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| 10 | 11   | D <sub>X</sub>   | Transmit Data ouput: Data is shifted out on this pin during the assigned transmit time slots. Elsewhere $D_X$ output is in the high impendance state. In COMBO I/II mode, voice data byte is shifted out from TRISTATE output $D_X$ at the MCLK frequency on the rising edge of MCLK. In GCI mode, voice data byte and control bytes are shifted out from OPEN-DRAIN output $D_X$ at half the MCLK. An external pull up resistor is needed. |  |  |  |  |  |

| 11 | 12   | AT               | Alternate Tone: Ring frequency out is controlled without μP intervention. Tri-state logic controls: f1 (Vcc), f2 (GND), pause (High Impedance).                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 14 | 15   | D <sub>R</sub>   | Receive data input: Data is shifted in during the assigned<br>Received time slots. In the COMBO I/II mode, voice data byte<br>is shifted in at the MCLK frequency on the falling edges of<br>MCLK. In the GCI mode, PCM data byte and contol byte are<br>shifted in at half the MCLK frequency on the receive rising<br>edges of MCLK. There is one period delay between transmit<br>rising edge and receive rising edge of MCLK.           |  |  |  |  |  |

| 15 | 16   | FS               | Frame Sync input: This signal is a 8kHz clock which defines<br>the start of the transmit and receive frames. Either of three<br>formats may be used for this signal: non delayed timing mode<br>delayed timing and GCI compatible timing mode.                                                                                                                                                                                              |  |  |  |  |  |

| 16 | 17   | MCLK             | Master Clock Input: This signal is used by the switched capacitor filters and the encoder/decoder sequencing logic. Values must be 512 kHz, 1.536 MHz, 2.048 MHz or 2.56 MHz selected by means of Control Register CRO. MCLK is used also to shift-in and out data. In GCI mode, 2.56 MHz and 512 kHz are not allowed.                                                                                                                      |  |  |  |  |  |

| 17 | 18   | LO               | Open drain output:<br>a logic 1 written into DO (CR1) appears at LO pin as a logic 0<br>a logic 0 written into DO puts LO pin in high impedance.                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 18 | -    | N. C.            | No connected.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

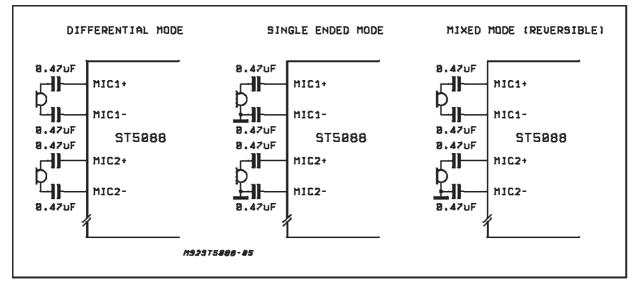

| 21 | 22   | MIC2+            | Alternative positive high impedance input to transmit pre-<br>amplifier.                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 22 | 23   | MIC1+            | Positive high impedance input to transmit pre-amplifier for microphone symetrical connection.                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 23 | 24   | MIC1-            | Negative high impedance input to transmit pre-amplifier for microphone symetrical connection.                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 24 | 21   | TRO              | Tape Recorder Output: This pin provides the analog combination of Tx voice signal and Rx voice signal.                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 25 | 25   | V <sub>CCA</sub> | Positive power supply input for the analog section.<br>+5 V $\pm$ 10%. V <sub>CC</sub> and V <sub>CCA</sub> must be directly connected together.                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 26 | 26   | MIC2-            | Alternative negative high impedance input to transmit pre-<br>amplifier.                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 27 | 27   | GNDA             | Analog Ground: All analog signals are referenced to this pin.<br>GND and GNDA must be connected together close to the<br>device.                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 28 | 28   | EAIN             | External Auxiliary input: This input can be used to provide<br>alternate signals to the Loudspeaker in place of Internal Ring<br>generator. Input signal should be voice band limited.                                                                                                                                                                                                                                                      |  |  |  |  |  |

# Following pin definitions are used only when COMBO I/II mode with separate MICROWIRE compatible serial control port is selected. (MS input set equal one)

PIN FUNCTIONS (continued)

| SO | PLCC | Name | Description                                                                                                                                                                                                                |

|----|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

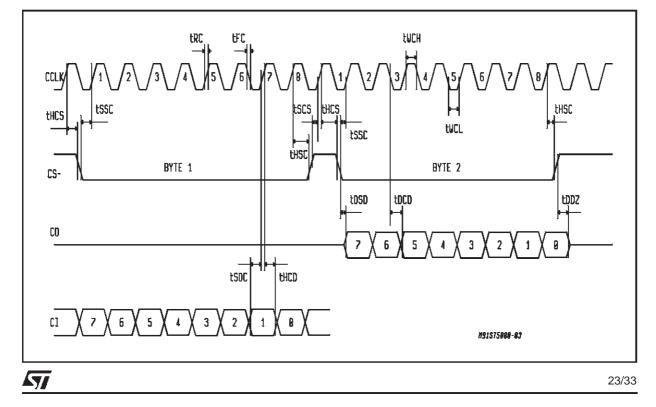

| 12 | 13   | CO   | Control data Output: Serial control/status information is shifted<br>out from the PIAFE on this pin when CS- is low on the falling<br>odges of CCLK.                                                                       |

| 13 | 14   | CI   | Control data Input: Serial Control information is shifted into the PIAFE on this pin when CS- is low on the rising edges of CCLK.                                                                                          |

| 19 | 19   | CCLK | Control Clock input: This clock shifts serial control information<br>into CI and out from CO when the CS- input is low, depending<br>on the current instruction. CCLK may be asynchronous with<br>the other system clocks. |

| 20 | 20   | CS-  | Chip Select input: When this pin is low, control information is written into and out from the PIAFE via CI and CO pins.                                                                                                    |

Following pin definitions are used only when the GCI mode is selected. (MS input set equal zero)

#### **PIN FUNCTIONS** (continued)

| SO          | PLCC        | Name        | Description                                                                                                                                                                            |

|-------------|-------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19,13,12,20 | 19,14,13,20 | A0,A1,A2,A3 | These pins select the address of PIAFE on GCI interface and must be hardwired to either $V_{CC}$ or GND. A0,A1,A2,A3 refer to C4,C5,C6,C7 bits of the first address byte respectively. |

### FUNCTIONAL DESCRIPTION

#### Power on initialization:

When power is first applied, power on reset cicuitry initializes PIAFE and puts it into the power down state. Gain Control Registers for the various programmable gain amplifiers and programmable switches are initialized as indicated in the Control Register description section. All CODEC functions are disabled. Digital Interface is configured in GCI mode or in COMBO I/II mode depending on Mode Select pin connection.

The desired selection for all programmable functions may be intialized prior to a power up command using Monitor channel in GCI mode or MI-CROWIRE port in COMBO I/II mode.

### Power up/down control:

Following power-on initialization, power up and power down control may be accomplished by writing any of the control instructions listed in Table 1 into PIAFE with "P" bit set to 0 for power up or 1 for power down.

Normally, it is recommended that all programmable functions be initially programmed while the device is powered down. Power state control can then be included with the last programming instruction or in a separate single byte instruction.

Any of the programmable registers may also be modified while ST5088 is powered up or down by setting "P" bit as indicated. When power up or down control is entered as a single byte instruction, bit 1 must be set to a 0. When a power up command is given, all de-activated circuits are activated, but output  $D_X$  will remain in the high impedance state on B time slots until the second Fs pulse after power up, even if a B channel is selected.

### Power down state:

Following a period of activity, power down state may be reentered by writing a power down instruction.

Control Registers remain in their current state and can be changed either by MICROWIRE control interface or GCI control channel depending on mode selected.

In addition to the power down instruction, detection of loss MCLK (no transition detected) automatically enters the device in "reset" power down state with  $D_X$  output in the high impedance state and L0 in high impedance state.

### Transmit section:

Transmit analog interface is designed in two stages to enable gains up to 35 dB to be realized. Stage 1 is a low noise differential amplifier providing 20 dB gain. A microphone may be capacitevely connected to MIC1+, MIC1- inputs, while the MIC2+ MIC2– inputs may be used to capacitively connect a second microphone (for digital handsfree operation) or an auxiliary audio circuit such as TEA 7540 Hands-free circuit. MIC1 or MIC2 source is selected with bit 7 of register CR4.

Following the first stage is a programmable gain

amplifier which provides from 0 to 15 dB of additional gain in 1 dB step. The total transmit gain should be adjusted so that, at reference point A, see Block Diagram description, the internal 0 dBmO voltage is 0.739 V (overload level is 1.06 Vrms). Second stage amplifier can be programmed with bits 4 to 7 of CR5. To temporarily mute the transmit input, bit TE (6 of CR4) may be set low. In this case, the analog transmit signal is grounded and the sidetone path is also disabled.

An active RC prefilter then precedes the 8th order band pass switched capacitor filter. A/D converter has a compressing characteristic according to CCITT A or mu255 coding laws, which must be selected by setting bits MA, IA in register CR0. A precision on chip voltage reference ensures accurate and highly stable transmission levels.

Any offset voltage arising in the gain-set amplifier, the filters or the comparator is cancelled by an internal autozero circuit.

Each encode cycle begins immediatly at the beginning of the selected Transmit time slot. The total signal delay referenced to the start of the time slot is approximatively 195  $\mu$ s (due to the transmit filter) plus 123  $\mu$ s (due to encoding delay), which totals 320  $\mu$ s. Voice data is shifted out on D<sub>X</sub> during the selected time slot on the transmit rising adges of MCLK.

#### **Receive section:**

Voice Data is shifted into the decoder's Receive voice data Register via the D<sub>R</sub> pin during the selected time slot on the 8 receive edges of MCLK.

The decoder consists of an expanding DAC with either A or MU255 law decoding characteristic which is selected by the same control instruction used to select the Encode law during initialization. Following the Decoder is a 3400 Hz 6th order low pass switched capacitor filter with integral Sin X/X correction for the 8 kHz sample and hold. 0 dBmO voltage at this (B) reference point (see Block Diagram description) is 0.49 Vrms. A transcient suppressing circuitry ensure interference

noise suppression at power up.

The analog speech signal output can be routed either to earpiece ( $V_{FR+}$ ,  $V_{FR-}$  outputs) or to loud-speaker (LS+, LS- outputs) by setting bits SL and SE (1 and 0 of CR4).

Total signal delay is approximatively 190  $\mu$ s (filter plus decoding delay) plus 62.5  $\mu$ s (1/2 frame) which gives approximatively 252  $\mu$ s.

Differential outputs  $V_{FR+}$ ,  $V_{FR-}$  are intended to directly drive an earpiece. Preceding the outputs is a programmable attenuation amplifier, which must be set by writing to bits 4 to 7 in register CR6. Attenuations in the range 0 to -15 dB relative to the maximum level in 1 dB step can be programmed. The input of this programmable amplifier is the summ of several signals which can be selected

- Receive speech signal which has been decoded and filtered,

- Internally generated tone signal, (Tone amplitude is programmed with bits 4 to 7 of register CR7),

- Sidetone signal, the amplitude of which is programmed with bits 0 to 3 of register CR5

$V_{FR+}$  and  $V_{FR-}$  outputs are capable of driving output power level up to 14mW into differentially connected load impedance between 100 and 400  $\Omega$ .

Differential outputs LS+,LS- are intended to directly drive a Loudspeaker. Preceding the outputs is a programmable attenuation amplifier, which must be set by writing to bits 0 to 3 in register CR6. Attenuations in the range 0 to -30 dB relative to the maximum level in 2.0 dB step can be programmed. The input of this programmable amplifier can be the summ of signals which can be selected by writing to register CR4:

- Receive speech signal which has been decoded and filtered,

- Internally generated tone signal, (Tone amplitude is programmed with bits 4 to 7 of register CR7),

- EAIN input which may be an alternate Ring signal or any voice frequency band limited signal. (An external decoupling capacitor of about 0.1µF is necessary).

Receive voice signal may be directed to output HFO by means of bit HFE in Register CR4. After processing, signal must be re-entered through input HFI to Loudspeaker amplifier input. (An external decoupling capacitor of about  $0.1\mu$ F is necessary).

The output loudspeaker section has two switchable gains of +9dB and +27dB.

#### +9dB LS Gain

This gain mode is fully equivalent to PIAFE ST5080 behaviour.

LS+ and LS- outputs are capable of driving output power level up to 80 mW into 50  $\Omega$  differentially connected load impedance at low distortion meeting PCM channel specifications. When the signal source is a Ring squarewave signal, power levels up to approximatively 200 mW can be delivered.

### +27dB LS Gain

Additional gain of 18dB has the purpose to increase the undistorted output power up to 150mW typical with digital input DR ranging from -12dBm0 to +3dBm0.

Output DC offset is limited by high pass filter with 35Hz cut frequency (with LS gain = +9dB cut frequency = 9Hz)

Anti-acoustic feed-back for loudspeaker to handset microphone loop with squelch effect: on chip

switchable anti-larsen for loudspeaker to handset microphone feedback is implemented. A 12dB depth gain control on both transmit and receive path is provided to keep constant the loop gain. On the transmit path the 12dB gain control is provided starting from the CR5 transmit gain definition; at the same time, on the receive path the 12dB gain control is provided starting from CR6 receive gain definition.

## DIGITAL ANTICLIPPING SYSTEM (D.A.S.)

An automatic anticlipping system is necessary to avoid distortion on LS+/LS- when the output swing approaches the supply rails. (LS GAIN >> +9dB).

The digital anticlipping system calculates equivalent input signal on DR pin and compares it with a selectable anticlipping threshold. The D.A.S. is then able to reduce the overall gain in order to avoid or limit the distortion.

Four different thresholds are programmable via register:

| -15dBm0 | D < 1%      | For safe margin            |

|---------|-------------|----------------------------|

| -13dBm0 | D = 1%      | For normal operation       |

| -9dBm0  | $D \ge 1\%$ | For noisy ambient (*)      |

| -7dBm0  | D >> 1%     | For very noisy ambient (*) |

(\*) When environment is noisy, power output might be more important than 1% distortion.

Gain reduction of the D.A.S. (Anticlipping Attack) has a fixed speed of 8KHz.

Gain recovery or increase (Anticlipping Release) has 4 programmable speeds of 4Hz, 8Hz, 31Hz and 62Hz.

### **TAPE RECORDER OUTPUT (TRO)**

This section provides a combination of Tx and Rx Analog Signals to an external user like a recordering machine. The output levels relative to a signal of 0dBm0 on channel Dx and DR are: Rx TRO =  $0.245V_{RMS}$  (for 0dBm0 on DR) Tx TRO =  $0.246V_{RMS}$  (for 0dBm0 on DX) The single ended Op Amp is able to drive an external load as low as  $600\Omega$ .

### **ALTERNATE TONE CONTROL (AT)**

This section allows to simplify the microprocessor control of ringer operation. When pin AT is put externally at high impedance state (or left open) the control of ring frequency emission is totally through a microprocessor, which updates in real time the contents of various registers.

When pin AT is forced at GND or Vcc the ring generator emits respectively the frequencies f2 (GND) and f1 (Vcc), previously defined through registers CR9 (f2) and CR8(f1). This operative mode requires only start-up intervention of the mi-

croprocessor.

#### **Digital and Control Interface:**

PIAFE provides a choice of either of two types of Digital Interface for both control data and PCM. For compatibility with systems which use time slot oriented PCM busses with a separate Control Interface, as used on COMBO I/II families of devices, PIAFE functions are described in next section.

Alternatively, for systems in which PCM and control data are multiplexed together using GCI interface scheme, PIAFE functions are described in the section following the next one.

PIAFE will automatically switch to one of these two types of interface by sensing the MS pin.

Due to Line Transceiver clock recovery circuitry, a low jitter may be provided on  $F_S$  and MCLK clocks.  $F_S$  and MCLK must be always in phase. For ST5421S Transceiver, as an example, maximun value of jitter amplitude is a step of 65 ns at each GCI frame (125 $\mu$ s). So, the maximum jitter amplitude is 130 ns pk-pk.

## COMBO I/II mode.

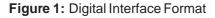

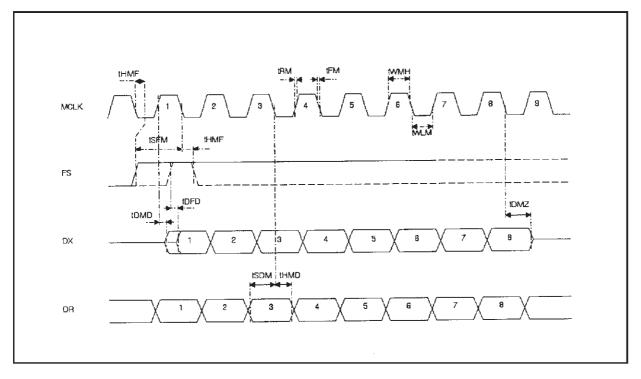

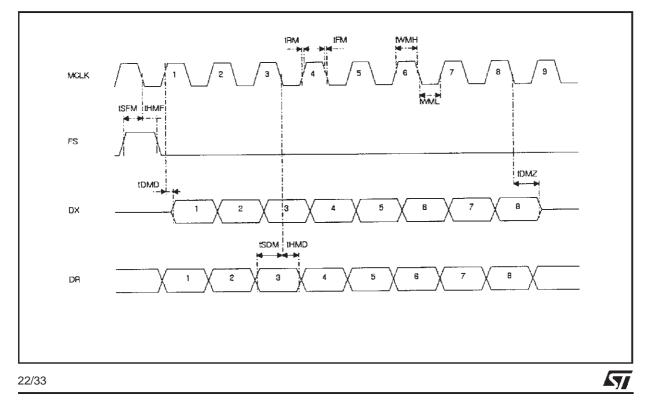

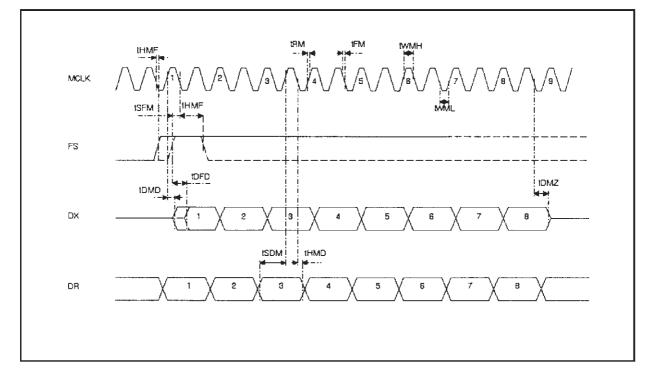

#### Digital Interface (Fig. 1)

Fs Frame Sync input determines the beginning of frame. It may have any duration from a single cycle of MCLK to a squarewave. Two different relationships may be established between the Frame Sync input and the first time slot of frame by setting bit 3 in register CR0. Non delayed data mode is similar to long frame timing on ETC5057/ TS5070 series of devices (COMBO I and COMBO II respectively): first time slot begins nominally coincident with the rising edge of Fs. Alternative is to use delayed data mode, which is similar to short frame sync timing on COMBO I or COMBO II, in which F<sub>S</sub> input must be high at least a half cycle of MCLK earlier the frame beginning. A time slot assignment circuit on chip may be used with both timing modes, allowing connection to one of the two B1 and B2 voice data channels.

Two data formats are available: in Format 1, time slot B1 corresponds to the 8 MCLK cycles following immediately the rising edge of FS, while time slot B2 corresponds to the 8 MCLK cycles following immediately time slot B1.

In Format 2, time slot B1 is identical to Format 1. Time slot B2 appears two bit slots after time slot B1. This two bits space is left available for insertion of the D channel data.

Data format is selected by bit FF (2) in register CR0. Time slot B1 or B2 is selected by bit T0 (0) in Control Register CR1.

Bit EN (2) in control register CR1 enables or disables the voice data transfer on  $D_X$  and  $D_R$  as appropriate. During the assigned time slot,  $D_X$

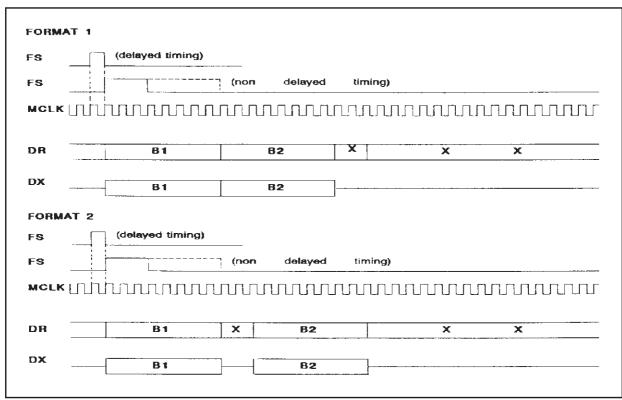

Figure 2: GCI Interface Frame Structure

output shifts data out from the voice data register on the rising edges of MCLK. Serial voice data is shifted into  $D_R$  input during the same time slot on the falling edges of MCLK.

$D_X$  is in the high impedance Tristate condition when in the non selected time slots.

### **Control Interface:**

Control information or data is written into or readback from PIAFE via the serial control port consisting of control clock CCLK, serial data input CI and output CO, and Chip Select input, CS-. All control instructions require 2 bytes as listed in Table 1, with the exception of a single byte power-up/down command.

To shift control data into ST5088, CCLK must be pulsed high 8 times while CS- is low. Data on Cl input is shifted into the serial input register on the rising edge of each CCLK pulse. After all data is shifted in, the content of the input shift register is decoded, and may indicate that a 2nd byte of control data will follow. This second byte may either be defined by a second byte-wide CSpulse or may follow the first contiguously, i.e. it is not mandatory for CS- to return high in between the first and second control bytes. At the end of

the 2nd control byte, data is loaded into the appropriate programmable register. CS- must return high at the end of the 2nd byte.

To read-back status information from PIAFE, the first byte of the appropriate instruction is strobed in during the first CS- pulse, as defined in Table 1. CS- must be set low for a further 8 CCLK cycles, during which data is shifted out of the CO pin on the falling edges of CCLK.

When CS- is high, CO pin is in the high impedance Tri-state, enabling CO pins of several devices to be multiplexed together.

Thus, to summarise, 2 byte READ and WRITE instructions may use either two 8-bit wide CSpulses or a single 16 bit wide CS-pulse.

#### Control channel access to PCM interface:

It is possible to access the B channel previously selected in Register CR1.

A byte written into Control Register CR3 will be automatically transmitted from Dx output in the following frame in place of the transmit PCM data. A byte written into Control Register CR2 will be automatically sent through the receive path to the Receive amplifiers.

In order to implement a continuous data flow from the Control MICROWIRE interface to a B channel, it is necessary to send the control byte on each PCM frame.

A current byte received on D<sub>R</sub> input can be read in the register CR2. In order to implement a continuous data flow from a B channel to MI-CROWIRE interface, it is necessary to read register CR2 at each PCM frame.

#### **GCI COMPATIBLE MODE**

GCI interface is an European standardized interface to connect ISDN dedicated components in the different configurations of equipment as Terminals, Network Terminations, PBX, etc...

In a Terminal equipment, this interface called SCIT for Special Circuit Interface for Terminals allows for example connection between:

- ST5421 (SID-GCI) and ST5451 (HDLC/GCI controller) used for 16 kbit/s D channel packet frames processing and SID control,

- Peripheral devices connected to a 64 kbit/s B channel and ST5451 used for GCI peripheral control.

ST5088 may be assigned to one of the B channels present on the GCI interface and is monitored via a control channel which is multiplexed with the 64 kbit/s Voice Data channels.

Figure 2 shows the frame structure at the GCI interface. Two 256 kbit/s channel are supported.

a)GCI channel 0: It is structured in four subchannels:

-B1 channel 8 bits per frame

- -B2 channel 8 bits per frame

- -M channel8 bits per frame ignored by PIAFE -SC channel 8 bits per frame ignored by

- PIAFE Only B1 or B2 channel can be selected in

PIAFE for PCM data transfer.

b)GCI channel 1: It is structured also in four subchannels:

- -B1\* channel 8 bits per frame -B2\* channel 8 bits per frame

- -M\* channel 8 bits per frame

- –SC\* which is structured as follows:

- 6 bits ignored by PIAFE

- A\* bit associated with M\* channel

- E\* bit associated with M\* channel.

B1\* or B2\* channel can be selected in PIAFE for PCM data transfer.

M\* channel and two associated bits E\* and A\* are used for PIAFE control.

Thus, to summarize, B1, B2, B1\* or B2\* channel can be selected to transmit PCM data and M\* channel is used to read/write status/command peripheral device registers. Protocol for byte exchange on the M\* channel uses E\* and A\* bits.

#### **Physical Interface**

The interface is physically constitued with 4 wires:

| Input Data wire:       | DR   |

|------------------------|------|

| Output Data wire:      | Dx   |

| Bit Clock:             | MCLK |

| Frame Synchronization: | Fs   |

Data is synchronized by MCLK and Fs clock inputs.

Fs insures reinitialization of time slot counter at each frame beginning. The rising edge or FS is the reference time for the first GCI channel bit.

Data is transmitted in both directions at half the MCLK input frequency. Data is transmitted on the the rising edge of MCLK and is sampled one period after the transmit rising edge, also on a rising edge.

Note: Transmit data may be sampled by far-end device ie SID ST5421 on the falling edge 1.5 period after the transmit rising edge.

Unused channel are high impedance. Data outputs are OPEN-DRAIN and need an external pull up resistor.

#### **COMBO** activation/deactivation

ST5088 is automatically set in power down mode when GCI clocks are idle. GCI section is reactivated when GCI clocks are detected. PIAFE is completly reactivated after receiving of a power up command.

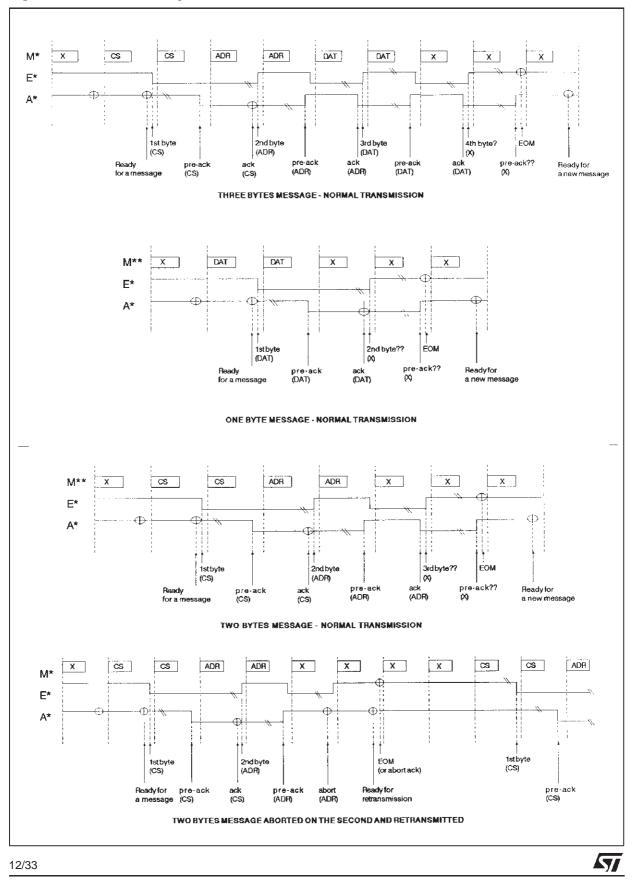

### Exchange protocol on M\* channel

Protocol allows a bidirectional transfer of bytes between ST5088 and GCI controller with acknowledgment at each received byte. For PIAFE, standard protocol is simplified to provide read or write register cycles almost identical to MI-CROWIRE serial interface.

#### Write cycle

Control Unit sends through the GCI controller following bytes:

- First byte is the chip select byte. The first four bits indicate the device address: (A3,A2,A1,A0). The four last bits are ignored. ST5088 compare the validated byte received internally with the address defined by pins A3, A2, A1, A0. If comparison is true, byte is acknowledged, if not, ST5088 does not acknowledge the byte.

**NOTE**: An internal "message in progress" flag remains active till the end of the complete message transmission to avoid irrelevant acknowledgement of any further byte.

- Second byte is structured as defined in Table 1.

- Third byte is the Data byte to write into the Register as indicated in Table 1.

It is possible but optional to write to several different registers in a single message. In this case the Chip Select byte is sent only once at the beginning of the message, the device automatically toggles between address byte and data byte.

#### **Read cycle**

Control Unit sends two bytes. First byte is the chip select byte as defined above. Second byte is structured as defined in Table 1.

If PIAFE identifies a read-back cycle, bit 2 of byte 1 in Table 1 equal 1, it has to respond to the Control Unit by sending a single byte message which is the content of the addressed register.

It is possible but optional to request several different read-back register cycles in a single message but it is recommended to wait the answer before requesting a new read back to avoid loss of data. ST5088 responds by sending a single data byte message at each request.

#### **Received byte validation:**

A received byte is validated if it is detected two consecutive times identical.

### **Exchange Protocol:**

Exchange protocol is identical for both directions. Sender uses E\* bit to indicate that it is sending a M\* byte while receiver uses A\* bit to acknowledge received byte.

When no message is transferred, E\* bit and A\* bit

are forced to inactive state.

A transmission is initialized by sender putting  $E^*$  bit from inactive state to active state and by sending first byte on M<sup>\*</sup> channel in the same frame.

Transmission of a message is allowed only if A\* bit from the receiver has been set inactive for at least two frames.

When receiver is ready, it validates the received byte internally when received in two consecutive frames identical. Then the receiver sets first A\* bit from inactive to active state (pre-acknowlegement), and maintains A\* bit active at least in the following frame (acknowledgement). If validation is not possible, (two last bytes received are not identical), receiver aborts the message setting A\* bit active for only a single frame.

For the first byte received, Abort sequence is not allowed. PIAFE does not respond either if two last bytes are not identical or if the byte received does not meet the Chip Select byte defined by A0-A3 pins bias.

A second byte may be transmitted by the sender putting E\* bit from active to inactive state and sending the second byte on the M\* channel in the same frame. E\* bit is set inactive for only one frame. If it remains inactive more than one frame, it is an end of message (i.e. not second byte available).

The second byte may be transmitted only after receiving the pre-acknowledgment of the previous byte transmitted (see Fig. 3). The same protocol is used if a third byte is transmitted. Each byte has to be transmitted at least in two consecutive frames.

The receiver validates current received byte as done on first byte and then set A\* bit in the next two frames first from active to inactive state (preacknowledgement), and after from inactive to active state (acknowledgement). If the receiver cannot validate the received current byte (two bytes received are not identical), it pre-acknowledges normally, but let A\* bit in the inactive state in the next frame which indicates an abort request.

If a message sent by ST5088 is aborted, it will stop the message and wait for a new read cycle instruction from the controller.

A message received by ST5088 is acknowledged or aborted without flow Control.

Figures 3 gives timing of a write cycle. Most significant bit (MSB) of a Monitor byte is sent first on  $M^*$  channel.

E\* and A\* bits are active low and inactive state on DOUT is high impedance.

### **PROGRAMMABLE FUNCTIONS**

#### Figure 3: E and A bits Timing

For both formats of Digital Interface, programmable functions are configured by writing to a number of registers using a 2-byte write cycle (not including chip select byte in GCI).

Most of these registers can also be read-back for

verification. Byte one is always register address, while byte two is Data.

Table 1 lists the register set and their respective adresses.

| Function                      |   |   | Ac | dre | ss by | Data byte |   |   |                   |

|-------------------------------|---|---|----|-----|-------|-----------|---|---|-------------------|

|                               | 7 | 6 | 5  | 4   | 3     | 2         | 1 | 0 | Dala byle         |

| Single byte Power up/down     | Р | Х | Х  | Х   | Х     | Х         | 0 | Х | none              |

| Write CR0                     | Р | 0 | 0  | 0   | 0     | 0         | 1 | Х | see CR0 TABLE 2   |

| Read-back CR0                 | Р | 0 | 0  | 0   | 0     | 1         | 1 | Х | see CR0           |

| Write CR1                     | Р | 0 | 0  | 0   | 1     | 0         | 1 | Х | see CR1 TABLE 3   |

| Read-back CR1                 | Р | 0 | 0  | 0   | 1     | 1         | 1 | Х | see CR1           |

| Write Data to receive path    | Р | 0 | 0  | 1   | 0     | 0         | 1 | Х | see CR2 TABLE 4   |

| Read data from D <sub>R</sub> | Р | 0 | 0  | 1   | 0     | 1         | 1 | Х | see CR2           |

| Write Data to D <sub>X</sub>  | Р | 0 | 0  | 1   | 1     | 0         | 1 | Х | see CR3 TABLE 5   |

| Write CR4                     | Р | 0 | 1  | 0   | 0     | 0         | 1 | Х | see CR4 TABLE 6   |

| Read-back CR4                 | Р | 0 | 1  | 0   | 0     | 1         | 1 | Х | see CR4           |

| Write CR5                     | Р | 0 | 1  | 0   | 1     | 0         | 1 | Х | see CR5 TABLE 7   |

| Read-back CR5                 | Р | 0 | 1  | 0   | 1     | 1         | 1 | Х | see CR5           |

| Write CR6                     | Р | 0 | 1  | 1   | 0     | 0         | 1 | Х | see CR6 TABLE 8   |

| Read-back CR6                 | Р | 0 | 1  | 1   | 0     | 1         | 1 | Х | see CR6           |

| Write CR7                     | Р | 0 | 1  | 1   | 1     | 0         | 1 | Х | see CR7 TABLE 9   |

| Read-back CR7                 | Р | 0 | 1  | 1   | 1     | 1         | 1 | Х | see CR7           |

| Write CR8                     | Р | 1 | 0  | 0   | 0     | 0         | 1 | Х | see CR8 TABLE 10  |

| Read-back CR8                 | Р | 1 | 0  | 0   | 0     | 1         | 1 | Х | see CR8           |

| Write CR9                     | Р | 1 | 0  | 0   | 1     | 0         | 1 | Х | see CR9 TABLE 11  |

| Read-back CR9                 | Р | 1 | 0  | 0   | 1     | 1         | 1 | Х | see CR9           |

| Write CR10                    | Р | 1 | 0  | 1   | 0     | 0         | 1 | Х | see CR10 TABLE 12 |

| Read-back CR10                | Р | 1 | 0  | 1   | 0     | 1         | 1 | Х | see CR10          |

Table 1: Programmable Register Intructions

NOTE 1: bit 7 of the address byte and data byte is always the first bit clocked into or out from: CI and CO pins when MICROWIRE serial port is enabled, or into and out from D<sub>R</sub> and D<sub>X</sub> pins when GCI mode selected. X = reserved: write 0

NOTE 2: "P" bit is Power up/down Control bit. P = 1 Means Power Down.

Bit 1 indicates, if set, the presence of a second byte.

NOTE 3: Bit 2 is write/read select bit.

| 7                | 6                | 5                | 4                | 3      | 2      | 1      | 0      | Function                                                                                                 |          |

|------------------|------------------|------------------|------------------|--------|--------|--------|--------|----------------------------------------------------------------------------------------------------------|----------|

| F1               | F0               | MA               | IA               | DN     | FF     | B7     | DL     | T diction                                                                                                |          |

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |                  |                  |        |        |        |        | MCLK = 1.536 MHz *<br>MCLK = 2.048 MHz                                                                   | 1)<br>1) |

|                  |                  | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |        |        |        |        | MU-law; CCITT D3-D4 *<br>MU-law; Bare Coding<br>A-law including even bit inversion<br>A-law; Bare Coding |          |

|                  |                  |                  |                  | 0<br>1 |        |        |        | Delayed data timing * (*<br>Non delayed data timing (*                                                   | 1)<br>1) |

|                  |                  |                  |                  |        | 0<br>1 |        |        | B1 and B2 consecutive * (*<br>B1 and B2 separated (*                                                     | 1)<br>1) |

|                  |                  |                  |                  |        |        | 0<br>1 |        | 8 bits time-slot *<br>7 bits time-slot                                                                   |          |

|                  |                  |                  |                  |        |        |        | 0<br>1 | Normal operation *<br>Digital Loop-back                                                                  |          |

Table 2: Control Register CR0 Functions

\*: state at power on initialization

(1): significant in COMBO I/II mode only

## Table 3: Control Register CR1 Functions

| 7      | 6      | 5      | 4      | 3      | 2      | 1                | 0                | Function                                                                                   |   |            |

|--------|--------|--------|--------|--------|--------|------------------|------------------|--------------------------------------------------------------------------------------------|---|------------|

| HFE    | ALE    | DO     | MR     | MX     | EN     | T1               | Т0               | Function                                                                                   |   |            |

| 0<br>1 |        |        |        |        |        |                  |                  | HFO / HFI pins disabled<br>HFO / HFi pins enabled                                          | * |            |

|        | 0<br>1 |        |        |        |        |                  |                  | Anti-larsen disabled<br>Anti-larsen enabled                                                | * |            |

|        |        | 0<br>1 |        |        |        |                  |                  | L0 latch is put in high impedance<br>L0 latch set to 0                                     | * |            |

|        |        |        | 0<br>1 |        |        |                  |                  | D <sub>R</sub> connected to rec. path<br>CR2 connected to rec. path                        | * | (1)<br>(1) |

|        |        |        |        | 0<br>1 |        |                  |                  | Trans path connected to $D_X$<br>CR3 connected to $D_X$                                    | * | (1)<br>(1) |

|        |        |        |        |        | 0<br>1 |                  |                  | voice data transfer disable<br>voice data transfer enable                                  | * |            |

|        |        |        |        |        |        | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | B1 channel selected<br>B2 channel selected<br>B1* channel selected<br>B2* channel selected | * | (2)<br>(2) |

\*: state at power on initialization

(1): significant in COMBO I / II mode only

(2): significant in GCI mode only.

14/33

## Table 4: Control Register CR2 Functions

| 7   | 6  | 5  | 4  | 3  | 2  | 1  | 0   | Function                                                             |  |  |  |  |

|-----|----|----|----|----|----|----|-----|----------------------------------------------------------------------|--|--|--|--|

| d7  | d6 | d5 | d4 | d3 | d2 | d1 | d0  | Function                                                             |  |  |  |  |

| msb |    |    |    |    |    |    | lsb | Data sent to Receive path or Data received from D <sub>R</sub> input |  |  |  |  |

Table 5: Control Registers CR3 Functions

| 7   | 6  | 5  | 4  | 3  | 2  | 1  | 0   | Function                        |

|-----|----|----|----|----|----|----|-----|---------------------------------|

| d7  | d6 | d5 | d4 | d3 | d2 | d1 | d0  | T unction                       |

| msb |    |    |    |    |    |    | lsb | D <sub>X</sub> data transmitted |

Table 6: Control Register CR4 Functions

| 7      | 6      | 5      | 4      | 3                | 2                | 1                | 0                | Function                                                                                                                                                                                        |   |  |  |  |

|--------|--------|--------|--------|------------------|------------------|------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|

| VS     | TE     | SI     | EE     | RTL              | RTE              | SL               | SE               | T unction                                                                                                                                                                                       |   |  |  |  |

| 0<br>1 |        |        |        |                  |                  |                  |                  | MIC1 selected<br>MIC2 selected                                                                                                                                                                  | * |  |  |  |

|        | 0<br>1 |        |        |                  |                  |                  |                  | Transmit input muted<br>Transmit input enabled                                                                                                                                                  | * |  |  |  |

|        |        | 0<br>1 |        |                  |                  |                  |                  | Internal sidetone disabled<br>Internal sidetone enabled                                                                                                                                         | * |  |  |  |

|        |        |        | 0<br>1 |                  |                  |                  |                  | EAIN disconnected<br>EAIN selected to Loudspeaker                                                                                                                                               | * |  |  |  |

|        |        |        |        | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |                  |                  | Ring / Tone muted<br>Ring / Tone to Earpiece<br>Ring / Tone to Loudspeaker<br>Ring / Tone to Earpiece and Loudspeaker                                                                           | * |  |  |  |

|        |        |        |        |                  |                  | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | Receive signal muted<br>Receive signal connected to earpiece amplifer<br>Receive signal connected to loudspeaker amplifier<br>Receive signal connected to loudspeaker and<br>earpiece amplifier | * |  |  |  |

state at power on initialization

| 57 |

|----|

|----|

\*:

## Table 7: Control Register CR5 Functions

| 7                | 6                | 5                | 4                | 3                | 2                | 1                | 0                | Function                                                  |

|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|-----------------------------------------------------------|

| Tra              | ansmit           | ampli            | fier             | Sid              | etone            | ampli            | fier             | i unction                                                 |

| 0<br>0<br>-<br>1 | 0<br>0<br>-<br>1 | 0<br>0<br>-<br>1 | 0<br>1<br>-<br>1 |                  |                  |                  |                  | 0 dB gain *<br>1 dB gain<br>in 1 dB step<br>15 dB gain    |

|                  |                  |                  |                  | 0<br>0<br>-<br>1 | 0<br>0<br>-<br>1 | 0<br>0<br>-<br>1 | 0<br>1<br>-<br>1 | -8 dB gain *<br>-9 dB gain<br>in 1 dB step<br>-23 dB gain |

\*: state at power on initialization

## Table 8: Control Register CR6 Functions

| 7                | 6                             | 5                | 4                | 3                | 2                | 1                | 0                | Function                                                 |

|------------------|-------------------------------|------------------|------------------|------------------|------------------|------------------|------------------|----------------------------------------------------------|

| Ea               | Earpiece ampifier Loudspeaker |                  |                  |                  |                  | peake            | r                | i unononi                                                |

| 0<br>0<br>-<br>1 | 0<br>0<br>-<br>1              | 0<br>0<br>-<br>1 | 0<br>1<br>-<br>1 |                  |                  |                  |                  | 0 dB gain *<br>-1 dB gain<br>in 1 dB step<br>-15 dB gain |

|                  |                               |                  |                  | 0<br>0<br>-<br>1 | 0<br>0<br>-<br>1 | 0<br>0<br>-<br>1 | 0<br>1<br>-<br>1 | 0 dB gain *<br>-2 dB gain<br>in 2 dB step<br>-30 dB gain |

\*: state at power on initialization

## Table 9: Control Register CR7 Functions

| 7                                         | 6                                    | 5                                         | 4                                    | 3                | 2                | 1  | 0      |                                                                                                          | Function                                                                        |                                                                                 |  |  |  |

|-------------------------------------------|--------------------------------------|-------------------------------------------|--------------------------------------|------------------|------------------|----|--------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|--|--|

|                                           | Tone                                 | gain                                      |                                      | F1               | F2               | SN | DE     | Attenuation                                                                                              | f1 V <sub>pp</sub>                                                              | f2 V <sub>pp</sub>                                                              |  |  |  |

| 0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1 | 0<br>0<br>0<br>1<br>1<br>1<br>X<br>X | 0<br>0<br>1<br>1<br>0<br>1<br>1<br>X<br>X | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 |                  |                  |    |        | 0 dB *<br>-3 dB<br>-6 dB<br>- 9 dB<br>-12 dB<br>-15 dB<br>-15 dB<br>-21 dB<br>-21 dB<br>-24 dB<br>-27 dB | 2.4 (1)<br>1.70<br>1.20<br>0.85<br>0.60<br>0.43<br>0.30<br>0.21<br>0.15<br>0.10 | 1.9 (1)<br>1.34<br>0.95<br>0.67<br>0.47<br>0.34<br>0.24<br>0.17<br>0.12<br>0.08 |  |  |  |

|                                           |                                      |                                           |                                      | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 0  |        | f1 and f2 muted<br>f2 selected<br>f1 selected<br>f1 and f2 in summed m<br>Squarewave signal sel          | *                                                                               |                                                                                 |  |  |  |

|                                           |                                      |                                           |                                      |                  |                  | 1  |        | Sinewave signal selected                                                                                 |                                                                                 |                                                                                 |  |  |  |

|                                           |                                      |                                           |                                      |                  |                  |    | 0<br>1 | Normal operation * Tone / Ring Generator connected toTransmit path                                       |                                                                                 |                                                                                 |  |  |  |

\*: state at power on initialization

(1):

value provided if f1 or f2 is selected alone. if f1 and f2 are selected in the summed mode, f1=1.34  $V_{pp}$  while f2=1.06  $V_{pp}$ . Output generator is 2.4  $V_{pp}$

Х reserved: write 0

## Table 10: Control Register CR8 Functions

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | Function                                                     |

|-----|-----|-----|-----|-----|-----|-----|-----|--------------------------------------------------------------|

| f17 | f16 | f15 | f14 | f13 | f12 | f11 | f10 | Tunction                                                     |

| mst |     |     |     |     |     |     | lsb | Binary equivalent of the decimal number used to calculate f1 |

## Table 11: Control Register CR9 Functions

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | Function                                                     |  |  |  |  |

|-----|-----|-----|-----|-----|-----|-----|-----|--------------------------------------------------------------|--|--|--|--|

| f27 | f26 | f25 | f24 | f23 | f22 | f21 | f20 |                                                              |  |  |  |  |

| msb |     |     |     |     |     |     | lsb | Binary equivalent of the decimal number used to calculate f2 |  |  |  |  |

## Table 12: Control Register CR10 Functions

| 7      | 6      | 5                | 4                | 3                | 2                | 1                | 0                | Function                                                                                                                                                                             |  |  |  |  |  |

|--------|--------|------------------|------------------|------------------|------------------|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| GLS    | ACE    | VT1              | VT0              | FD1              | FD0              | DFT              | HFT              | Function                                                                                                                                                                             |  |  |  |  |  |

| 1<br>0 |        |                  |                  |                  |                  |                  |                  | +27 dB into LH Path<br>(*) +9dB into LH Path                                                                                                                                         |  |  |  |  |  |

|        | 1<br>0 |                  |                  |                  |                  |                  |                  | Anticlipping ON<br>(*) Anticlipping OFF                                                                                                                                              |  |  |  |  |  |

|        |        | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |                  |                  |                  |                  | (*) -15dm0 Anticlipping Threshold<br>-13dm0 Anticlipping Threshold<br>-9dm0 Anticlipping Threshold<br>-7dm0 Anticlipping Threshold                                                   |  |  |  |  |  |

|        |        |                  |                  | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |                  |                  | (*) 256ms Gain Recovery Time Constant / (4Hz)<br>128ms Gain recovery Time Constant / (8Hz)<br>32ms Gain Recovery Time Constant / (31Hz)<br>16ms Gain Recovery Time Constant / (62Hz) |  |  |  |  |  |

|        |        |                  |                  |                  |                  | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | (*) Standard Frequency Tone Range<br>Halved Frequency Tone Range<br>Doubled Frequency Tone Range<br>Forbidden                                                                        |  |  |  |  |  |

(\*) Default values inserted into the Register at Power On.

### CONTROL REGISTER CR0

First byte of a READ or a WRITE instruction to Control Register CR0 is as shown in TABLE 1. Second byte is as shown in TABLE 2.

#### **Master Clock Frequency Selection**

A master clock must be provided to PIAFE for operation of filter and coding/decoding functions. In COMBO I/II mode, MCLK frequency can be either 512 kHz, 1.536 MHz, 2.048 MHz or 2.56 MHz.

Bit F1 (7) and F0 (6) must be set during initialization to select the correct internal divider.

In GCI mode, MCLK must be either 1.536MHz or

2.048MHz.

512KHz and 2.56MHz are not allowed. Default value is 1.536 MHz for both modes. Any clock different from the default one must be selected prior a Power-Up instruction for both modes.

#### **Coding Law Selection**

Bits MA (5) and IA (4) permit selection of Mu-255 law or A law coding with or without even bit inversion.

After power on initialization, the Mu-255 law is selected.

|                    |   | Mu 255 law |        |        |        |        |        |        | True A law even bit<br>inversion |        |        |        |        |        |        |        | A law without even bit inversion |        |        |        |        |        |        |        |

|--------------------|---|------------|--------|--------|--------|--------|--------|--------|----------------------------------|--------|--------|--------|--------|--------|--------|--------|----------------------------------|--------|--------|--------|--------|--------|--------|--------|

|                    | m | sb         |        |        |        |        | ls     | b      | msb Isb                          |        |        |        |        |        | msb    |        |                                  |        |        |        | lsb    |        |        |        |

| Vin = + full scale | 1 | 0          | 0      | 0      | 0      | 0      | 0      | 0      | 1                                | 0      | 1      | 0      | 1      | 0      | 1      | 0      | 1                                | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

| Vin = 0 V          |   | 1<br>1     | 1<br>1 | 1<br>1 | 1<br>1 | 1<br>1 | 1<br>1 | 1<br>1 | 1<br>0                           | 1<br>1 | 0<br>0 | 1<br>1 | 0<br>0 | 1<br>1 | 0<br>0 | 1<br>1 | 1<br>0                           | 0<br>0 |

| Vin = - full scale | 0 | 0          | 0      | 0      | 0      | 0      | 0      | 0      | 0                                | 0      | 1      | 0      | 1      | 0      | 1      | 0      | 0                                | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

MSB is always the first PCM bit shifted in or out of PIAFE.

#### **Digital Interface timing**

Bit DN=0 (3) selects digital interface in delayed timing mode while DN=1 selects non delayed data timing.

In GCI mode, bit DN is not significant.

After reset and if COMBO I/II mode is selected, delayed data timing is selected.

### **Digital Interface format**

Bit FF=0 (2) selects digital interface in Format 1 where B1 and B2 channel are consecutive. FF=1 selects Format 2 where B1 and B2 channel are separated by two bits. (see digital interface format section).

In GCI mode, bit FF is not significant.

#### 56+8 selection

Bit 'B7' (1) selects capability for PIAFE to take into account only the seven most significant bits of the PCM data byte selected.

When 'B7' is set, the LSB bit on  $D_R$  is ignored and LSB bit on  $D_X$  is high impedance. This function allows connection of an external "in band" data generator directly connected on the Digital Interface.

### **Digital loopback**

Digital loopback mode is entered by setting DL bit(0) equal 1.

In Digital Loopback mode, data written into Receive PCM Data Register from the selected received time-slot is read-back from that Register in the selected transmit time-slot on  $D_X$ . Time slot is selected with Register CR1.

No PCM decoding or encoding takes place in this mode. Transmit and Receive amplifier stages are muted.

### **CONTROL REGISTER CR1**

First byte of a READ or a WRITE instruction to Control Register CR1 is as shown in TABLE 1. Second byte is as shown in TABLE 3.

#### Hands-free I/Os selection

Bit HFE set to one enables HFI, HFO pins for connection of an external handfree circuit such as TEA 7540. HFO is an analog output that provides the receive voice signal. 0 dBMO level on that output is 0.491 Vrms ( $1.4V_{pp}$ ). HFI is an analog high impedance input ( $10 \ K\Omega \ typ$ .) intended to send back the processed receive signal to the Loudspeaker. 0 dBMO level on that input is 0.491Vrms.

#### Anti-larsen selection

Bit ALE set to one enables on-chip antilarsen and squelch effect system.

#### Latch output control

Bit DO controls directly logical status of latch output LO: ie, a "ZERO" written in bit DO puts output LO in high impedance, a "ONE" written in bit DO sets output LO to zero.

# Microwire access to B channel on receive path

Bit MR (4) selects access from MICROWIRE Register CR2 to Receive path. When bit MR is set high, data written to register CR2 is decoded each frame, sent to the receive path and data input at  $D_R$  is ignored.

In the other direction, current PCM data input received at  $D_R$  can be read from register CR2 each frame.

# Microwire access to B channel on transmit path

Bit MX (3) selects access from MICROWIRE write only Register CR3 to  $D_X$  output. When bit MX is set high, data written to CR3 is output at  $D_X$  every frame and the output of PCM encoder is ignored.

### **B** channel selection

Bit 'EN' (2) enables or disables voice data transfer on  $D_X$  and  $D_R$  pins. When disabled, PCM data from DR is not decoded and PCM time-slots are high impedance on  $D_X$ .

In GCI mode, bits 'T1' (1) and 'T0' (0) select one of the four channels of the GCI interface.

In COMBO I/II mode, only B1 or B2 channel can be selected according to the interface format selected. Bit 'T1' is ignored.

#### **CONTROL REGISTER CR2**

Data sent to receive path or data received from  $D_R$  input. Refer to bit MR(4) in "Control Register CR1" paragraph.

### **CONTROL REGISTER CR3**

Dx data transmitted. Refer to bit MX(3) in "Control Rgister CR1" paragraph.

### **CONTROL REGISTER CR4**

First byte of a READ or a WRITE instruction to Control Register CR4 is as shown in TABLE 1. Second byte is as shown in TABLE 6.

#### **Transmit Input Selection**

MIC1 or MIC2 source is selected with bit VS (7). Transmit input selected can be enabled or muted with bit TE (6).

Transmit gain can be adjusted within a 15 dB range in 1 dB step with Register CR5.

### Sidetone select

Bit "SI" (5) enables or disables Sidetone circuitry. When enabled, sidetone gain can be adjusted with Register (CR5). When Transmit path is disabled, bit TE set low, sidetone circuit is also disabled.

### **External Auxiliary signal select**

Bit "EE" (4) set to one connects EAIN input to the

loudspeaker amplifier input.

## **Ring/Tone signal routing**

Bits "RTL" (3) and RTE (2) provide select capability to connect on-chip Ring/Tone generator either to loudspeaker amplifier input or to earpiece amplifier input or both.

#### PCM receive data routing

Bits "SL" (1) and "SE" (0) provide select capability to connect received speech signal either to Loudspeaker amplifier input or to earpiece amplifier input or both.

#### **CONTROL REGISTER CR5**

First byte of a READ or a WRITE instuction to Control Register CR5 is as shown in TABLE 1. Second byte is as shown in TABLE 7.

#### **Transmit gain selection**

Transmit amplifier can be programmed for a gain from 0dB to 15dB in 1dB step with bits 4 to 7. 0 dBmO level at the output of the transmit amplifier (A reference point) is 0.739 Vrms (overload voltage is 1.06 Vrms).

#### Sidetone attenuation selection

Transmit signal picked up after the switched capacitor low pass filter may be fed back into the Receive Earpiece amplifier.

Attenuation of the signal at the output of the sidetone attenuator can be programmed from -8dB to -23dB relative to reference point A in 1 dB step with bits 0 to 3.

#### **CONTROL REGISTER CR6**

First byte of a READ or a WRITE instruction to Control Register CR6 is as shown in TABLE 1. Second byte is as shown in TABLE 8.

#### Earpiece amplifier gain selection:

Earpiece Receive gain can be programmed in 1 dB step from 0 dB to -15 dB relative to the maximum with bits 4 to 7.

0 dBmO voltage at the output of the amplifier on pins  $V_{Fr+}$  and  $V_{Fr-}$  is then 824.5 mVrms when 0dB gain is selected down to 146.6 mVrms when -15 dB gain is selected.

#### Loudspeaker amplifier gain selection:

Loudspeaker Receive amplifier gain can be programmed in 2 dB step from 0 dB to -30 dB relative to the maximum with bits 0 to 3.

0 dBmO voltage on the output of the amplifier on pins LS+ and LS- on 50  $\Omega$  is then 1.384 Vrms (3.91V<sub>pp</sub>) when 0 dB gain is selected down to 43.7 mVrms (123.6mV<sub>pp</sub>) when -30 dB gain is selected.

Current limitation is approximatively 150 mApk.

#### CONTROL REGISTER CR7:

First byte of a READ or a WRITE instruction to Control Register CR7 is as shown in TABLE 1. Second byte is as shown in TABLE 9.

#### Tone/Ring amplifier gain selection

Output level of Ring/Tone generator, before attenuation by programmable attenuator is 2.4 Vpkpk when f1 generator is selected alone or summed with the f2 generator and 1.9 Vpk-pk when f2 generator is selected alone.

Selected output level can be attenuated down to -27 dB by programmable attenutator by setting bits 4 to 7.

#### Frequency mode selection

Bits 'F1' (3) and 'F2' (2) permit selection of f1 and/or f2 frequency generator according to TA-BLE 9.

When f1 (or f2) is selected, output of the Ring/Tone is a squarewave (or a sinewave) signal at the frequency selected in the CR8 (or CR9) Register.

When f1 and f2 are selected in summed mode, output of the Ring/Tone generator is a signal where f1 and f2 frequency are summed.

In order to meet DTMF specifications, f2 output level is attenuated by 2dB relative to the f1 output level.

Frequency temporization must be controlled by the microcontroller.

Any switching between two frequencies of the same channel (f1 or f2) is done maintaining practically the phase continuity.

The actual change in the frequency of the tone generator takes place within 1/16th of the period of the highest of the two frequencies that are switched between, plus  $2\mu s$  for internal data acquisition.

#### **Waveform selection**

Bit 'SN' (1) selects waveform of the output of the Ring/Tone generator. Sinewave or squarewave signal can be selected.

#### **DTMF** selection

Bit DE (0) permits connection of Ring/Tone/DTMF generator on the Transmit Data path instead of the Transmit Amplifier output. Earpiece feed-back may be provided by sidetone circuitry by setting bit SI or directly by setting bit RTE in Register CR4. Loudspeaker feed-back may be provided directly by setting bit RTL in Register CR4.

#### **CONTROL REGISTERS CR8 AND CR9**

First byte of a READ or a WRITE instruction to

Control Register CR8 or CR9 is as shown in TA-BLE 1. Second byte is respectively as shown in TABLE 10 and 11.

Tone or Ring signal frequency value is defined by the formula:

f1 = CR8 / 0.128 Hz and f2 = CR9 / 0.128 Hz(with DFT = HFT = 0 in CR10)

where CR8 and CR9 are decimal equivalents of the binary values of the CR8 and CR9 registers respectively. Thus, any frequency between 7.8 Hz and 1992 Hz may be selected in 7.8 Hz step.

TABLE 13 gives examples for the main frequencies usual for Tone or Ring generation.

#### **CONTROL REGISTER CR10**

First byte of a READ or a WRITE instruction to control register CR10 is as shown in TABLE 1. Second byte is as shown in Table 12.

#### Extra +18dB in LS Gain

GLS = 1 sets extra 18dB Gain (total Gain = 27dB) GLS = 0 sets standard Gain = 9dB like on ST5080

#### Anticlipping enable, thresholds and time constants

ACE = 1 enables the operation of the Digital anticlipping section (D.A.S.), needed to avoid distortion on sine wave when GLS = 1 (extra 18dB on LS) anticlipping thresholds of -15, -13, -9 and -7dBmo are defined by bits 4 and 5 (VT1/VT0).

Gain recovery the constants (anticlipping release) are selectable among four values, 256ms, 128ms, 32ms and 16ms by bits 2 and 3 (FD1/FD0).

### **Doubled Tone/Ringer Frequency Range**

Double frequency range on tone & ringer generator is obtained by putting DFT = 1 (and HFT = 0). Formula for frequency generator is:

f1 = CR8/0.064Hz and f2 = CR9/0.064Hz.

Maximum frequency is 3984.4Hz and frequency accuracy is 15.6Hz.

#### Halved Tone/Ringer Frequency Range

Halved frequency and double accuracy on tone & ringer generator is obtained bu putting HFT = 1 (and DFT = 0).

Formula for frequency generator is:

f1 = CR8/0.256Hz and f1 = CR9/0.256Hz

Frequency range is from 3.9Hz to 996.1Hz and step is 3.9Hz with improved accuracy for low frequencies combination.

HFT = DFT= 1 is a forbidden combination.

20/33

| Description  | f1 value (decimal) | Theoric value (Hz) | Typical value (Hz) | Error % |