# ICs for Consumer Electronics

TVTEXT 8-Bit Microcontroller, ROMless-Version:

SDA 5250

TVTEXT 8-Bit Microcontroller, ROM-Versions:

SDA 5251

SDA 5252

SDA 5254

SDA 5255

| SDA 525x<br>Revision History:    |                                 | Current Version: 1998-04-08                             |

|----------------------------------|---------------------------------|---------------------------------------------------------|

| Previous Ver                     | sion:                           | User's Manual 06.97                                     |

| Page<br>(in previous<br>Version) | Page<br>(in current<br>Version) | Subjects (major changes since last revision)            |

|                                  |                                 | The layout of the document has been completely updated. |

|                                  |                                 |                                                         |

#### Edition 1998-04-08

Published by Siemens AG, Bereich Halbleiter, Marketing-Kommunikation, Balanstraße 73, 81541 München

© Siemens AG 1998.

All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### **Packing**

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

## **SIEMENS**

| Table of            | Contents                                        | Page |

|---------------------|-------------------------------------------------|------|

| 1                   | General Description                             | 5    |

| 2                   | Features                                        | 5    |

| 3                   | Block Diagram                                   |      |

| 4                   | Pin Configurations                              |      |

| <del>4</del><br>4.1 | Pin Configuration P-MQFP-80-1 (ROMless-Version) |      |

| 4.1                 | Pin Configuration P-SDIP-52-1 (ROM-Versions)    |      |

| 4.2<br>4.3          | Pin Configuration P-MQFP-64-1 (ROM-Versions)    |      |

| 4.4                 | Pin Configuration P-LCC-84-2 (Emulator-Version) |      |

| 5                   | Pin Functions (ROM- and ROMless-Version)        |      |

| ວ                   | •                                               |      |

| 6                   | Functional Description                          |      |

| 6.1                 | Acquisition                                     | 16   |

| 6.1.1               | TTX/VPS Slicer                                  | 16   |

| 6.1.2               | Acquisition Hardware                            | 16   |

| 6.1.3               | Memory Interface                                | 17   |

| 6.1.4               | Acquisition Control Registers                   | 18   |

| 6.2                 | Display Generator                               |      |

| 6.2.1               | Display Format and Timing                       | 20   |

| 6.2.2               | Display Cursor                                  | 20   |

| 6.2.3               | Flash                                           | 20   |

| 6.2.4               | Full Screen Background Colour                   | 20   |

| 6.2.5               | Clear Page Logic                                | 20   |

| 6.2.6               | Display Page Addressing                         |      |

| 6.2.7               | Character Generator                             |      |

| 6.2.8               | On Screen Display (OSD)                         |      |

| 6.2.9               | Display Special Function Registers              | 24   |

| 6.2.10              | Sandcastle Decoder                              |      |

| 6.3                 | Microcontroller                                 |      |

| 6.3.1               | Architecture                                    |      |

| 6.3.1.1             | CPU-Hardware                                    |      |

| 6.3.1.2             | CPU-Timing                                      | 46   |

| 6.3.1.3             | Addressing Modes                                | 47   |

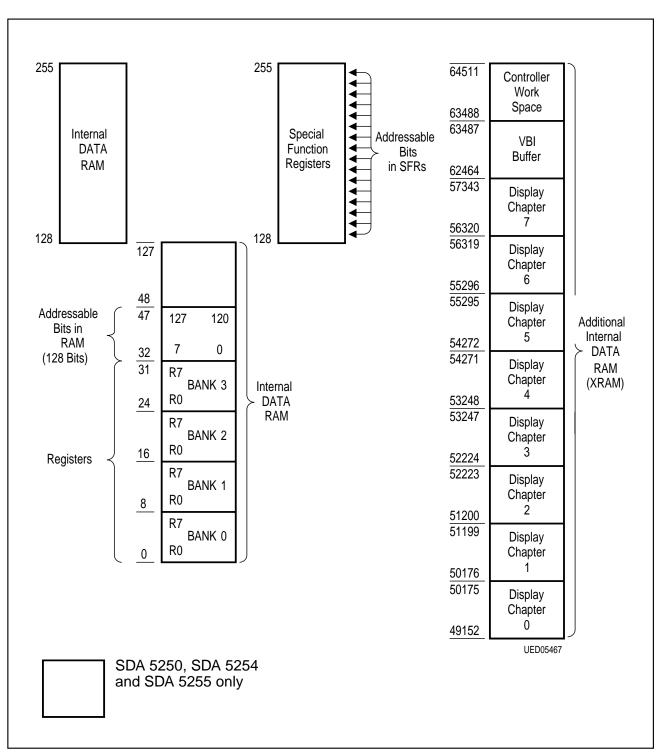

| 6.3.2               | Memory Organization                             | 49   |

| 6.3.2.1             | Program Memory                                  | 49   |

| 6.3.2.2             | Internal Data RAM                               | 55   |

| 6.3.2.3             | Special Function Registers                      | 56   |

| 6.3.3               | Interrupt System                                |      |

| 6.3.3.1             | Interrupt Sources                               | 62   |

| 6.3.4               | Interrupt Control                               | 63   |

| 6.3.4.1             | Interrupt Nesting                               | 71   |

# **SIEMENS**

| Table of | Contents                                 | Page |

|----------|------------------------------------------|------|

| 6.3.4.2  | External Interrupts                      | 72   |

| 6.3.4.3  | Interrupt Task Function                  |      |

| 6.3.4.4  | Response Time                            | 74   |

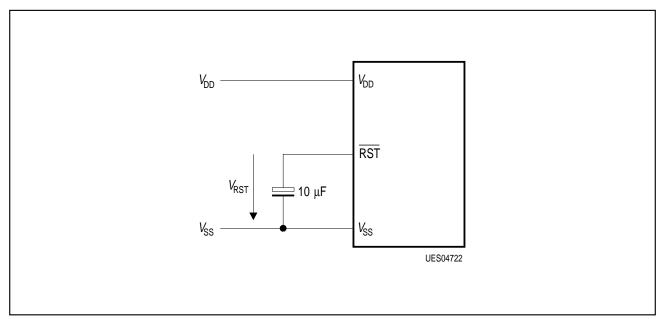

| 6.3.5    | Processor Reset and Initialization       | 75   |

| 6.3.6    | Ports and I/O-Pins                       | 78   |

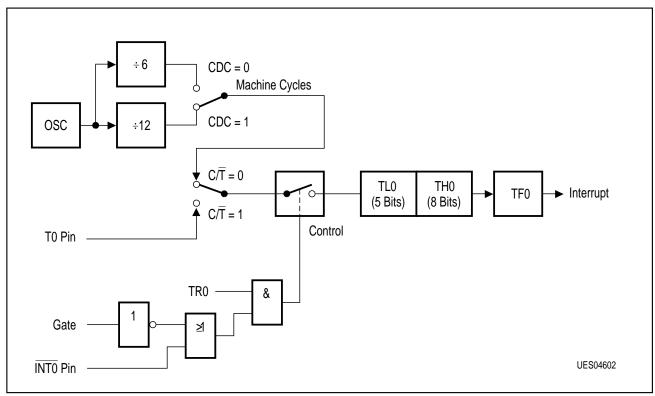

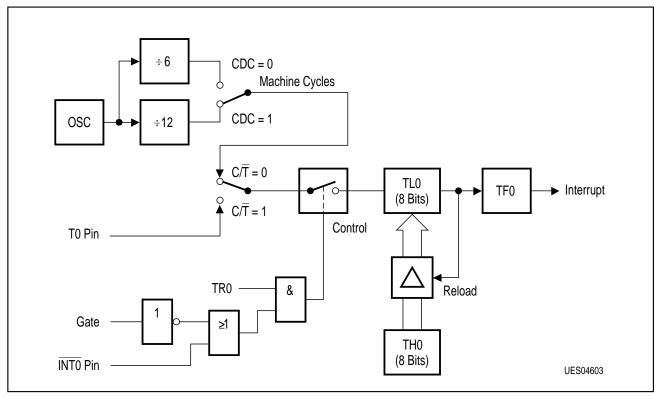

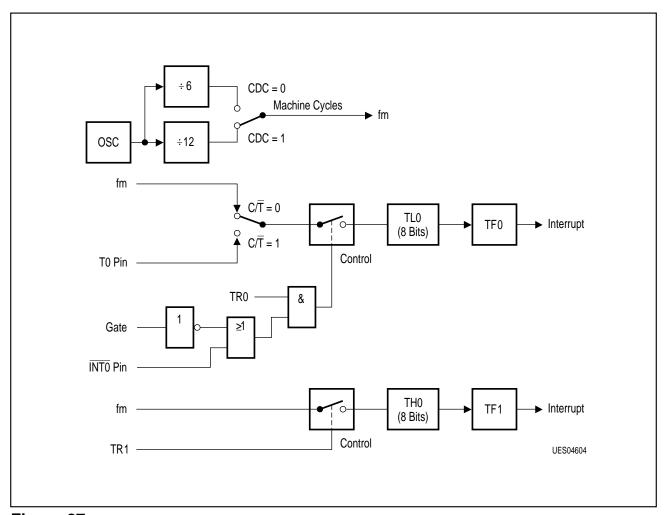

| 6.3.7    | General Purpose Timers/Counters          | 80   |

| 6.3.8    | Watchdog Timer                           | 87   |

| 6.3.9    | Capture Compare Timer                    | 90   |

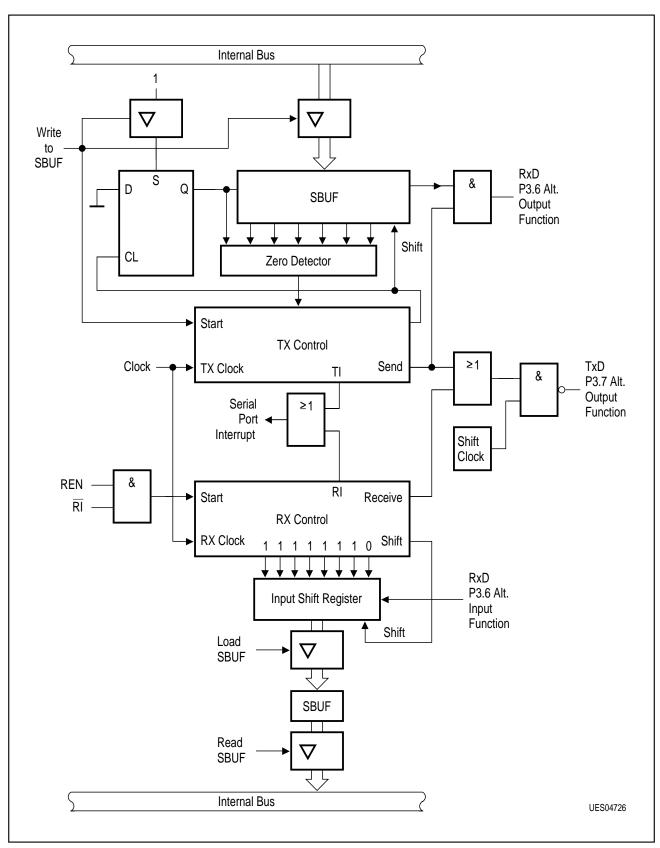

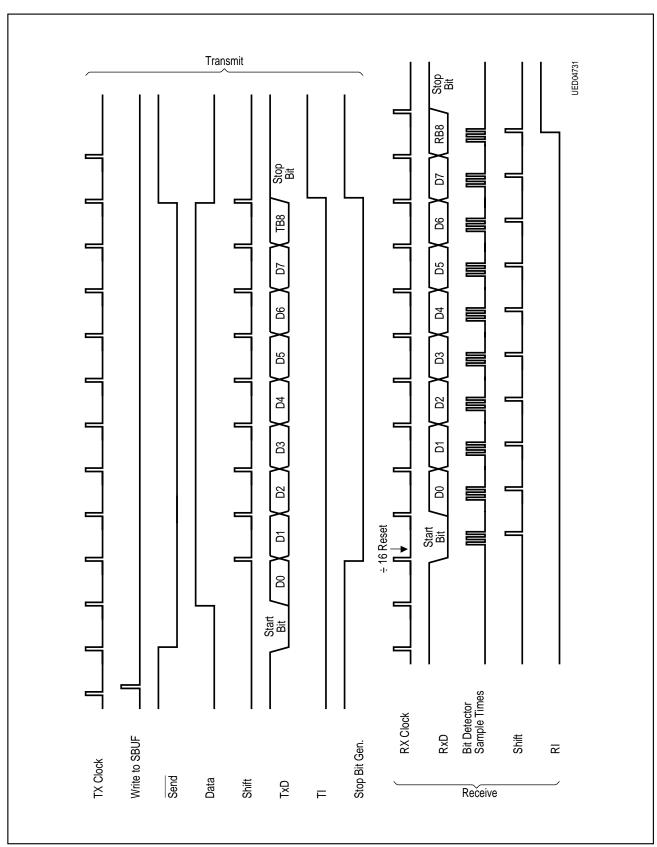

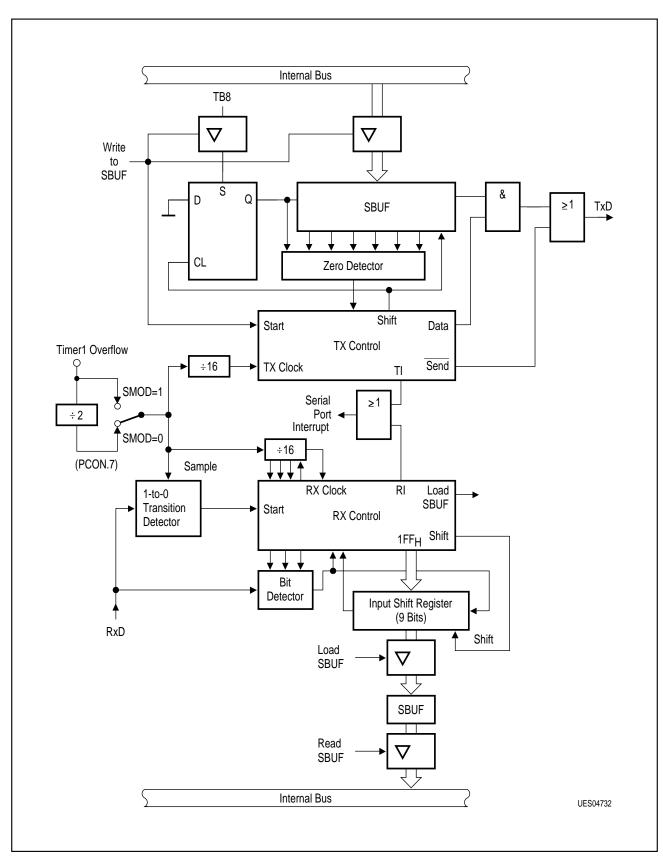

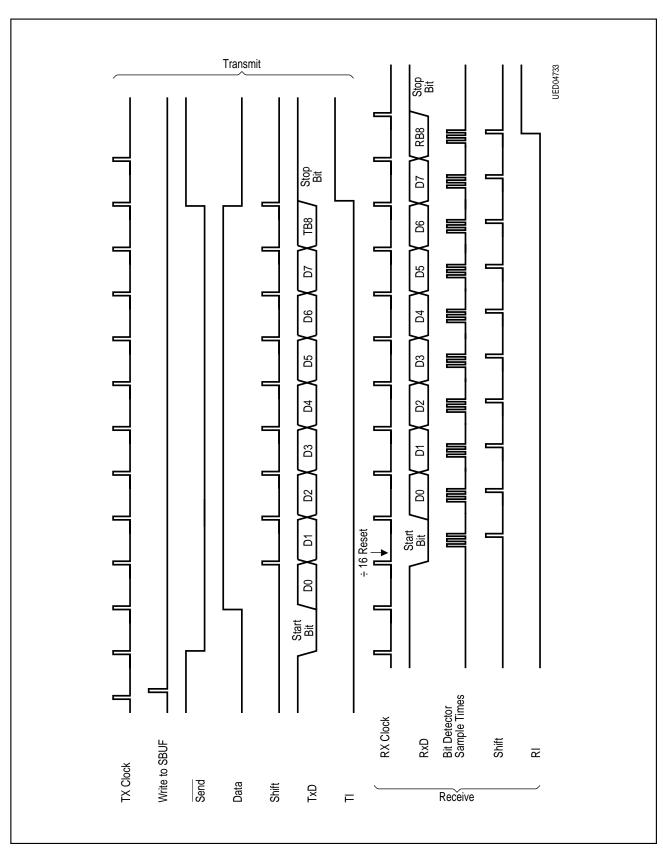

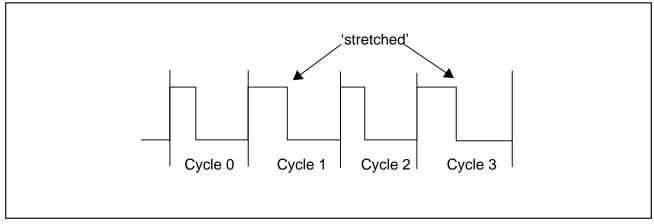

| 6.3.10   | Serial Interface                         | 91   |

| 6.3.10.1 | Multiprocessor Communication             | 93   |

| 6.3.10.2 | Baud Rates                               | 94   |

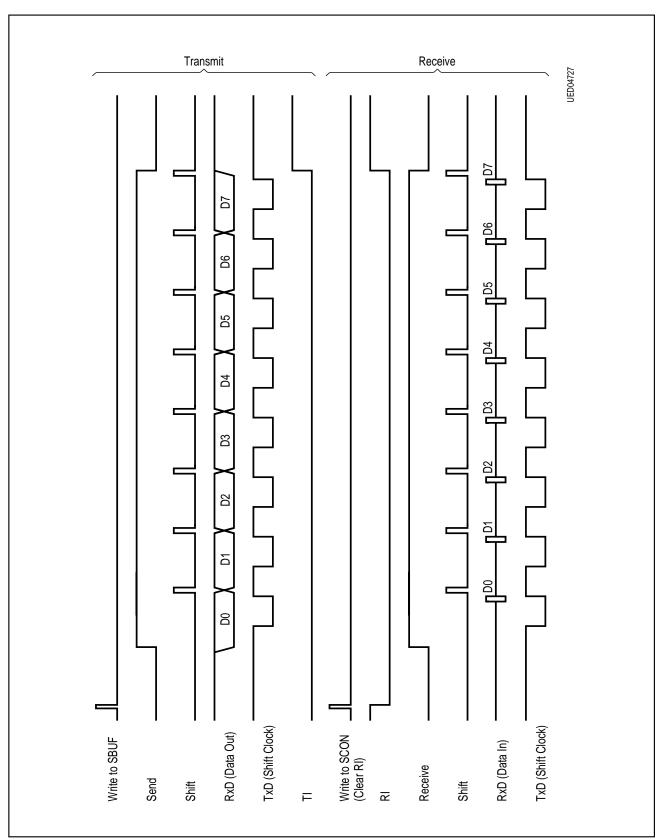

| 6.3.10.3 | More about Mode 0                        | 95   |

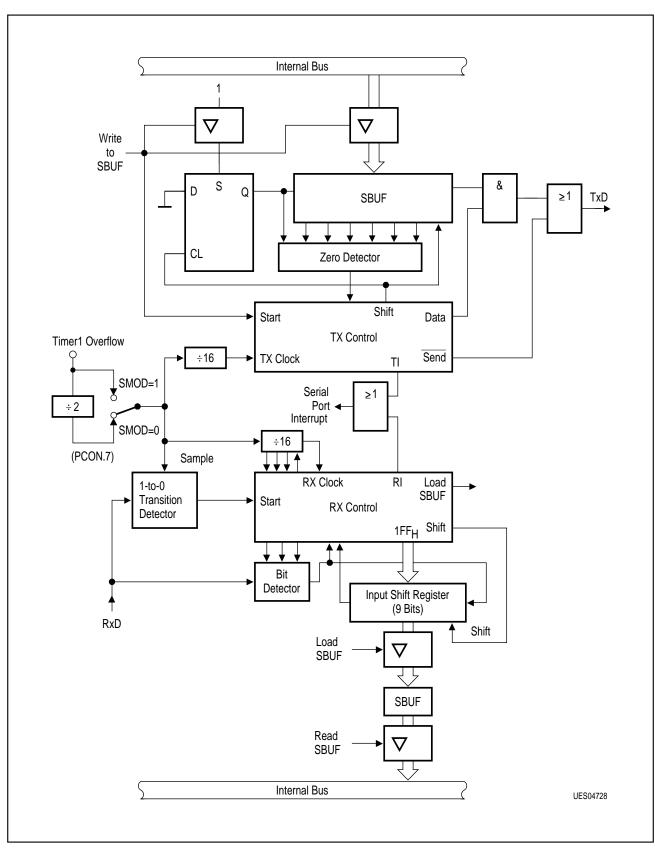

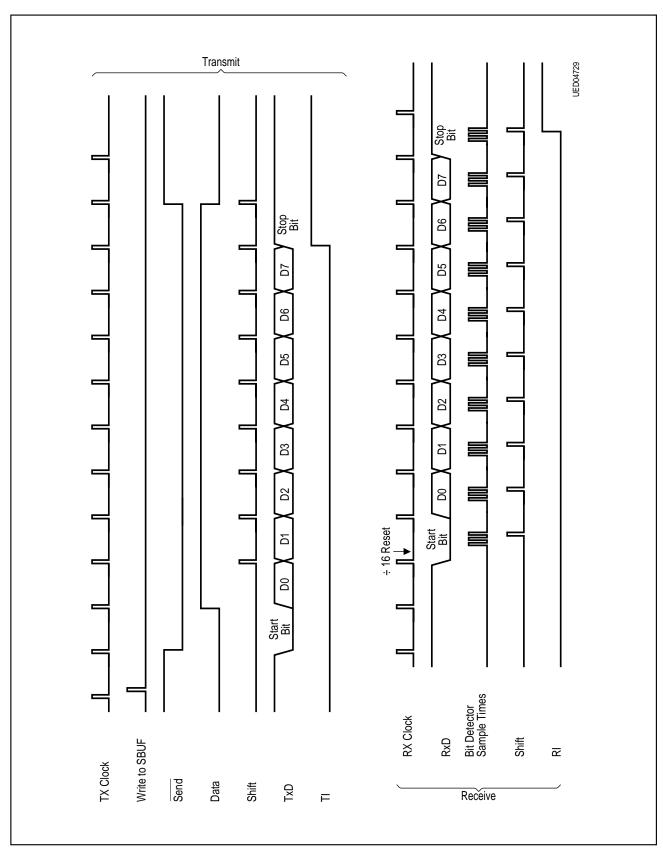

| 6.3.10.4 | More about Mode 1                        |      |

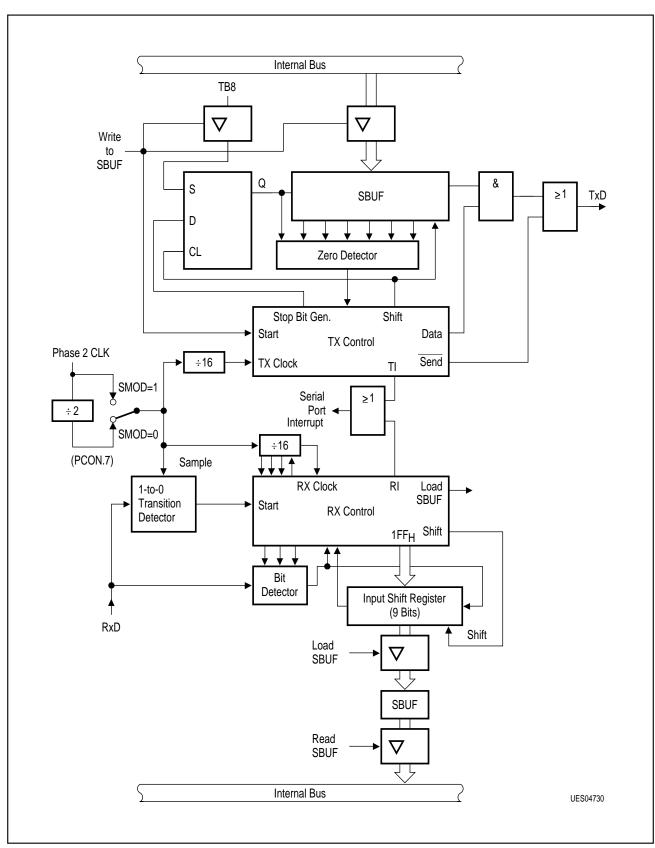

| 6.3.10.5 | More about Modes 2 and 3                 | 96   |

| 6.3.11   | Pulse Width Modulation Unit (PWM)        | 106  |

| 6.3.12   | Analog Digital Converter                 | 112  |

| 6.3.13   | Advanced Function Register               | 115  |

| 6.3.14   | Instruction Set                          |      |

| 6.3.14.1 | Notes on Data Addressing Modes           |      |

| 6.3.14.2 | Notes on Program Addressing Modes        | 116  |

| 6.3.14.3 | Instruction Set Description              |      |

| 6.3.15   | Instruction Opcodes in Hexadecimal Order | 122  |

| 7        | Electrical Characteristics               | 129  |

| 7.1      | Absolute Maximum Ratings                 | 129  |

| 7.2      | DC-Characteristics                       |      |

| 7.3      | AC-Characteristics                       | 131  |

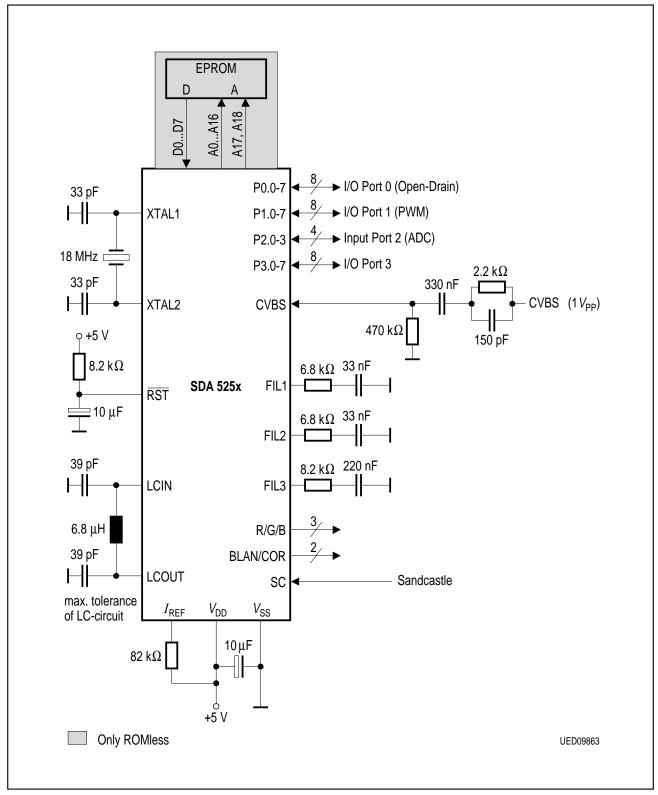

| 8        | Applications                             | 136  |

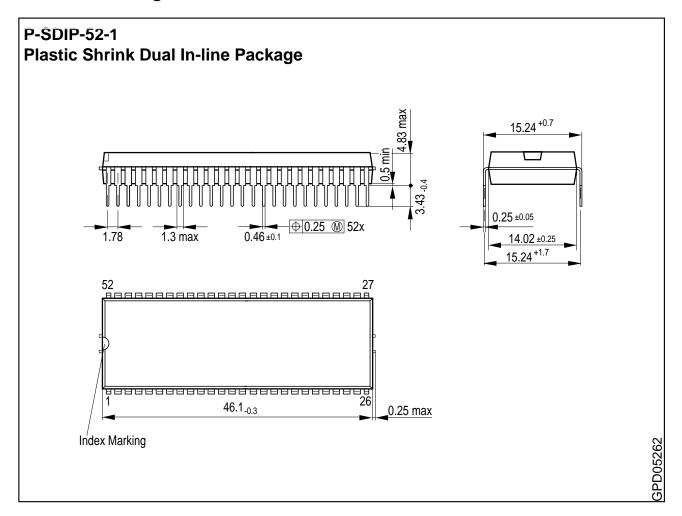

| 9        | Package Outlines                         | 137  |

| 10       | Index                                    | 141  |

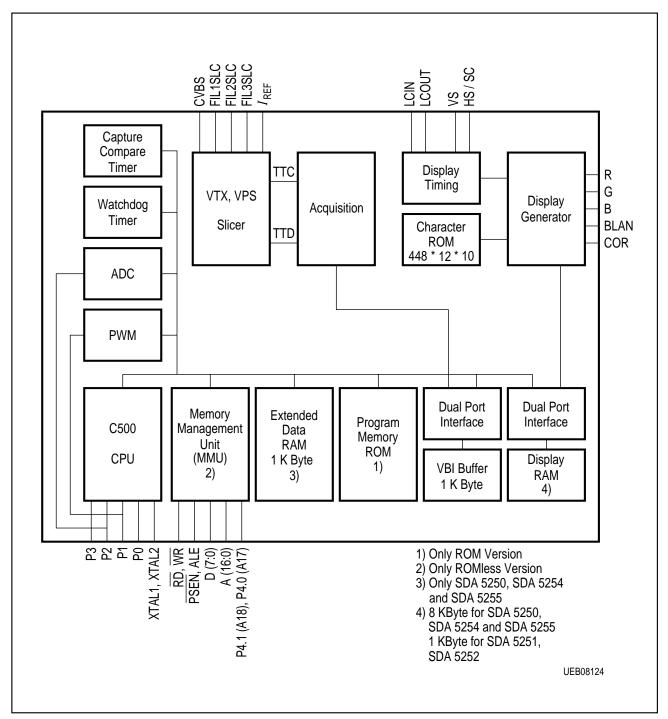

#### 1 General Description

The SDA 525x contains a slicer for TTX, VPS and WSS, an accelerating acquisition hardware modul, a display generator for "Level 1" TTX data and an 8 bit microcontroller running at 333 ns cycle time. The controller with dedicated hardware guarantees flexibility, does most of the internal processing of TTX acquisition, transfers data to/from the external memory interface and receives/transmits data via I<sup>2</sup>C and UART user interfaces. The block diagram shows the internal organization of the SDA 525x. The Slicer combined with dedicated hardware stores TTX data in a VBI buffer of 1 Kbyte. The microcontroller firmware does the total acquisition task (hamming- and parity-checks, page search and evaluation of header control bits) once per field.

#### 2 Features

#### **Acquisition**

- Feature selection via special function register

- Simultaneous reception of TTX, VPS and WSS

- Fixed framing code for VPS and TTX

- Acquisition during VBI

- Direct access to VBI RAM buffer

- Acquisition of packets X/26, X/27, 8/30 (firmware)

- Assistance of all relevant checks (firmware)

- 1-bit framing code error tolerance (switchable)

#### **Display**

- Features selectable via special function register

- 50/60 Hz display

- Level 1 serial attribute display pages

- Blanking and contrast reduction output

- 8 direct addressable display pages for SDA 5250, SDA 5254 and SDA 5255

- 1 direct addressable display page for SDA 5251 and SDA 5252

- 12 × 10 character matrix

- 96 character ROM (standard G0 character set)

- 143 national option characters for 11 languages

- 288 characters for X/26 display

- 64 block mosaic graphic characters

- 32 characters for OSD in expanded character ROM + 32 characters inside OSD box

- Conceal/reveal

- Transparent foreground/background inside/outside of a box

- Contrast reduction inside/outside of a box

- Cursor (colour changes from foreground to background colour)

- Flash (flash rate 1s)

- Programmable horizontal and vertical sync delay

- · Full screen background colour in outer screen

- Double size / double width / double height characters

#### **Synchronization**

- Display synchronization to sandcastle or Horizontal Sync (HS) and Vertical Sync (VS) with start-stop-oscillator

- Independent clock systems for acquisition, display and controller

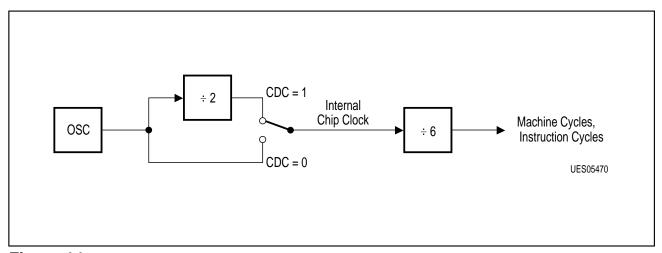

#### Microcontroller

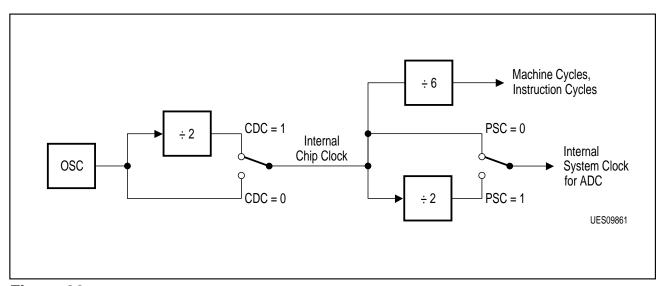

- 8 bit C500-CPU (8051 compatible)

- 18 MHz internal clock

- 0.33 µs instruction cycle

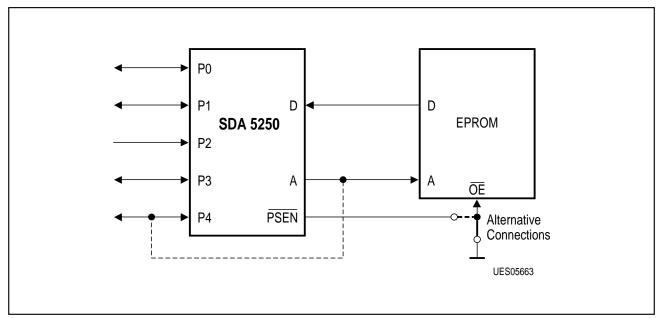

- Parallel 8-bit data and 16...19 bit address bus (ROMless-Version)

- Eight 16-bit data pointer registers (DPTR)

- Two 16-bit timers

- Watchdog timer

- Capture compare timer for infrared remote control decoding

- Serial interface (UART)

- 256 bytes on-chip RAM

- 8 Kbyte on-chip display-RAM (access via MOVX) for SDA 5250, SDA 5254 and SDA 5255

- 1 Kbyte on-chip display-RAM (access via MOVX) for SDA 5251 and SDA 5252

- 1 Kbyte on-chip TVT/VPS-Acquisition-buffer-RAM (access via MOVX)

- 1 Kbyte on-chip extended-RAM (access via MOVX) for SDA 5250, SDA 5254 and SDA 5255

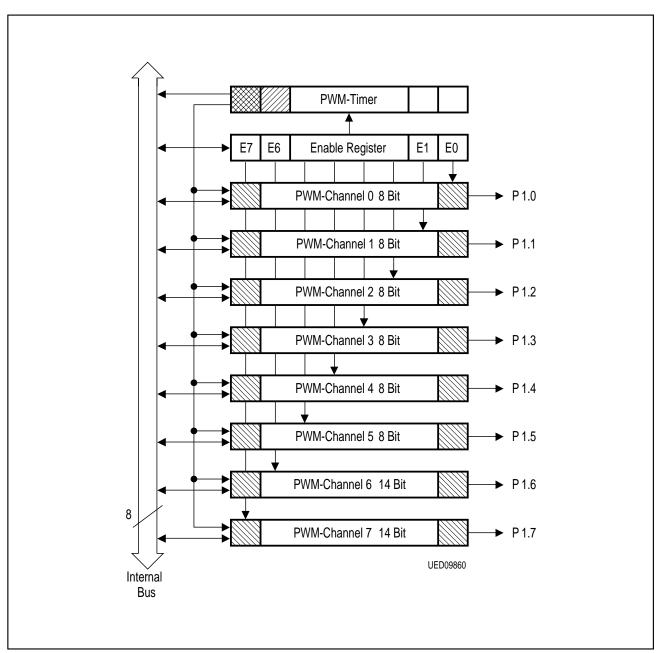

- 6 channel 8-bit pulse width modulation unit

- 2 channel 14-bit pulse width modulation unit

- 4 multiplexed ADC inputs with 8-bit resolution

- One 8-bit I/O port with open drain output and optional I<sup>2</sup>C-Bus emulation (PORT 0)

- Two 8-bit multifunctional I/O ports (PORT 1, PORT 3)

- One 4-bit port working as digital or analog inputs (PORT 2)

- One 2-bit I/O port with optional functions

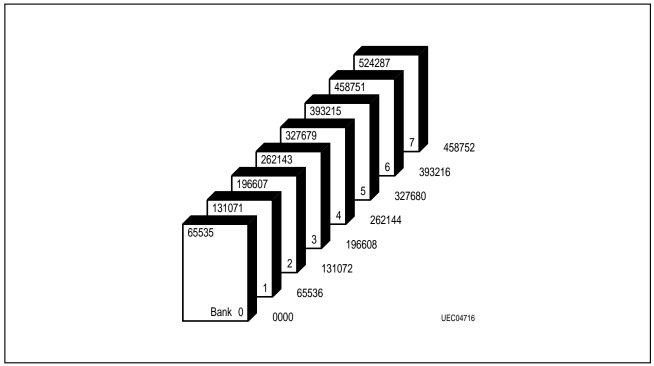

- One 3-bit I/O port with optional RAM/ROM address expansion up to 512 Kbyte (ROMless-Version)

- P-SDIP-52-1 Package or P-MQFP-64-1 for ROM-Versions (SDA 5251, SDA 5252, SDA 5254, SDA 5255)

- P-MQFP-80-1 Package for ROMless-Version (SDA 5250 M)

- P-LCC-84-2 Package for Emulator-Version (SDA 5250)

- 5 V Supply Voltage

## 3 Block Diagram

Figure 1 Block Diagram

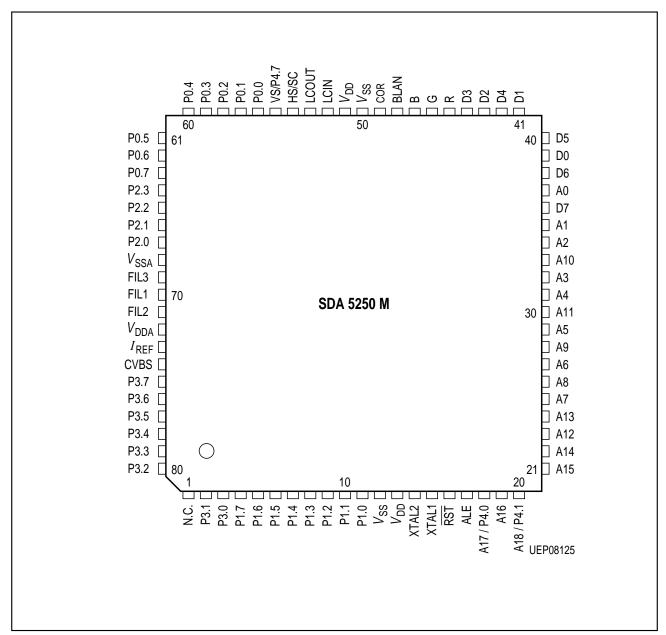

## 4 Pin Configurations

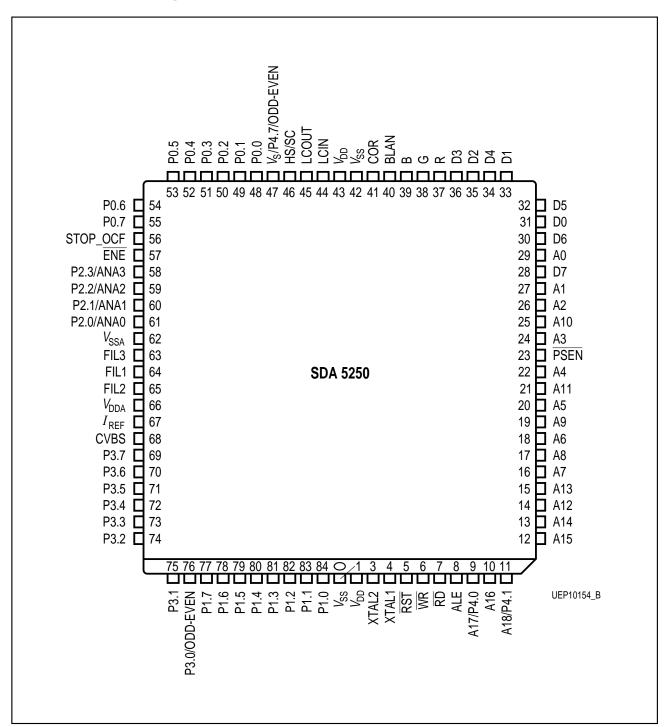

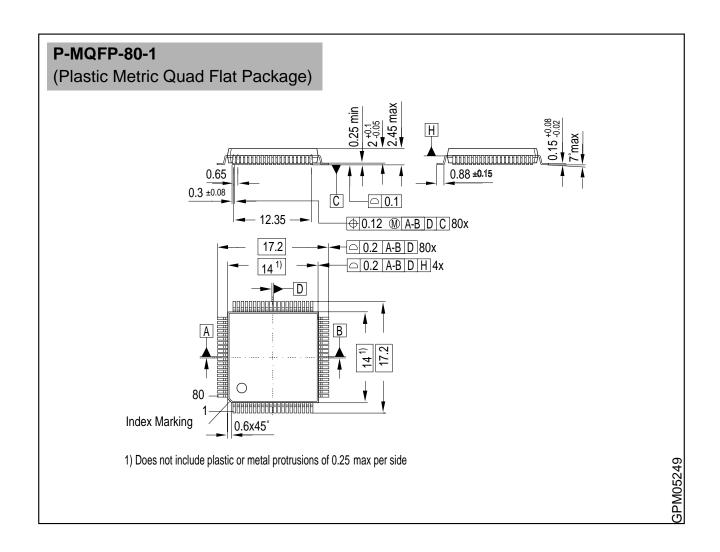

## 4.1 Pin Configuration P-MQFP-80-1 (ROMless-Version)

Figure 2

Pin Configuration P-MQFP-80-1 (ROMless-Version)

(top view)

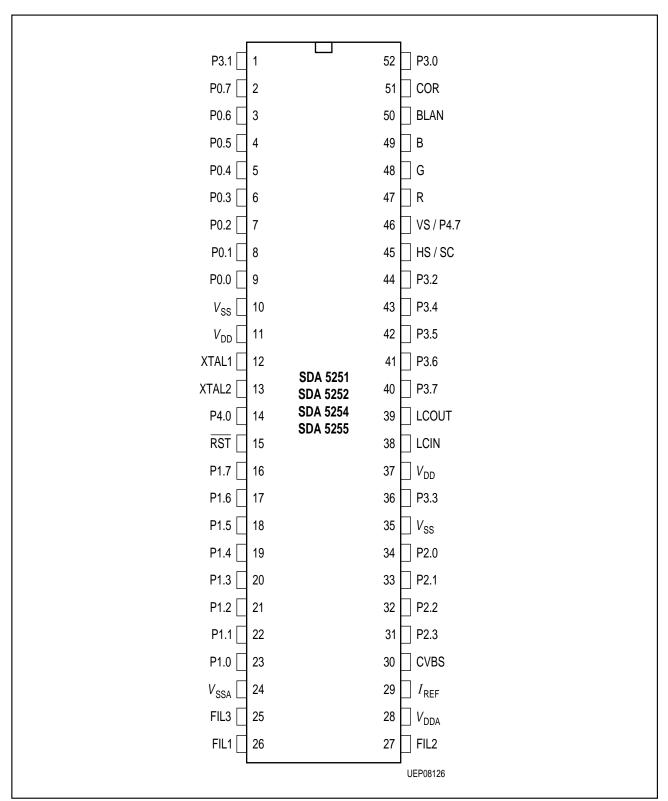

## 4.2 Pin Configuration P-SDIP-52-1 (ROM-Versions)

Figure 3

Pin Configuration P-SDIP-52-1 (ROM-Versions)

(top view)

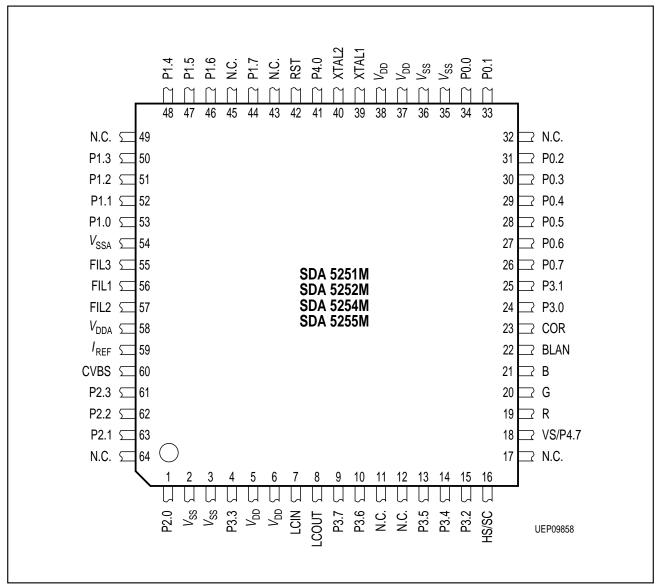

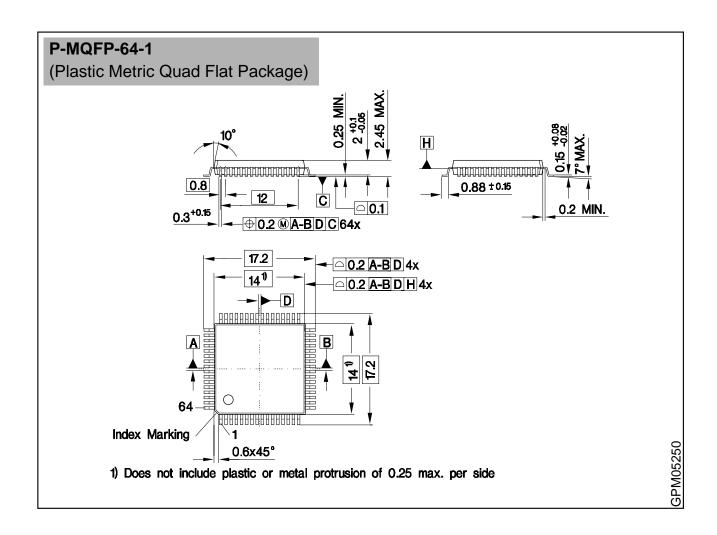

## 4.3 Pin Configuration P-MQFP-64-1 (ROM-Versions)

Figure 4

Pin Configuration P-MQFP-64-1 (ROM-Versions)

(top view)

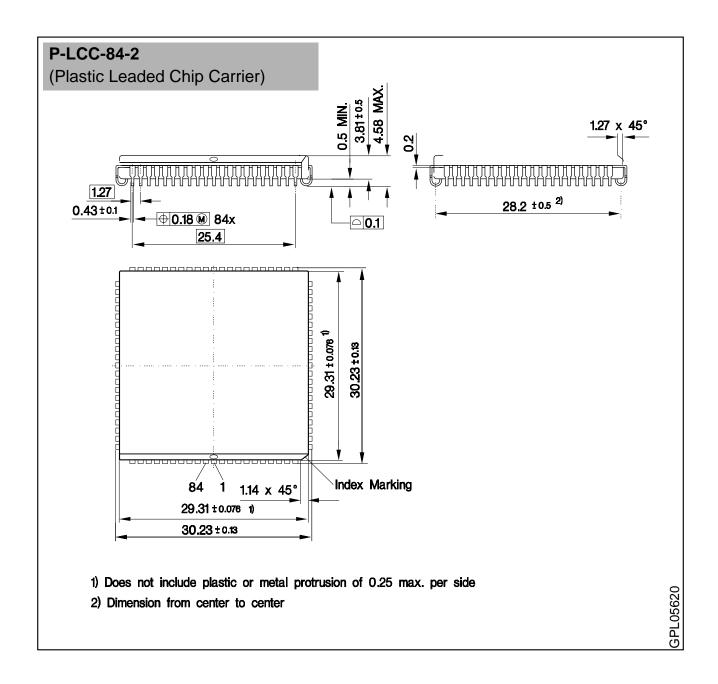

#### 4.4 Pin Configuration P-LCC-84-2 (Emulator-Version)

Figure 5

Pin Configuration P-LCC-84-2 (Emulator-Version)

(top view)

## 5 Pin Functions (ROM- and ROMless-Version)

Table 1

Pin Functions (ROM- and ROMless-Version)

| Symbol                                                       | Pin No.<br>P-SDIP-<br>52-1                   | Pin No.<br>P-MQFP-<br>64-1                   | Pin No.<br>P-MQFP-<br>80-1                   | Pin No.<br>P-LCC-84-<br>2                    | Input (I)<br>Output (O)<br>Supply (S)         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0.0<br>P0.1<br>P0.2<br>P0.3<br>P0.4<br>P0.5<br>P0.6<br>P0.7 | 9<br>8<br>7<br>6<br>5<br>4<br>3              | 34<br>33<br>31<br>30<br>29<br>28<br>27<br>26 | 56<br>57<br>58<br>59<br>60<br>61<br>62<br>63 | 48<br>49<br>50<br>51<br>52<br>53<br>54<br>55 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | Port 0 is an 8-bit open drain bidirectional I/O port. Port 0 pins that have 1s written to them float; in this state they can be used as high-impedance inputs (e.g. for software driven I <sup>2</sup> C Bus).                                                                                                                                                                                                                                                           |

| P1.0<br>P1.1<br>P1.2<br>P1.3<br>P1.4<br>P1.5<br>P1.6<br>P1.7 | 23<br>22<br>21<br>20<br>19<br>18<br>17<br>16 | 53<br>52<br>51<br>50<br>48<br>47<br>46<br>44 | 11<br>10<br>9<br>8<br>7<br>6<br>5<br>4       | 84<br>83<br>82<br>81<br>80<br>79<br>78<br>77 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | Port 1 is an 8-bit bidirectional multifunctional I/O port with internal pullup resistors. Port 1 pins that have 1s written to them are pulled high by the internal pullup resistors and in that state can be used as inputs.  The secondary functions of port 1 pins are: Port bits P1.0 - P1.5 contain the 6 output channels of the 8-bit pulse width modulation unit. Port bits P1.6 - P1.7 contain the two output channels of the 14-bit pulse width modulation unit. |

| P2.0<br>P2.1<br>P2.2<br>P2.3                                 | 34<br>33<br>32<br>31                         | 1<br>63<br>62<br>61                          | 67<br>66<br>65<br>64                         | 61<br>60<br>59<br>58                         | <br> -<br> -<br> -                            | P2.0 - P2.3 are working as digital or analog inputs.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| XTAL2                                                        | 13                                           | 40                                           | 14                                           |                                              | 0                                             | Output of the inverting oscillator amplifier. To drive the device from an external clock source, XTAL1 should be driven, while XTAL2 is left open.                                                                                                                                                                                                                                                                                                                       |

| XTAL1 RST                                                    | 15                                           | 42                                           | 16                                           | 5                                            | I                                             | Input to the inverting oscillator amplifier  A low level on this pin resets the processor                                                                                                                                                                                                                                                                                                                                                                                |

Table 1

Pin Functions (ROM- and ROMless-Version) (cont'd)

| Symbol                                                                                     | Pin No.<br>P-SDIP-<br>52-1                                                | Pin No.<br>P-MQFP-<br>64-1                                               | Pin No.<br>P-MQFP-<br>80-1                                               | Pin No.<br>P-LCC-84-<br>2                                                  | Input (I)<br>Output (O)<br>Supply (S)   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\overline{V_{DD}}$                                                                        | 11, 37                                                                    | 5, 6,<br>37, 38                                                          | 13, 51                                                                   | 2, 43                                                                      | S                                       | Power supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $V_{\rm SS}$                                                                               | 10, 35                                                                    | 2, 3,<br>35, 36                                                          | 12, 50                                                                   | 1, 42                                                                      | S                                       | Ground (0 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| R<br>G<br>B<br>BLAN<br>COR<br>P3.0<br>P3.1<br>P3.2<br>P3.3<br>P3.4<br>P3.5<br>P3.6<br>P3.7 | 47<br>48<br>49<br>50<br>51<br>52<br>1<br>44<br>36<br>43<br>42<br>41<br>40 | 19<br>20<br>21<br>22<br>23<br>24<br>25<br>15<br>4<br>14<br>13<br>10<br>9 | 45<br>46<br>47<br>48<br>49<br>3<br>2<br>80<br>79<br>78<br>77<br>76<br>75 | 37<br>38<br>39<br>40<br>41<br>76<br>75<br>74<br>73<br>72<br>71<br>70<br>69 | O O O O O O I/O I/O I/O I/O I/O I/O I/O | Red colour signal output Blue colour signal output Blanking output Contrast Reduction output  Port 3 is an 8-bit bidirectional I/O port with internal pullup resistors. Port 3 pins that have 1s written to them are pulled high by the internal pullup resistors and in that state can be used as inputs. It also contains the interrupt, timer and serial port input pins. The output latch corresponding to a secondary function must be programmed to a one (1) for that function to operate. The secondary functions are assigned to the pins of port 3 as follows:  - INTO (P3.2): interrupt 0 input/timer 0 gate control input  - INT1 (P3.3): interrupt 1 input/timer 1 gate control input  - T0 (P3.4): counter 0 input  - T1 (P3.5): counter 1 input  - RXD(P3.6): serial port receive line  - TXT(P3.7): serial port transmit line  Attention: P3.6 must not be kept to '0' during reset, otherwise a special test mode will be activated. |

Table 1

Pin Functions (ROM- and ROMless-Version) (cont'd)

| Symbol               | Pin No.<br>P-SDIP-<br>52-1 | Pin No.<br>P-MQFP-<br>64-1 | Pin No.<br>P-MQFP-<br>80-1 | Pin No.<br>P-LCC-84-<br>2 | Input (I)<br>Output (O)<br>Supply (S) | Function                                                                                                                                                                                                                                                                  |

|----------------------|----------------------------|----------------------------|----------------------------|---------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HS/SC                | 45                         | 16                         | 54                         | 46                        | I                                     | Horizontal sync input (alternative sandcastle sync input) for display                                                                                                                                                                                                     |

| VS/P4.7              | 46                         | 18                         | 55                         | 47                        | I/O                                   | Vertical sync input for display (alternative Port 4.7)                                                                                                                                                                                                                    |

| CVBS                 | 30                         | 60                         | 74                         | 68                        | I                                     | CVBS (video signal) input                                                                                                                                                                                                                                                 |

| P4.0                 | 14                         | 41                         | 18                         | 9                         | I/O                                   | Port 4.0 is a bidirectional I/O port                                                                                                                                                                                                                                      |

| P4.1                 |                            | _                          | 20                         | 11                        | I/O                                   | with internal pullup resistors. Port 4 pins that have 1s written to them are pulled high by the internal pullup resistors and in that state can be used as inputs. Attention: P4.0 must not be kept to '0' during reset, otherwise a special test mode will be activated. |

| $I_{REF}$            | 29                         | 59                         | 73                         | 67                        | I                                     | Reference current input for slicer PLLS                                                                                                                                                                                                                                   |

| $\overline{V_{DDA}}$ | 28                         | 58                         | 72                         | 66                        | S                                     | Analog Supply Voltage for Slicer and ADC                                                                                                                                                                                                                                  |

| $V_{SSA}$            | 24                         | 54                         | 68                         | 62                        | S                                     | Analog Ground for Slicer and ADC                                                                                                                                                                                                                                          |

| FIL1                 | 26                         | 56                         | 70                         | 64                        | I/O                                   | PLL loop filter I/O for TTX slicing                                                                                                                                                                                                                                       |

| FIL2                 | 27                         | 57                         | 71                         | 65                        | I/O                                   | PLL loop filter I/O for VPS/WSS slicing                                                                                                                                                                                                                                   |

| FIL3                 | 25                         | 55                         | 69                         | 63                        | I/O                                   | PLL loop filter I/O for TTX/VPS/WSS data slicing                                                                                                                                                                                                                          |

| LCIN                 | 38                         | 7                          | 52                         | 44                        | I                                     | LCIN and LCOUT are used to                                                                                                                                                                                                                                                |

| LC-OUT               | 39                         | 8                          | 53                         | 45                        | О                                     | connect the external display dot clock frequency reference.                                                                                                                                                                                                               |

Table 2

Additional PINS for ROMless-Version

| Symbol   | Pin Nr.<br>P-MQFP-80-1 | Pin Nr.<br>P-LCC-84-2 | Input (I)<br>Output (O)<br>Supply (S) | Function                     |

|----------|------------------------|-----------------------|---------------------------------------|------------------------------|

| A0       | 37                     | 29                    | 0                                     | Address bus for external     |

| A1       | 35                     | 27                    | 0                                     | memory                       |

| A2       | 34                     | 26                    | 0                                     |                              |

| A3       | 32                     | 24                    | 0                                     |                              |

| A4       | 31                     | 22                    | 0                                     |                              |

| A5       | 29                     | 20                    | 0                                     |                              |

| A6       | 27                     | 18                    | 0                                     |                              |

| A7       | 25                     | 16                    | 0                                     |                              |

| A8       | 26                     | 17                    | 0                                     |                              |

| A9       | 28                     | 19                    | 0                                     |                              |

| A10      | 33                     | 25                    | 0                                     |                              |

| A11      | 30                     | 21                    | 0                                     |                              |

| A12      | 23                     | 14                    | 0                                     |                              |

| A13      | 24                     | 15                    | 0                                     |                              |

| A14      | 22                     | 13                    | 0                                     |                              |

| A15      | 21                     | 12                    | 0                                     |                              |

| A16      | 19                     | 10                    | 0                                     |                              |

| D0       | 39                     | 31                    | I/O                                   | Data bus for external memory |

| D1       | 41                     | 33                    | I/O                                   |                              |

| D2       | 43                     | 35                    | I/O                                   |                              |

| D3       | 44                     | 36                    | I/O                                   |                              |

| D4       | 42                     | 34                    | I/O                                   |                              |

| D5       | 40                     | 32                    | I/O                                   |                              |

| D6       | 38                     | 30                    | I/O                                   |                              |

| D7       | 36                     | 28                    | I/O                                   |                              |

| STOP_OCF | _                      | 56                    | I/O                                   | Control Signals for data     |

| ENE      | _                      | 57                    | 1                                     | memory extension and         |

| RD       | _                      | 7                     | 0                                     | emulation.                   |

| WR       | -                      | 6                     | 0                                     |                              |

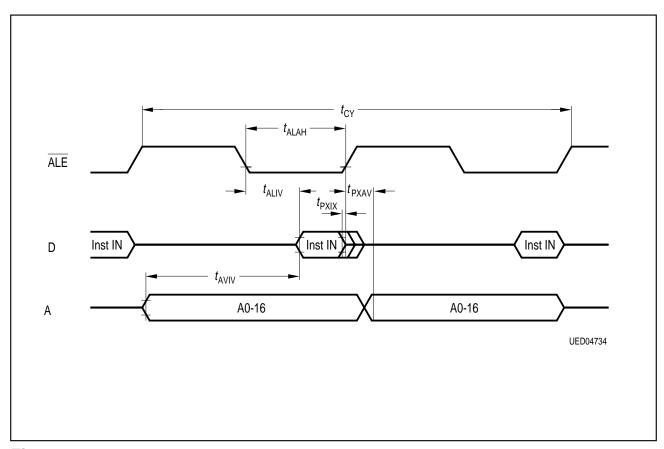

| ALE      | 17                     | 8                     | 0                                     |                              |

| PSEN     | _                      | 23                    | 0                                     |                              |

#### 6 Functional Description

#### 6.1 Acquisition

#### 6.1.1 TTX/VPS Slicer

The slicer extracts horizontal and vertical sync information and TTX data from the CVBS signal. The slicer includes an analog circuit for sync filtering and data slicing. Further there are two analog PLLs for system clock generation for both TTX and VPS. Therefore the slicer is able to receive both TTX and VPS in succeeding lines of a vertical blanking interval. A third data-PLL shifts the phase of the system clock for data sampling. The internal slicer timing signals are generated from the VPS-PLL.

## 6.1.2 Acquisition Hardware

The acquisition hardware transforms the sliced bit stream into a byte stream. A framing code check follows to identify a TTX or VPS line. If the framing code error tolerance is enabled then one-bit errors will be allowed.

For each line in the VBI in which a framingcode is detected, a maximum of 42 bytes (VPS: 26 bytes) plus a status word are stored in the VBI-buffer. After framing code detection a status word is generated which informs about the type of data received (TTX or VPS) and the signal quality of the TV channel. **Chapter "Acquisition Status Word" on page 17** shows the format of this status word. The horizontal and vertical windows in which TTX or VPS data are accepted and checked for framing code errors are generated automatically. The VBI buffer data will be analyzed (Hamming, parity and acquisition) by the microcontroller and stored in the dual port display RAM or the external RAM, if selected. This analysis is repeated for every field.

## **Acquisition Status Word**

| TTX/VPS  | FCER | FCOK         | LIN.4                                                                                                                                                                                                                                 | LIN.3                                                 | LIN.2               | LIN.1 | LIN.0 |  |  |  |

|----------|------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------|-------|-------|--|--|--|

| LIN.(40) |      |              | used to rea                                                                                                                                                                                                                           | n which dat<br>lize a "softw                          |                     |       |       |  |  |  |

| FCOK     |      | har<br>sto   | = Framing code OK (VPS or TTX). This bit is set always by hardware, because lines with valid framing codes are stored only. This bit is reset by software in VBI-buffer. If reset, it indicates that this line was already processed. |                                                       |                     |       |       |  |  |  |

| FCER     |      | erro         | <ul> <li>The framing code for TTX lines was accepted with 1-bit error. For VPS lines this bit has no meaning.</li> <li>For TTX lines the framing code E4<sub>H</sub> was detected.</li> </ul>                                         |                                                       |                     |       |       |  |  |  |

| TTX/VPS  |      | is $0 = A v$ | ocked to th<br>alid VPS fra                                                                                                                                                                                                           | aming code<br>e TTX frequ<br>aming code<br>e VPS freq | uency.<br>was detec |       |       |  |  |  |

## 6.1.3 Memory Interface

The acquisition dual port interface manages the VBI memory write access request from the acquisition hardware and an asynchronous memory access request from the microcontroller. The acquisition hardware delivers the address and data and then a request to the interface. The access of acquisition hardware and controller is under a special arbiter control. The end of data is indicated by the bit LIN24ST in SFR ACQSIR.

#### 6.1.4 Acquisition Control Registers

The following sections gives an overview about special function registers ACQMS\_1, ACQMS\_2 and ACQSIR, with which slicer and acquisition can be controlled:

## Acquisition Mode and Status Register ACQMS\_1

Acquisition Mode and Status ACQMS\_1 SFR-Address C1<sub>H</sub>

Register

Default after reset: 00<sub>H</sub>

(MSB) (LSB)

| 0 | 0 | VPSE | 0 | CRIC.1 | CRIC.0 | ENERT | TTXE |

|---|---|------|---|--------|--------|-------|------|

|---|---|------|---|--------|--------|-------|------|

TTXE 1: enable TTX in lines 6 - 22

**ENERT** 1: allow 1 bit error for TTX

CRIC.1 ... CRIC.0 00: The CRI is not included in FRC

01: last 2 bits of CRI are included in the FRC10: last 4 bits of CRI are included in the FRC11: last 8 bits of CRI are included in the FRC

**VPSE** 1: enable VPS in line 16. Text-reception in this line is

automatically disabled

**Comments** Bits 4, 6 and 7 are not defined, must be set to 0

Acquisition Mode and Status Register ACQMS\_2

Acquisition Mode and Status ACQMS\_2 SFR-Address C2<sub>H</sub>

Register

Default after reset: 00<sub>H</sub>

(MSB) (LSB)

| TEST.7 | TEST.6 | TEST.5 | TEST.4 | TEST.3 | TEST.2 | TEST.1 | TEST.0 |

|--------|--------|--------|--------|--------|--------|--------|--------|

|        |        |        |        |        |        |        |        |

**Comments** all bits have to be set to 0. Setting any of these bits will switch

on special slicer test modes for production test

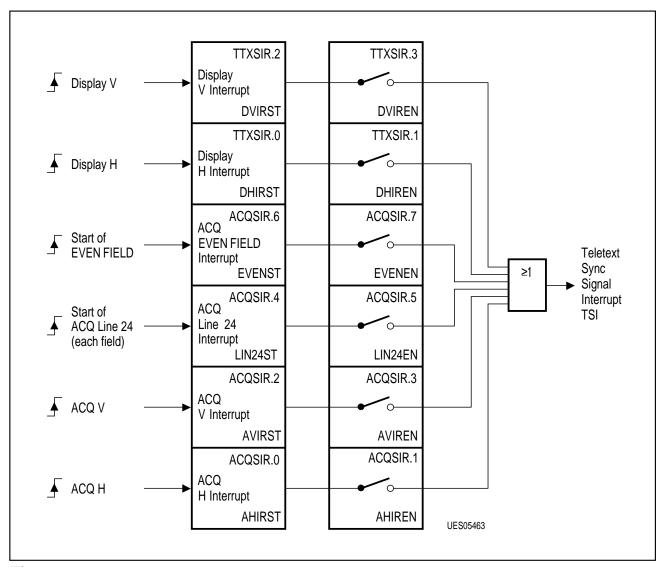

## **Acquisition-Sync-Interrupt-Register ACQSIR**

Acquisition-Sync-Interrupt- ACQSIR SFR-Address CO<sub>H</sub>

Register

Default after reset: 00<sub>H</sub>

(MSB) (LSB)

| ,        |        |          |                                                                                                                                                    |               |                  |             | ` ,       |  |  |

|----------|--------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------|-------------|-----------|--|--|

| EVENEN   | EVENST | LIN24EN  | LIN24ST                                                                                                                                            | AVIREN        | AVIRST           | AHIREN      | AHIRST    |  |  |

|          |        |          |                                                                                                                                                    |               |                  |             |           |  |  |

| AHIRST   |        |          | uisition hor                                                                                                                                       | •             | •                | •           |           |  |  |

|          |        | by t     | the positive                                                                                                                                       | edge of H     | S. It must b     | e reset by  | software. |  |  |

| AHIREN   |        | 1 = ena  | able acquisi                                                                                                                                       | ition horizo  | ntal sync in     | terrupt req | uest.     |  |  |

| AVIRST   |        |          | <ul> <li>1 = acquisition vertical sync interrupt request. This bit is set by<br/>the positive edge of VS. It must be reset by software.</li> </ul> |               |                  |             |           |  |  |

| AVIREN   |        |          | ·<br>able acquisi                                                                                                                                  | Ŭ             |                  | •           |           |  |  |

| AVIIVEIN |        | 1 – 6116 | able acquisi                                                                                                                                       | ilion vertica | ii syric ii ilei | rupt reque  | 3ί.       |  |  |

| LIN24ST  |        |          | uisition line                                                                                                                                      | •             | •                | •           |           |  |  |

1 = acquisition line 24 interrupt request. Acquisition hardware processing in VBI interval is finished. This bit assists the synchronization of acquisition software to the ACQ-Timing. It is set by hardware at the beginning of line 24 and the corresponding line of 2nd field. It is reset by software.

**LIN24EN** 1 = enable acquisition line 24 interrupt request.

**EVENST** 1 = even field interrupt. Must be reset by software.

**EVENEN** 1 = enable even field interrupt requests.

**Comments** None

## 6.2 Display Generator

The display features of SDA525x are similar to the Siemens SDA5248 TTX controller. The display generator reads character addresses and control characters from the display memory, selects the pixel information from the character ROM and translates it into RGB values corresponding to the World Standard Teletext Norm. The national option character bits for 11 languages inclusive X/26 characters are also supported.

## 6.2.1 Display Format and Timing

A page consists of 25 rows of 40 characters each. One character covers a matrix of 12 horizontal and 10 vertical pixels. The pixel frequency should be 12 MHz corresponding to 1  $\mu$ s for one character and 40  $\mu$ s for one row. A total of 250 TV lines are used for TTX display. The display can be shifted horizontally from 0  $\mu$ s to 21.33  $\mu$ s with respect to HS and vertically from line 1 (314) to line 64 (377) with respect to VS. The display position is determined by the registers DHD and DVD.

Note: To avoid interferences between the subharmonics of the 18 MHz controller clock and the 12 MHz pixel clock, a pixel clock of about 11,5 MHz is recommended.

#### 6.2.2 Display Cursor

A cursor is available which changes foreground to background colour for one character. Cursor flash can be realized via software enabling/disabling the cursor. The cursor position is defined by cursor position registers DCRP and DCCP.

#### 6.2.3 Flash

A character background flash (character is changed to background colour) is realized by hardware. The flash frequency is 1 Hz with a duty cycle of 32:18.

#### 6.2.4 Full Screen Background Colour

The SDA 525x delivers the new full screen background colour feature. Special function register SFR DTIM(7-5) includes three bits which define the default background colour for the inner and outer screen area.

#### 6.2.5 Clear Page Logic

The clear page logic generates a signal which is interpreted by the character generator to identify non displayable rows. In row 25 specific information is stored by the microcontroller indicating which of the rows 0 - 24 should be interpreted as erased during character generation. At the beginning of each row the special control characters are read from the display memory (see **Table 3**).

Table 3

Clear Page Bits

| row 25 /column: | D7               | D6               | D5               | D4               | D3               | D2               | D1               | D0               |

|-----------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| 0               | ER <sub>7</sub>  | ER <sub>6</sub>  | ER <sub>5</sub>  | ER <sub>4</sub>  | ER <sub>3</sub>  | ER <sub>2</sub>  | ER <sub>1</sub>  | ER <sub>0</sub>  |

| 1               | ER <sub>15</sub> | ER <sub>14</sub> | ER <sub>13</sub> | ER <sub>12</sub> | ER <sub>11</sub> | ER <sub>10</sub> | ER <sub>9</sub>  | ER <sub>8</sub>  |

| 2               | ER <sub>23</sub> | ER <sub>22</sub> | ER <sub>21</sub> | ER <sub>20</sub> | ER <sub>19</sub> | ER <sub>18</sub> | ER <sub>17</sub> | ER <sub>16</sub> |

| 3               | 0                | 0                | 0                | 0                | 0                | 0                | 0                | ER <sub>24</sub> |

$ER_{24}...ER_0 = 1$ : row is interpreted as a blanked row

$ER_{24}...ER_0 = 0$ : row is received and displayed

#### 6.2.6 Display Page Addressing

The display generator hardware generates a row/column address for the display memory. Because there is a binary to row/column address translation between display generator and memory, the OSD programmer has to take care of this. The relationship between row/column and binary address in memory is shown in **Table 4**.

Table 4

Row/Column to Binary Translation Table

|       | C0               |     | C31              | C32              | ••• | C39              |

|-------|------------------|-----|------------------|------------------|-----|------------------|

| Row0  | 00 <sub>H</sub>  |     | 1F <sub>H</sub>  | 3F8 <sub>H</sub> |     | 3FF <sub>H</sub> |

| Row1  | 20 <sub>H</sub>  |     | 3F <sub>H</sub>  | 3F0 <sub>H</sub> |     | 3F7 <sub>H</sub> |

| :     | :                | i : | :                | :                | :   | :                |

| Row23 | 2E0 <sub>H</sub> |     | 2FF <sub>H</sub> | 340 <sub>H</sub> |     | 347 <sub>H</sub> |

| Row24 | 300 <sub>H</sub> |     | 31F <sub>H</sub> | 338 <sub>H</sub> |     | 33F <sub>H</sub> |

| Row25 | 320 <sub>H</sub> |     | 337 <sub>H</sub> |                  |     |                  |

#### **6.2.7** Character Generator

The character generator includes the character and control code decoder, the RAM interface and the RGB-, BLAN- and COR-signal generator. The display generator reads data from the display RAM and calculates appropriate data which drives the RGB output pins. The pixel clock is generated by a start-stop-oscillator. The synchronization of display and pixel clock is done via external sandcastle or HS and VS signals. For 60 Hz display the number of lines per character can be reduced to 9 or 8. In this case pixel information of line 10 or 9 plus 10 are rejected. With this mode combined with the variable vertical offset it is possible to generate NTSC displays with 25 rows.

Characters with a binary value < 32 are interpreted as control characters. For binary values  $\ge$  32 a ROM character is selected through the addition of the character address, the language setting in SFR, the europe designation and the graphics control bits delivered from the control bit decoder.

A total of 64 OSD characters and 64 mosaic graphics characters are available. OSD characters with addresses  $80...SF_{\rm H}$  can be displayed together with 60 lower case characters because there is no memory overlapping with any other characters. OSD characters with addresses  $60...7F_{\rm H}$  can only be displayed if bit OSD in SFR LANGC is set (see diagrams: Physical Address Space and Vertical Address Space).

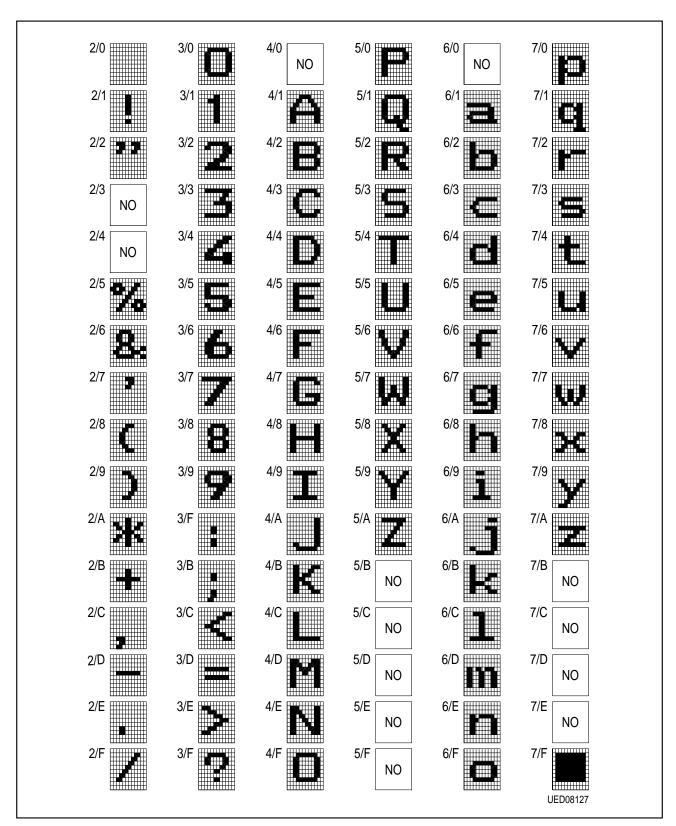

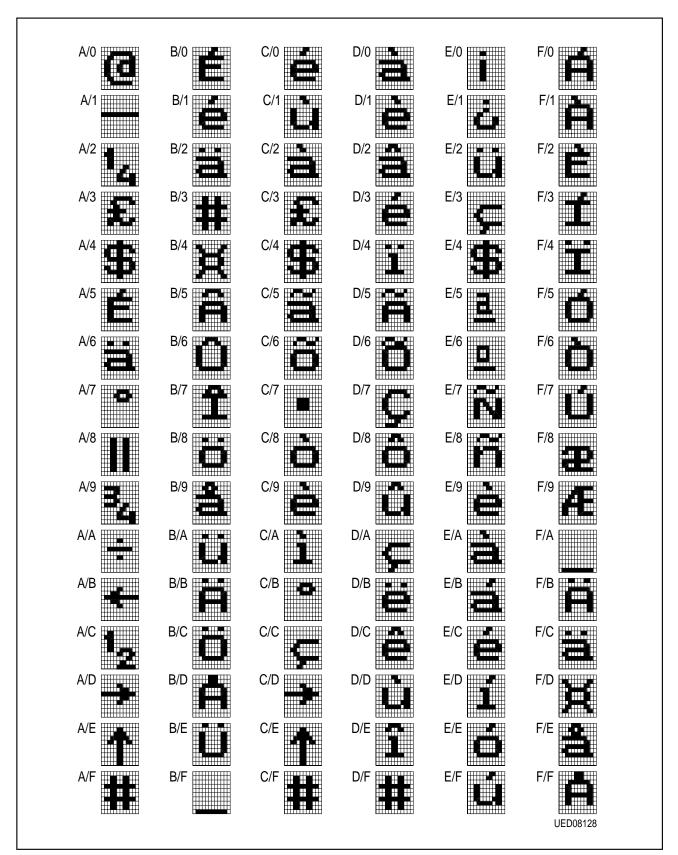

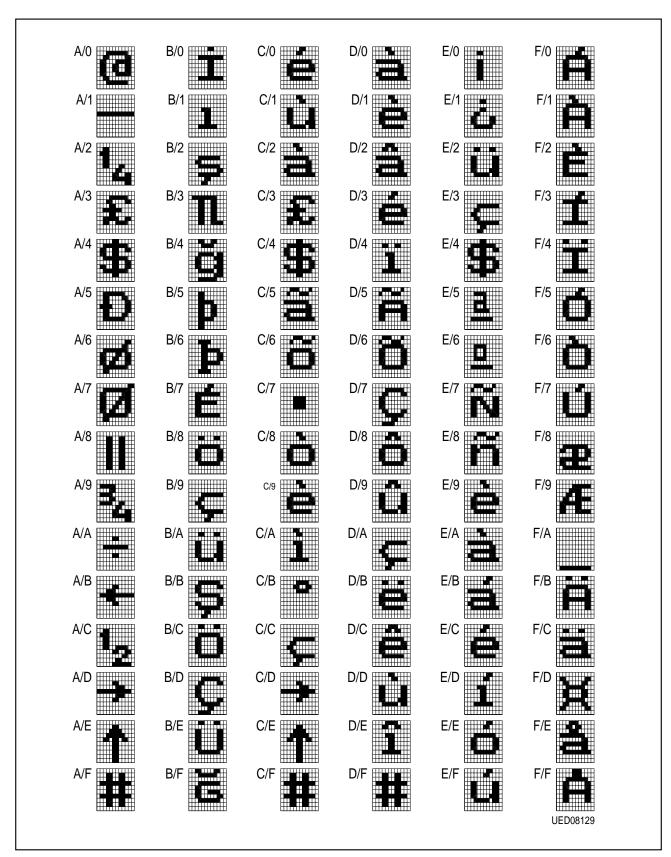

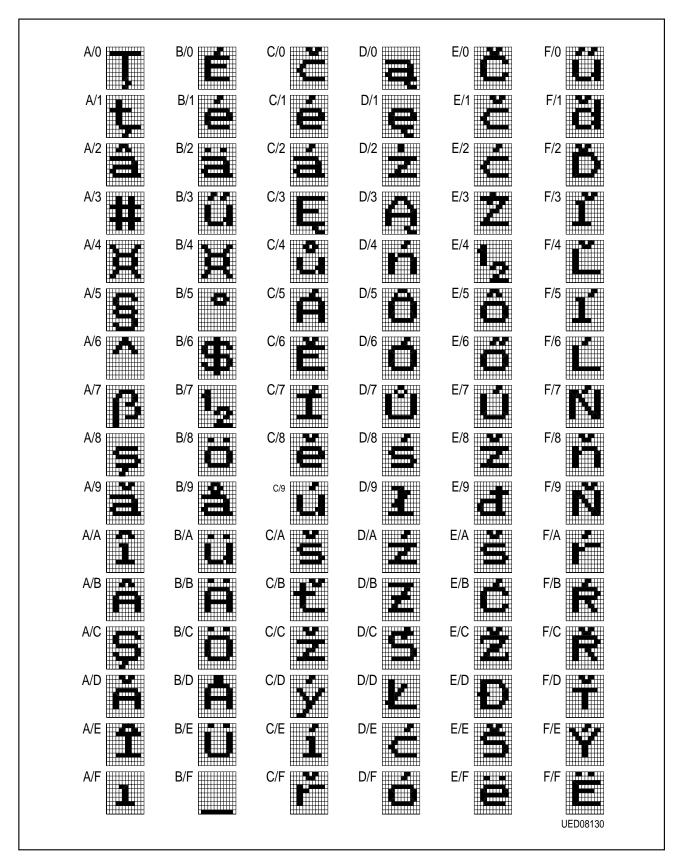

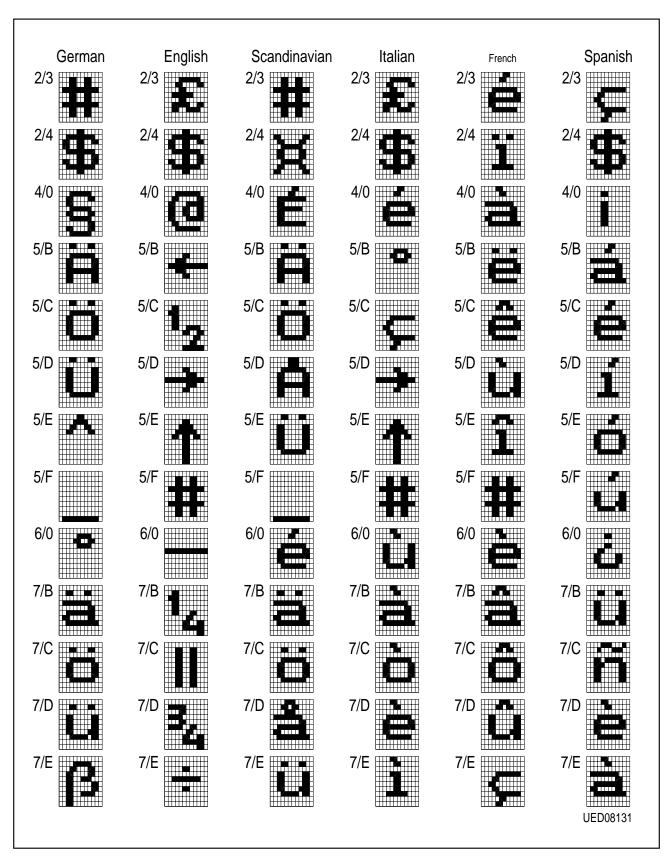

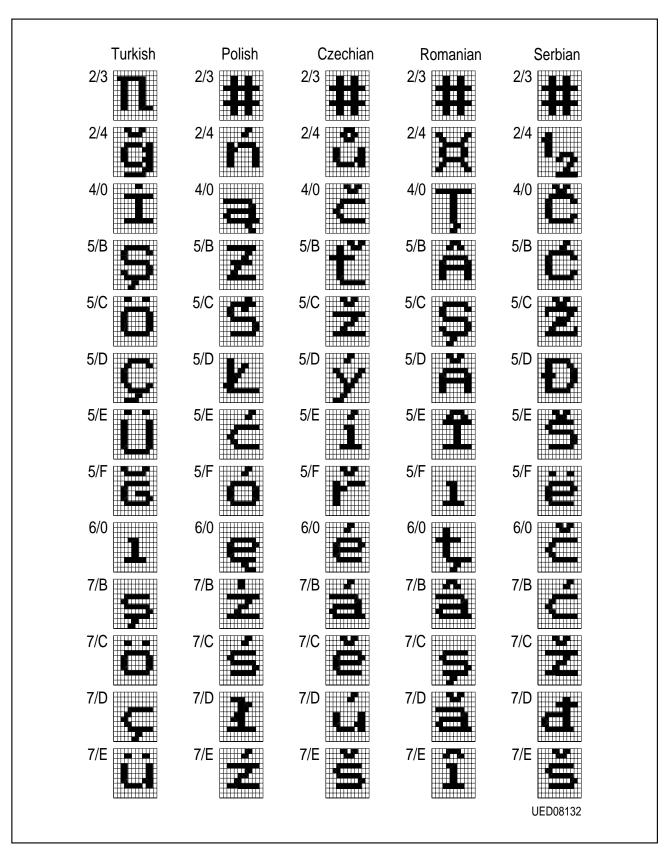

## Figures 6 - 13 shows the character ROM contents.

The control byte decoder analyses the serial attributes from the display memory and generates control clocks for the RGB logic and the character address decoder. The interpretation of control characters is corresponding to World Standard Teletext norm. **Table 5** shows the characters and the appearance on the screen.

The RGB logic combines data from the character address decoder, control byte decoder and settings from the SFR registers and generates signal R, G, B, BLAN and COR.

## 6.2.8 On Screen Display (OSD)

A display page in the display memory can also be used for on screen displays. It should be recognized that all serial attributes of a normal text page are also valid for an OSD display. Therefore if double height is selected anywhere in a normal text page, row n and row n-1 (upper row) should be saved and overwritten by OSD data in order to generate a correct display. Switching back to text display is accomplished by rewriting the text data to the page. The same procedure is needed for the "erase row bits" in row 25. By means of enable box bits, transparent control bits and the serial attribute "OSD", the OSD screen can be controlled fully independent of the normal text page. The serial OSD-bit toggles the screen between normal display and OSD.

Table 5

Serial Control Bytes

| B7, B6, B5, B4 | 0                              | 1                                  |

|----------------|--------------------------------|------------------------------------|

| B3, B2, B1, B0 |                                |                                    |

| 0              | Alpha Black                    | Mosaic Black                       |

| 1              | Alpha Red                      | Mosaic Red                         |

| 2              | Alpha Green                    | Mosaic Green                       |

| 3              | Alpha Yellow                   | Mosaic Yellow                      |

| 4              | Alpha Blue                     | Mosaic Blue                        |

| 5              | Alpha Magenta                  | Mosaic Magenta                     |

| 6              | Alpha Cyan                     | Mosaic Cyan                        |

| 7              | Alpha White <sup>(1)</sup>     | Mosaic White                       |

| 8              | Flash                          | Conceal <sup>(2)</sup>             |

| 9              | Steady <sup>(1,2)</sup>        | Contiguous Mosaic <sup>(1,2)</sup> |

| А              | End Box (1,3)                  | Separated Mosaic <sup>(2)</sup>    |

| В              | Start Box (3)                  | OSD <sup>(5)</sup>                 |

| С              | Normal Height <sup>(1,2)</sup> | Black Background <sup>(2)</sup>    |

| D              | Double Height                  | New Background (2)                 |

| Е              | Double Width <sup>(4)</sup>    | Hold Mosaic <sup>(2)</sup>         |

| F              | Double Size <sup>(4)</sup>     | Release Mosaic <sup>(1)</sup>      |

<sup>(1)</sup> Reset state at begin of each row.

<sup>(2)</sup> Takes effect with control character. Other control characters takes effect in the next character field.

<sup>(3)</sup> Two identical control characters are transmitted in sequence. The effect begins between the control characters.

<sup>(4)</sup> Can only be activated if SFR DMOD.0 is set to '1', otherwise no influence.

<sup>(5)</sup> Toggle; takes effect with next character (on), takes effect with control character (off).

## 6.2.9 Display Special Function Registers

The display generator includes 9 registers to select the different formats and functions.

## **Display Horizontal Delay Register DHD**

**Display Horizontal Delay**

**DHD**

SFR-Address C3<sub>H</sub>

SFR-Address C4<sub>H</sub>

Register

Default after reset: 00<sub>H</sub>

(MSB) (LSB)

|  | HD.7 | HD.6 | HD.5 | HD.4 | HD.3 | HD.2 | HD.1 | HD.0 |

|--|------|------|------|------|------|------|------|------|

|--|------|------|------|------|------|------|------|------|

**HD.7 ... HD.0** variable negative horizontal display offset relative to positive

edge of HS in pixel units.

**Comments** None

## **Display Vertical Delay Register DVD**

Register

Default after reset: 00<sub>H</sub>

**Display Vertical Delay**

(MSB) (LSB)

DVD

| _ | _ | VD.5 | VD.4 | VD.3 | VD.2 | VD.1 | VD.0 |

|---|---|------|------|------|------|------|------|

|---|---|------|------|------|------|------|------|

**VD.5** ... **VD.0** variable negative vertical display offset relative to positive

edge of VS in HS units.

**Comments** None

**Display Transparent Control Register DTCR**

Display Transparent Control DTCR SFR-Address C5<sub>H</sub>

Register

Default after reset: 00<sub>H</sub>

(MSB) (LSB)

| CORI CORO CRP BP TRFI TRFO TRBI TRB |

|-------------------------------------|

|-------------------------------------|

**TRBO** 1 = Transparent Background Colors outside Box **and** OSD.

**TRBI** 1 = Transparent Background Colors inside Box **or** OSD.

**TRFO** 1 = Transparent Foreground Colors outside Box **and** OSD.

**TRFI** 1 = Transparent Foreground Colors inside Box **or** OSD.

**IBP** 1 = Invert Blanking Polarity. Blanking is active high.

0 = Blanking is active low.

**ICRP** 1 = Invert Contrast Reduction Polarity. COR is active high.

0 = COR is active low.

**CORO** 1 = Contrast Reduction for Background Color outside Box

and outside OSD.

**CORI** 1 = Contrast Reduction for Background Color inside Box or

inside OSD.

Note: Outside of a box means outside of a box opened by control code sequence '0B,0B' and outside of an OSD-Box opened by control code '1B'.

Inside a box means inside of a box opened by control code sequence '0B,0B' or inside an OSD-Box opened by control code '1B'.

**Comments** For further Transparent Modes see SFR DCRP.

## **Display Mode Register DMOD**

Display Mode Register DMOD SFR-Address D6<sub>H</sub>

Default after reset: XXXX0000B

(MSB) (LSB)

- - - - 0 0 DSDW

**DSDW** if set, displaying Double Size and Double Width characters is

enabled

if cleared, control codes 0E<sub>H</sub> and 0F<sub>H</sub> have no effect

Bit 1 to 3 have always to be written with '0'

Bit 4 to 7 not implemented, to be written with '0'

Note: This register is not readable. Thus, do not use read-modify-write operations like ANL, ORL to modify this register.

#### Display Feature Double Size and Double Width

Double Size and Double Width are selectable via serial attributes. The control codes are '0E' for Double Width and '0F' for Double Size. Now, there are 4 control codes available, to modify the character size:

| Control<br>Code | Name          | Effect                                                                                                         | Side Effects                 |

|-----------------|---------------|----------------------------------------------------------------------------------------------------------------|------------------------------|

| OC              | Normal Size   | No stretching Vertical character stretching Horizontal character stretching Horizontal and vertical stretching | any activated stretching off |

| OD              | Double Height |                                                                                                                | horizontal stretching off    |

| OE              | Double Width  |                                                                                                                | vertical stretching off      |

| OF              | Double Size   |                                                                                                                | None                         |

Since Double Width and Double Size control codes should not be interpreted by a pure level 1 text-decoder, this size attributes have to be enabled by setting SFR-bit DSDW.

Double Width and Double Size characters are accomplished by skipping every second character code after setting any of this following attributes where the remaining displayable characters are stretched horizontally and thus conceating the character. Although every second character is hidden, these codes will take effect if they are control characters.

## **Display Mode Register 1 DMODE1**

Display Mode Register 1 DMODE1 SFR-Address C6<sub>H</sub>

Default after reset: 00<sub>H</sub>

(MSB) (LSB)

| ST_TOP   | ST_DIS | CON                                                                                                                                                                                                                                                                              | DH.1                                                                                                                  | DH.0                         | BD_24 | BD_1_23                   | BD_0 |  |  |  |

|----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------|-------|---------------------------|------|--|--|--|

| BD_0     |        |                                                                                                                                                                                                                                                                                  | <ul><li>1 = Box characters in row 0 are ignored.</li><li>0 = Box characters in row 0 are displayed.</li></ul>         |                              |       |                           |      |  |  |  |

| BD_1_23  |        |                                                                                                                                                                                                                                                                                  |                                                                                                                       | s in row 1 -<br>s in row 1 - | _     |                           |      |  |  |  |

| BD_24    |        |                                                                                                                                                                                                                                                                                  | <ul><li>1 = Box characters in status row are ignored.</li><li>0 = Box characters in status row are allowed.</li></ul> |                              |       |                           |      |  |  |  |

| DH.1 DF  | 1.0    | <ul> <li>00 = Normal row display.</li> <li>01 = Rows 0 - 11 are displayed in double height. Status row is displayed in normal height.</li> <li>10 = Rows 12 - 23 are displayed in double height. Status row is displayed in normal height.</li> <li>11 = Not defined.</li> </ul> |                                                                                                                       |                              |       |                           |      |  |  |  |

| CON      |        |                                                                                                                                                                                                                                                                                  |                                                                                                                       | aracters are                 |       | е.                        |      |  |  |  |

| ST_DIS   |        | <ul><li>1 = Status row is handled as blanked row.</li><li>0 = Status row is displayed.</li></ul>                                                                                                                                                                                 |                                                                                                                       |                              |       |                           |      |  |  |  |

| ST_TOP   |        |                                                                                                                                                                                                                                                                                  |                                                                                                                       | displayed ir<br>displayed ir |       |                           |      |  |  |  |

| Comments | 5      | -                                                                                                                                                                                                                                                                                | -                                                                                                                     | -                            |       | sequence 0<br>ened by con | • •  |  |  |  |

code 1B<sub>H</sub>) will not be affected.

**Display Mode Register 2 DMODE2**

Display Mode Register 2 DMODE2 SFR-Address C7<sub>H</sub>

Default after reset: 00<sub>H</sub>

(MSB) (LSB)

| DTFST 2 | DTEST 1 | DTEST 0 | DCHAP 2  | DCHAP 1 | DCHAP.0 | C10 | C7 |

|---------|---------|---------|----------|---------|---------|-----|----|

| DIEGI.2 | DIE01.1 | DIE01.0 | DOMAI .Z | DOITAL  |         | 0.0 | 0, |

C7 1 = Header is handled as erased row (Suppress Header).

C10 1 = Rows 1 - 23 are handled as erased rows (Inhibit Display).

**DCHAP.2..0** selects one of eight display chapters.

**DTEST.0** Not defined, must be set to 0.

**DTEST.1** Not defined, must be set to 0.

**DTEST.2** Not defined, must be set to 0.

**Comments** For 1-page-versions (SDA 5251, SDA 5252) the bits

DCHAP.2..0 have to be set to '0'.

#### Language Control Register LANGC

Language Control Register LANGC SFR-Address C9<sub>H</sub>

Default after reset: 00<sub>H</sub>

(MSB) (LSB)

| OSD 64 | LANGC.6 | LANGC.5 | LANGC.4 | LANGC.3 | LANGC.2 | LANGC.1 | LANGC.0 |

|--------|---------|---------|---------|---------|---------|---------|---------|

|--------|---------|---------|---------|---------|---------|---------|---------|

**LANGC.4... LANGC.0** Language selection for text outside of an OSD window.

00000 : German 01010 : English

01011: Scandinavian

01100 : Italian 01101 : French 01110 : Spanish 11001 : Turkish 11010 : Rumanian 11011 : Hungarian 11100 : Czechish 11101 : Polish 11110 : Serbian others : Not defined

LANGC.6... LANGC.5

00: West european special characters are addressable.

01: West european special characters are addressable

(Turkish).

10: East european special characters are addressable.

11: Not defined.

**OSD\_64**

64 OSD character mode on. If the serial attribute OSD is set a total of 64 OSD characters is available. The lower case G0 characters can not be used.

32 OSD character mode on. Only OSD characters in ROM column 8 and 9 are available if serial attribute OSD is set. Outside an OSD box all 64 OSD characters are

available (see Figure 12).

Comments

see Diagrams 'x' and 'y' Physical and Vertical address spaces

**SIEMENS**

**Display Cursor Column Position Register DCCP**

Display Cursor Column DCCP SFR-Address CA<sub>H</sub>

**Position Register**

Default after reset: 00<sub>H</sub>

(MSB) (LSB)

- DC\_EN DCCP.5 DCCP.4 DCCP.3 DCCP.2 DCCP.1 DCCP.0

**DC\_EN** 1 = Display Cursor Enable.

0 = Display Cursor Disable.

**DCCP.5...DCCP.0** Active cursor column position.

DCCP.5...0 =  $0_D$ : column 1 on screen.

Bit 7 reserved, should be set to '0'.

**Comments** None

**Display Cursor Row Position Register DCRP**

Display Cursor Row Position DCRP SFR-Address CB<sub>H</sub>

Register

Default after reset: 00<sub>H</sub>

(MSB) (LSB)

TRBOS COROS - DCRP.4 DCRP.3 DCRP.2 DCRP.1 DCRP.0

**DCRP.4...DCRP.0** defines row of active cursor position.

**TRBOS** 1 = The outer screen display area appears transparent

0 = The outer screen display area gets the background colour

defined in register DTIM

**COROS** 1 = Contrast reduction outer screen

Bit 5 reserved, should be set to '0'.

**Comments** bits TRBOS and COROS thematically belong to the SFR

**DTCR**

## **Display Timing Control Register DTIM**

**Display Timing Control**

DTIM

SFR-Address CC<sub>H</sub>

Register

Default after reset: 00<sub>H</sub>

(MSB) (LSB)

| BG_R | BG_G | BG_B | EO_P30 | EO_VS | SANDC | LIN9 | LIN8 |

|------|------|------|--------|-------|-------|------|------|

| _    | _    | _    | _      | _     |       |      |      |

LIN8 1 = 8 line character mode (higher priority than LIN9).

**LIN9** 1 = 9 line character mode.

**SANDC** 1 = horizontal and vertical synchronization accepts sandcastle

pulse from pad HS/SC.

0 = horizontal and vertical synchronization accepts HS and

VS pulses from pads HS/SC and VS respectively.

**EO\_VS** 1 = The ODD/EVEN-signal evaluated from CVBS is enabled

on Pin VS.

0 = ODD/EVEN function is disabled.

1 = The ODD/EVEN-signal evaluated from CVBS is enabled

on Pin P3.0.

**EO\_P30** 0 = ODD/EVEN function is disabled.

BG\_R BG\_G BG\_B

|       | BG_R | BG_G | BG_B |        | BG_R | BG_G | BG_B |

|-------|------|------|------|--------|------|------|------|

| black | 0    | 0    | 0    | yellow | 1    | 1    | 0    |

| red   | 1    | 0    | 0    | violet | 1    | 0    | 1    |

| green | 0    | 1    | 0    | cyan   | 0    | 1    | 1    |

| blue  | 0    | 0    | 1    | white  | 1    | 1    | 1    |

outer screen background colour

## **Teletext-Sync-Interrupt-Register TTXSIR**

Teletext-Sync-Interrupt- TTXSIR SFR-Address C8<sub>H</sub>

Register

Default after reset: 00<sub>H</sub>

(MSB) (LSB)

| _      | VSY | HSY | PCLK | DVIREN                       | DVIRST | DHIREN      | DHIRST   |

|--------|-----|-----|------|------------------------------|--------|-------------|----------|

| DHIRST |     | •   | •    | tal sync int<br>set by softw |        | est (set by | positive |

**DHIREN** 1 = enable display horizontal sync interrupt requests.

**DVIRST** 1 = display vertical sync interrupt request (set by positive edge of VS, reset by software).

**DVIREN** 1 = enable display vertical sync interrupt requests.

**PCLK** Reflects state of internal pixel clock.

**HSY** Reflects state of HS-signal decoded by SC-decoder

VSY Reflects state of VS-signal decoded by SC-decoder

(SANDC=1).

Reflects state of VS-pin (SANDC=0).

Bit 7 reserved, should be set to '0'

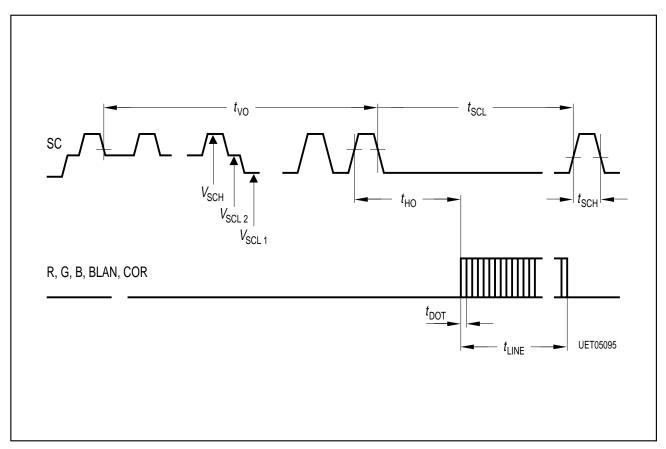

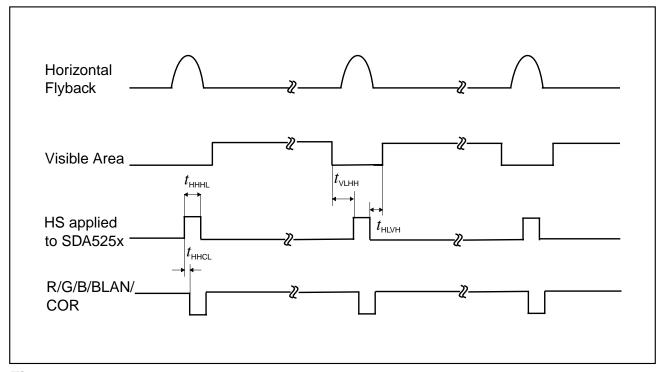

#### 6.2.10 Sandcastle Decoder

To fit the requirements of various applications the input circuit of the sandcastle decoder is programmable. Both slicing levels ( $V_{\rm SCH}$ ,  $V_{\rm SCL2}$ ) which are important for proper SC-decoder function can be varied in a range of about 0.9 V and in addition there is the possibility to increase the implemented hysteresis by 0.3 V typically. Further noise reduction and spike rejection on pin SC is accomplished by using a digital filter following the input circuitry. See **Figure 41** on **page 133** for further information on  $V_{\rm SCH}$  and  $V_{\rm SCI-2}$ .

## Sandcastle Control Register SCCON

| Sandcastle Control Register S | SCCON | SFR-Address CE <sub>H</sub> |

|-------------------------------|-------|-----------------------------|

|-------------------------------|-------|-----------------------------|

Default after reset: 00<sub>H</sub>

(MSB) (LSB)

| 0 | SCCH.2 | SCCH.1 | SCCH.0 | 0 | SCCL.2 | SCCL.1 | SCCL.0 |

|---|--------|--------|--------|---|--------|--------|--------|

|---|--------|--------|--------|---|--------|--------|--------|

| SCCL10 | $00 = \text{set } V_{\text{SCL2}} \text{ to lowest level (1.0 V typ.)}$ $01 = \text{increase } V_{\text{SCL2}} \text{ by 0.3 V (typ.)}$ $10 = \text{increase } V_{\text{SCL2}} \text{ by 0.6 V (typ.)}$ $11 = \text{increase } V_{\text{SCL2}} \text{ by 0.9 V (typ.)}$ |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCL.2  | 0 = hysteresis $V_{\rm SCL2}$ set to 0.3 V (typ.)<br>1 = increase hysteresis $V_{\rm SCL2}$ by 0.6 V (typ.)                                                                                                                                                             |

| SCCH10 | $00 = \text{set } V_{\text{SCH}} \text{ to lowest level 3.0 V (typ.)}$ $01 = \text{increase } V_{\text{SCH}} \text{ by 0.3 V (typ.)}$ $10 = \text{increase } V_{\text{SCH}} \text{ by 0.6 V (typ.)}$ $11 = \text{increase } V_{\text{SCH}} \text{ by 0.9 V (typ.)}$     |

| SCCH.2 | 0 = hysteresis $V_{\rm SCH}$ set to 0.3 V (typ.)<br>1 = increase hysteresis $V_{\rm SCH}$ by 0.6 V                                                                                                                                                                      |

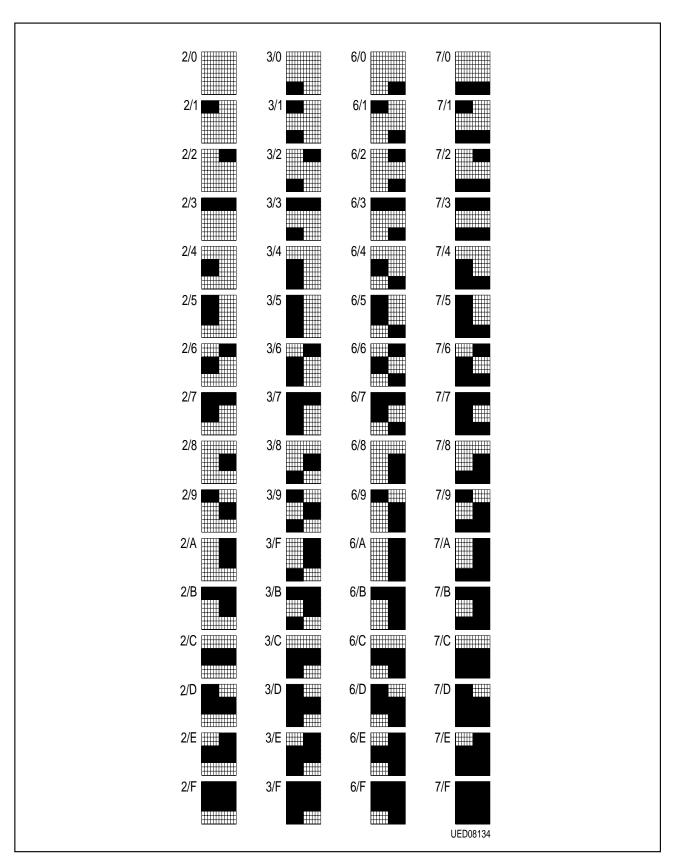

Figure 6

G0 Character Set

Note: NO = hardware mapped national option character

Figure 7

Character Set West Europe

Figure 8

Character Set West Europe (Turkish)

Figure 9 Character Set East Europe

Figure 10 National Option Characters I

Figure 11

National Option Characters II

Figure 12

OSD Characters Set (these characters are customized and thus left blank on this page)

Note: Characters ... to ... can only be used inside an OSD box.

Figure 13

Graphics Character Set

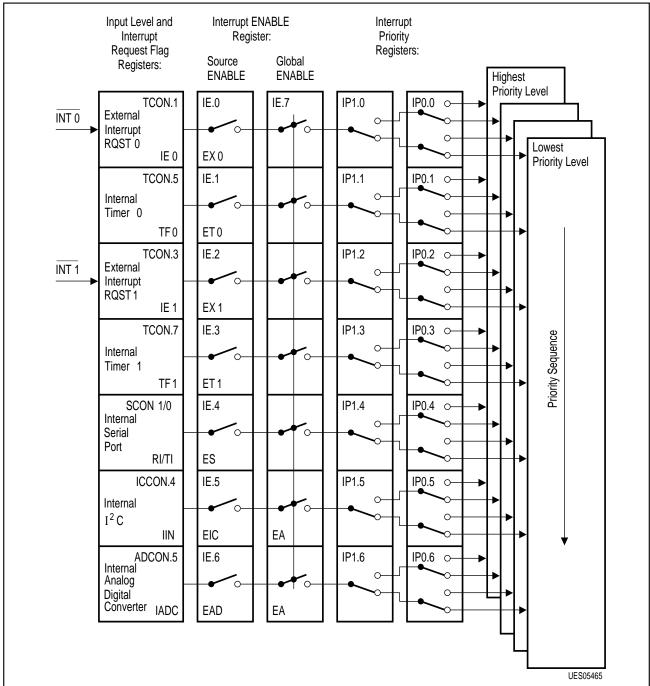

#### 6.3 Microcontroller

#### 6.3.1 Architecture

The CPU manipulates operands in two memory spaces: the program memory space, and the data memory space. The program memory address space is provided to accommodate relocatable code.

The data memory address space is divided into the 256-byte internal data RAM, XRAM (extended data memory, accessible with MOVX-instructions) and the 128-byte Special Function Register (SFR) address spaces. Four register banks (each bank has eight registers), 128 addressable bits, and the stack reside in the internal data RAM. The stack depth is limited only by the available internal data RAM. It's location is determined by the 8-bit stack pointer. All registers except the program counter and the four 8-register banks reside in the special function register address space. These memory mapped registers include arithmetic registers, pointers, I/O-ports, registers for the interrupt system, timers, pulse width modulator and serial channel. Many locations in the SFR-address space are addressable as bits.

Note that reading from unused locations within data memory will yield undefined data.

Conditional branches are performed relative to the 16 bit program counter. The registerindirect jump permits branching relative to a 16-bit base register with an offset provided by an 8-bit index register. Sixteen-bit jumps and calls permit branching to any location in the memory address space.

The processor as five methods for addressing source operands: register, direct, register-indirect, immediate, and base-register plus index-register indirect addressing.

The first three methods can be used for addressing destination operands. Most instructions have a "destination, source" field that specifies the data type, addressing methods and operands involved. For operations other than moves, the destination operand is also a source operand.

Registers in the four 8-register banks can be accessed through register, direct, or register-indirect addressing; the lower 128 bytes of internal data RAM through direct or register-indirect addressing, the upper 128 bytes of internal data RAM through register-indirect addressing; and the special function registers through direct addressing. Look-up tables resident in program memory can be accessed through base-register plus index-register indirect addressing.

#### 6.3.1.1 CPU-Hardware

#### **Instruction Decoder**

Each program instruction is decoded by the instruction decoder. This unit generates the internal signals that control the functions of each unit within the CPU-section. These signals control the sources and destination of data, as well as the function of the Arithmetic/Logic Unit (ALU).

### **Program Control Section**

The program control section controls the sequence in which the instructions stored in program memory are executed. The conditional branch logic enables conditions internal and external to the processor to cause a change in the sequence of program execution. The 16-bit program counter holds the address of the instruction to be executed. It is manipulated with the control transfer instructions listed in **Chapter "Instruction Set" on page 116**.

#### Internal Data RAM