# CS4041 CHIPSet

84041 and 84045 CHIPSet

> Data Book Revision 1.0

February 1995

PRELIMINARY

CHIP5

#### **Copyright Notice**

Copyright© 1994 and 1995 Chips and Technologies, Inc. ALL RIGHTS RESERVED.

This manual is copyrighted by Chips and Technologies, Inc. You may not reproduce, transmit, transcribe, store in a retrieval system, or translate into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, any part of this publication without the express written permission of Chips and Technologies, Inc.

#### **Restricted Rights Legend**

Use, duplication, or disclosure by the Government is subject to restrictions set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at 252.277-7013.

#### **Trademark Acknowledgment**

CHIPS Logotype, CHIPSlink, CHIPSPort, ELEAT, LeAPSet, NEAT, NEATsx, PEAK, SCAT, SuperMathDX, and Wingine are registered trademarks of Chips and Technologies, Inc.

Printgine, SuperState, SuperMath, WinPC and XRAM Video Cache are trademarks of Chips and Technologies, Inc.

IBM®, is a registered trademarks of International Business Machines Corporation.

IBM® AT, XT, PS/2, Micro Channel, Enhanced Graphics Adapter, Color Graphics Adapter, Video Graphics Adapter, IBM Color Display and IBM Color Display and IBM Monochrome Display are trademarks of International Business Machines Corporation.

VESA® is a registered trademark of Video Electronics Standards Association.

VL-Bus is a trademark of Video Electronics Standards Association.

All other trademarks are the property of their respective holders.

#### Disclaimer

This document is provided for the general information of the customer. Chips and Technologies, Inc., reserves the right to modify the information contained herein as necessary and the customer should ensure that it has the most recent revision of the document. CHIPS makes no warranty for the use of its products and bears no responsibility for any errors which may appear in this document. The customer should be on notice that the field of personal computers is the subject of many patents held by different parties. Customers should ensure that they take appropriate action so that their use of the products does not infringe upon any patents. It is the policy of Chips and Technologies, Inc. to respect the valid patent rights of third parties and not to infringe upon or assist others to infringe upon such rights.

### **CS4041 CHIPSet**

#### n Local Bus

- VESA Local Bus 2.0 Compatible

- Full L1 Write Back Cache Support

- Up to 3 LDEV#s and 3 sets of LREQ# / LGNT# pairs provided directly

- Read and write bursting from VL Masters supported

#### n DRAM Controller

- 8 banks of DRAMs supported (4 double banks SIMMs, etc.)

- Page mode and page interleave

- 256K, 1M, 4M, and 16M deep DRAMs supported

- Direct Drive RAS

- Direct drive CAS, DWE, and MA for up to 36 DRAM chips

- Hidden refresh with staggered RAS

- SMM memory support

- Variety of timing modes for system optimization

### n Cache Controller

- Direct mapped, external tag, internal comparator

- 16 byte line size

- 64K, 128K, 256K, 512K or 1M size

- Write back or Write through

- Single bank or dual bank (word interleaved) cache

- Multiple timing modes supported for cost performance tradeoff

#### n Power Management

- SMI support

- Many power management features can be utilized without SMI

- Internal Clock switching and stopping

- Intel, AMD, and Cyrix support

- Event monitoring

- I/O restart capability

### n Integrated Local Bus IDE

- Requires only 3 TTL

- Support for 8 drives (4 connectors)

- Data port accesses accelerated via local bus accesses

- Timing modes selectable for each drive

### n Keyboard Controller

- Integrated state machine based keyboard controller

- Mouse port included

- Keylock input provided on a multifunction pin

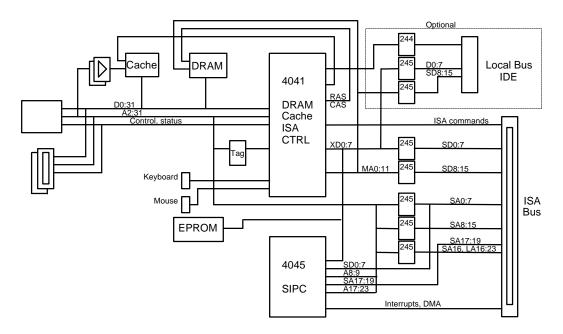

Figure 1: System Block Diagram

Revision 1.0 2/10/95 Preliminary CS4041

# **Revision History**

| Revision | Date     | By       | Comments                                                                    |

|----------|----------|----------|-----------------------------------------------------------------------------|

|          |          | -        |                                                                             |

| 0.1      | 9/29/93  | BN       | First Release: Confidential-NDA Required; Subject to change without notice. |

| 0.2      | 4/12/94  | DJ/st    | Second Release: Added Index Register 01; Subject to change without notice.  |

| 0.3      | 12/14/94 | DJ/st    | Third Release: Added 84041 & 84045 Pin Diagrams; Added 84041/84045          |

|          |          |          | Absolute Maximum Conditions, Recommended Operations, and DC                 |

|          |          |          | Characteristics; Added 84041 & 84045 Mechanical Specifications; Subject to  |

|          |          |          | change without notice.                                                      |

| 0.4      | 1/27/95  | DJ/st/bb | Fourth Release: Added AC Characteristics; Numerous minor clarifications and |

|          |          |          | corrections.                                                                |

| 1.0      | 2/10/95  | DH/st    | Official Release                                                            |

Revision 1.0 2/10/95 2 Preliminary CS4041

# **Table of Contents**

| ı. | Introduction                                | 11 |

|----|---------------------------------------------|----|

|    | 1.1. CPUs Supported                         | 11 |

|    | 1.2. External Chips                         | 11 |

| 2. | Pinouts                                     | 13 |

|    | 2.1. Pin Descriptions                       |    |

|    | 2.2. 84041 Pin Overview                     | 15 |

|    | 2.3. 84045 Pin Overview                     | 17 |

|    | 2.4. 84041 Pin Descriptions                 | 18 |

|    | 2.5. 84045 Pin Descriptions                 | 24 |

| 3. | Registers                                   | 29 |

|    | 3.1. I/O Ports and Configuration Registers  | 29 |

|    | 3.2. 84041 I/O Port Addresses               | 32 |

|    | 3.3. 84041 Index Configuration Registers    | 35 |

|    | 3.4. 84045 I/O Port Addresses               | 60 |

|    | 3.5. 84045 Configuration Registers          | 63 |

| 4. | System Level Functions and Cross References | 69 |

|    | 4.1. Clocks                                 | 69 |

|    | 4.2. Reset and GATEA20                      | 69 |

|    | 4.3. Arbitration                            |    |

|    | 4.4. Refresh                                | 70 |

|    | 4.5. Co-processor Logic                     | 71 |

|    | 4.6. ISA Bus and ISA Features               | 71 |

|    | 4.7. Local Bus Support                      | 71 |

|    | 4.8. DRAM controller                        | 71 |

|    | 4.9. Cache Controller                       | 72 |

|    | 4.10. Keyboard/Mouse Controller             | 73 |

|    | 4.11. IDE Controller                        | 73 |

|    | 4.12. CPUs Containing Writeback Caches      |    |

| 4.13. CPU Capabilities for Power Management                  |     |

|--------------------------------------------------------------|-----|

| 4.13.1 CPU Clock Control                                     |     |

| 4.13.2 System Management Mode (SMM)                          | 74  |

| 5. 84041 Functional Description                              | 75  |

| 5.1. DRAM/Cache/ISA Controller Chip                          |     |

| 5.2. Clocks                                                  | 75  |

| 5.2.1. Clock Generating Logic                                |     |

| 5.2.2. Clock Inputs                                          |     |

| 5.3. Reset and GATEA20                                       | 76  |

| 5.3.1. CPU Reset and SMI                                     |     |

| 5.3.2. Emulated 8042 KBRESET# and GATEA20                    | 77  |

| 5.4. Arbitration                                             |     |

| 5.5. Address Mapping                                         | 78  |

| 5.5.1. I/O Addressing                                        |     |

| 5.5.2. Memory Addressing                                     | 80  |

| 5.6. SMM Memory Support                                      | 84  |

| 5.6.1. 4041 SMM Memory Map Details                           |     |

| 5.6.2. Additional 4041 SMM Features                          | 85  |

| 5.7. CPUs Supported                                          | 86  |

| 5.7.1. CPU SMM Differences                                   |     |

| 5.7.2. CPU Clock Differences                                 |     |

| 5.7.3. CPU L1 Cache Options                                  |     |

| 5.7.4. CPU Pin Connections                                   | 87  |

| 5.8. CPU Write Back Cache Snooping                           |     |

| 5.9. Secondary Cache Controller                              |     |

| 5.9.1. Pin Usage                                             |     |

| 5.9.2. External Connections                                  |     |

| 5.9.3. SRAM Requirements                                     |     |

| 5.9.5. Write Protection                                      |     |

| 5.9.6. Cache RAM Power-Down                                  |     |

| 5.9.7. Cache Coherency                                       | 97  |

| 5.9.8. Cache Operation                                       |     |

| 5.9.9. Cache Mode and Initialization                         |     |

| 5.9.10. Tag & Data SRAM Testing                              |     |

| 5.10. DRAM Controller                                        |     |

| 5.10.1. Block Decodes                                        |     |

| 5.10.2. Address Muxing                                       |     |

| 5.10.3. Timing Modes                                         |     |

| 5.10.5. DRAM Parity                                          |     |

| 5.10.6. Alternate Master Accesses (VL or ISA Master, or DMA) |     |

| 5.10.7. Programming the Timing Modes.                        | 114 |

| 5.10.8. Automatic DRAM Sizing & Setup                        | 115 |

|      | 5.11. ISA Bus                                           | 115  |

|------|---------------------------------------------------------|------|

|      | 5.11.1. CPU or VL Master Accesses to the ISA Bus        | 115  |

|      | 5.11.2. DMA or ISA Master Accesses to the ISA Bus       | 116  |

|      | 5.11.3. DMA or ISA Master Accesses to DRAM or VL Slaves | 116  |

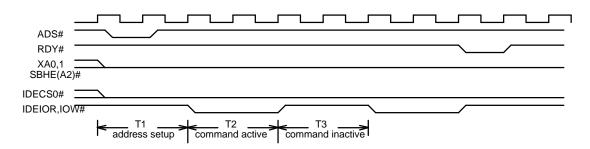

|      | 5.12. Fast IDE                                          | 116  |

|      | 5.12.1. Connections and Signal Generation               |      |

|      | 5.12.2. Cycle Description                               |      |

|      | 5.12.3. Software Considerations                         | 122  |

|      | 5.13. Multifunction Pins                                | 123  |

|      | 5.13.1. CPU Functions                                   | 123  |

|      | 5.13.2. Cache and DRAM Functions                        | 123  |

|      | 5.13.3. VL-Bus Functions                                | 123  |

|      | 5.13.4. SMM and Power Management Functions              | 123  |

|      | 5.13.5. Chip Selects and I/Os, & Misc                   | 124  |

|      | 5.13.6. Pin Selection                                   | 124  |

|      | 5.14. Power Management                                  | 125  |

|      | 5.14.1. Power Management Techniques                     | 125  |

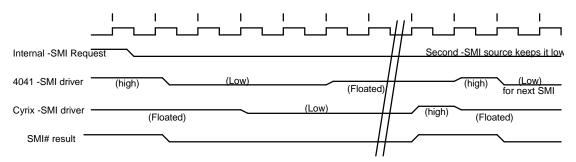

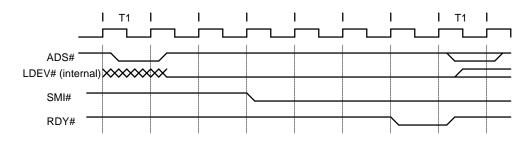

|      | 5.14.2. SMI Sources                                     | 128  |

|      | 5.14.3. SMI Timing Modes                                |      |

|      | 5.14.4. Activity Monitor Timers                         |      |

|      | 5.14.5. Wake Up Events                                  |      |

|      | 5.14.6. Events Detection                                |      |

|      | 5.14.7. I/O Restart                                     |      |

|      | 5.14.8. Power Management Clock Changing                 | 134  |

|      | 5.15. Internal Keyboard/Mouse Controller                | 136  |

|      | 5.15.1. Host CPU Commands                               | 137  |

|      | 5.16. Manufacturing Test Modes                          | 141  |

| 6. 8 | 84045 Functional Description                            | 142  |

|      | 6.1. SIPC Chip Overview                                 | 142  |

|      | 6.1.1. 4045 Added Features                              |      |

|      | 6.1.2. Using 4045 in place of 4035                      |      |

|      | 6.1.3. A quick design checklist.                        |      |

|      | 6.2. Clocks                                             | 1/13 |

|      | 6.2.1. 14.31818 MHz clock                               |      |

|      | 6.2.2. SCLK                                             |      |

|      | 6.2.3. DMA and Refresh clock generation.                |      |

|      | 6.2.4. 32.768KHz clock                                  |      |

|      | 6.3. Reset                                              | 144  |

|      | 6.3.1. Inhibiting IPC Reset for 0V Suspend              |      |

|      |                                                         |      |

|      | 6.4. GATEA20                                            | 146  |

|      | 6.5. Arbitration                                        |      |

|      | 6.5.1. Arbitration Overview                             |      |

|      | 6.5.2. VL Master Arbitration                            |      |

|      | 6.5.3. Main Arbitration Logic                           | 147  |

| 6.6. Performance Control (DeTurbo)                          | 150 |

|-------------------------------------------------------------|-----|

| 6.7. Refresh                                                |     |

| 6.8. ISA Bus                                                | 152 |

| 6.9. IPC Functions                                          |     |

| 6.9.2. Interrupt Controllers                                |     |

| 6.9.3. Timers                                               |     |

| 6.9.4. RTC                                                  |     |

| 6.10. Address Buffers                                       | 159 |

| 6.11. Internal IO Decode and configuration register access. | 159 |

| 6.11.1. Configurations Registers.                           |     |

| 6.11.2. IO decodes.                                         | 159 |

| 6.12. 486 Floating point logic                              | 160 |

| 6.13. Keyboard and Mouse Interrupts.                        | 160 |

| 6.14. Port B and Speaker logic                              | 161 |

| 6.15. Manufacturing Test Modes                              | 161 |

| 7. Electrical Specifications                                | 164 |

| 8. Mechanical Specifications                                | 170 |

6

# **List of Figures**

| Figure 1    | System Block Diagram                      |     |

|-------------|-------------------------------------------|-----|

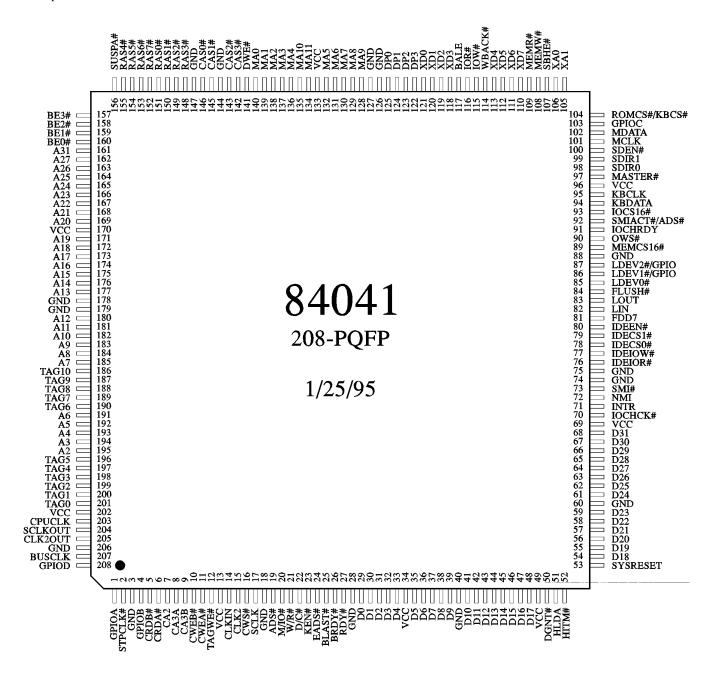

| Figure 2.1  | 84041 Pinout                              |     |

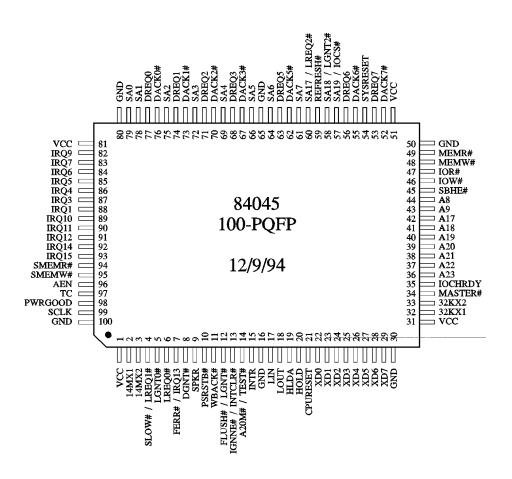

| Figure 2.2  | 84045 Pinout                              |     |

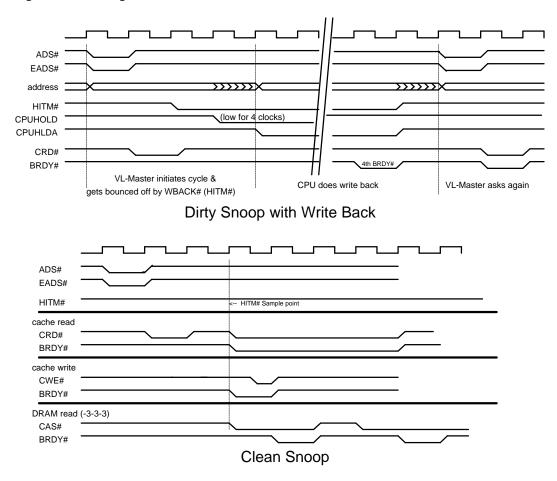

| Figure 5.1  | L1 Write Back Cache Snoop                 | 89  |

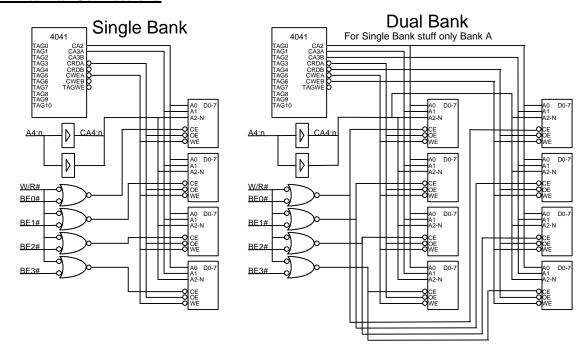

| Figure 5.2  | Cache Data SRAM Connections               | 92  |

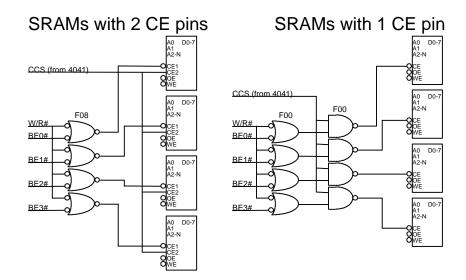

| Figure 5.3  | Cache RAM Low Power Option Connections    | 93  |

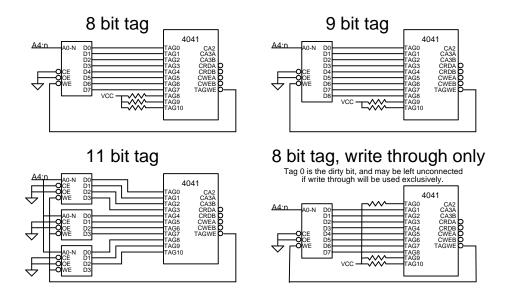

| Figure 5.4  | Cache Tag RAM Connections                 | 93  |

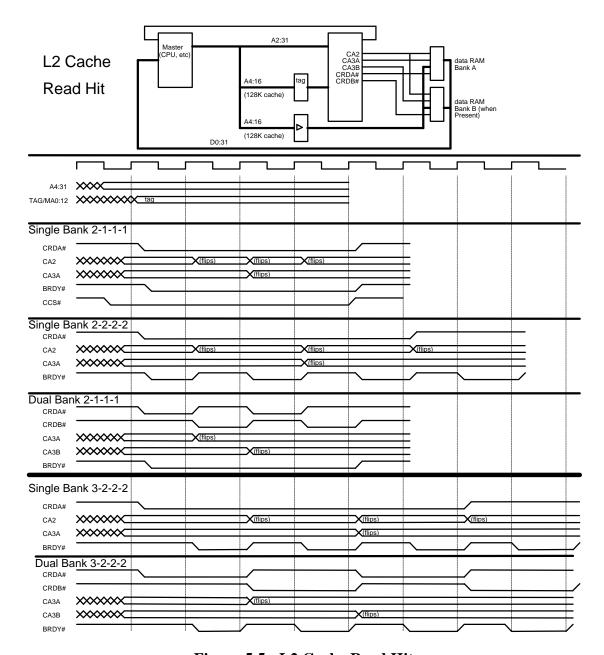

| Figure 5.5  | L2 Cache Read Hit                         | 98  |

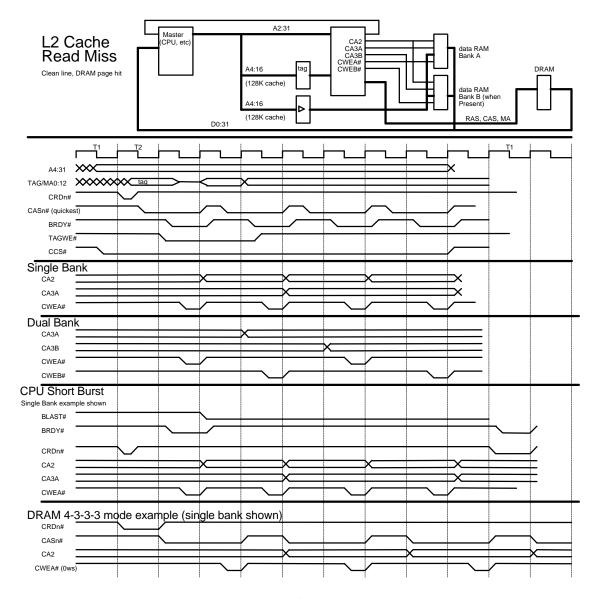

| Figure 5.6  | L2 Cache Read Miss                        | 99  |

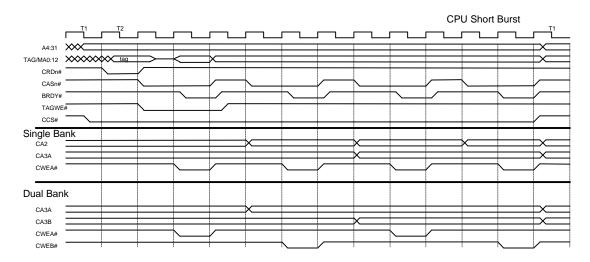

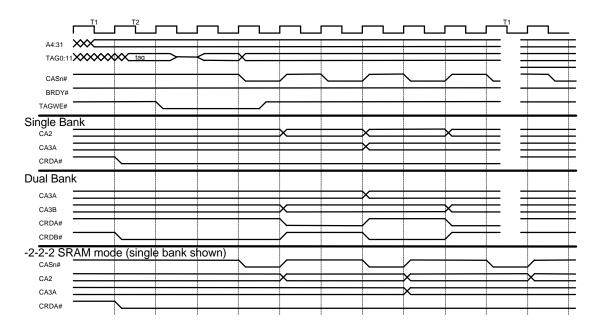

| Figure 5.7  | L2 Cache Read Miss, -2-2-2 Cache Writes   | 100 |

| Figure 5.8  | L2 Cache Write Back                       | 100 |

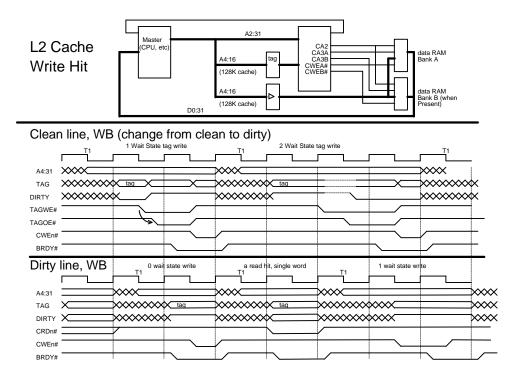

| Figure 5.9  | L2 Cache Write Hit                        | 101 |

| Figure 5.10 | L1 Cache Write Back                       | 101 |

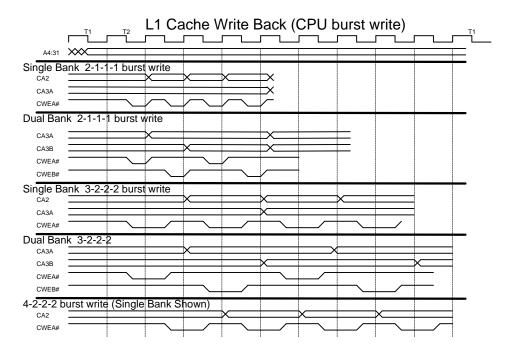

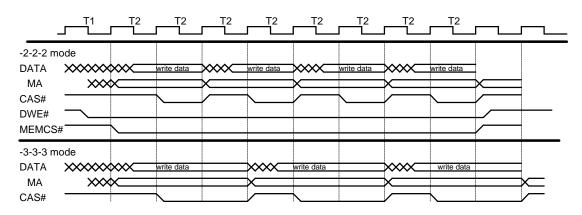

| Figure 5.11 | Burst Read Timing Modes                   | 111 |

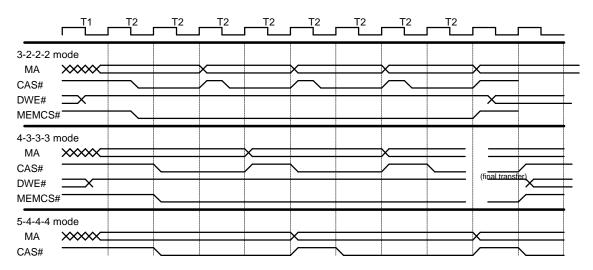

| Figure 5.12 | Burst Write Timing Modes                  | 112 |

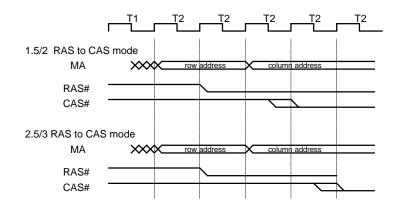

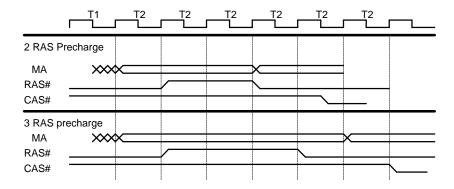

| Figure 5.13 | RAS to CAS Timing Modes                   | 112 |

| Figure 5.14 | RAS Precharge Timing Modes                | 112 |

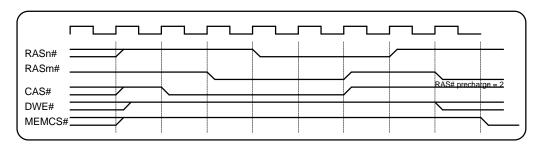

| Figure 5.15 | Refresh cycle                             | 113 |

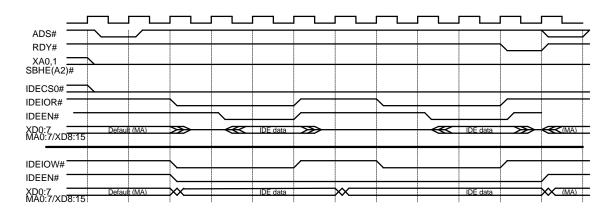

| Figure 5.16 | Basic Fast IDE Timing.                    | 120 |

| Figure 5.17 | Fast IDE Programmable Parameters          | 120 |

| Figure 5.18 | Cyrix SMI# Timing                         | 129 |

| Figure 5.19 | I/O Restart Timing                        |     |

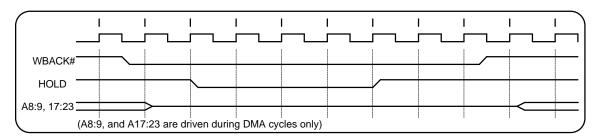

| Figure 6.1  | WBACK# Timing                             | 149 |

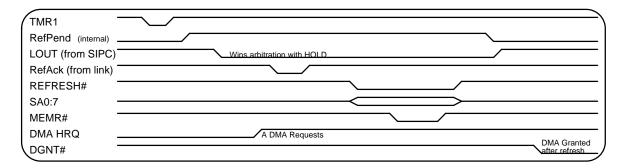

| Figure 6.2  | Hidden Refresh Timing                     | 151 |

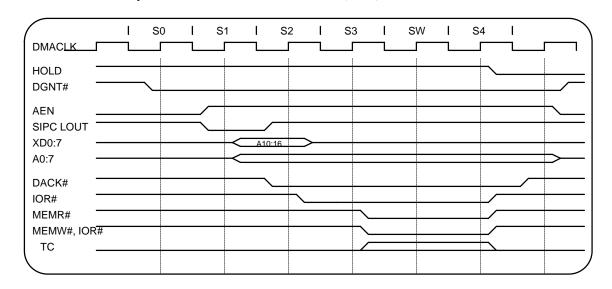

| Figure 6.3  | DMA Cycle Timing                          | 154 |

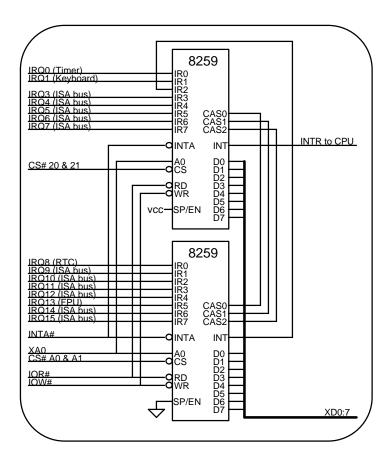

| Figure 6.4  | Interrupt Controller Internal Connections |     |

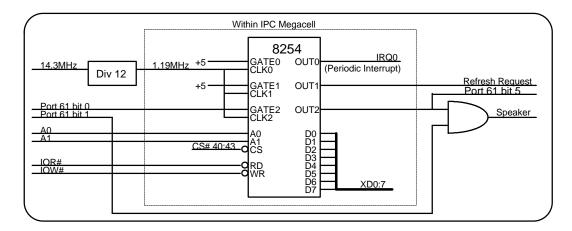

| Figure 6.5  | 8254 Timer Internal Connections           | 156 |

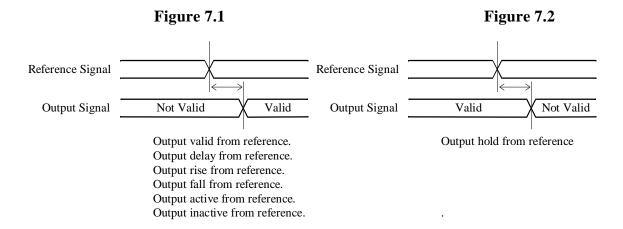

| Figure 7.1  | Timing Waveform                           | 169 |

| Figure 7.2  | Timing Waveform                           | 169 |

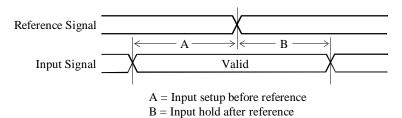

| Figure 7.3  | Timing Waveform                           | 169 |

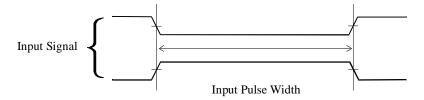

| Figure 7.4  | Timing Waveform                           |     |

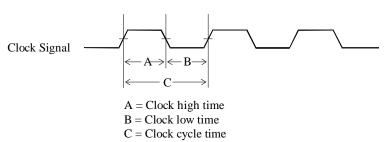

| Figure 7.5  | Timing Waveform                           | 169 |

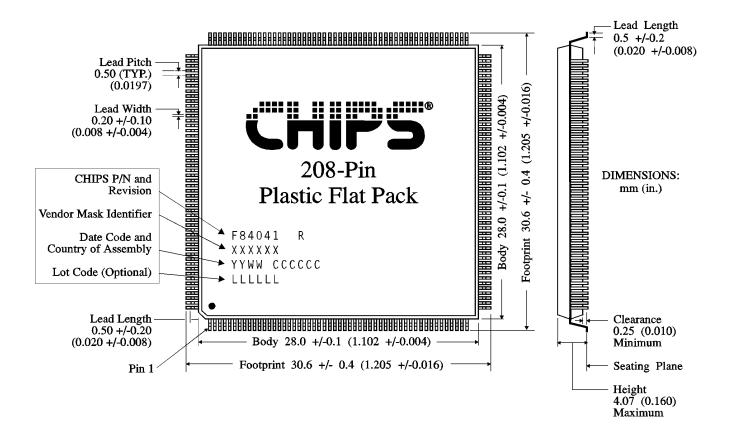

| Figure 8.1  | 84041 Packaging Dimensions                | 170 |

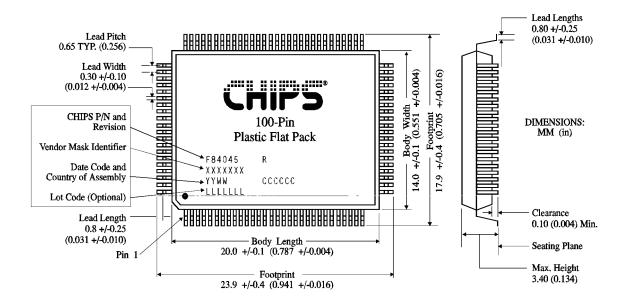

| Figure 8.2  | 84045 Packaging Dimensions                | 171 |

# **List of Tables**

| Table 2.1    | 84041 Pin List                                                | 15  |

|--------------|---------------------------------------------------------------|-----|

| Table 2.2    | 84045 Pin List                                                | 17  |

| Table 3.1    | 84041 and 84045 I/O Port Summary                              | 29  |

| Table 3.2    | 84041 and 84045 Configuration Register Summary                | 30  |

| Table 4.1    | CPU Chip Reset Signal Routing                                 | 69  |

| Table 5.1    | Clock Divider                                                 | 75  |

| Table 5.2    | GATEA20 & KBRESET Source.                                     | 76  |

| Table 5.3    | Bus Owner Indication                                          | 78  |

| Table 5.4    | I/O Decode Lower Bit Mask (A6:0)                              | 79  |

| Table 5.5    | I/O Decode Upper Bit Mask (A15:7)                             | 79  |

| Table 5.6    | DRAM Shadow Bit Encoding                                      | 81  |

| Table 5.7    | Programmable Memory Decode Size and Placement                 | 82  |

| Table 5.8    | User/SMM Space Shadow RAM Bits                                | 84  |

| Table 5.8.1  | CPU Address Bit Usage                                         | 90  |

| Table 5.9    | Cache Pin Usage                                               | 91  |

| Table 5.10   | Tag Bit Mapping                                               | 92  |

| Table 5.11   | Data SRAM Configurations                                      | 94  |

| Table 5.12   | TAG SRAM Configurations                                       | 94  |

| Table 5.13   | Suggested Cache Timing Modes and RAM Speeds                   | 94  |

| Table 5.14   | Cache Modes.                                                  | 102 |

| Table 5.15   | Cache Test Window Location                                    | 104 |

| Table 5.16   | 512K Cache Test Mode Mapping When In The Lower Meg            | 104 |

| Table 5.17   | RAS and CAS usage                                             | 107 |

| Table 5.18   | DRAM Block Starting Address                                   | 107 |

| Table 5.19   | DRAM Size Options                                             | 108 |

| Table 5.20   | CPU Address Assignments For Interleaving and Non-Interleaving |     |

| Table 5.21   | Address Multiplexing                                          | 110 |

| Table 5.22   | Staggered Refresh Set Assignment                              | 113 |

| Table 5.23   | Suggested DRAM Timing Modes                                   |     |

| Table 5.24   | Default signal states                                         | 118 |

| Table 5.25   | Programmable Timing Parameters                                |     |

| Table 5.26   | Determine Which Drive Is Active                               |     |

| Table 5.27   | Fast IDE Register Set                                         |     |

| Table 5.28:  | Drive Speed Selection                                         |     |

| Table 5.29:  | Register Settings for IDE Timing                              |     |

| Table 5.30:  | Programming for Standard IDE Modes                            |     |

| Table 5.30.1 | Typical Timing Parameters                                     |     |

| Table 5.31   | Multifunction Pin Function Programming                        |     |

| Table 5.32   | Multifunction Pin Programming Registers                       |     |

| Table 5.33   | SMM Status and Enable Registers                               |     |

| Table 5.34   | Activity Timer Selectable Functions                           |     |

| Table 5.34.1 | Time Base Selection                                           |     |

| Table 5.35   | CPU Slow Clock Programming                                    |     |

| Table 5.36   | SMM Timer Resolutions and Max Time-Outs                       |     |

| Table 5.37   | Event Functions                                               |     |

| Table 5.38   | External Pin Event Modes In Index Register 8Fh                |     |

| Table 5.39   | Event Fixed I/O Address Ranges                                | 132 |

| Table 5.40 | Selectable Ranges for Specific Events    | 133 |

|------------|------------------------------------------|-----|

| Table 5.41 | Power Management Configuration Registers |     |

| Table 5.42 | PLL Stabilization Delay Time             |     |

| Table 6.1  | Timer usage and setup                    |     |

| Table 6.2  | Real Time Clock/CMOS RAM addresses       |     |

| Table 6.3  | SIPC Port B bits                         | 161 |

### 1. Introduction

The CS4041 is the first product in the GreenCHIPS CHIPSet product portfolio of Chips and Technologies, Inc. It provides all of the system logic for implementing a high performance, Energy Star compliant 486 PC/AT design, while maintaining an extremely competitive cost structure. The powerful feature set includes the CHIPS "standard" system blocks and offers a new level of system integration while addressing the ever evolving requirements that the market place demands. It is 100% PC/AT compatible and directly supports the 486DX, 486DX2, 486DX4, 486SX and 486 derivatives that support the CPU write back cache architecture.

The high performance CHIPSet consists of the F84041 Systems Controller and F84045 GreenCHIPS IPC. The F84041 System Controller is packaged in a 208-pin PQFP and integrates the major system logic functions. Included in the F84041 is the CHIPS patented Page Interleave DRAM controller, high performance cache controller, VL local bus controller, ISA bus controller, power management module, a local bus IDE controller and fully compatible 8042 keyboard controller with PS/2 mouse support. The companion F84045 is packaged in a 100 pin PQFP and contains the industry standard Integrated Peripheral Controller (IPC) which includes the DMA controllers, timers, interrupt controllers and real time clock.

The enhanced feature set of GreenCHIPS DRAM and cache controllers are perfect for today's High Performance PC/AT designs. The page interleave DRAM controller offers high performance as well as extreme flexibility in supporting 486 memory subsystems. The DRAM controller supports up to eight banks of memory that can be configured with 256K, 1M, 4M or 16M memory devices. Page interleaving, timing modes, memory mix options, direct drive support and block by block parity support can be tuned to meet the most optimum requirements for the system design. In addition, the high performance secondary cache controller provides options that can be optimized for performance, cost or both. The direct mapped cache architecture employs internal comparators with external TAG and data SRAM that can operate in a writethrough or write-back mode. Cache sizes from 64K to 1M are supported with flexible single bank or dual bank support that allow flexible timing mode selection based on CPU speed and SRAM speed.

The "Green" in GreenCHIPS comes from the Power management support integrated in the CHIPSet. The CS4041 provides the perfect level of power management support for Energy Star compliant desktops. Included in the power management section is direct support for SMM operation and clock switching for the popular 486 derivatives. Two event timers, programmable I/O pins, I/O restart and programmable event detection provide a wide range of options for power management selection and customization.

The CS4041 provides new levels of integration in system logic CHIPSets by providing a local bus IDE interface and keyboard controller. The robust local bus IDE interface is decoupled from the AT state machine and does not use a VL local bus load. The interface is versatile enough to support up to eight IDE drives allowing each drive to have unique command settings. The result is the best performance for each drive type allowing significant performance gains over the standard ISA interface. This is accomplished without any compromise to the standard VL local bus.

### 1.1. CPUs Supported

- Intel 486 CPUs

- AMD 486 CPUs

- Cyrix 486 CPUs

- IBM 486 CPUs

- L1 (CPU) write back cache fully supported

- SMI support (both Intel and Cyrix)

- Clock Frequencies:

25MHz, 33MHz, 40MHz, 50MHz

### 1.2. External Chips

| Qty | TTL Parts      | Used For                      |  |  |  |  |  |  |

|-----|----------------|-------------------------------|--|--|--|--|--|--|

|     | Basic System   |                               |  |  |  |  |  |  |

| 3   | LS245          | A <-> SA & LA                 |  |  |  |  |  |  |

| 2   | LS245          | XD0:7 <-> SD0:7 & MA2:9 <->   |  |  |  |  |  |  |

|     |                | SD8:15                        |  |  |  |  |  |  |

| 1   | F244           | Clock buffer                  |  |  |  |  |  |  |

| 1   | F00            | Miscellaneous                 |  |  |  |  |  |  |

|     | Add for Cache: |                               |  |  |  |  |  |  |

| 2   | F244           | Cache address                 |  |  |  |  |  |  |

| 1   | F08            | BE# and W/R# combining        |  |  |  |  |  |  |

|     | Add for IDE:   |                               |  |  |  |  |  |  |

| 2   | LS245          | Data bus buffers              |  |  |  |  |  |  |

| 1   | LS244          | Control Signal Buffers        |  |  |  |  |  |  |

|     | DRAM Buffers   |                               |  |  |  |  |  |  |

| 0   |                | For 2 banks                   |  |  |  |  |  |  |

| 4   | F244           | For full complement of DRAMs. |  |  |  |  |  |  |

|     |                | Buffering based on loading.   |  |  |  |  |  |  |

Revision 1.0 2/10/95 12 Preliminary CS4041

### 2. Pinouts

The CS4041 CHIPSet is comprised of two chips, the 84041 and the 84045. Following the 84041 and 84045 pinout diagrams are the pin descriptions.

Figure 2.1: 84041 Pinout

Revision 1.0 2/10/95 13 Preliminary CS4041

**Figure 2.2: 84045 Pinout**

# 2.1. Pin Descriptions

### **2.2.** 84041 Pin Overview

The 84041 table below lists the pins by signal names. The detailed pin functional descriptions for the 84041 follow the pin list.

**Table 2.1: 84041 Pin List**

|                   |     |            |          |          |          | Ext. Load           | External    |                                   |

|-------------------|-----|------------|----------|----------|----------|---------------------|-------------|-----------------------------------|

| Signal            | Qty | In/out     | Driver   | Iol (mA) | Іон (тА) | C <sub>L</sub> (pF) | Pull-up (Ω) | Comments                          |

| CLKIN             | 1   | IN         | -        | -        | -        | -                   | -           | From oscillator                   |

| CLK2OUT           | 1   | OUT        | TS       | 8        | -2       | 30                  | -           | 4041 CLK2                         |

| SCLKOUT           | 1   | OUT        | TS       | 8        | -2       | 85                  | -           | 4041, 4045, VL (usually buffered) |

| CPUCLK            | 1   | OUT        | TS       | 8        | -2       | 50                  | -           | CPU (usually buffered             |

| STPCLK#           | 1   | OUT        | TS       | 4        | -1       | 30                  | -           | CPU                               |

| SUSPA#            | 1   | IN         | -        | _        | _        | _                   | _           | Cyrix CPU                         |

| CLK2              | 1   | IN         | -        | _        | -        | -                   | -           | Oscillator circuit                |

| SCLK              | 1   | IN         | -        | -        | -        | -                   | -           | Oscillator circuit                |

| CWS#              | 1   | IN         | -        | _        | -        | -                   | -           | Unbuffered clock                  |

| BUSCLK            | 1   | OUT        | TS       | 4        | -1       | 50                  | _           | Buffer                            |

| SYSRESET          | 1   | IN         | _        | -        | -        | _                   | _           | IPC                               |

| HLDA              | 1   | IN         | -        | _        | -        | _                   | _           | CPU                               |

| DGNT#             | 1   | IN         | -        | -        | -        | _                   | _           | IPC                               |

| MASTER#           | 1   | IN         | _        | _        | _        | _                   | 300         | ISA Bus                           |

| SMIACT# / SMIADS# | 1   | IN         | _        |          | _        | <del></del>         | 10K         | CPU                               |

| ADS#              | 1   | I/O        | TS       | 4        | -1       | 75                  | 10K         | CPU, loc. bus dev.                |

| W / R#            | 1   | I/O        | TS       | 4        | -1       | 75                  | 10K         | CPU, loc. bus dev.                |

| D / C#            | 1   | I/O        | TS       | 4        | -1       | 75                  |             | CPU, loc. bus dev.                |

|                   |     |            |          |          |          |                     | -           | 7                                 |

| M / IO#           | 1   | I/O<br>I/O | TS       | 4        | -1<br>-1 | 75<br>75            | -<br>10K    | CPU, loc. bus dev.                |

| RDY#              | -   |            | TS<br>TS | 4        |          | 75                  |             | CPU, loc. bus dev.                |

| BRDY#             | 1   | I/O        |          |          | -1       |                     | 10K         | CPU, loc. bus dev.                |

| KEN#              | 1   | OUT        | TS       | 4        | -1       | 30                  | -           | CPU                               |

| FLUSH#            | 1   | OUT        | TS       | 4        | -1       | 30                  | -           | CPU                               |

| BLAST#            | 1   | I/O        | TS       | 4        | -1       | 75                  | - 1077      | CPU, loc. bus dev.                |

| EADS#             | 1   | I/O        | TS       | 4        | -1       | 75                  | 10K         | CPU, loc. bus dev.                |

| HITM#             | 1   | IN         | -        | -        | -        | -                   | 10K         | CPU                               |

| WBACK#            | 1   | OUT        | TS       | 4        | -1       | 100                 | -           | To 4045 & VL slots                |

| BALE              | 1   | OUT        | TS       | 24       | -4       | 240                 | -           | ISA Bus                           |

| MEMR#             | 1   | I/O        | TS       | 24       | -3       | 240                 | 10K         | ISA Bus                           |

| MEMW#             | 1   | I/O        | TS       | 24       | -3       | 240                 | 10K         | ISA Bus                           |

| IOR#              | 1   | I/O        | TS       | 24       | -3       | 240                 | 10K         | ISA Bus                           |

| IOW#              | 1   | I/O        | TS       | 24       | -3       | 240                 | 10K         | ISA Bus                           |

| IOCHRDY           | 1   | I/O        | OC       | 24       | -        | 240                 | 1K          | ISA Bus                           |

| 0WS#              | 1   | IN         | -        | -        | -        | -                   | 300         | ISA Bus                           |

| MEMCS16#          | 1   | I/O        | OC       | 24       | -        | 240                 | 300         | ISA Bus                           |

| IOCS16#           | 1   | IN         | -        | -        | -        | -                   | 300         | ISA Bus                           |

| BE0-3#            | 4   | I/O        | TS       | 4        | -1       | 75                  | -           | CPU, loc. bus dev.                |

| A2-9              | 8   | IN         | -        | -        | -        | -                   | -           | CPU, loc. bus dev., AT buffers    |

| A10:16            | 7   | I/O        | TS       | 4        | -1       | 75                  | -           | CPU, loc. bus dev., AT buffers    |

| A17:23            | 7   | IN         | -        | -        | -        | -                   | -           | CPU, loc. bus dev., AT buffers    |

| A24:27, A31       | 5   | I/O        | TS       | 4        | -1       | 75                  | -           | CPU, loc. bus dev., AT buffers    |

| SBHE#             | 1   | I/O        | TS       | 24       | -4       | 240                 | -           | ISA Bus                           |

| XA0-1             | 2   | I/O        | TS       | 4        | -1       | 50                  | -           | F245                              |

| ROMCS#            | 1   | OUT        | TS       | 4        | -1       | 50                  | -           | ROM chip, 8042CS                  |

| LDEV0:2#          | 3   | IN         | -        | -        | -        | -                   | 10K         | From VL-Bus slots                 |

| CA2               | 1   | OUT        | TS       | 8        | -2       | 75                  | -           | 8 cache RAMs                      |

| CA3A,B            | 2   | OUT        | TS       | 4        | -1       | 50                  | -           | 4 cache RAMs                      |

| CRDA,B            | 2   | OUT        | TS       | 4        | -1       | 50                  | -           | 4 cache RAMs                      |

| CWEA#,B           | 2   | OUT        | TS       | 4        | -1       | 50                  | -           | 4 cache RAMs                      |

| TAGWE#            |     | OUT        | TS       | 4        | -1       | 50                  | İ _         | 3 tag RAMs                        |

|                   | 1   | 001        | 1.5      | -        | -1       | 50                  | _           | J tag KAWIS                       |

Revision 1.0 2/10/95 15 Preliminary CS4041

Table 2.1: 84041 Pin List (continued)

| Signal        | Qty | In/out | driver | Iol (mA) | Іон (mA) | Ext. Load           | External    | Comments                 |

|---------------|-----|--------|--------|----------|----------|---------------------|-------------|--------------------------|

|               |     |        |        |          |          | C <sub>L</sub> (pF) | Pull-up (Ω) |                          |

| RAS0-7#       | 8   | OUT    | TS     | 16       | -3       | 120                 | -           | 12 DRAMs                 |

| CAS0-3#       | 4   | OUT    | TS     | 16       | -3       | 65                  | -           | 6 DRAMs                  |

| DWE#          | 1   | OUT    | TS     | 16       | -3       | 240                 | -           | 24 DRAMs                 |

| MA0-11        | 12  | I/O    | TS     | 16       | -3       | 200                 | -           | 24 DRAMs                 |

| D0:31         | 32  | I/O    | TS     | 4        | -1       | 75                  | -           | CPU, DRAMs, local bus    |

| DP0:3         | 4   | I/O    | TS     | 4        | -1       | 65                  | -           | CPU, DRAMs               |

| XD0:7         | 8   | I/O    | TS     | 4        | -1       | 65                  | -           | 8042, ROM, LS245, 4045   |

| SDIR0:1       | 2   | OUT    | TS     | 4        | -1       | 40                  | -           | F245                     |

| SDEN#         | 1   | OUT    | TS     | 4        | -1       | 40                  | -           | F245, inverter           |

| IOCHCK#       | 1   | IN     | -      |          |          |                     | 4.7K        | ISA Bus                  |

| NMI           | 1   | OUT    | TS     | 4        | -1       | 30                  | -           | CPU                      |

| SMI#          | 1   | I/O    | TS     | 4        | -1       | 30                  | -           | CPU                      |

| INTR          | 1   | IN     | -      | -        | -        | -                   | -           | 4045                     |

| IDEIOR#       | 1   | OUT    | TS     | 4        | -1       | 40                  | -           | Buffer                   |

| IOEIOW#       | 1   | OUT    | TS     | 4        | -1       | 40                  | -           | Buffer                   |

| IDECS0,1#     | 2   | OUT    | TS     | 4        | -1       | 40                  | -           | Buffer                   |

| IDEEN#        | 1   | OUT    | TS     | 4        | -1       | 40                  | -           | Buffer enables           |

| FDD7          | 1   | IN     | -      | -        | -        | -                   | -           | SD7                      |

| LIN           | 1   | IN     | -      | -        | -        | -                   | -           | IPC                      |

| LOUT          | 1   | OUT    | TS     | 4        | -1       | 30                  | -           | IPC                      |

| KBCLK, KBDATA | 2   | I/O    | OC     | 4        | -        | 240                 | 4.7K        | Keyboard connector, etc. |

| MCLK, MDATA   | 2   | I/O    | OC     | 4        | -        | 240                 | 4.7K        | Mouse connector          |

| GPIOA         | 1   | IN     | -      | -        | -        | -                   | -           |                          |

| GPIOB:D       | 3   | I/O    | TS     | 4        | -1       | 50                  | -           |                          |

| VCC           | 8   |        |        |          |          |                     |             |                          |

| GND           | 15  |        |        |          |          |                     |             |                          |

| Total         | 208 |        |        |          |          |                     |             |                          |

Driver types: TS = tri-state, OC = open collector.

### 2.3. 84045 Pin Overview

The 84045 table below lists the pins by signal names. The detailed pin functional descriptions for the 84045 follows the pin list.

**Table 2.2: 84045 Pin List**

| Signal                 | Qty  | In/out | driver | Iol (mA) | Ioн (mA) | Ext. Load           | External        | Comments                                   |

|------------------------|------|--------|--------|----------|----------|---------------------|-----------------|--------------------------------------------|

|                        |      |        |        |          |          | C <sub>L</sub> (pF) | Pull-up (Ω<br>) |                                            |

| 14MX1                  | 1    | IN     | -      | -        | -        | -                   | -               | 14.31818MHz crystal input                  |

| 14MX2                  | 1    | OUT    | TP     | 2        | -1       | 50                  | -               | 14.31818MHz crystal output                 |

| SCLK                   | 1    | IN     | -      | -        | -        | -                   | -               | Oscillator circuit                         |

| PWRGOOD                | 1    | IN     | -      | -        | -        | -                   | -               | Power supply or PUC circuit                |

| CPURESET               | 1    | OUT    | TP     | 4        | -1       | 50                  | -               | CPU(s)                                     |

| SYSRESET               | 1    | OUT    | TP     | 8        | -2       | 50                  | -               | Coproc, 4025, buffer to ISA bus            |

| HOLD                   | 1    | OUT    | TP     | 4        | -1       | 30                  | -               | CPU(s)                                     |

| HLDA                   | 1    | IN     | -      | -        | -        | -                   | -               | CPU                                        |

| DGNT#                  | 1    | OUT    | TP     | 4        | -1       | 40                  | -               | 4041, one buffer direction                 |

| WBACK#                 | 1    | IN     | -      | -        | -        | -                   | -               | 4041                                       |

| LREQ0#                 | 1    | IN     | -      | -        | -        | -                   | 10K             | Local Master. Pull up if not used          |

| LGNT0#                 | 1    | OUT    | TP     | 4        | -1       | 50                  | -               | Local Master                               |

| MASTER#                | 1    | IN     | -      | -        | -        | -                   | 300             | ISA Bus                                    |

| REFRESH#               | 1    | I/O    | OC     | 24       | -        | 240                 | 300             | ISA Bus                                    |

| AEN                    | 1    | OUT    | TP     | 24       | -3       | 240                 | -               | ISA Bus                                    |

| TC                     | 1    | OUT    | TP     | 4        | -1       | 240                 | -               | ISA Bus                                    |

| DREQ0:3, 5:7           | 7    | IN     | -      | -        | -        | -                   | 10K             | ISA Bus                                    |

| DACK0:3, 5:7#          | 7    | OUT    | TP     | 4        | -1       | 240                 | -               | ISA Bus                                    |

| SLOW# / LREQ1#         | 1    | IN     | -      | -        | -        | -                   | 10K             | Turbo Button                               |

| FLUSH# / LGNT1#        | 1    | OUT    | TS     | 4        | -1       | 30                  | -               | CPU                                        |

| MEMR#, MEMW#           | 2    | OUT    | TS     | 24       | -3       | 240                 | 10K             | ISA Bus, 4041. Driven for DMA cycles only. |

| SMEMR#, SMEMW#         | 2    | OUT    | TP     | 24       | -3       | 240                 | -               | ISA Bus, 4041. Always driven.              |

| IOR#, IOW#             | 2    | I/O    | TS     | 24       | -3       | 240                 | 10K             | ISA Bus, 4041. Driven for DMA cycles only. |

| IOCHRDY                | 1    | I/O    | OC     | 24       | -        | -                   | 1K              | ISA Bus, 4041                              |

| SBHE#                  | 1    | OUT    | TS     | 24       | -3       | 240                 | -               | ISA Bus, 4041                              |

| SA0:7                  | 8    | I/O    | TS     | 24       | -3       | 240                 | -               | ISA Bus, F245                              |

| A8:9                   | 2    | I/O    | TS     | 8        | -2       | 65                  | -               | CPU, 4041                                  |

| SA17 / LREQ2#          | 1    | I/O    | TS     | 24       | -3       | 240                 | -               | ISA Bus / VL Master                        |

| SA18 / LGNT2#          | 1    | OUT    | TS     | 24       | -3       | 240                 | -               | ISA Bus / VL Master                        |

| SA19 / IOCS#           | 1    | I/O    | TS     | 24       | -3       | 240                 | -               | ISA Bus / I/O decode                       |

| A17:19                 | 3    | I/O    | TS     | 8        | -2       | 65                  | -               | CPU, 4041. Driven for DMA, in to gen SA.   |

| A20:23                 | 4    | I/O    | TS     | 8        | -2       | 65                  | -               | CPU, 4041. Driven for DMA.                 |

| A20M# / TEST#          | 1    | I/O    | TS     | 4        | -1       | 30                  | 10K             | CPU                                        |

| XD0:7                  | 8    | I/O    | TS     | 4        | -1       | 65                  | -               | 4041, LS244, 8042, ROM                     |

| IRQ1, 3:7, 9:11,14:15  | 11   | IN     | -      | -        | -        | -                   | -               | ISA Bus (IRQ1 from 8042)                   |

| IRQ12                  | 1    | I/O    | TS     | 4        | -1       | 240                 | -               | ISA Bus & internal mouse option            |

| INTR                   | 1    | OUT    | TP     | 4        | -1       | 30                  | -               | CPU                                        |

| FERR#/IRQ13            | 1    | IN     | -      | -        | -        | -                   | -               | CPU or coprocessor logic                   |

| IGNNE#/INTCLR#/RTCIRQ# | 1    | OUT    | TP     | 4        | -1       | 30                  | -               | CPU or coprocessor logic                   |

| SPKR                   | 1    | OUT    | TP     | 4        | -1       | 30                  | -               | Speaker buffer                             |

| 32KX1                  | 1    | IN     | -      |          | -        | -                   | -               | Crystal Circuit                            |

| 32KX2                  | 1    | OUT    | TP     | *        | *        | *                   | -               | Crystal Circuit                            |

| PSRSTB                 | 1    | IN     | -      | -        | -        | -                   | RC              | RC circuit                                 |

| LIN                    | 1    | IN     | -      | -        | -        | -                   | -               | 4041                                       |

| LOUT                   | 1    | OUT    | TP     | 4        | -1       | 30                  | -               | 4041                                       |

| VCC                    | 4    |        |        |          |          |                     |                 |                                            |

| GND                    | 6    |        |        |          |          |                     |                 |                                            |

| Total                  | 100  |        |        |          |          |                     |                 |                                            |

| - · · · · ·            | - 00 |        |        | L        |          |                     |                 | 1                                          |

<sup>\*</sup> Analog pin. Recommended external crystal circuit should be used (2 x 20 pF, 10K series, 10M  $\,\Omega$  biasing). TP = Totem-Pole, TS = Tri-State, OC = Open Collector.

Revision 1.0 2/10/95 17 Preliminary CS4041

### 2.4. 84041 Pin Descriptions

### **CLOCKs and RESET**

| CLKIN       | 14  | IN  | Input from Oscillator. Either 1x or 2x as determined by NMI at powerup (high for 1x, low for 2x). Used to create CLK2OUT, SCLKOUT and (optionally) BUSCLK. Also used as a time base for the power management timers.                                                                                                                                                                                                    |

|-------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK2OUT     | 205 | OUT | 2x system clock (when CLKIN is 2x). In full speed mode CLK2OUT is a buffered version of CLKIN. In slow mode it is the output of the clock divider. When CLKIN is 1x CLK2OUT will also be 1x, and will be at the same frequency and phase as SCLKOUT. In either mode it has a very low skew with respect to SCLKOUT and CPUCLK. It is externally fed back to CLK2 of the 4041, and any other logic requiring a 2x clock. |

| SCLKOUT     | 204 | OUT | The 1x system clock for everything except the CPU. This output buffered and fed back to SCLK of the 4041, goes to the 4045, and the VL-Bus. The unbuffered SCLKOUT is used as CWS#.                                                                                                                                                                                                                                     |

| SUSPA#      | 156 | IN  | Suspend Acknowledge from the Cyrix CPU. May be left floating if not used. Required only for Cyrix CPUs which contain a PLL. This pin is enabled with Configuration Register 38h bit 2.                                                                                                                                                                                                                                  |

| CPUCLK      | 203 | OUT | 1x CPU clock. This output is the same as SCLKOUT except that it may be stopped by the power management hardware.                                                                                                                                                                                                                                                                                                        |

| STPCLK#     | 2   | OUT | Stop Clock signal to the CPU. Used for S series CPUs to stop the clock between the CPU PLL and the CPU core. The 4041 will optionally drive this pin low before changing clock frequencies.                                                                                                                                                                                                                             |

| CLK2        | 15  | IN  | 2x clock input. Used for the DRAM state machine. It is also used as the source for the ISA bus clock divider.                                                                                                                                                                                                                                                                                                           |

| SCLK        | 17  | IN  | 1x clock input.                                                                                                                                                                                                                                                                                                                                                                                                         |

| CWS#        | 16  | IN  | Cache Write strobe. This is an advanced 1x clock used for the cache write strobe in order to meet the data hold time of the SRAMs. It is normally advanced by 3-5nS from SCLK.                                                                                                                                                                                                                                          |

| BUSCLK      | 207 | OUT | ISA bus clock. Generated by dividing the CLKIN pin down by a variety of factors. BUSCLK should be driven onto the ISA bus through a non-inverting buffer. (BALE is generated during the low phase of BUSCLK).                                                                                                                                                                                                           |

| SYSRESET    | 53  | IN  | System reset from the 4045.                                                                                                                                                                                                                                                                                                                                                                                             |

| Arbitration | n   |     |                                                                                                                                                                                                                                                                                                                                                                                                                         |

| HLDA        | 51  | IN  | CPU Hold Acknowledge. When low, indicates that the CPU has control of the local bus. When high, either a local master, the DMA controller, or an ISA master has the bus. The 4041 chip generates parity for DRAM write cycles when this pin is high. Cache line fills are only done when HLDA is low. The DRAM controller may switch timing modes based on HLDA to provide relaxed timing for alternate masters.        |

| DGNT#       | 50  | IN  | DMA controller grant. When low, indicates that either the DMA controller or an ISA bus master has control of the bus. The 4041 becomes an ISA slave and floats the ISA bus commands when this signal is low.                                                                                                                                                                                                            |

Revision 1.0 2/10/95 18 Preliminary CS4041

SMIACT# / SMIADS#

MASTER# 97 IN ISA bus master signal. Indicates that an ISA master has the bus. The 4041 uses this to determine the difference between DMA and ISA master cycles. It is used in determining the timing for IOCHRDY generation.

### **CPU & Local Bus control signals**

|         | 92  | IN  | Indicates SMM memory accesses. The function depends on the CPU type. For Intel SMM it is an SMIACT# status signal. For Cyrix SMM it is the ADS# for SMM cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADS#    | 19  | I/O | Address Strobe. Input for CPU and local master cycles, output for DMA and ISA master cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| W / R#  | 21  | I/O | Write/Read status signal. Input for CPU and local master cycles, output for DMA and ISA master cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| D / C#  | 22  | I/O | Data/Code status signal. Input for CPU and local master cycles, output for DMA and ISA master cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| M / IO# | 20  | I/O | Memory/IO status signal. Input for CPU and local master cycles, output for DMA and ISA master cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RDY#    | 27  | I/O | Non Burst ready. Output when 4041 is a slave. Input from a local bus slave or external cache controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| BRDY#   | 26  | I/O | Burst Ready. Output when 4041 is a slave. Input from a local bus slave or external cache controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| KEN#    | 23  | OUT | Cache Enable to the CPU. Always driven. Only local DRAM is cached in the CPU. Certain areas may be marked non-cacheable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| FLUSH#  | 84  | OUT | Flush L1 cache. May be used when entering SMM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BLAST#  | 25  | I/O | Burst Last. Driven (low) for DMA and ISA master cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| EADS#   | 24  | I/O | External Address Strobe. Used to snoop and invalidate the 486 cache on DMA and ISA master memory cycles. Floated when a local master has the bus. Optionally driven active for writes to write protected memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| HITM#   | 52  | IN  | Hit Modified. Input from the CPU indicating that the result of the snoop is a dirty cache line, i.e., the CPU cache contains the only valid copy of data that an alternate master is attempting to read. See also WBACK# below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| WBACK#  | 114 | OUT | Writeback. Output to the 4045 and VL bus slots based on the HITM# input, indicating that the CPU needs to perform an L1 cache writeback operation before an alternate master receives the data that the master is attempting to read. The 4041 determines when to allow the writeback to occur in relation to other system activity. The bus cycle from an alternate master will be aborted to allow the CPU to write back the data. When the 4041 has control of the local bus (ISA masters or DMA) it will back off the bus while WBACK# is low. As required by VL bus protocol, a local bus master (LBM) must be capable of aborting a cycle (without RDY# or BRDY#), then restarting the cycle again after the writeback operation is completed. In response to WBACK#, the 4045 drops HOLD long enough to give control the CPU, then re-asserts HOLD and gives control back to the alternate master after the CPU has finished the writeback operation and re-asserted HLDA. |

Revision 1.0 2/10/95 19 Preliminary CS4041

| ISA | Bus |

|-----|-----|

|     |     |

| BALE     | 117 | OUT | Buffered Address Latch Enable. Direct drive of the ISA bus.                                                                                                                                                       |

|----------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEMR#    | 109 | I/O | Memory Read Strobe. Direct drive of the IS A bus. Output when HLDA or LGNT# are low. Input when they are both high.                                                                                               |

| MEMW#    | 108 | I/O | Memory Write Strobe. Direct drive of the ISA bus. Output when HLDA or LGNT# are low. Input when they are both high.                                                                                               |

| IOR#     | 116 | I/O | I/O Read Strobe. Direct drive of the ISA bus. Output when HLDA or LGNT# are low. Input when they are both high.                                                                                                   |

| IOW#     | 115 | I/O | I/O Write Strobe. Direct drive of the ISA bus. Output when HLDA or LGNT# are low. Input when they are both high.                                                                                                  |

| IOCHRDY  | 91  | I/O | ISA bus ready. Output when an ISA slave (DMA and ISA master accesses to local DRAM or local bus slaves). Open collector. Input for CPU or local master accesses to the ISA bus.                                   |

| 0WS#     | 90  | IN  | ISA bus Zero wait state signal. An ISA bus slave will drive this signal low when a memory command falls to force a 0 wait state cycle. It may also be used to force a 2 wait state cycle for 8 bit memory or I/O. |

| MEMCS16# | 89  | I/O | Output when an ISA slave (DMA and ISA master accesses to local DRAM or local bus slaves). Open collector. Input for CPU or local master accesses to the ISA bus.                                                  |

| IOCS16#  | 93  | IN  | Input for CPU or local master accesses to the ISA bus.                                                                                                                                                            |

|          |     |     |                                                                                                                                                                                                                   |

### Address

| BE0:3# | 160, 159, 158, 157 |                                                                                                                                           |  |  |

|--------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|        | I/O                | Byte enables. Input for CPU or local master accesses to the ISA bus. Output for DMA or ISA master cycles. Generated from XA0:1 and SBHE#. |  |  |

| SBHE#  | 107 I/O            | ISA Bus BHE#. Output for CPU or local master accesses to the ISA bus. Input for DMA or ISA master cycles.                                 |  |  |

| XA0:1  | 106, 105           | I/O Output for CPU or local master accesses to the ISA bus. Input for DMA or ISA master cycles.                                           |  |  |

| A2:9   | 195, 194, 193,     | 192, 191, 185, 184, 183                                                                                                                   |  |  |

|        | IN                 | Local Bus Address bus. Always inputs.                                                                                                     |  |  |

| A10:16 | 182, 181, 180,     | 177, 176, 175, 174                                                                                                                        |  |  |

|        | I/O                | Local Bus Address bus. Output for DMA cycles. A10:16 of the DMA address is sent on XD0:6 from the 4045 and latched in the 4041.           |  |  |

| A17:23 | 173, 172, 171,     | 169, 168, 167, 166                                                                                                                        |  |  |

|        | IN                 | Local Bus Address bus. Always inputs.                                                                                                     |  |  |

Revision 1.0 2/10/95 20 Preliminary CS4041

| A24:27, A31 | 165, 164, 163, 162, 161 |

|-------------|-------------------------|

|             |                         |

I/O Local bus address. Driven low for DMA and ISA master cycles.

ROMCS# / KBCS#

OUT Logical OR of the ROM chip select and 8042 chip select. The 8042 chip select is active for I/O ports 60 and 64. The ROM chip select is programmable.

LDEV0:2# 85,86,87 IN Local Device. A local bus slave or cache controller drives these signals

IN Local Device. A local bus slave or cache controller drives these signals low to indicate that it will handle the cycle. This signal is sampled either at the end of the first or second T2. LDEV1# and LDEV2# may be redefined as other inputs.

They are disabled at power up. LDEV0# is enabled at power up.

### **Cache Controller**

| CA2         | 7       | OUT       | Cache address bit 2 for a single bank cache. Upper most data SRAM address bit (A15,16,17,18,or 19) for a double bank cache. |

|-------------|---------|-----------|-----------------------------------------------------------------------------------------------------------------------------|

| CA3A, CA3B  | 8, 9    | OUT       | Cache address bit 3 for each bank of a double bank cache. CA3A used for a single bank.                                      |

| CRDA#, CRDB | #       | 6, 5      | OUT Cache Read strobe for each bank of a double bank cache. CRDA# used for a single bank.                                   |

| #CWEA, CWEI | 3#      | 11, 10    | OUT Cache Write strobe for each bank of a double bank cache. CRDA# used for a single bank. Generated from CWS#.             |

| TAGWE#      | 12      | OUT       | Tag Write enable. Driven low during L2 read miss cycles and when changing the dirty bit from clean to dirty.                |

| TAG0:10     | 201, 20 | 0, 199, 1 | 98, 197, 196, 190, 189, 188, 187, 186                                                                                       |

I/O Tag RAM bits. TAG0 is the dirty bit. 8, 9, and 11 bit tags are supported. TAG0:7 is always used for 8 bit tag, TAG0:8 for 9 bit tag. Unused bits must be pulled up.

### **DRAM Controller**

RAS0:7# 151, 150, 149, 148, 155, 154, 153, 152

OUT RAS for each of 8 DRAM banks. Direct Drive.

CAS0:3# 146, 145, 143, 142

OUT CAS0:3 for each byte of DRAM Direct drive for up to 2 banks of DR AM.

DWE# 141 OUT DRAM write enable. Direct drive for 2 banks of DRAM. Also used to control the

direction of external DRAM data buffers if used.

MA0:1 140, 139

MA2:9/XD8:15 138, 137, 136, 132, 131, 130, 129, 128

MA10:11 135, 134

I/O DRAM address/upper data bus. Direct drive for up to 2 banks of DRAM. During ISA cycles MA2:9 become XD8:15 respectively (the upper byte of ISA bus data). They are buffered with a 245 to generate SD8:15. MA0:1 and 10:11 are output only.

Revision 1.0 2/10/95 21 Preliminary CS4041

# **Data Bus**

| D0:7    | 29, 30, 31, 32, 33, 35, 36, 37                                                                                                                                                               |                 |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|