intersil

#### PRELIMINARY

Data Sheet

March 2001 File Number 8010

### Wireless LAN Integrated Medium Access Controller with Baseband Processor with Mini-PCI

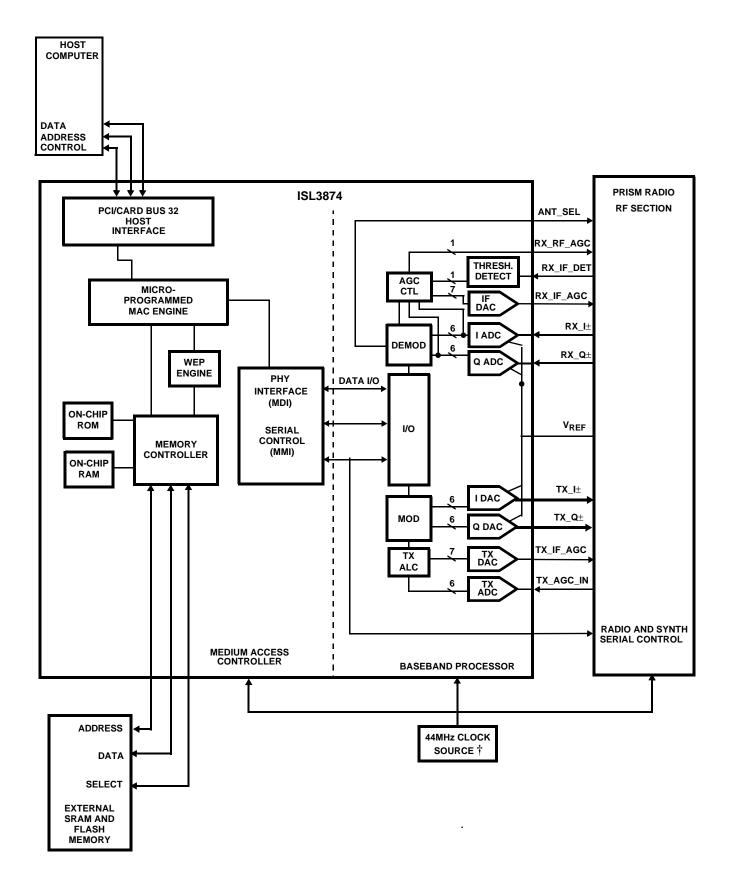

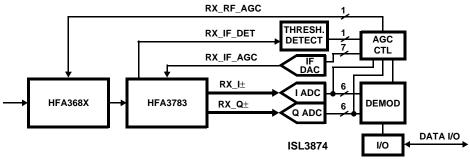

The Intersil ISL3874 Wireless LAN Integrated Medium Access Controller with Integrated Baseband Processor is part of the PRISM® 2.4GHz radio

chip set. The ISL3874 directly interfaces with the Intersil's IF QMODEM (HFA3783). Adding Intersil's RF/IF Converter (ICW3685) and Intersil's Power Amp (HFA3983/4/5) offers the designer a complete end-to-end WLAN Chip Set solution. Protocol and PHY support are implemented in firmware thus, supporting customization of the WLAN solution.

Firmware implements the full IEEE 802.11 Wireless LAN MAC protocol. It supports BSS and IBSS operation under DCF, and operation under the optional Point Coordination Function (PCF). Low level protocol functions such as RTS/CTS generation and acknowledgment, fragmentation and de-fragmentation, and automatic beacon monitoring are handed without host intervention. Active scanning is performed autonomously once initiated by host command. Host interface command and status handshakes allow concurrent operations from multi-threaded I/O drivers. Additional firmware functions specific to access point applications are also available.

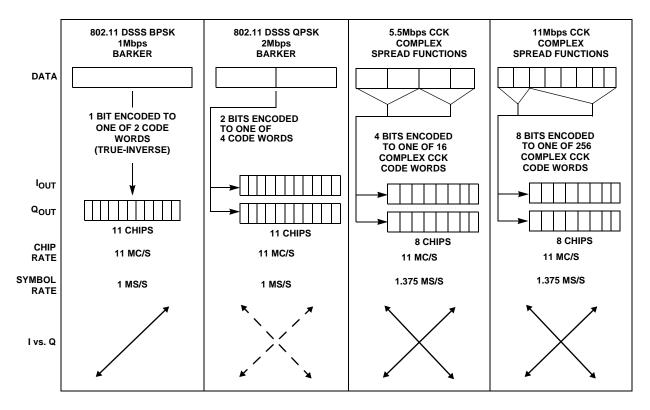

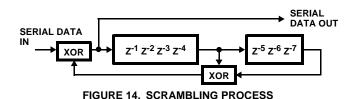

The ISL3874 has on-board A/Ds and D/A for analog I and Q inputs and outputs, for which the HFA3783 IF QMODEM is recommended. Differential phase shift keying modulation schemes DBPSK and DQPSK, with data scrambling capability, are available along with Complementary Code Keying to provide a variety of data rates. Both Receive and Transmit AGC functions with 7-bit AGC control obtain maximum performance in the analog portions of the transceiver.

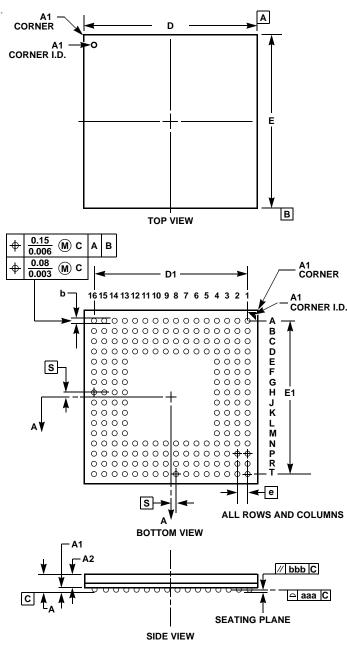

Built-in flexibility allows the ISL3874 to be configured through a general purpose control bus, for a range of applications. The ISL3874 is housed in a thin plastic BGA package suitable for mini PCI board applications.

The ISL3874 is designed to provide maximum performance with minimum power consumption. External pin layout is organized to provide optimal PC board layout to all user interfaces including mini PCI.

### Features

- Start up modes allow the mini PCI Card Information Structure to be initialized from a serial EEPROM. This Allows Firmware to be Downloaded from the Host, Eliminating the Parallel Flash Memory Device

- Firmware Can Be Loaded from Serial Flash Memory

- Zero Glue Connection to 16-Bit Wide SRAM Devices

- Low Frequency Crystal Oscillator to Maintain Time and Allow Baseband Clock Source to Power Off During Sleep Mode

- High Performance Internal WEP Engine

- Debug Mode Support Tracing Execution from On-Chip Memory

- Programmable MBUS Cycle Extension Allows Accessing of Slow Memory Devices without Slowing the Clock

- Complete DSSS Baseband Processor

- RAKE Receiver with Decision Feedback Equalizer

- Processing Gain.....FCC Compliant

- Programmable Data Rate ..... 1, 2, 5.5, and 11Mbps

- Ultra Small Package.....14mm x 14mm

- Modulation Methods..... DBPSK, DQPSK, and CCK

- Supports Full or Half Duplex Operations

- On-Chip A/D and D/A Converters for I/Q Data (6-Bit, 22MSPS), AGC, and Adaptive Power Control (7-Bit)

- Targeted for Multipath Delay Spreads 125ns at 11Mbps, 250ns at 5.5Mbps

- Supports Short Preamble and Antenna Diversity

### Applications

- Enterprise WLAN Systems

- PCI Card Wireless LAN Adapters

- PCN / Wireless PBX / Wireless Local Loop

- High Data Rate Wireless LAN Systems Targeting IEEE 802.11b Standard

- Wireless LAN Access Points and Bridge Products

- Spread Spectrum WLAN RF Modems

- TDMA or CSMA Packet Protocol Radios

### **Ordering Information**

| PART<br>NUMBER | TEMP.<br>RANGE ( <sup>o</sup> C) | PACKAGE         | PART<br>NUMBER  |

|----------------|----------------------------------|-----------------|-----------------|

| ISL3874IK      | -40 to 85                        | 192 BGA         | V192.14x14      |

| ISL3874IK96    | -40 to 85                        | Tape and Reel 1 | 1000 Units/Reel |

PRISM® is a registered trademark of Intersil Americas Inc. PRISM and design is a trademark of Intersil Americas Inc.

### Simplified Block Diagram

# ISL3874 Signal Descriptions

#### TABLE 1. HOST INTERFACE PINS

| PIN NAME | PIN<br>NUMBER | PIN I/O TYPE        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                            |  |

|----------|---------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| HAD31    | A8            | 5V Tol, CMOS, BiDir | PCI address/data bus bit 31. These signals make up the multiplexed PCI address and data bus on the primary interface. During the address phase of a primary bus PCI cycle, HAD31-HAD0 contain a 32-bit address or other destination information. During the data phase, HAD31-HAD0 contain data.                                                                                       |  |

| HAD30    | A9            | 5V Tol, CMOS, BiDir | PCI address/data bus bit 30.                                                                                                                                                                                                                                                                                                                                                           |  |

| HAD29    | C8            | 5V Tol, CMOS, BiDir | PCI address/data bus bit 29.                                                                                                                                                                                                                                                                                                                                                           |  |

| HAD28    | A10           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 28.                                                                                                                                                                                                                                                                                                                                                           |  |

| HAD27    | B9            | 5V Tol, CMOS, BiDir | PCI address/data bus bit 27.                                                                                                                                                                                                                                                                                                                                                           |  |

| HAD26    | B10           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 26.                                                                                                                                                                                                                                                                                                                                                           |  |

| HAD25    | C9            | 5V Tol, CMOS, BiDir | PCI address/data bus bit 25.                                                                                                                                                                                                                                                                                                                                                           |  |

| HAD24    | A11           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 24.                                                                                                                                                                                                                                                                                                                                                           |  |

| HAD23    | B11           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 23.                                                                                                                                                                                                                                                                                                                                                           |  |

| HAD22    | B12           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 22.                                                                                                                                                                                                                                                                                                                                                           |  |

| HAD21    | A12           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 21.                                                                                                                                                                                                                                                                                                                                                           |  |

| HAD20    | A13           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 20.                                                                                                                                                                                                                                                                                                                                                           |  |

| HAD19    | C12           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 19.                                                                                                                                                                                                                                                                                                                                                           |  |

| HAD18    | A14           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 18.                                                                                                                                                                                                                                                                                                                                                           |  |

| HAD17    | C13           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 17.                                                                                                                                                                                                                                                                                                                                                           |  |

| HAD16    | C14           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 16.                                                                                                                                                                                                                                                                                                                                                           |  |

| HAD15    | E14           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 15.                                                                                                                                                                                                                                                                                                                                                           |  |

| HAD14    | E15           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 14.                                                                                                                                                                                                                                                                                                                                                           |  |

| HAD13    | F16           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 13.                                                                                                                                                                                                                                                                                                                                                           |  |

| HAD12    | F15           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 12.                                                                                                                                                                                                                                                                                                                                                           |  |

| HAD11    | F14           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 11.                                                                                                                                                                                                                                                                                                                                                           |  |

| HAD10    | G16           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 10.                                                                                                                                                                                                                                                                                                                                                           |  |

| HAD9     | G15           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 9.                                                                                                                                                                                                                                                                                                                                                            |  |

| HAD8     | G14           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 8.                                                                                                                                                                                                                                                                                                                                                            |  |

| HAD7     | H15           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 7.                                                                                                                                                                                                                                                                                                                                                            |  |

| HAD6     | G13           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 6.                                                                                                                                                                                                                                                                                                                                                            |  |

| HAD5     | J15           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 5.                                                                                                                                                                                                                                                                                                                                                            |  |

| HAD4     | J14           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 4.                                                                                                                                                                                                                                                                                                                                                            |  |

| HAD3     | K14           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 3.                                                                                                                                                                                                                                                                                                                                                            |  |

| HAD2     | K15           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 2.                                                                                                                                                                                                                                                                                                                                                            |  |

| HAD1     | L14           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 1.                                                                                                                                                                                                                                                                                                                                                            |  |

| HAD0     | L16           | 5V Tol, CMOS, BiDir | PCI address/data bus bit 0.                                                                                                                                                                                                                                                                                                                                                            |  |

| HBE3     | C10           | 5V Tol, CMOS, BiDir | PCI bus commands and byte enables. These signals are multiplexed on the same PCI terminals. During the address phase of a primary bus PCI cycle, HBE3-HBE0 define the bus command. During the data phase, this 4-bit bus is used as byte enables. The byte enables determine which byte paths of the full 32-bit data bus carry meaningful data. HBE3 applies to byte 3 (HAD31-HAD24). |  |

| HBE2     | B14           | 5V Tol, CMOS, BiDir | PCI bus commands and byte enables. HBE2 applies to byte 2 (HAD23-HAD16).                                                                                                                                                                                                                                                                                                               |  |

| HBE1     | E16           | 5V Tol, CMOS, BiDir | PCI bus commands and byte enables. HBE1 applies to byte 1 (HAD15-HAD8).                                                                                                                                                                                                                                                                                                                |  |

#### TABLE 1. HOST INTERFACE PINS (Continued)

| PIN NAME | PIN<br>NUMBER | PIN I/O TYPE              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|---------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HBE0     | H16           | 5V Tol, CMOS, BiDir       | PCI bus commands and byte enables. HBE0 applies to byte 0 (HAD7-HAD0).                                                                                                                                                                                                                                                                                                                                      |

| HINTA    | C6            | CMOS, Output              | PCI Bus Interrupt A                                                                                                                                                                                                                                                                                                                                                                                         |

| HRESET   | D6            | 5V Tol, CMOS, Input       | PCI reset.                                                                                                                                                                                                                                                                                                                                                                                                  |

| HFRAME   | B15           | 5V Tol, BiDir             | PCI cycle frame. FRAME is driven by the initiator of a bus cycle. FRAME is asserted to indicate that a bus transaction is beginning, and data transfers continue while this signal is asserted. When FRAME is deasserted, the PCI bus transaction is in the final data phase.                                                                                                                               |

| HIRDY    | A15           | 5V Tol, CMOS, BiDir       | PCI initiator ready. HIRDY indicates the PCI bus initiators ability to complete the current data phase of the transaction. A data phase is completed on a rising edge of PCLK where both HIRDY and HTRDY are asserted. Until HIRDY and HTRDY are both sampled asserted, wait states are inserted.                                                                                                           |

| HTRDY    | A16           | 5V Tol, CMOS, BiDir       | PCI target ready. HTRDY indicates the primary bus targets ability to complete the current data phase of the transaction. A data phase is completed on a rising edge of PCLK when both HIRDY and HTRDY are asserted. Until both HIRDY and HTRDY are asserted, wait states are inserted.                                                                                                                      |

| HREQ     | B7            | CMOS, Output              | PCI bus request. HREQ is asserted by the ISL3874 to request access to the PCI bus as an initiator.                                                                                                                                                                                                                                                                                                          |

| HSERR    | B16           | CMOS, Output              | PCI system error. HSERR is an output that is pulsed from the ISL3874 when enabled through the command register indicating a system error has occurred. The ISL3874 need not be the target of the PCI cycle to assert this signal. When HSERR is enabled in the control register, this signal also pulses, indicating that an address parity error has occurred on a CardBus interface.                      |

| HSTOP    | C16           | 5V Tol, CMOS, BiDir       | PCI cycle stop signal. HSTOP is driven by a PCI target to request the initiator to stop the current PCI bus transaction. HSTOP is used for target disconnects and is commonly asserted by target devices that do not support burst data transfers.                                                                                                                                                          |

| HDEVSEL  | D15           | 5V Tol, CMOS, BiDir       | PCI device select. The ISL3874 asserts HDEVSEL to claim a PCI cycle as the target device. As a PCI initiator on the bus, the ISL3874 monitors HDEVSEL until a target responds. If no target responds before timeout occurs, the ISL3874 terminates the cycle with an initiator abort.                                                                                                                       |

| HPERR    | D16           | 5V Tol, CMOS, BiDir       | PCI bus parity. In all PCI bus read and write cycles, the ISL3874 calculates even parity across the HD31-HAD0 and BE3-BE0 buses. As an initiator during PCI cycles, the ISL3874 outputs this parity indicator with a one-PCLK delay. As a target during PCI cycles, the calculated parity is compared to the initiator parity indicator. A compare error results in the assertion of a parity error (PERR). |

| HGNT     | C7            | 5V Tol, CMOS, ST<br>Input | PCI bus grant. HGNT is driven by the PCI bus arbiter to grant the ISL3874 access to the PCI bus after the current data transaction has completed. HGNT may or may not follow a PCI bus request, depending on the PCI bus parking algorithm.                                                                                                                                                                 |

| HPCLK    | A7            | 5V Tol, CMOS,<br>Input    | HPCLK provides timing for all transactions on the PCI bus. All PCI signals are sampled at the rising edge of PCLK.                                                                                                                                                                                                                                                                                          |

| HPAR     | B13           | 5V Tol, CMOS, BiDir       | PCI bus parity.                                                                                                                                                                                                                                                                                                                                                                                             |

| HIDSEL   | C11           | 5V Tol, CMOS,<br>Input    | Initialization device select. HIDSEL selects the ISL3874 during configuration space accesses.<br>HIDSEL can be connected to one of the upper 24 PCI address lines on the PCI bus.                                                                                                                                                                                                                           |

| HPME     | B8            | CMOS, Output              | Power Management Event Output. HPME provides output for PME signals.                                                                                                                                                                                                                                                                                                                                        |

| TABLE 2. | MEMORY | INTERFACE PINS |

|----------|--------|----------------|

|----------|--------|----------------|

| PIN NAME    | PIN NUMBER | PIN I/O TYPE                     | DESCRIPTION                                                                                                                                                                                                                                                                                                             |

|-------------|------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PL4-MA19    | A4         | CMOS BiDir, 2mA                  | MBUS Address Bit 19, needed to address between 512KB and 1MB of data store                                                                                                                                                                                                                                              |

| MA18        | A3         | CMOS BiDir, 2mA                  | MBUS Address Bit 18                                                                                                                                                                                                                                                                                                     |

| MA17        | B4         | CMOS BiDir, 2mA                  | MBUS Address Bit 17                                                                                                                                                                                                                                                                                                     |

| MA16        | C3         | CMOS TS Output, 2mA              | MBUS Address Bit 16                                                                                                                                                                                                                                                                                                     |

| MA15        | B3         | CMOS TS Output, 2mA              | MBUS Address Bit 15                                                                                                                                                                                                                                                                                                     |

| MA14        | A1         | CMOS TS Output, 2mA              | MBUS Address Bit 14                                                                                                                                                                                                                                                                                                     |

| MA13        | C2         | CMOS TS Output, 2mA              | MBUS Address Bit 13                                                                                                                                                                                                                                                                                                     |

| MA12        | E3         | CMOS TS Output, 2mA              | MBUS Address Bit 12                                                                                                                                                                                                                                                                                                     |

| MA11        | B1         | CMOS TS Output, 2mA              | MBUS Address Bit 11                                                                                                                                                                                                                                                                                                     |

| MA10        | D2         | CMOS TS Output, 2mA              | MBUS Address Bit 10                                                                                                                                                                                                                                                                                                     |

| MA9         | D3         | CMOS TS Output, 2mA              | MBUS Address Bit 9                                                                                                                                                                                                                                                                                                      |

| MA8         | C1         | CMOS TS Output, 2mA              | MBUS Address Bit 8                                                                                                                                                                                                                                                                                                      |

| MA7         | F4         | CMOS TS Output, 2mA              | MBUS Address Bit 7                                                                                                                                                                                                                                                                                                      |

| MA6         | E2         | CMOS TS Output, 2mA              | MBUS Address Bit 6                                                                                                                                                                                                                                                                                                      |

| MA5         | D1         | CMOS TS Output, 2mA              | MBUS Address Bit 5                                                                                                                                                                                                                                                                                                      |

| MA4         | F2         | CMOS TS Output, 2mA              | MBUS Address Bit 4                                                                                                                                                                                                                                                                                                      |

| MA3         | E1         | CMOS TS Output, 2mA              | MBUS Address Bit 3                                                                                                                                                                                                                                                                                                      |

| MA2         | F3         | CMOS TS Output, 2mA              | MBUS Address Bit 2                                                                                                                                                                                                                                                                                                      |

| MA1         | F1         | CMOS TS Output, 2mA              | MBUS Address Bit 1                                                                                                                                                                                                                                                                                                      |

| MAO / MWEH- | G2         | CMOS TS Output, 2mA, 50K Pull Up | MBUS Write Enable, high byte. Asserted on writes to the high-order byte of x16 memory devices that use the JEDEC 4-wire control interface. Also asserted (as MA[0]) when accessing the odd (high-order) byte of a word stored in a x8 memory device. During word accesses of x8 memory, the odd byte is accessed first. |

| MD15        | H4         | CMOS, BiDir, 2mA, 50K Pull Up    | MBUS Data Bit 15                                                                                                                                                                                                                                                                                                        |

| MD14        | G1         | CMOS, BiDir, 2mA, 50K Pull Up    | MBUS Data Bit 14                                                                                                                                                                                                                                                                                                        |

| MD13        | H3         | CMOS, BiDir, 2mA, 50K Pull Down  | MBUS Data Bit 13                                                                                                                                                                                                                                                                                                        |

| MD12        | H2         | CMOS, BiDir, 2mA, 50K Pull Down  | MBUS Data Bit 12                                                                                                                                                                                                                                                                                                        |

| MD11        | H1         | CMOS, BiDir, 2mA, 50K Pull Up    | MBUS Data Bit 11                                                                                                                                                                                                                                                                                                        |

| MD10        | J3         | CMOS, BiDir, 2mA, 50K Pull Up    | MBUS Data Bit 10                                                                                                                                                                                                                                                                                                        |

| MD9         | M1         | CMOS, BiDir, 2mA, 50K Pull Up    | MBUS Data Bit 9                                                                                                                                                                                                                                                                                                         |

| MD8         | M3         | CMOS, BiDir, 2mA, 50K Pull Down  | MBUS Data Bit 8                                                                                                                                                                                                                                                                                                         |

| MD7         | M2         | CMOS, BiDir, 2mA 50K Pull Down   | MBUS Data Bit 7                                                                                                                                                                                                                                                                                                         |

| MD6         | N1         | CMOS, BiDir, 2mA, 50K Pull Down  | MBUS Data Bit 6                                                                                                                                                                                                                                                                                                         |

| MD5         | N3         | CMOS, BiDir, 2mA, 50K Pull Down  | MBUS Data Bit 5                                                                                                                                                                                                                                                                                                         |

| MD4         | P1         | CMOS, BiDir, 2mA, 50K Pull Down  | MBUS Data Bit 4                                                                                                                                                                                                                                                                                                         |

| MD3         | N2         | CMOS, BiDir, 2mA, 50K Pull Down  | MBUS Data Bit 3                                                                                                                                                                                                                                                                                                         |

| MD2         | P3         | CMOS, BiDir, 2mA, 50K Pull Down  | MBUS Data Bit 2                                                                                                                                                                                                                                                                                                         |

| MD1         | R1         | CMOS, BiDir, 2mA, 50K Pull Down  | MBUS Data Bit 1                                                                                                                                                                                                                                                                                                         |

| MD0         | P2         | CMOS, BiDir, 2mA, 50K Pull Down  | MBUS Data Bit 0                                                                                                                                                                                                                                                                                                         |

| PIN NAME  | PIN NUMBER | PIN I/O TYPE                        | DESCRIPTION                                                                                                                                                                                                                                        |

|-----------|------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MLBE      | L3         | CMOS BiDir Output, 2mA, 50K Pull Up | MBUS Lower Byte Enable. Asserted when accessing the low-order byte of x16 memory devices that use the JEDEC 5-wire control interface.                                                                                                              |

| MOE       | L1         | CMOS TS Output, 2mA, 50K Pull Up    | Memory Output Enable; asserted on memory reads                                                                                                                                                                                                     |

| MWE/ MWEL | L2         | CMOS TS Output, 2mA, 50K Pull Up    | Low (or only) Byte Memory Write Enable. Asserted on writes to x8 memory devices, x16 memory devices that use the JEDEC 5-wire control inteface, or writes to the low-order byte of x16 memory devices that use the JEDEC 4-wire control interface. |

| RAMCS     | K2         | CMOS TS Output, 2mA, 50K Pull Up    | RAM Select; asserted on MBUS cycles when the address is in the area configured as RAM                                                                                                                                                              |

| NVCS      | K1         | CMOS TS Output, 2mA, 50K Pull Up    | NV Memory Select; asserted on MBUS cycles when the address is in the area configured as non-volitile memory.                                                                                                                                       |

#### TABLE 2. MEMORY INTERFACE PINS (Continued)

#### TABLE 3. GENERAL PURPOSE PORT PINS

| PIN NAME | PIN NUMBER | PIN I/O TYPE                       | DESCRIPTION OF FUNCTION<br>(IF OTHER THAN IO PORT)                                                                                                                                                                                                                              |

|----------|------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

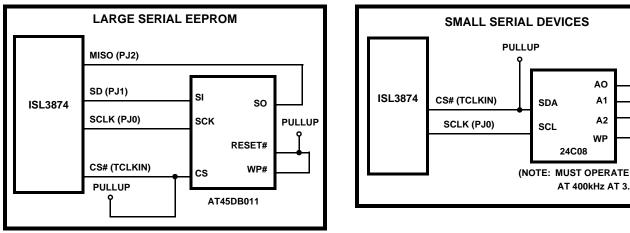

| PJ4      | T2         | CMOS BiDir, 2mA, 50K Pull Down     | PE1. PE1 and PE2 are bit-encoded functions that control the RF and IF sections.                                                                                                                                                                                                 |

| PJ5      | T4         | CMOS BiDir, 2mA, 50K Pull Down     | LE_IF. LE_IF and LE_RF are the corresponding serial<br>enables for the IF and RF chips. The trailing edge of the<br>latch enables (LE) are required to latch the data in the<br>input register. The last 20 bits of data before the trailing<br>edge of enables are latched in. |

| PJ6      | P4         | CMOS BiDir, 2mA                    | LED1.                                                                                                                                                                                                                                                                           |

| PJ7      | ТЗ         | CMOS BiDir, 2mA, 50K Pull Down     | RADIO_PE. This signal is the power enable to the RF and IF components, but not the baseband.                                                                                                                                                                                    |

| PK0      | R5         | CMOS BiDir, 2mA, ST, 50K Pull Down | LE_RF. LE_RF and LE_IF are the corresponding serial<br>enables for the RF and IF chips. The trailing edge of the<br>latch enables (LE) are required to latch the data in the<br>input register. The last 20 bits of data before the trailing<br>edge of enable are latched in.  |

| PK1      | R4         | CMOS BiDir, 2mA, 50K Pull Down     | SYNTHCLK. Separate signals, SYNTHCLK and SYNTHDATA, are used to program the synthesizer through bit manipulation in firmware.                                                                                                                                                   |

| PK2      | N7         | CMOS BiDir, 2mA, 50K Pull Down     | SYNTHDATA. Separate signals, SYNTHDATA and SYNTHCLK, are used to program the synthesizer through bit manipulation in firmware.                                                                                                                                                  |

| РКЗ      | R6         | CMOS BiDir, 2mA, 50K Pull Down     | PA_PE. This signal, when asserted high, enables the Tx section of the Modulator/Demodulator and RF/IF up/down converter circuits.                                                                                                                                               |

| PK4      | T5         | CMOS BiDir, 2mA, 50K Pull Down     | PE2. PE2 and PE1 are bit-encoded functions that control the RF and IF sictions.                                                                                                                                                                                                 |

| PK7      | P7         | CMOS BiDir, 2mA, 50K Pull Down     | CAL_EN. Calibrates the Rx function to eliminate DC offset in the Rx chain.                                                                                                                                                                                                      |

| PL3      | P8         | CMOS BiDir, 2mA, 50K Pull Up       | TR_SW_BAR. Antenna Diversity Control                                                                                                                                                                                                                                            |

| PL7      | T6         | CMOS BiDir, 2mA, 50K Pull Down     | TR_SW. Antenna Diversity Control                                                                                                                                                                                                                                                |

| PIN NAME   | PIN NUMBER | PIN I/O TYPE                   | DESCRIPTION                                                                                                                                                                                 |

|------------|------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PJ0        | P5         | CMOS BiDir, 2mA, 50K Pull Up   | SCLK, serial clock for serial EEPROM devices                                                                                                                                                |

| PJ1        | T1         | CMOS BiDir, 2mA, 50K Pull Down | Serial Data Out (SD) used on serial EEPROM devices which require three and four wire interfaces, example: AT45DB011                                                                         |

| PJ2        | R3         | CMOS BiDir, 2mA, 50K Pull Down | Serial Data In (MISO) used on serial EEPROM devices, Used in four wire serial devices only. Not currently supported in software. Consult the factory for additional updates on this option. |

| TCLKIN(CS) | L4         | I/O, 50K Pull Down             | CS used for Chip Select Output for Serial Devices which have a 4 wire interface like the AST45DB011 and also serial data on two wire devices like the 24C08.                                |

#### TABLE 4. SERIAL EEPROM PORT CONNECTIONS

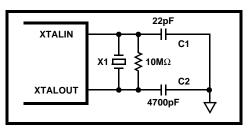

#### TABLE 5. CLOCKS PORT PINS

| PIN NAME | PIN NUMBER | PIN I/O TYPE         | DESCRIPTION                                                               |

|----------|------------|----------------------|---------------------------------------------------------------------------|

| XTALIN   | J2         | Analog Input         | 32.768kHz Crystal Input                                                   |

| XTALOUT  | J1         | CMOS Output, 2mA     | 32.768kHz Crystal Output                                                  |

| CLKOUT   | A2         | CMOS, TS Output, 2mA | Clock Output (Selectable as MCLK, TCLK, or TOUT0)                         |

| BBP_CLK  | J16        | Input                | Baseband Processor Clock. The nominal frequency for this clock is 44 MHz. |

#### TABLE 6. BASEBAND PROCESSOR RECEIVER PORT PINS

| PIN NAME  | PIN NUMBER | R PIN I/O TYPE DESCRIPTION                                                                   |                                                                                                |

|-----------|------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| RX_IF_AGC | T16        | 0                                                                                            | Analog drive to the IF AGC control.                                                            |

| RX_RF_AGC | P16        | 0                                                                                            | Drive to the RF AGC stage attenuator. CMOS digital.                                            |

| RX_IF_DET | R10        | I                                                                                            | Analog input to the receive power A/D converter for AGC control.                               |

| RXI+      | R7         | I Analog input to the internal 6-bit A/D of the In-phase received data. Balanced differentia |                                                                                                |

| RXI-      | T7         | I Analog input to the internal 6-bit A/D of the In-phase received data. Balanced differen    |                                                                                                |

| RXQ+      | R9         | I                                                                                            | Analog input to the internal 6-bit A/D of the Quadrature received data. Balanced differential. |

| RXQ-      | Т9         | I                                                                                            | Analog input to the internal 6-bit A/D of the Quadrature received data. Balanced differential. |

#### TABLE 7. BASEBAND PROCESSOR TRANSMITTER PORT PINS

| PIN NAME  | PIN NUMBER | PIN I/O TYPE | DESCRIPTION                                                                                       |

|-----------|------------|--------------|---------------------------------------------------------------------------------------------------|

| TX_AGC_IN | T10        | I            | Input to the transmit power A/D converter for transmit AGC control.                               |

| TX_IF_AGC | R16        | 0            | Analog drive to the transmit IF power control.                                                    |

| TXI+      | R12        | 0            | TX Spread baseband I digital output data. Data is output at the chip rate. Balanced differential. |

| TXI–      | T12        | 0            | TX Spread baseband I digital output data. Data is output at the chip rate. Balanced differentia.  |

| TXQ+      | R14        | 0            | TX Spread baseband Q digital output data. Data is output at the chip rate. Balanced differential. |

| TXQ-      | T14        | 0            | TX Spread baseband Q digital output data. Data is output at the chip rate. Balanced differential. |

| PIN NAME          | PIN NUMBER | PIN I/O TYPE          | DESCRIPTION                                                                                                                                                                                                                                 |

|-------------------|------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GRESET            | L15        | I                     | Global Reset for MAC, Active LOW                                                                                                                                                                                                            |

| TCLKIN(CS)        | L4         | I/O, 50K Pull<br>Down | CS used for Chip Select Output for Serial Devices which have a 4 wire interface like the AST45DB011 and also serial data on two wire devices like the 24C08.                                                                                |

| ANTSEL            | N15        | 0                     | The antenna select signal changes state as the receiver switches from antenna to antenna during the acquisition process in the antenna diversity mode. This is a complement for ANTSEL (pin 40) for differential drive of antenna switches. |

| ANTSEL            | N16        | 0                     | The antenna select signal changes state as the receiver switches from antenna to antenna during the acquisition process in the antenna diversity mode. This is a complement for ANTSEL (pin 39) for differential drive of antenna switches. |

| Test_Mode         | C4         | I                     | Must be tied to GND.                                                                                                                                                                                                                        |

| CompCap1          | R15        | I                     | Compensation Capacitor.                                                                                                                                                                                                                     |

| CompCap2          | R13        | I                     | Compensation Capacitor.                                                                                                                                                                                                                     |

| CompRes1          | T15        | 1                     | Compensation Resistor.                                                                                                                                                                                                                      |

| CompRes2          | P13        | I                     | Compensation Resistor.                                                                                                                                                                                                                      |

| DBG4<br>(MPCIACT) | B6         | I/O                   | Manufacturing Debug Signals, Leave Unconnected.<br>Connected to MPCIACT Signal on Mini-PCI Connector.                                                                                                                                       |

| DBG3<br>(CLKRUN)  | A5         | I/O                   | Manufacturing Debug Signals, Leave Unconnected.<br>Connected to CLKRUN Signal on Mini-PCI Connector.                                                                                                                                        |

| DBG2<br>(LED2)    | C5         | I/O                   | Manufacturing Debug Signals, Leave Unconnected.<br>Used as LED2 Output Signal.                                                                                                                                                              |

| DBG1              | B5         | I/O                   | Manufacturing Debug Signals, Leave Unconnected.                                                                                                                                                                                             |

| DBG0              | A6         | I/O                   | Manufacturing Debug Signals, Leave Unconnected.                                                                                                                                                                                             |

#### TABLE 9. POWER PORT PINS

| PIN NAME         | PIN NUMBER                                                                      | PIN I/O TYPE | DESCRIPTION                                                                          |

|------------------|---------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------|

| V <sub>DDA</sub> | M13, P12, R11, T8, R8, P9                                                       | Power        | Analog DC Power Supply 2.7 - 3.6V.                                                   |

| V <sub>DD</sub>  | P6, D4, D7, D9, D11, D14, F13,<br>H13, K16, M15, N5, N4, K4,<br>G3, E4          | Power        | Digital DC Power Supply 2.7 - 3.6V.                                                  |

| V <sub>SSA</sub> | N13, T13, T11, N9                                                               | GND          | Analog Ground.                                                                       |

| V <sub>sub</sub> | N10, P10                                                                        | GND          | Analog Ground.                                                                       |

| GND              | B2, D5, D8, D10, D12, D13,<br>E13, H14, J13, N14, N8, N6,<br>R2, M4, K3, J4, G4 | GND          | Digital Ground.                                                                      |

| V <sub>REF</sub> | P11                                                                             | Input        | Voltage Reference for A/Ds and D/As.                                                 |

| I <sub>REF</sub> | N12                                                                             | Input        | Current Reference for internal ADC and DAC devices. Requires 12K resistor to ground. |

| NC               | P15, P14, N11, M14, C15, L13,<br>M16, K13                                       | NC           | No Connection.                                                                       |

ST = Schmitt Trigger (Hysteresis), TS = Three-State. Signals ending with "-" are active low.

#### **Absolute Maximum Ratings**

| Supply Voltage 4V                                               |

|-----------------------------------------------------------------|

| Input, Output or I/O Voltage GND -0.5V to V <sub>CC</sub> +0.5V |

| ESD Classification Class 2                                      |

#### **Operating Conditions**

| Voltage Range              |      |              |

|----------------------------|------|--------------|

| Ambient Temperature Range. | <br> | 40°C to 85°C |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)   | θ <sub>JA</sub> ( <sup>o</sup> C/W)  |

|----------------------------------------|--------------------------------------|

| BGA Package                            | 56                                   |

| Maximum Storage Temperature Range65    | <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Junction Temperature           | 100 <sup>0</sup> C                   |

| Maximum Soldering Temperature See Tech | Brief TB334                          |

|                                        |                                      |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

1. θ<sub>JA</sub> is measured with the component mounted on a low effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

#### DC Electrical Specifications (Test conditions @ 25°C)

| PARAMETER                    | SYMBOL            | TEST CONDITIONS                                                               | MIN                  | TYP  | MAX     | UNITS |

|------------------------------|-------------------|-------------------------------------------------------------------------------|----------------------|------|---------|-------|

| Power Supply Current         | ICCOP             | V <sub>CC</sub> = 3.6V, CLK Frequency = 44MHz                                 | -                    | 170  | TBD     | mA    |

| Standby Power Supply Current | I <sub>CCSB</sub> | V <sub>CC</sub> = Max, Outputs Not Loaded                                     | -                    | 3    | TBD     | mA    |

| Input Leakage Current        | l                 | $V_{CC}$ = Max, Input = 0V or $V_{CC}$                                        | -                    | 100  | TBD     | nA    |

| Output Leakage Current       | Ι <sub>Ο</sub>    | $V_{CC}$ = Max, Input = 0V or $V_{CC}$                                        | -                    | 300  | TBD     | nA    |

| Logical One Input Voltage    | VIH               | V <sub>CC</sub> = Max, Min                                                    | 0.7V <sub>CC</sub>   | -    | -       | V     |

| Logical Zero Input Voltage   | V <sub>IL</sub>   | V <sub>CC</sub> = Min, Max                                                    | -                    | -    | VCC*0.3 | V     |

| Logical One Output Voltage   | V <sub>OH</sub>   | I <sub>OH</sub> = -1mA, V <sub>CC</sub> = Min                                 | V <sub>CC</sub> -0.2 | 2.6  | -       | V     |

| Logical Zero Output Voltage  | V <sub>OL</sub>   | $I_{OL} = 2mA, V_{CC} = Min$                                                  | -                    | 0.05 | 0.2     | V     |

| Input Capacitance            | C <sub>IN</sub>   | CLK Frequency = 1MHz. All measurements referenced to GND. $T_A = 25^{\circ}C$ | -                    | 5    | 10      | pF    |

| Output Capacitance           | C <sub>OUT</sub>  | CLK Frequency 1MHz. All measurements referenced to GND. $T_A = 25^{\circ}C$   | -                    | 5    | 10      | pF    |

NOTE: All values in this table have not been measured and are only estimates of the performance at this time.

#### **AC Electrical Specifications**

| PARAMETER                                    | SYMBOL           | MIN  | TYP  | MAX | UNITS |

|----------------------------------------------|------------------|------|------|-----|-------|

| CLOCK SIGNAL TIMING                          |                  |      | 1    | 1   |       |

| OSC Clock Period (Typ. 44MHz)                | t <sub>CYC</sub> | 22.5 | 20.8 | 200 | ns    |

| High Period                                  | t <sub>H1</sub>  | 10   | 10.4 | -   | ns    |

| Low Period                                   | t <sub>L1</sub>  | 10   | 10.4 | -   | ns    |

| Full Scale Input Voltage (V <sub>P-P</sub> ) |                  | TBD  | TBD  | 4   | V     |

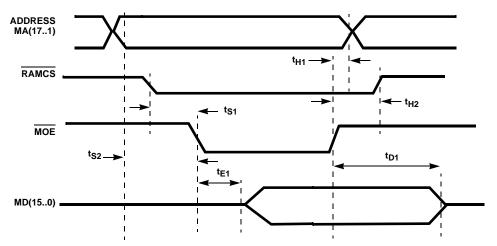

| EXTERNAL MEMORY READ INTERFACE               |                  |      |      |     |       |

| MOE-Setup Time from RAMCS_                   | t <sub>S1</sub>  | 0    | -    | -   | ns    |

| MOE_Setup Time from MA (170)                 | t <sub>S2</sub>  | 0    | -    | -   | ns    |

| MA (171) Hold Time from MOE_ Rising Edge     | t <sub>H1</sub>  | 20   | -    | -   | ns    |

| RAMCS_ Hold from MOE_ Rising Edge            | t <sub>H2</sub>  | 20   | -    | -   | ns    |

| MD (150) Enable from MOE_ Falling            | t <sub>E1</sub>  | 5    | -    | -   | ns    |

| MO (150) Disable from MOE_ Rising Edge       | t <sub>D1</sub>  | -    | -    | 100 | ns    |

| EXTERNAL MEMORY WRITE INTERFACE              |                  |      |      |     |       |

| MA (170) Setup to MWE_ Falling Edge          | t <sub>S3</sub>  | 0    | 0    | 0   | ns    |

| RAMCS_ Setup to MWE                          | t <sub>S4</sub>  | 0    | -    | -   | ns    |

| MA (170) Hold from MWE_ Rising Edge          | t <sub>H3</sub>  | 15   | -    | -   | ns    |

| RAMCS _ Hold from MWE_ Rising Edge           | t <sub>H4</sub>  | 15   | -    | -   | ns    |

| MD (150) Setup to MWE_ Rising Edge           | t <sub>S5</sub>  | 40   | -    | -   | ns    |

| MD (150) Hold from MWE_ Rising Edge          | t <sub>H5</sub>  | 15   | -    | -   | ns    |

AC Electrical Specifications (Continued)

| PARAMETER                                                    | SYMBOL           | MIN                      | TYP  | MAX              | UNITS |

|--------------------------------------------------------------|------------------|--------------------------|------|------------------|-------|

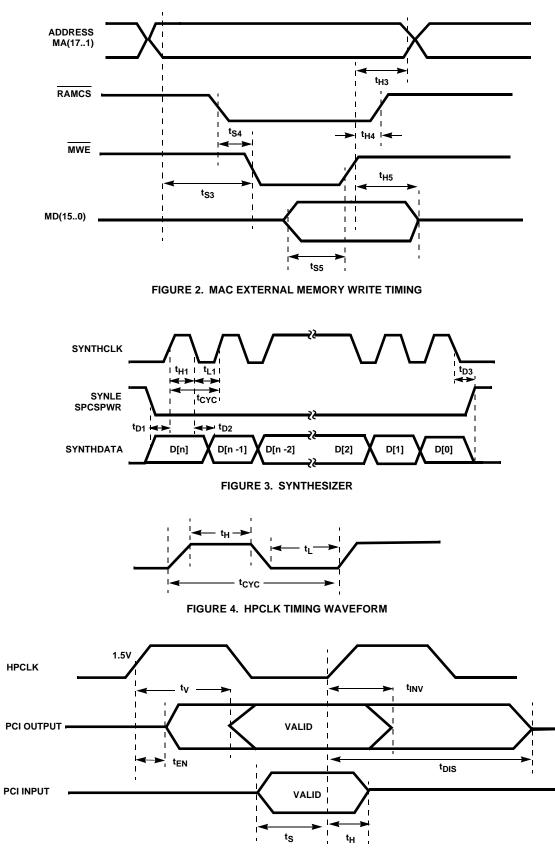

| SYNTHESIZER                                                  |                  |                          |      |                  |       |

| SYNTHCLK(PK1) Period                                         | tCYC             | 90                       | -    | 4,000            | ns    |

| SYNTHCLK(PK1) Width Hi                                       | t <sub>H1</sub>  | t <sub>CYC</sub> /2 - 10 | -    | $t_{CYC}/2 + 10$ | ns    |

| SYNTHCLK(PK1) Width Lo                                       | t <sub>L1</sub>  | t <sub>CYC</sub> /2 - 10 | -    | $t_{CYC}/2 + 10$ | ns    |

| SYNTHDATA(PK2) Hold Time from Falling Edge of SYNTHCLK(PK1)  | t <sub>D2</sub>  | 0                        | -    | -                | ns    |

| SYNTHCLK(PK1) Falling Edge to SYNLE Inactive                 | t <sub>D3</sub>  | 35                       | -    | -                | ns    |

| SYSTEM INTERFACE - PCI TIMING                                | •                |                          |      |                  |       |

| Cycle Time, HPCLK                                            | tCYC             | 30                       | -    | -                | ns    |

| Pulse Duration, HPCLK High                                   | t <sub>H</sub>   | 11                       | -    | -                | ns    |

| Pulse Duration, HPCLK Low                                    | tL               | 11                       | -    | -                | ns    |

| Slew Rate, HPCLK                                             | t <sub>S</sub>   | 1                        | -    | 4                | V/ns  |

| Propagation Delay Time, HPCLK to Signal Valid Delay Time     | t <sub>V</sub>   | -                        | -    | 11               | ns    |

| Propogation Delay Time, HPCLK to Signal Invalid Delay Time   | t <sub>INV</sub> | 2                        | -    | -                | ns    |

| Enable Time, High Impedance to Active Delay Time from HPCLK  | t <sub>EN</sub>  | 2                        | -    | -                | ns    |

| Disable Time, Active to High Impedance Delay Time from HPCLK | t <sub>DIS</sub> | -                        | -    | 28               | ns    |

| Setup Time Before HPCLK Valid                                | t <sub>S</sub>   | 7                        | -    | -                | ns    |

| Hold Time After HPCLK High                                   | t <sub>H</sub>   | 0                        | -    | -                | ns    |

| BASEBAND SIGNALS                                             | ·                |                          |      |                  |       |

| Full Scale Input Voltage (VP-P)                              |                  | 0.25                     | 0.50 | 1.0              | V     |

| Input Bandwidth (-0.5dB)                                     |                  | -                        | 20   | -                | MHz   |

| Input Capacitance                                            |                  | -                        | 5    | -                | pF    |

| Input Impedance (DC)                                         |                  | 5                        | -    | -                | kΩ    |

| FS (Sampling Frequency)                                      |                  | -                        | -    | 22               | MHz   |

# Waveforms

#### Waveforms (Continued)

FIGURE 5. PCI BUS TIMING WAVEFORMS

11

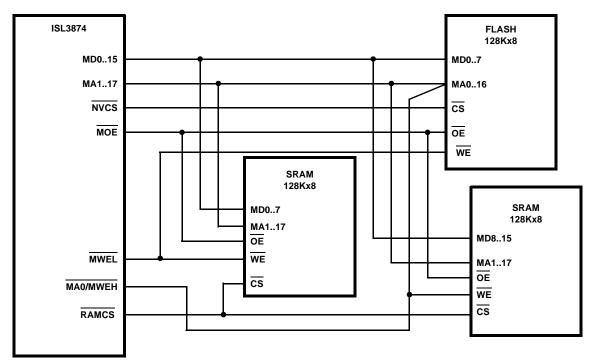

# External Memory Interface

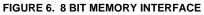

The ISL3874 provides separate external chip selects for code space and data storage space. Code space is accessible as data space through an overlay mechanism, except for an internal ROM. Refer to Figures 6, 7 and 8 for ISL3874 memory configuration detail examples.

The maximum possible memory space size is 4Mbytes. Most of the data store space is reserved for storage of received and transmitted data, with some areas reserved for use by firmware. However, a portion of the data store may be allocated as code store. This permits higher speed instruction execution, by using fast RAMs, than is possible from Flash memories. The maximum size of this overlay is the full code space address range, 128kbytes, and is allocated in independent sections of 16KBytes each, on 16kbyte boundaries, ranging from the highest address of the actual physical memory space and extending down.

Mapping code execution to RAM requires the RAM to have code written into it. Typically, this is done by placing code in a non-volatile memory such as a Flash in the code space. At initialization, the code in the non-volatile memory transfers itself to RAM, maps the appropriate blocks of the code space to the RAM, and then branches to begin execution from RAM. This allows low cost, slow Flash devices to hold an entire code image, which can be executed much faster from RAM. If code is not placed in an external non-volatile memory as described here, it must be transferred to the RAM via the Host Interface.

Slow memories are not dynamically sensed. Following reset, the instruction clock operates with a slower cycle while the Flash is copied to RAM. Once code has been copied from Flash to RAM, execution transfers to RAM and the clock is raised to the normal operating frequency.

As mentioned above, it is feasible to operate without a code image in a non-volatile memory. In such a system, the firmware must be downloaded to RAM through the host interface before operation can commence.

The external SRAM memory must be organized in a 16-bit width to provide adequate performance to implement the 802.11 protocol at 11Mb/s rates. Systems designed for lower performance applications may be able to use 8-bit wide memory.

AO

A1

A2

WP

AT 400kHz AT 3.3VDC)

24C08

The minimum external memory is 128kbytes of SRAM, organized 8 or 16 bits wide. Typical applications, including 802.11 station designs, use 256kbytes organized 128K x 16. An access point application could make use of the full address space of the device with 4Mbytes organized a 2M x 16.

The ISL3874 supports 8 or 16-bit code space, and 8 or 16-bit data space. Code space is typically populated with the least expensive Flash memory available, usually an 8-bit device. Data space is usually populated with high-speed RAMs configured as a 16-bit space. This mixing of 8/16 bit spaces is fully supported, and may be done in any combination desired for code and data space.

The ISL3874 supports direct control of single chip 16-bit wide SRAMs with high/low byte enables, as well as direct control of a 16-bit space constructed from 8-bit wide SRAMs. The type of memory configuration is specified via the appropriate MD pin, sensed when the ISL3874 is reset.

ISL3874 pin MA0/MWEH functions as Address 0 for 8-bit access, (such as Flash) as MWEH (High Byte Write Enable) when two x8 memories are configured as a single x16 space, and as the upper Byte Enable when a single x16 memory is used. No external logic is required to generate the required signals for both types of memory configurations, even when both exist together; all that is required is for the ISL3874 code to configure the ISL3874 memory controller to generate the proper signals for the particular address space being accessed.

For 8-bit spaces, the ISL3874 dynamically configures pin MA0/MWEH cycle-by-cycle as the address LSB.

MWEL/MWE is the only write control, and MOE is the read output enable.

For 16-bit spaces constructed from 8-bit memories, the ISL3874 dynamically configures pin MA0/MWEH cycle-by-cycle as the high byte write enable, MWEL as the low write enable signal, and MOE as the read output enable.

For 16-bit spaces constructed from single-chip x16 memories (such as SRAMs), the ISL3874 dynamically configures pin MA0/MWEH cycle-by-cycle as the upper byte enable. Pin MLBE is connected as the low byte enable, MWEL/MWE is the write control, and MOE is the read output enable.

These memory implementations require no external logic. The memory spaces may each be constructed from any type of memory desired. The only restriction is that a single memory space must be constructed from the same type of memory; for example, data space may not use both x8 and x16 memories, it must be all x8, or all x16. This restriction does not apply across memory spaces; e.g., code space may use a x8 memory and data space a single x16 memory, or code space two x8 memories and data space a single x8 memory.

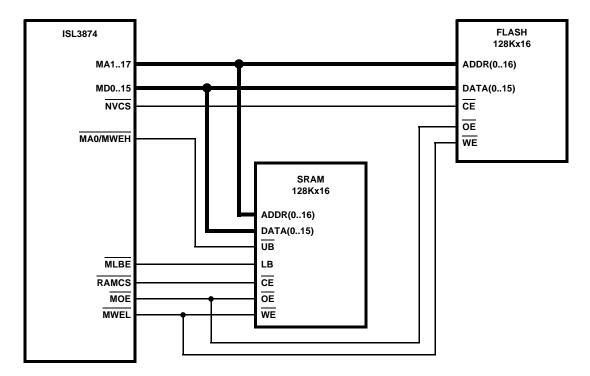

# Serial EEPROM Memory Interface

The ISL3874 contains a small on-ship ROM firmware which was added to allow the CIS or CIS plus firmware image to be transferred from a off-chip serial nonvolatile memory device to RAM after a system reset. This allows a system configuration without a parallel Flash device. The operating frequency for the 24C08 Serial EEPROM must be 400kHz with an operating voltage of 3.3V. Refer to Figure 8 for additional details on configuring the serial memory to the ISL3874.

The Power On Reset Configuration Section in this document provides additional details on memory selection and control after a reset condition.

# PC Card Interface

The PCI Host Interface allows access to the ISL3874 memory and host registers using PCI memory read or write transactions.

The host interface supports Target Mode operation transferring double words. Direct memory access to the ISL3874 memory space using Aux port transfers is supported in Target Mode. BAP transfers operate in Target Mode in a similar manner to how they worked on the HFA3842 and thus allow quick porting of base functionality HFA3842 driver code to this part.