## **DSM2150F5V**

# DSM (Digital Signal Processor System Memory) For Analog Devices General Purpose DSPs

#### **FEATURES SUMMARY**

#### ■ Glueless Connection to DSP

- 512K x 8 or 256K x 16 (8 or 16 bit operation)

- Easily add memory, logic, and I/O to the external memory interface (EMI) of Analog Devices' general purpose DSP families

#### ■ Dual Flash Memories

- 512K x 8 Main Flash memory divided into eight, 64 KByte sectors.

- 32K x 8 Secondary Flash memory divided into four, 8 KByte sectors.

- Small sector size ideal for storing small data sets, and calibration or configuration constants.

- Concatenate Secondary Flash with Main Flash for total of 544 KBytes.

- Each Flash sector can be write protected.

- Built-in programmable address decoding logic allows mapping individual Flash sectors to any address boundary.

#### ■ Up to 40 Multifunction I/O Pins

- Increase total DSP system I/O capability

- I/O controlled by DSP software or PLD logic

#### **■** General purpose PLD

- Over 3.000 Gates of PLD with 16 macrocells

- Use for peripheral glue logic to keypads, control panel, displays, LCDs, and other devices.

- Eliminate PLDs and external logic devices

- Create state machines, chip selects, simple shifters and counters, clock dividers, delays

- Simple PSDsoft Express software ... Free

## ■ In-System Programming (ISP) with JTAG

- Program entire chip in 20-35 seconds with no involvement of the DSP

- Links with JTAG debug port on DSP

- Eliminate sockets for pre-programmed memory and logic devices

- ISP allows efficient manufacturing and product testing supporting Just-In-Time inventory

- Use low-cost FlashLINK™ JTAG programmer with PC

Figure 1. Packages

#### ■ Content Security

Programmable Security Bit blocks access of device programmers and readers

## ■ Operating Range

- V<sub>CC</sub>: 3.3V±10%

- Temperature: –40°C to +85°C

## ■ Zero-Power Technology

100 μA standby current (typical)

## ■ Packaging

80-pin TQFP

## ■ Flash Memory Speed, Endurance, Retention

- 120 ns, 100K cycles, 15 year retention

December 2001 1/6

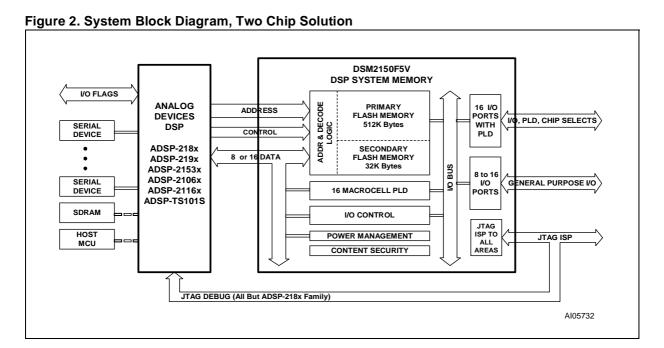

#### SUMMARY DESCRIPTION

The DSM2150F5 provides a turn-key system memory solution for the Analog Devices general purpose DSP families. With dual in-system programmable (ISP) Flash memories, parameter storage, programmable logic, and additional I/O, the combination of the DSM2150F5 with the DSP results in a simple and flexible two-chip DSP system. On-chip memory decode logic simplifies mapping the dual banks of Flash memory to the DSP for boot loading, code execution, data recording, code swapping, and pa-rameter storage. An on-chip JTAG ISP port allows blank DSM devices to be programmed on the circuit board, thus reducing development time, simplifying manufacturing flow, lowering the cost of field upgrades, and eliminating the need for sockets and pre-programmed memory and logic devices. The DSM's JTAG interface may also be chained with the DSP's JTAG debug interface for quick code iterations on the bench. JTAG ISP is accomplished via the FlashLINK JTAG programmer which plugs into any PC or laptop parallel port.

In addition to ISP Flash memory, DSM devices add programmable logic (PLD) and up to 16 con-

figurable I/O pins to the DSP system. PLD and I/O configuration are programmable by JTAG ISP, just like the Flash memory. The PLD consists of more than 3000 gates and has 16 macrocell registers. Common uses for the PLD include chip selects for external devices, state-machines, simple shifters and counters, key-pad and control panel interfaces, clock dividers, handshake delay, muxes, etc. The on-chip PLD eliminates the need for small external PLDs and logic devices. Configuration of PLD, I/O, and Flash memory mapping are easily entered in a point-and-click environment using the software development tool, PSDsoft Express. The software is available to download www.st.com/psd.

The two-chip combination of a DSP and a DSM device is ideal for systems which have limitations on size, EMI levels, and power consumption. DSM memory and logic are "zero-power", meaning they automatically go to standby between memory accesses or logic input changes, producing low active and standby current consumption, making them ideal for battery powered products.

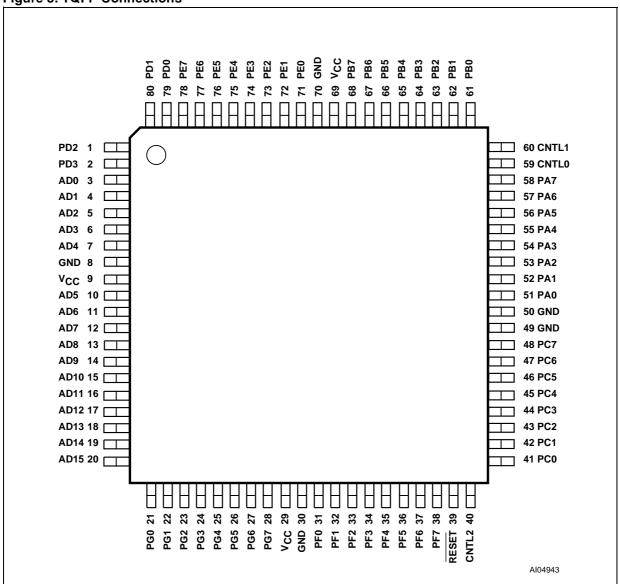

Figure 3. TQFP Connections

Table 1. Pin Assignments – TQFP80

| 1 4 5 10 11 11 11 7 10 0 19 |                        |

|-----------------------------|------------------------|

| Pin No.                     | Pin<br>Assign<br>ments |

| 1                           | PD2                    |

| 2                           | PD3                    |

| 3                           | AD0                    |

| 4                           | AD1                    |

| 5                           | AD2                    |

| 6                           | AD3                    |

| 7                           | AD4                    |

| 8                           | GND                    |

| 9                           | V <sub>CC</sub>        |

| 10                          | AD5                    |

| 11                          | AD6                    |

| 12                          | AD7                    |

| 13                          | AD8                    |

| 14                          | AD9                    |

| 15                          | AD10                   |

| 16                          | AD11                   |

| 17                          | AD12                   |

| 18                          | AD13                   |

| 19                          | AD14                   |

| 20                          | AD15                   |

| - IQFP8U |                        |

|----------|------------------------|

| Pin No.  | Pin<br>Assign<br>ments |

| 21       | PG0                    |

| 22       | PG1                    |

| 23       | PG2                    |

| 24       | PG3                    |

| 25       | PG4                    |

| 26       | PG5                    |

| 27       | PG6                    |

| 28       | PG7                    |

| 29       | V <sub>CC</sub>        |

| 30       | GND                    |

| 31       | PF0                    |

| 32       | PF1                    |

| 33       | PF2                    |

| 34       | PF3                    |

| 35       | PF4                    |

| 36       | PF5                    |

| 37       | PF6                    |

| 38       | PF7                    |

| 39       | RESET                  |

| 40       | CNTL2                  |

| Pin No. | Pin<br>Assign<br>ments |

|---------|------------------------|

| 41      | PC0                    |

| 42      | PC1                    |

| 43      | PC2                    |

| 44      | PC3                    |

| 45      | PC4                    |

| 46      | PC5                    |

| 47      | PC6                    |

| 48      | PC7                    |

| 49      | GND                    |

| 50      | GND                    |

| 51      | PA0                    |

| 52      | PA1                    |

| 53      | PA2                    |

| 54      | PA3                    |

| 55      | PA4                    |

| 56      | PA5                    |

| 57      | PA6                    |

| 58      | PA7                    |

| 59      | CNTL0                  |

| 60      | CNTL1                  |

| Pin No. | Pin<br>Assign<br>ments |

|---------|------------------------|

| 61      | PB0                    |

| 62      | PB1                    |

| 63      | PB2                    |

| 64      | PB3                    |

| 65      | PB4                    |

| 66      | PB5                    |

| 67      | PB6                    |

| 68      | PB7                    |

| 69      | V <sub>CC</sub>        |

| 70      | GND                    |

| 71      | PE0                    |

| 72      | PE1                    |

| 73      | PE2                    |

| 74      | PE3                    |

| 75      | PE4                    |

| 76      | PE5                    |

| 77      | PE6                    |

| 78      | PE7                    |

| 79      | PD0                    |

| 80      | PD1                    |

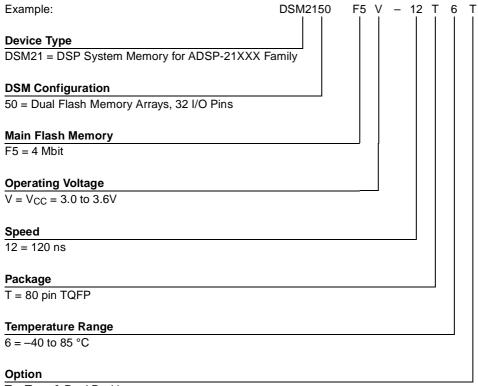

## **Table 2. Ordering Information Scheme**

T = Tape & Reel Packing

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is registered trademark of STMicroelectronics All other names are the property of their respective owners

© 2001 STMicroelectronics - All Rights Reserved

STMicroelectronics group of companies Austalia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States. www.st.com