# AN827

## Using KEELOQ<sup>®</sup> to Validate Subsystem Compatibility

Author: Lucio Di Jasio Microchip Technology Inc.

#### OVERVIEW

Proper modular design can make a system more flexible, easier to maintain and update, and most of all, can help get the design completed faster. In fact, modules or subsystems design can happen in parallel, and can be out-sourced when convenient. Subsystems can also be conveniently replaced during the life of an application to simplify maintenance and allow upgrades. In many situations though, it can be extremely important to verify compatibility of the replacement module in order to ensure the system performs to specifications, maintains quality standards and/or allows safe operation of the whole system. As an example, we offer the case of a mobile phone with its rechargeable battery module. Batteries can be based on different technologies (NiCd, NiMH, Li Ion, etc.) that, in turn, require different charging algorithms. A mismatch would lead to potentially dangerous situations (including as an extreme, fire and explosion of the battery pack) severely compromising the safety of use of the whole product. The situation is different in the

case of security applications (such as modular Home Alarm systems) where module validation is required to prevent tampering of the system, theft, and intrusion.

This Application Note concentrates on the use of the HCS410 transcoder to implement a reliable (yet low cost) method for module authentication using the KEELOQ technology.

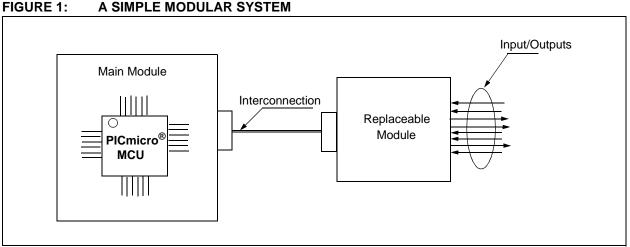

## A MODULAR SYSTEM

In the following sections, we will consider a simple system composed of two modules: a main module containing a microprocessor, and a replaceable module containing some kind of I/O circuitry. As a design constraint we will assume the replaceable I/O module to be very cost-sensitive. The main module will be able to recognize I/O module replacements and determine if the new modules are compatible. Compatibility will be considered granted if the new modules are "proved" to be manufactured from the same company that manufactures the main module or a licensed third party.

The reader will further note how the Interconnection represents in all respects a third important subsystem, with cost and reliability as the main constraints on its specification. For simplicity, we will consider it to be based on low cost cabling with as few contacts (wires) as possible.

## Notice:

This is a non-restricted version of Application Note AN825 which is available under the KEELOQ License Agreement. All Application Notes under the KEELOQ License Agreement are contained in the KEELOQ CD DS40038.

## SERIALIZATION OF MODULES

The first step in module production control involves the concept of Serialization. That is, every module produced must contain a unique Serial Number to identify it from among the entire production. Serialization is also obviously beneficial for quality control, maintenance programs, etc., although here we specify the Serial Number must be machine-readable. In other words, we require the replaceable module to be able to provide a unique number, in a digital form, upon request over the interconnection system. At any point in time (especially before making use of any of the replaceable module functions) the main module will request this unique number and compare it against a value in the main controller non-volatile memory. The main controller can use this Serial Number to implement various types of policies, such as:

- · identifying the valid replacements

- · logging its value through the application life

- using it for any sort of documentation of the system history for maintenance and/or warranty checking purposes

An optimal system would also require all replaceable modules to have some read/write non-volatile memory accessible through the same communication channel. Such non-volatile memory could then be used by the manufacturer to supply calibration data for the main processor to adjust the input/output signal conditioning (correcting gains and offsets for example), as well as allow the main board to log usage information.

### **AUTHENTICATION OF MODULES**

The problem with Serialization is in its simplicity. If the serial number is readable by the main module and its value is checked multiple times, then tapping into the interconnection system will easily provide this information. Production of multiple replacement modules with the same Serial Number is trivial. All the modules would appear the same to the main board. It would actually be impossible to detect any change or replacement.

In everyday life, we use IDs and signatures to authenticate individuals with the assumption that they cannot be easily counterfeited or duplicated. But in the digital world, duplicating a Serial Number is almost too easy. It is similar to the instance in a bank where, to get access to our accounts, we were requested to supply a password and we had to say it aloud in front of other people. If the password is fixed, then as soon as we use it, it is compromised.

A solution to the authentication problem, consists in making it possible to **deduce** whether something or somebody knows (or contains) a number (a password or a key) without ever communicating it, or exposing it to cloning.

#### **IDENTIFY FRIEND OR FOE (IFF)**

The IFF anti-cloning technique that is used in the following section is simple, yet very effective.

The term IFF is believed to be traced to its first use in the aviation industry, where it was employed in the radar systems to distinguish approaching Friend planes from the enemies (or Foes).

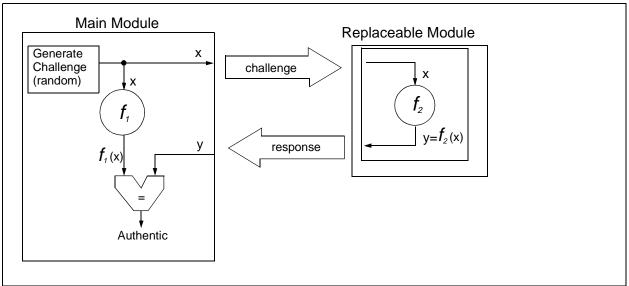

The main IFF concept is based on the use of formulas instead of fixed values during the authentication process. In our simple system, the main processor sends a large random number (usually referred to as the "challenge") to the replaceable module. The module would apply a convened formula to the challenge value, compute a "response" value and send it back to the main processor. The main processor would compare the returned value with the locally computed value. If the formula used by the replaceable module is the correct one, the main processor finds a match and accepts the new module as compatible or 'authentic', as shown in Figure 2. The reader will note how, during the entire transaction, no detail of the formula is ever communicated between the two modules. Tapping into the interconnection system will not reveal any information that could be used in the creation of a duplicate module, since the challenge value is always different, possibly even random.

For increased security, the process can be repeated as many times as required to achieve the requested level of confidence.

Of course there are many factors to be considered that influence the overall security of the system. Among these factors are:

- 1. the computational complexity of the formula

- 2. the bit length of the challenge and response

- 3. the encryption/decryption keys are never exchanged between the two modules

#### FIGURE 2: IFF OR CHALLENGE AND RESPONSE

## KEELOQ - IFF

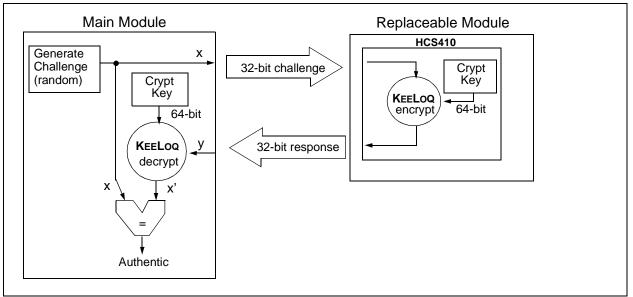

A KEELOQ IFF system adds a little twist to the standard IFF mechanism. The process takes advantage of the symmetrical nature of the KEELOQ block cipher. KEELOQ is a robust, field proven, 64-bit key encryption engine (block cipher) operating on 32-bit (data blocks): challenge and response. The method is illustrated by the following sequence of steps:

- 1. A 32-bit challenge (x) is generated by the Main Module (optimally as a random value).

- 2. The challenge is sent to the Replaceable Module.

- The Replaceable Module authentication device (HCS410) uses the KEELOQ encryption algorithm to generate a 32-bit Response (y) and sends it back.

- 4. The Main module applies the KEELOQ decryption algorithm to the 32-bit response generating a new 32-bit value (x').

- 5. The result of the decryption process (x') is compared with the original Challenge (x)

- 6. If the two values match, the Replaceable module is verified to be compatible and can be used further by the Main module.

If the Replaceable module is not compatible, any attempt to guess the right response value (y) for a given challenge (x) has a probability of  $1/2^{32}$  or in other words, one in four billion. The challenge and response process can then be repeated (looping through steps 1 to 6) to increase the verification security as required, effectively extending the equivalent challenge and response length by two, three. n-times.

The resulting level of security provided by this system would still not be recommended for high-level monetary transactions, where 128-bit key (and higher) systems are considered the norm. However, Embedded Applications in the consumer and industrial field can get an exceptional level of security while achieving an optimal compromise with system cost.

## THE HCS410 TRANSCODER

For the cost of a single KEELOQ HCS410 transcoder (transponder and encoder) device on the replaceable module, only one I/O line (one wire) in the interconnection, and a few lines of code on the main board processor, the user gets a very high level Authentication system, including serialization and R/W Nonvolatile Memory features.

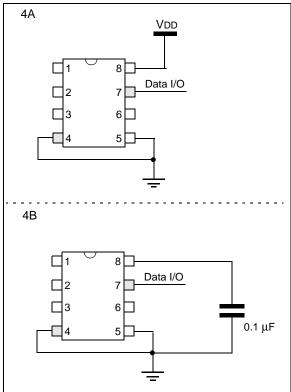

The HCS410 is available in an 8-pin SOIC (or DIP) package and requires no external components to operate to its full capabilities (see Figure 4, A). Its power supply ranges from 2V to 6.3V, with an operating current of less than 300  $\mu$ A at 6.3V, posing no constraints on the replaceable module power supply design.

From the details provided by the HCS410 Data Sheet [DS40158] we learn that it is designed to operate in three different modes:

- as an Hopping Code encoder

- as a contact-less Transponder (see Microchip literature [DS41116] for WM package details and availability)

- as a wired Authentication device operating in KEELOQ-IFF mode (often referred to in the Data Sheet as the IFF-W mode)

In this application we will employ the HCS410 only in this third mode.

#### FIGURE 4: HCS410 IFF-W CONNECTIONS

In the configuration illustrated in Figure 4(B), the power supply connection of pin 8 to VDD becomes redundant, as the part derives (internally) its power supply from the same I/O (pin 7 LCO) that is used for the bi-directional communication. In this case adding a 0.1  $\mu F$  capacitor (tank) on pin 8 is recommended.

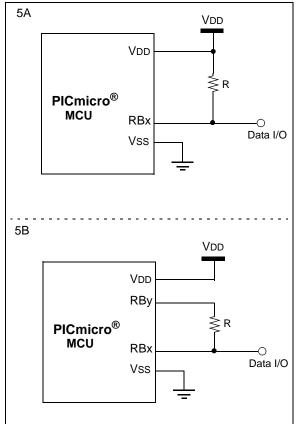

The HCS410 Data I/O line is the only added wire required for the system interconnection. Correspondingly, the processor on the main module will dedicate only one extra I/O for communication with the HCS410 (see Figure 5, A). An open collector I/O will be used if available or will be emulated, by switching dynamically the I/O line from the Output low state for a logic zero (pulse), to Input (tri-state) for a logic one condition, with an external pull up resistor. When communication with the HCS410 is not requested (Standby mode), power consumption can be minimized by the main processor controlling the pull-up resistor with a second I/O (RBy) Figure 5, B. When attempting communication with the HCS410 there will be a short additional delay, necessary to charge up the tank capacitor through the pull-up resistor and internal voltage regulator, before the device powers up.

#### FIGURE 5: PICmicro IFF-W CONNECTION

## **HCS410 IFF OPERATION**

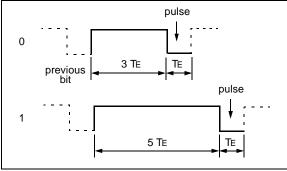

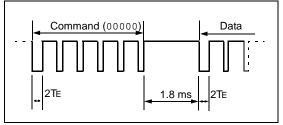

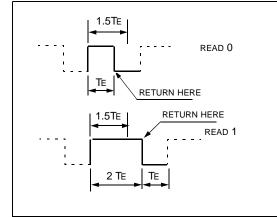

Communication with the HCS410 over the Data I/O line uses a Pulse Position Modulation format. The protocol is asymmetrical, meaning that the encoding of ones and zeros differs depending on the direction of communication. This also provides for power supply over the same data line, while optimizing communication speed. When communicating to the HCS410, data and command bits are expressed with the modulation format represented in Figure 6 below.

Where TE represents the basic Time Element which can be configured to be 100  $\mu s$  or 200  $\mu s$ , by setting appropriately the TBSL bit in the device configuration memory.

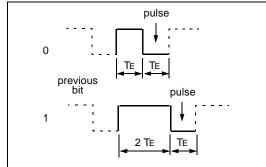

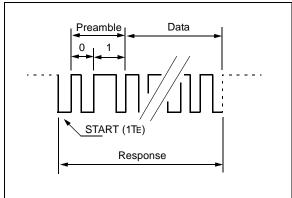

When the HCS410 sends data bits back, they are expressed with the modulation format represented in Figure 7 below.

#### FIGURE 7: RESPONSES FROM THE HCS410

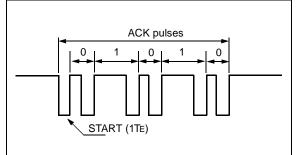

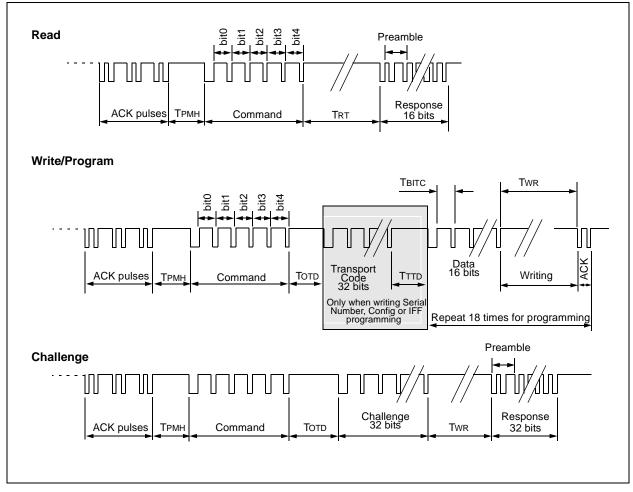

Communication activity with the HCS410 always starts with the wait for a specific 5-bit pattern of (01010) known as the Acknowledge Pulse, see Figure 8.

The device will send a new Acknowledge Pulse sequence immediately after a successful Power-up Reset, and will repeat the pattern periodically while waiting for a command.

The internal clock oscillator of the HCS410 is based on an RC circuit and can be calibrated by programming the OSCCAL bits in the device configuration memory. A device programmer can make use of the Acknowledge Pulse sequence to verify such calibration or to finely tune (auto-baudrate) the communication routines.

In the following, for simplicity, we will consider that the HCS410 clock oscillator has been calibrated.

#### FIGURE 8: ACKNOWLEDGE PULSES

All activity of the HCS410 is performed exclusively in response to specific 5-bit commands. The available commands offer a very powerful set of functions for Authentication applications:

- IFF-Encryption using one of two possible 64-bit keys stored in the device configuration memory

- Read and Write access to four independent 16-bit locations of nonvolatile memory (EEPROM)

- Read access to a 32-bit Serial Number, split in two 16-bit words for convenience

- Write access to the device Configuration word (protected by a special 32-bit transport code)

- The ability to reconfigure the entire device memory, including all keys and calibration parameters

#### TABLE 1: IFF COMMANDS

| Command | Description                      |

|---------|----------------------------------|

| 00001   | Read Configuration word          |

| 00010   | Read low serial number           |

| 00011   | Read high serial number          |

| 001XX   | Read user area (00, 01, 10, 11)  |

| 01000   | Configure HCS410                 |

| 01001   | Write Configuration word         |

| 01010   | Write low serial number          |

| 01011   | Write high serial number         |

| 011XX   | Write user area (00, 01, 10, 11) |

| 10001   | IFF Encryption using KEY-1       |

| 10101   | IFF Encryption using KEY-2       |

Commands must be sent to the HCS410 immediately after receiving the Acknowledge Pulse sequence. After completion of one command, the user must wait for the next Acknowledge Pulse sequence from the HCS410 before requesting a new operation. When sending a command to the HCS410 and subsequently, when sending packets of 16 or 32 data bits, a long START bit (2TE) is required as illustrated in Figure 9.

FIGURE 9: COMMAND-DATA START BIT

Commands that read and write to memory locations will require 16-bit packets of data to be sent after the command (and a short delay of 1.8 ms) and will respond with packets of the same size.

Encryption commands for authentication, require 32 bits of data to be sent after the command, and respond with the same data length.

Finally, configuration commands are protected by a special 32-bit code, known as the Transport Code. It acts as the secret combination of a safe, and prevents the device configuration from being lost, should a communication error transform a normal command into a configuration command.

Responses from the HCS410 on the contrary, are always preceded by a (single TE) START pulse, followed by a fixed preamble composed of a (0, 1) pattern as shown in Figure 10.

FIGURE 10: RESPONSE PREAMBLE

A more complete summary of the IFF commands and waveforms can be found in Figure 11 and Table 2.

#### TABLE 2: IFF TIMING PARAMETERS

| Parameter                                     | Symbol | Minimum    | Typical | Maximum | Units |

|-----------------------------------------------|--------|------------|---------|---------|-------|

| PPM Command Bit Time<br>Data = 1<br>Data = 0  | Твітс  | 3.5<br>5.5 | 4<br>6  |         | TE    |

| PPM Response Bit Time<br>Data = 1<br>Data = 0 | TBITR  |            | 2<br>3  |         | TE    |

| PPM Command Minimum High Time                 | Трмн   | 1.5        | —       | —       | TE    |

| Response Time (Minimum for Read)              | Trt    | 6.5        | —       | —       | ms    |

| Opcode to Data Input Time                     | Тотр   | 1.8        | —       | —       | ms    |

| Transport Code to Data Input Time             | Τττο   | 6.8        | —       | —       | ms    |

| IFF EEPROM Write Time (16 bits)               | Twr    | —          | —       | 30      | ms    |

#### **APPLICATION SOFTWARE**

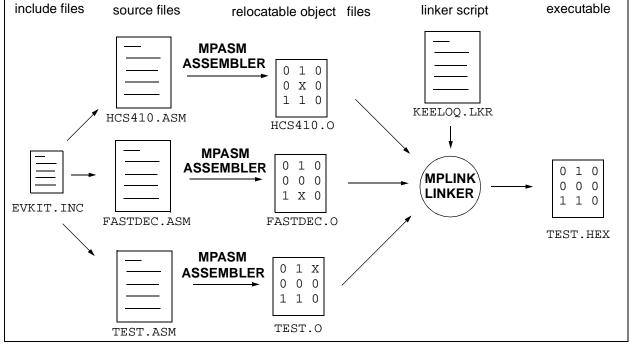

The following sections of this Application Note will concentrate on the software. We will develop a small set of functions for communication with an HCS410 in authentication applications. The code was written as a set of relocatable object modules. While the use of relocatable modules and a linker is natural for high level language programmers, many programmers familiar with the Microchip PICmicro assembler MPASM<sup>TM</sup>, might not be familiar with the use of MPLINK<sup>TM</sup> object linker and the techniques required to produce relocatable object modules in assembler. Figure 12 illustrates the adopted project structure. For convenience, as a hardware target we used the KEELOQ Evaluation Kit II (DM303006) as the Main module, and we will use the prototype area to connect an HCS410 in the configuration represented in Figure 4 (B).

The demonstration code can be downloaded to the PIC16F877 present on the demo board through the serial port using the Evaluation Kit windows software (Download Firmware function). Alternatively the user will be able to connect the In-Circuit Debugger MPLAB<sup>®</sup> ICD to the J4 connector on the same demo board. This second arrangement will also permit the user to insert breakpoints and view the contents of RAM and EEPROM while exploring the code and the device functionality.

FIGURE 12: PROJECT STRUCTURE

As shown in Figure 12, there are several source files that contribute to the creation of the demonstration application. In order of importance, these files are:

- the EVKIT.H include file, containing the definitions of all the I/Os of the PIC16F877 that controls the KEELOQ EVALUATION KIT II main board

- the HCS410.ASM module, containing all the communication specific functions that will be analyzed in detail in the following sections

- the FASTDEC. ASM module, containing the standard KEELOQ decrypt module

- the TEST.ASM module, containing the Main Loop of the demonstration application

- the KEELOQ.LKR linker script, that defines the memory allocation rules to be used by the linker when assembling the object modules together.

#### WRITING RELOCATABLE CODE

The reader should refer to the "*MPASM*<sup>TM</sup> User's Guide with MPLINK<sup>TM</sup> and MPLIB<sup>TM</sup> (DS33014) for more details and programming examples with special reference to Chapter 4: "Using MPASM<sup>TM</sup> to create Relocatable Objects."

## THE HCS410 MODULE

The HCS410 module exports four global functions for easy access to the main functionality offered by the HCS410 transcoder. They are:

- 32-bit data Encryption with one of two 64-bit keys

- Read access to non volatile memory (4 x 16 bits)

- Write access to non volatile memory (4 x 16 bits)

- 32-bit Serial Number read

The module uses four RAM locations (in an overlay segment) as local variables and temporaries, and it references to one external 32-bit buffer (HOP0..HOP3) for data I/O.

In order to keep the code simple and let the reader concentrate on the core concepts of the communication mechanism, all of the HCS410 communication routines have been written for the most generic PICmicro MCU using only the Watchdog Timer (as a time-out mechanism) in all waiting loops. This means that if, at any time, the communication fails, or the HCS410 does not respond (or is missing from the replaceable module), the Main module will RESET, preventing the application from executing further.

The following sections will describe the design and use of the routines composing the  ${\tt HCS410.ASM}$  module from the bottom up.

The Delay routine provides multiple of 4  $\mu$ s delays and adapts to three different clock frequencies; 4 MHz,

8 MHz and 20 MHz depending on the definition of the CLOCK variable (by default CLOCK is defined to be equal to 20 MHz that is the oscillator frequency used by the KEELOQ Evaluation Kit II demo board.

The WaitFall function is one of the main building blocks of the communication routine. Its role is fundamental in the receiving of the special PPM modulation format used by the HCS410 device. WaitFall loops, polling the Data I/O line until a falling edge is detected (pulse) and returns with a '0' or a '1', depending on whether the pulse was detected before or after a specific lapsed time (1.5 TE).

#### FIGURE 13: WAITFALL OPERATION

The ReceiveData function uses the WaitFall function to discriminate actual data bits sent by the HCS410. ReceiveData also synchronizes on the START pulse and discards the Preamble (0,1) pattern. The Preamble pattern is extremely valuable in wireless applications to distinguish the transcoder response from the reader circuit noise, but in a wired application, such as the one we are developing, there is no use for it. Receive Data assembles CNTBIT bits in bytes and proceeds filling the HOP buffer.

The inner loop, labeled ReceiveBit, is also used by the GetACK function to capture the Acknowledge pulses and compare them against the specific (01010) ACK pattern.

The function SendData, performs the opposite task, sending CNTBIT bits from the HOP buffer over the Data I/O line, according to the defined PPM format.

The SendCommand function uses the inner loop of the SendData function to send a 5-bit command.

Finally, let's review the main four functions that the  ${\tt HCS410.ASM}$  declares as global for other modules to use.

Encrypt1 and Encrypt2 respectively request the HCS410 to perform KEELOQ encryption on a 32-bit challenge value taken from the HOP buffer, using the first or second 64-bit key available. The function will return with the 32-bit response in the same HOP buffer.

ReadUserData requests the HCS410 to perform a 16bit data read command from one of the four User memory locations according to the value of the W register upon call (0,1,2,3). In addition to that, if W contains the value -1 (0xFF) the 16-bit data returned will be the 16 LSb's of the device Serial Number. If W contains the value -2 (0xFE), the 16-bit data returned will be the 16 MSb's of the device Serial Number.

WriteUserData similarly requests the HCS410 to write a 16-bit data to one of the four User memory locations according to the value contained in the W register upon call (0,1,2,3). A write to the Serial Number locations, similarly to the operation of the ReadUserData command, is not supported in the current version (such command would require sending additional 32 bits of Transport Code before the data).

## THE FASTDEC MODULE

The FASTDEC.ASM module contains a fast implementation of the KEELOQ Decryption algorithm. It declares a single GLOBAL label Decrypt. This function requires the FSR register to point to an 64-bit array (8 bytes) containing the Crypt Key to be used and operates on an EXTERN 32-bit buffer (HOP0..HOP3) which is holding the data. The decryption function performs 32-bit data decryption in about 16,000 Tcycles (corresponding to about 3 ms @ 20 MHz) and returns the 32bit output in the same buffer (HOP0..HOP3).

As in every good encryption system, security must not rely on the secrecy of the algorithm used, but solely on the secrecy of the crypt keys used. In a KEELOQ system, there is no exception to this rule: proper key management is vital. In fact, while the KEELOQ algorithm is not secret (although it is patented and released only under license), the secrecy of the crypt keys chosen is of utmost importance. In many KEELOQ Hopping code applications, it is recommended to use special Key Generation techniques, (simple, normal, secure, etc.), to make the key used by every single unit different and unique. In KEELOQ IFF technology this is not necessary, because of its very nature, the challenge/response system already provides a very high level of security (provided a good random generation algorithm is used for calculating the challenge).

It must be remembered, however, that if a simple single crypt key (Manufacturer's Code) system is chosen, then the disclosure of this 64-bit value to third parties and subcontractors becomes extremely critical.

## THE TEST MODULE

The TEST. ASM module contains some basic code to initialize the PICmicro MCU for the Evaluation Kit II board hardware configuration and to demonstrate the functionality of the HCS410 module.

In detail, the main loop will cyclically perform the following operations:

- 1. Request the Serial Number.

- 2. Write to all three 16-bit locations in User non-volatile memory.

- 3. Read back the written values.

- 4. Generate a pseudo random challenge (using the KEELOQ decrypt function with a different key provides a good random number generator.

- 5. Send the challenge and request an Encryption with one of the two keys contained in the HCS410 device.

- 6. Send the response to the Fastdec function and, finally, compare it to the original challenge.

If there is a match, the loop continues. Otherwise, an error is reported and the board RESETS.

#### MODULE AUTHENTICATION APPLICATIONS

It must be noted that there are two main categories of applications where the Module Authentication system, as illustrated in this Application Note, can be conveniently employed. The difference between the two can be better explained with example applications. The first category, "closed systems", can be represented by a cellular phone and its battery pack. Let's say the HCS410 (authentication device) is placed in the battery pack and one contact is added to the battery to allow for the IFF bi-directional communication. This would force the replacement of the battery with the manufacturer's original batteries only. If a user wants to bypass the authentication mechanism, the phone (a closed system) must be disassembled. This not only voids any warranty, but is also perceived by the average user as a risky operation and is unlikely to be performed. On the contrary, in an "open system" such as an industrial rack-mounted stack module (or the one presented at

the beginning of this Application Note), there is no restriction to work-around the authentication module, since there is easy access to the interconnection system. The key to effective use of module authentication in "open systems" is to make the authenticating device an "essential" part of the system. In the replaceable module example, this would mean storing some essential configuration information such as gain or offset values of the analog I/Os present. in the User nonvolatile memory area of the HCS410. Without those values, the system cannot perform any useful operations.

## **MEMORY USAGE**

Program memory used: 324 words.

RAM memory used: 20 bytes.

## CONCLUSIONS

The code presented shows how effective the use of an HCS410 transcoder can be in a module authentication application. In summary:

- KEELOQ IFF technology offers 64-bit security in a low cost device.

- The HCS410.ASM relocatable object module can be linked in any existing application with minimal load on the PICmicro MCU resources.

- A single pin added to the interconnection system (single wire) provides an effective bi-directional communication path.

- Four 16-bit locations of R/W memory provide space for calibration data and/or usage statistics.

- A 32-bit serial number (read-only) allows module tagging and effective production and maintenance tracking.

There is still ample room for extension of this application code. The HCS410 includes a full Anti-Collision system that would allow the connection of multiple (HCS410) devices on a single wire, in a bus-like configuration. Authentication of multiple modules using a single PICmicro MCU I/O would be possible on such a bus.

Further time-outs could be explicitly controlled by the use of timers (instead of the sole Watchdog Timer), to provide module "hot swapping" capabilities, such as multiple modules insertion/extraction detection.

## AN827

## REFERENCES

| DS91002 | TB003 Introduction to KEELOQ Technology                      |

|---------|--------------------------------------------------------------|

| DS91000 | TB001 Secure Learning RKE systems<br>using KEELOQ Technology |

| DS40158 | HCS410 Device Data Sheet                                     |

| DS00742 | AN742 Modular Mid Range Decoder                              |

| DS00744 | AN744 Modular Mid Range Decoder in C                         |

| DS91041 | KEELOQ Decryption Routines in C                              |

| DS00824 | KEELOQ Encoders Oscillator Calibration                       |

| DS00655 | Using KEELOQ to Generate Hopping Code<br>Passwords           |

#### Software License Agreement

The software supplied herewith by Microchip Technology Incorporated (the "Company") for its PICmicro® Microcontroller is intended and supplied to you, the Company's customer, for use solely and exclusively on Microchip PICmicro Microcontroller products.

The software is owned by the Company and/or its supplier, and is protected under applicable copyright laws. All rights are reserved. Any use in violation of the foregoing restrictions may subject the user to criminal sanctions under applicable laws, as well as to civil liability for the breach of the terms and conditions of this license.

THIS SOFTWARE IS PROVIDED IN AN "AS IS" CONDITION. NO WARRANTIES, WHETHER EXPRESS, IMPLIED OR STATU-TORY, INCLUDING, BUT NOT LIMITED TO, IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICU-LAR PURPOSE APPLY TO THIS SOFTWARE. THE COMPANY SHALL NOT, IN ANY CIRCUMSTANCES, BE LIABLE FOR SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES, FOR ANY REASON WHATSOEVER.

#### APPENDIX A: EVKIT.INC SOURCE CODE

```

;*

;** EvKit II include file

; * *

;* 09/27/01 LDJ updated

;*

#define TRUE 1

#define FALSE 0

;// serial port

#define RTS PORTC,0 ;// o

#define CTS

PORTC,5 ;// i

#define TX_232 PORTC,6 ;// o

#define RX_232 PORTC,7 ;// i

;// LCD display

#define DB4 PORTD,0 ;//i/o

PORTD,1 ;//i/o

#define DB5

#define DB6 PORTD,2 ;//i/o

#define DB7 PORTD,3 ;//i/o

#define RW PORTD,4 ;// o select RD or Write

#define RS PORTD,5 ;// o select register

#define LCD_E PORTD,6 ;// o chip select

;// programming Socket

#define LED PORTD,7 ;// o switch on the yellow LED

#define VDD PORTD,7 ;// o set socket VDD pin to 5V

PORTD,7 ;// o set socket VDD pin to 5V

;// encoder programming

#define S0 PORTB,0 ;// o clock

#define S1

PORTB,1 ;// o

#define S2 PORTB,2 ;// o

#define S3 PORTB,3 ;// o

#define DATA PORTA,5 ;// i/o data

;// Step up circuit

#define VPPON PORTA,4 ;// o apply voltage

#define STEPOUT PORTC, 2 ;// o PWM output pin

#define VPPRST PORTB,5 ;// o clears Vpp/ reset part

#define STEPIN PORTA,0 ;// i analog input

;// HCS512 programming

#define DAT512 PORTA,2 ;// i/o

#define CLK512 PORTA,1 ;// i/o

#define MCL512 PORTB,4 ;// i MCLR line

```

;// HCS515/HCS500 programming #define DAT515 PORTE,2 ;// i/o #define CLK515 PORTA,3 ;// i/o ;// transponder interface #define PWM\_COIL PORTC,1 ;// o 125kHz carrier #define COIL\_IN PORTE,1 ;// i reading transponder #define COIL\_ON PORTB,0 ;// o activate resonant circuit ;// radio receiver #define RFIN PORTE,0 ;// i radio input ;// i2c interface #define SCL PORTC,3 ;// o Serial Clock #define SDA PORTC,4 ;// i/o Serial Data ;#define TRIS\_SDA TRISC4 ;// keypad interface #define BOOT PORTB,4 ;// i BOOT button PORTB,0 ;// o rows #define ROW0 #define ROW1 PORTB,1 ;// o PORTB,2 #define ROW2 ;// o PORTB, 3 ;// o #define ROW3 #define COL0 PORTB,4 ;// i columns #define COL1 PORTB,5 ;// i #define COL2 PORTB,6 ;// i #define COL3 PORTB,7 ;// i ;// init masks ;// clock/data lines to decoders are default to float at init #define DEFPA b'11101111'; // x x DATA VPPON CLK515 DAT512 CLK512 STEPIN #define DEFPB b'11010000'; // COL3 COL2 VPPRST COL0 S3 S2 S1 S0/COIL\_ON #define DEFPC b'10110110'; // RX\_232 TX\_232 CTS SDA SCL STEPOUT PWM\_COIL RTS ;// STEPOUT defaults to input until used (external pull down) #define DEFPD b'0000000'; // LED E RS RW DB7..DB4 #define DEFPE b'11101111'; // x x x !PSP x DAT515 COIL\_IN RFIN #include <pl6f877.inc> ; debugging macro, outputs 1 literal digit on LCD connector DEBUG MACRO LIT movlw LIT & 0x0f iorwf PORTD, F nop nop 0xf0 movlw

andwf

ENDM

PORTD, F

## APPENDIX B: TEST.ASM

|            |                                            |                                                         |     | table" ENCRYPT routine                                                     |  |

|------------|--------------------------------------------|---------------------------------------------------------|-----|----------------------------------------------------------------------------|--|

| ;          | using an HCS410 in IFF-W mode<br>radix hex |                                                         |     |                                                                            |  |

| i          | nclude                                     | <evkit.inc:< td=""><td>&gt;</td><td></td></evkit.inc:<> | >   |                                                                            |  |

|            |                                            |                                                         |     | <pre>; encryption lib module exports ; decryption lib module exports</pre> |  |

| ;;         |                                            |                                                         |     |                                                                            |  |

| ,<br>BANK1 |                                            | UDATA                                                   |     | ; make sure gets allocated in BANKO                                        |  |

|            | RES                                        |                                                         | ; ( | crypto key stored lsb first                                                |  |

| KEY1       | RES                                        | 1                                                       |     |                                                                            |  |

|            | RES                                        |                                                         |     |                                                                            |  |

| KEY3       | RES                                        | 1                                                       |     |                                                                            |  |

| KEY4       | RES                                        | 1                                                       |     |                                                                            |  |

| KEY5       | RES                                        | 1                                                       |     |                                                                            |  |

| KEY6       | RES                                        | 1                                                       |     |                                                                            |  |

| KEY7       | RES                                        | 1                                                       | ; ( | crypto key msb                                                             |  |

| BANK0      |                                            | UDATA                                                   |     |                                                                            |  |

|            |                                            |                                                         | ; ] | hopping code 32 bit register                                               |  |

|            |                                            | 1                                                       |     |                                                                            |  |

| HOP2       |                                            |                                                         |     |                                                                            |  |

| HOP3       | RES                                        | 1                                                       |     |                                                                            |  |

| SN         | RES                                        | HOP0, HOP1,<br>4<br>4                                   | ; † | temp storage for Serial Number                                             |  |

|            | UP<br>oto                                  | CODE<br>START                                           |     |                                                                            |  |

| C          | ODE                                        |                                                         | ; r | eset vector                                                                |  |

| START      |                                            |                                                         |     |                                                                            |  |

| ba<br>mo   | anksel                                     | TRISA<br>DEFPA<br>TRISA                                 |     |                                                                            |  |

| m          | ovlw<br>ovwf<br>ovlw                       |                                                         |     |                                                                            |  |

|            |                                            | TRISC                                                   |     |                                                                            |  |

|            |                                            | DEFPD                                                   |     |                                                                            |  |

|            | ovwf                                       |                                                         |     |                                                                            |  |

|            | ovlw                                       | DEFPE                                                   |     |                                                                            |  |

|            | ovwf                                       |                                                         |     |                                                                            |  |

| m          | anksel<br>ovlw<br>ovwf                     | ADCON1<br>0x0e<br>ADCON1                                | ; 1 | ANO only analog input                                                      |  |

| ba<br>mo   | anksel<br>ovlw                             | OPTION_REG                                              | ';] | prescaler to WDT 1:8                                                       |  |

; init CRYPTO KEY banksel KEY0 movlw0xEF ; lsb movwfKEY0 movlw0xCD movwfKEY1 movlw0xAB movwfKEY2 movlw0x89 movwfKEY3 movlw0x67 movwfKEY4 movlw0x45 movwfKEY5 movlw0x23 movwfKEY6 movlw0x01 movwfKEY7 ; msb ; load init value for challenge banksel CHG movlw 0x67 movwf CHG+0 movlw 0x45 movwf CHG+1 movlw 0x23 movwf CHG+2 movlw 0x01 movwf CHG+3 MainLoop ; 1. read Serial Number locations movlw -1 ; SN 16 Lsb ReadUser call movf HOP0,W ; save value in local variable movwf SN+0 movf HOP1,W SN+1 movwf movlw -2 ; SN 16 Msb call ReadUser movf HOP0,W ; save value in local variable SN+2 movwf movf HOP1,W movwf SN+3 ; 2. write to all EEPROM USER locations (4321) movlw 21 movwf HOP0 movlw 43 movwf HOP1 ; write to EEPROM location 0 movlw 0 call WriteUser ; write to EEPROM location 1 movlw 1 WriteUser call ; write to an EEPROM location 2 movlw 2 call WriteUser

```

; write to an EEPROM location 3

movlw

3

call

WriteUser

; 3. read back values from USER EEPROM locations

; read EEPROM location 0

movlw

0

call

ReadUser

; read EEPROM location 1

movlw 1

call

ReadUser

; read EEPROM location 2

movlw 2

call

ReadUser

; read EEPROM location 3

movlw

3

call

ReadUser

; 4. generate a new challenge (and turn off LED)

; challenges should be randomized,

; Hint: use again Keeloq with a different Crypt Key

to act as a random number generator

; for simplicity a sequential challenge generation is used here

bcf

LED

incf

CHG+0,F

btfsc STATUS,Z

incf

CHG+1,F

; move challenge into data buffer

movf

CHG+0,W

movwf

HOP0

movf

CHG+1,W

HOP1

movwf

movf

CHG+2,W

movwf

HOP2

movf

CHG+3,W

movwf

HOP3

; 5. call HCS410 encrypt library function

call

Encrypt1

; 6. verify the response using Keeloq Decrypt

movlw

KEY0

; enter with W pointing to CRYPTO KEY

call

Decrypt

movf

HOP0,W

; compare decrypted response with challenge

CHG+0,W

xorwf

btfss

STATUS, Z

goto

AError

movf

HOP1,W

; compare decrypted response with challenge

xorwf

CHG+1,W

btfss

STATUS, Z

goto

AError

movf

HOP2,W

; compare decrypted response with challenge

CHG+2,W

xorwf

btfss

STATUS, Z

goto

AError

movf

HOP3,W

; compare decrypted response with challenge

xorwf

CHG+3,W

btfss

STATUS,Z

goto

AError

```

| if  | succ | essful | turn                     | LED | on |                                      |

|-----|------|--------|--------------------------|-----|----|--------------------------------------|

| bsf |      | LED    |                          |     |    |                                      |

|     |      |        |                          |     |    |                                      |

|     |      |        | if successful<br>bsf LED |     |    | if successful turn LED on<br>bsf LED |

; 7. loop goto MainLoop

AError

goto 0 ; reset in case of error

END

\_

#### APPENDIX C: HCS410.INC

;\* Filename: HCS410.INC ;\* Author: Lucio Di Jasio

;\* Company: Microchip Technology

;\* Revision: Rev 1.00 ;\* Date: 28/SEP/01 ; \* ;\* include file that exports: ;\* relocatable library function for HCS410 use ;\*

EXTERN Encrypt1, Encrypt2, ReadUser, WriteUser

#### APPENDIX D: HCS410.ASM

```

Software License Agreement

; The software supplied herewith by Microchip Technology Incorporated

; (the "Company") for its PICmicro® Microcontroller is intended and

; supplied to you, the Company's customer, for use solely and

; exclusively on Microchip PICmicro Microcontroller products. The

; software is owned by the Company and/or its supplier, and is

; protected under applicable copyright laws. All rights are reserved.

; Any use in violation of the foregoing restrictions may subject the

; user to criminal sanctions under applicable laws, as well as to

; civil liability for the breach of the terms and conditions of this

; license.

; THIS SOFTWARE IS PROVIDED IN AN "AS IS" CONDITION. NO WARRANTIES,

; WHETHER EXPRESS, IMPLIED OR STATUTORY, INCLUDING, BUT NOT LIMITED

; TO, IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A

; PARTICULAR PURPOSE APPLY TO THIS SOFTWARE. THE COMPANY SHALL NOT,

; IN ANY CIRCUMSTANCES, BE LIABLE FOR SPECIAL, INCIDENTAL OR

; CONSEQUENTIAL DAMAGES, FOR ANY REASON WHATSOEVER.

;* Filename: HCS410.ASM

;* Author:

Lucio Di Jasio

;* Company: Microchip Technology

;* Revision: Rev 1.00

; *

Date:

28/SEP/01

; *

;*

relocatable module that implements:

; *

Encrypt function challenging an HCS410 in IFFW

; *

encrypts the 32 bits hopping in IN HOPO (LSB) TO HOP3(MSB)

; *

W contains pointer to HOPO

;* NOTE:

;*

local variables are assumed to be in BANKO

;*

HOP must be in BANK0 or BANK1

assembled using MPASM v02.61

; *

;*

include "evkit.inc"

; Keelog Evaluation Kit II board I/O defs

#define TWENTYMHZ 5

#define EIGHTMHZ

2

#define FOURMHZ

1

#define CLOCK TWENTYMHZ

EXTERN HOPO, HOP1, HOP2, HOP3

;------

; HCS410 commands

#define HCS410_RCFG 0x01

;// read config word

;// read SN high

#define HCS410_RSNH 0x03

#define HCS410_RSNL 0x02

;// read SN low

;// read USER area #0

#define HCS410_RU0 0x04

#define HCS410_RU1 0x05

;//

#1

0x06

н

#define HCS410_RU2

;//

#2

"

#define HCS410_RU3

0x07

;//

#3

#define HCS410_WU0

0x0c

;// write USER area #0

"

#define HCS410_WU1

0x0d

;//

#1

#define HCS410 WU2 0x0e

;//

#2

;// "

#define HCS410_WU3 0x0f

#3

#define HCS410_ENC1 0x11

;// challenge resp. 32Bit Keyl Encrypt

#define HCS410_ENC2 0x15

;// challenge resp. 32Bit Key2 Encrypt

```

```

;-----

; Macros to control the DATA line

; implementation specific to the Keeloq Evaluation Kit II board

;

; default condition (DATA line pull-up)

PULLUP MACRO

banksel

TRISA

bsf

DATA

; make it input

banksel

PORTA

ENDM

; PPM pulse condition (DATA line to GND)

PULSE MACRO

banksel

TRISA

bcf

DATA

; make it output

banksel

PORTA

bcf

DATA

; drive LOW

ENDM

UDATA_OVR

; defines local variables (in reusable mem)

WORK

RES

1

TMP

RES

1

CNTBIT RES

1

DLY

RES

1

.hcs410 CODE

;-----

-----

Encrypt1

GLOBAL Encrypt1

call GetACK

; sycnhronize

; send authentication request

movlw HCS410_ENC1

; encrypt request

goto

Encrypt

;-----

_____

Encrypt2

GLOBAL Encrypt2

call GetACK

; sycnhronize

; send authentication request

movlw HCS410_ENC2

; encrypt request

Encrypt

call

SendCommand

; send challenge (data to be encrypted)

movlw .32

SendData

call

; wait for response

movlw .32

ReceiveData

call

return

; Read User Data

; INPUT

;

W

0..3 select User Location

-1 = Serial Number L

;

```

## AN827

```

;

-2 = Serial Number H

; OUTPUT:

HOP0, HOP1 data read form user memory

;

;

ReadUser

GLOBAL ReadUser

addlw HCS410_RU0

; make it a 410 command

movwf HOP3

; save in temp

call

GetACK

; synchronize

movf

HOP3,W

; send comand

SendCommand

call

movlw

.16

call

ReceiveData

; read back 1 x16 bit word

return

;------

; Write User Data

; INPUT

W

0..3 select User Location

;

HOP0, HOP1 data to write in user memory

;

:

WriteUser

GLOBAL WriteUser

addlw HCS410_WU0 ; make it a 410 command

movwf HOP3

; save in temp

call

GetACK

; synchronize

HOP3,W

movf

; send comand

call

SendCommand

movlw .16

call

SendData

; read back 1 x16 bit word

return

;------

; Delay W x 4us

; INPUT

W delay requested

;

;

DelayWx4us

movwf DLY

; DLY x 4us

DelayL

nop

; 1 Tcy

if CLOCK > FOURMHZ

goto $+1

; 4 Tcy

goto

$+1

endif

if CLOCK > EIGHTMHZ

goto $+1

; 12 Tcy

goto

$+1

goto $+1

;

goto $+1

goto $+1

;

goto $+1

endif

decfsz DLY,F

; +3 Tcy

goto

DelayL

retlw 0

;-----

; Wait for a Falling Edge

```

```

;

; INPUT

W timeout value

;

; timeout = DLY x .16Tcy

#define KTO

.16

WaitFall

movwf DLY

WaitFallL

nop

; 1 Tcy

$+1

goto

goto

$+1

goto

$+1

$+1

goto

$+1

;

qoto

btfss DATA

retlw 0

; return with edge

decfsz DLY,F

goto WaitFallL

; if long wait some more until it falls

WaitFallTOL

btfsc DATA

goto WaitFallTOL

retlw 1

; return with TO

;-----

; GetACK

;

loops until it receives a correct ACK pattern

;

GetACK

PULLUP

; power up the device

movlw .250*CLOCK/KTO

call DelayWx4us ; pause 1ms

; wait for ACK signal

movlw TMP

movwf FSR

; TMP will receive the data

3

; read 3 bit (preceded by 01)

movlw

movwf CNTBIT

call ReceiveBit

movf TMP,W

andlw b'11100000'

; compare (upper) three bit

; match with 010 ACK pattern

xorlw b'01000000'

btfss STATUS,Z

goto

GetACK

; if not keep waiting

return

;-----

; ReceiveData

;

; INPUT :

; W number of bit to receive

; OUTPUT:

; HOP0..HOP3 received data

;

ReceiveData

movwf CNTBIT

movlw HOP0

; init pointer

movwf FSR

```

```

ReceiveBit

```

## AN827

```

; wait for start falling edge (WDT timeout)

btfsc DATA

goto

ReceiveBit

; discard first two bit 01 (synch pattern)

WR1

btfss DATA

goto

WR1

WF1

btfsc

DATA

WF1

goto

WR2

btfss

DATA

WR2

goto

WF2

btfsc

DATA

goto

WF2

ReceiveNBL

btfss

DATA

; waiting for the new rising edge

goto

ReceiveNBL

; measure the delay before next gap

movlw .300*CLOCK/KTO ; timeout at 300us (1.5xTE)

call

WaitFall

movwf

WORK

rrf

WORK, F

; move bit to carry

; rotate bit in lsb first

rrf

INDF,F

WR3

btfss DATA

; wait until you get to the next gap

goto

WR3

; loop for every bit

decf

CNTBIT,F

movlw 0x7

; every 8 bit increment pointer

andwf CNTBIT,W

btfsc STATUS,Z

incf

FSR,F

movf

CNTBIT,F

btfss STATUS,Z

ReceiveNBL

goto

return

;------

; SendData

;

; INPUT

W number of bit to send

;

HOP0..HOP3 data to send

;

SendData

movwf

CNTBIT

movlw HOP0

; init pointer

movwf

FSR

SendCMD

movlw

.250

; max delay 256x4us = 1ms

call

DelayWx4us

movlw

.250

; max delay 256x4us = 1ms

call

DelayWx4us

.250

; max delay 256x4us = 1ms

movlw

call

DelayWx4us

movlw

.250

; max delay 256x4us = 1ms

```

```

call

DelayWx4us

PULSE

.100

movlw

call

DelayWx4us

; 2 x TE = 100x4us = 400us

;

; loop for CNTBIT

SendNBL

PULLUP

rrf

; lsb first

INDF,F

movlw

.150

; bit 0-> 3 x TE = 150x4us = 600us

btfsc

STATUS,C

; bit 1-> 5 x TE = 250x4us = 1000us

movlw

.250

call

DelayWx4us

PULSE

movlw

.50

; 1x TE = 50x4us = 200us

call

DelayWx4us

; count bit out

CNTBIT,F

decf

movlw

0x7

; every 8 bit increment pointer

andwf

CNTBIT,W

SKPNZ

incf

FSR,F

movf

CNTBIT,F

btfss

STATUS,Z

goto

SendNBL

PULLUP

return

;------

; Send Command

;

; INPUT

;

W HCS410_ command

;

SendCommand

movwf

TMP

; save command in temp

movlw

TMP

; make FSR point to it

movwf

FSR

5

; send 5 bit

movlw

movwf CNTBIT

SendCMD

; enter send data subroutine

qoto

```

END

## APPENDIX E: KEELOQ.LKR

// File: keeloq.lkr // Sample linker command file for mid-range with: // 1 ROM page(2k), 2 RAM banks // Lucio Di Jasio 09/26/01 11 LIBPATH . CODEPAGENAME=vectorsSTART=0x0END=0x4PROTECTEDCODEPAGENAME=pageSTART=0x5END=0x7FFCODEPAGENAME=.idlocsSTART=0x2000END=0x2003PROTECTED CODEPAGE NAME=.config START=0x2007 END=0x2007 PROTECTED DATABANK NAME=sfr0 START=0x0 END=0x1F PROTECTED START-0v80 שזא הם הידי הם NAME-ofr1 FND=0-9F

| DATABANK                                            | NAME=sfr1                                                                               | START=0x80                                                                     | END=0x9F                                                         | PROTECTED                                                                        |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------|

| DATABANK<br>DATABANK                                | NAME=gpr0<br>NAME=gpr1                                                                  | START=0x20<br>START=0xA0                                                       | END=0x6F<br>END=0xBF                                             | PROTECTED                                                                        |

| SHAREBANK<br>SHAREBANK                              | NAME=gprnobnk<br>NAME=gprnobnk                                                          |                                                                                | END=0x7F<br>END=0xFF                                             |                                                                                  |

| SECTION<br>SECTION<br>SECTION<br>SECTION<br>SECTION | NAME=STARTUP<br>NAME=PROG<br>NAME=IDLOCS ROI<br>NAME=CONFIG<br>NAME=BANK0<br>NAME=BANK1 | ROM=vectors<br>ROM=page<br>M=.idlocs //<br>ROM=.config<br>RAM=gpr0<br>RAM=gpr1 | <pre>// ROM code s ID locations // Configurat // allocates</pre> | interrupt vectors<br>space<br>tion bits location<br>ram in bank0<br>ram in bank1 |

## APPENDIX F: FASTDEC.INC

| ;;************************************* |                                                    |                                         |  |  |  |

|-----------------------------------------|----------------------------------------------------|-----------------------------------------|--|--|--|

| ; *                                     | Filename:                                          | FASTDEC.INC                             |  |  |  |

| ;**                                     | ; * * * * * * * * * * * * * * * * * * *            |                                         |  |  |  |

| ;*                                      | Author:                                            | Lucio Di Jasio                          |  |  |  |

| ;*                                      | Company:                                           | Microchip Technology                    |  |  |  |

| ;*                                      | Revision:                                          | Rev 1.00                                |  |  |  |

| ; *                                     | Date:                                              | 26/SEP/01                               |  |  |  |

| ; *                                     |                                                    |                                         |  |  |  |

| ; *                                     | include fil                                        | e that exports:                         |  |  |  |

| ;*                                      | ;* relocatable library function for Keeloq Decrypt |                                         |  |  |  |

| ; *                                     | ;* decrypts the 32 bits in HOPO (LSB) TO HOP3(MSB) |                                         |  |  |  |

| ; *                                     | ;* uses W as pointer to KEYO                       |                                         |  |  |  |

| ;*                                      |                                                    |                                         |  |  |  |

| ; *                                     |                                                    |                                         |  |  |  |

| ;**                                     | * * * * * * * * * * * *                            | *************************************** |  |  |  |

EXTERN Decrypt

NOTES:

\_

Microchip's Secure Data Products are covered by some or all of the following patents:

Code hopping encoder patents issued in Europe, U.S.A., and R.S.A. — U.S.A.: 5,517,187; Europe: 0459781; R.S.A.: ZA93/4726 Secure learning patents issued in the U.S.A. and R.S.A. — U.S.A.: 5,686,904; R.S.A.: 95/5429

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microID, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELOQ® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

## WORLDWIDE SALES AND SERVICE

#### AMERICAS

**Corporate Office** 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: 480-792-7627 Web Address: http://www.microchip.com

**Rocky Mountain** 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7966 Fax: 480-792-7456

#### Atlanta

500 Sugar Mill Road, Suite 200B Atlanta, GA 30350 Tel: 770-640-0034 Fax: 770-640-0307

Boston

2 Lan Drive, Suite 120 Westford, MA 01886 Tel: 978-692-3848 Fax: 978-692-3821

Chicago

333 Pierce Road, Suite 180 Itasca, IL 60143 Tel: 630-285-0071 Fax: 630-285-0075

Dallas

4570 Westgrove Drive, Suite 160 Addison, TX 75001 Tel: 972-818-7423 Fax: 972-818-2924

#### Detroit

Tri-Atria Office Building 32255 Northwestern Highway, Suite 190 Farmington Hills, MI 48334 Tel: 248-538-2250 Fax: 248-538-2260 Kokomo

2767 S. Albright Road

Kokomo, Indiana 46902 Tel: 765-864-8360 Fax: 765-864-8387 Los Angeles

18201 Von Karman, Suite 1090 Irvine, CA 92612

Tel: 949-263-1888 Fax: 949-263-1338

New York 150 Motor Parkway, Suite 202 Hauppauge, NY 11788 Tel: 631-273-5305 Fax: 631-273-5335

San Jose

Microchip Technology Inc. 2107 North First Street, Suite 590 San Jose, CA 95131 Tel: 408-436-7950 Fax: 408-436-7955

Toronto

6285 Northam Drive, Suite 108 Mississauga, Ontario L4V 1X5, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Australia

Microchip Technology Australia Pty Ltd Suite 22, 41 Rawson Street Epping 2121, NSW Australia Tel: 61-2-9868-6733 Fax: 61-2-9868-6755 China - Beijing Microchip Technology Consulting (Shanghai) Co., Ltd., Beijing Liaison Office Unit 915 Bei Hai Wan Tai Bldg. No. 6 Chaoyangmen Beidajie Beijing, 100027, No. China Tel: 86-10-85282100 Fax: 86-10-85282104 China - Chengdu Microchip Technology Consulting (Shanghai) Co., Ltd., Chengdu Liaison Office Rm. 2401, 24th Floor, Ming Xing Financial Tower No. 88 TIDU Street

Chengdu 610016, China Tel: 86-28-6766200 Fax: 86-28-6766599 China - Fuzhou

Microchip Technology Consulting (Shanghai) Co., Ltd., Fuzhou Liaison Office Unit 28F, World Trade Plaza No. 71 Wusi Road Fuzhou 350001, China Tel: 86-591-7503506 Fax: 86-591-7503521 China - Shanghai

Microchip Technology Consulting (Shanghai) Co., Ltd. Room 701, Bldg. B Far East International Plaza No. 317 Xian Xia Road Shanghai, 200051 Tel: 86-21-6275-5700 Fax: 86-21-6275-5060

#### China - Shenzhen

Microchip Technology Consulting (Shanghai) Co., Ltd., Shenzhen Liaison Office Rm. 1315, 13/F, Shenzhen Kerry Centre, Renminnan Lu Shenzhen 518001, China Tel: 86-755-2350361 Fax: 86-755-2366086 Hong Kong Microchip Technology Hongkong Ltd. Unit 901-6, Tower 2, Metroplaza

223 Hing Fong Road Kwai Fong, N.T., Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

#### India

Microchip Technology Inc. India Liaison Office **Divyasree Chambers** 1 Floor, Wing A (A3/A4) No. 11, O'Shaugnessey Road Bangalore, 560 025, India Tel: 91-80-2290061 Fax: 91-80-2290062

#### Japan

Microchip Technology Japan K.K. Benex S-1 6F 3-18-20, Shinyokohama Kohoku-Ku, Yokohama-shi Kanagawa, 222-0033, Japan Tel: 81-45-471-6166 Fax: 81-45-471-6122 Korea Microchip Technology Korea 168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku Seoul, Korea 135-882 Tel: 82-2-554-7200 Fax: 82-2-558-5934 Singapore Microchip Technology Singapore Pte Ltd. 200 Middle Road #07-02 Prime Centre Singapore, 188980 Tel: 65-334-8870 Fax: 65-334-8850 Taiwan Microchip Technology Taiwan 11F-3, No. 207 Tung Hua North Road Taipei, 105, Taiwan Tel: 886-2-2717-7175 Fax: 886-2-2545-0139

#### EUROPE

Denmark

Microchip Technology Nordic ApS Regus Business Centre Lautrup hoj 1-3 Ballerup DK-2750 Denmark Tel: 45 4420 9895 Fax: 45 4420 9910 France Microchip Technology SARL Parc d'Activite du Moulin de Massy 43 Rue du Saule Trapu Batiment A - ler Etage 91300 Massy, France Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79 Germany Microchip Technology GmbH

Gustav-Heinemann Ring 125 D-81739 Munich, Germany Tel: 49-89-627-144 0 Fax: 49-89-627-144-44 Italy

Microchip Technology SRL Centro Direzionale Colleoni Palazzo Taurus 1 V. Le Colleoni 1 20041 Agrate Brianza Milan, Italy Tel: 39-039-65791-1 Fax: 39-039-6899883

#### United Kingdom

Arizona Microchip Technology Ltd. 505 Eskdale Road Winnersh Triangle Wokingham Berkshire, England RG41 5TU Tel: 44 118 921 5869 Fax: 44-118 921-5820

01/18/02