# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note: Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

# 3874 Group

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

#### **DESCRIPTION**

The 3874 group is the 8-bit microcomputer based on the 740 family core technology.

The 3874 group includes data link layer communication control circuit, A-D converters, D-A converter, automatic data transfer serial I/O, UART, and watchdog timer etc.

The various microcomputers in the 3874 group include variations of internal memory size and packaging. For details, refer to the section on part numbering.

For details on availability of microcomputers in the 3874 group, refer to the section on group expansion.

### **FEATURES**

| ● Basic machine-language instructions                              |

|--------------------------------------------------------------------|

| (at 6.4 MHz oscillation frequency, in double-speed mode)           |

|                                                                    |

| ■Memory size                                                       |

| ROM 16 K to 60 K bytes                                             |

| RAM 1024 to 2048 bytes                                             |

| ● Programmable input/output ports                                  |

| ●Input port1                                                       |

| ●Interrupts                                                        |

| (Interrupt source discrimination register exists, included key in- |

| put interrupt)                                                     |

| ●Timer 1, timer 2, timer 3                                         |

| ●Timer X, timer Y                                                  |

| ● Serial I/O1                                                        |

|----------------------------------------------------------------------|

| fer function available)                                              |

| ●A-D converter 8-bit X 8 channels                                    |

| ●D-A converter                                                       |

| Data link layer communication control circuit                        |

| Clock generating circuit                                             |

| (connect to external ceramic resonator or quartz-crystal oscillator) |

| ●Watchdog timer                                                      |

| • Power source voltage                                               |

| ● Power dissipation                                                  |

| In double-speed mode90 mW                                            |

| In high-speed mode60 mW                                              |

| (at 32 kHz oscillation frequency, at 5 V power source voltage)       |

| In low-speed mode                                                    |

| (at 32 kHz oscillation frequency, at 3 V power source voltage)       |

| ●Operating temperature range40 to 85°C                               |

| (Extended operating temperature version and automotive version)      |

# **APPLICATION**

Automotive comfort control for audio system, air conditioning etc., automotive body electronics control, household appliances, and other consumer applications, etc.

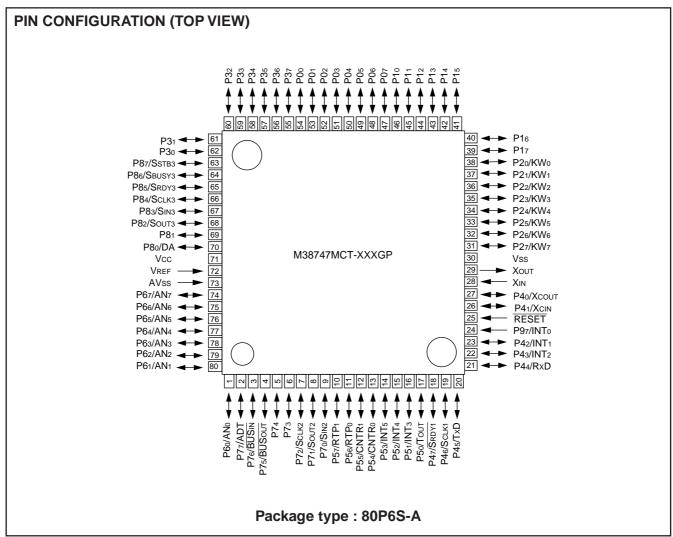

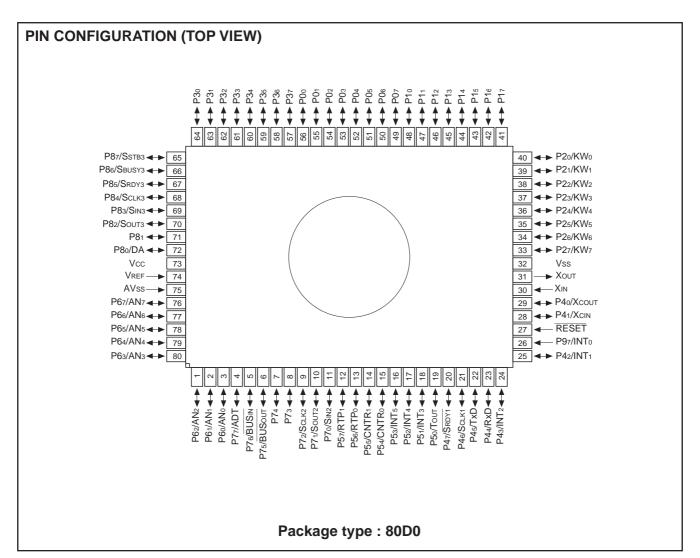

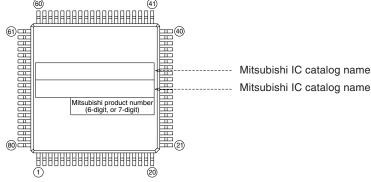

#### **PIN CONFIGURATION**

Fig. 1 M38747MCT-XXXGP pin configuration

Fig. 2 M38749EFFS pin configuration

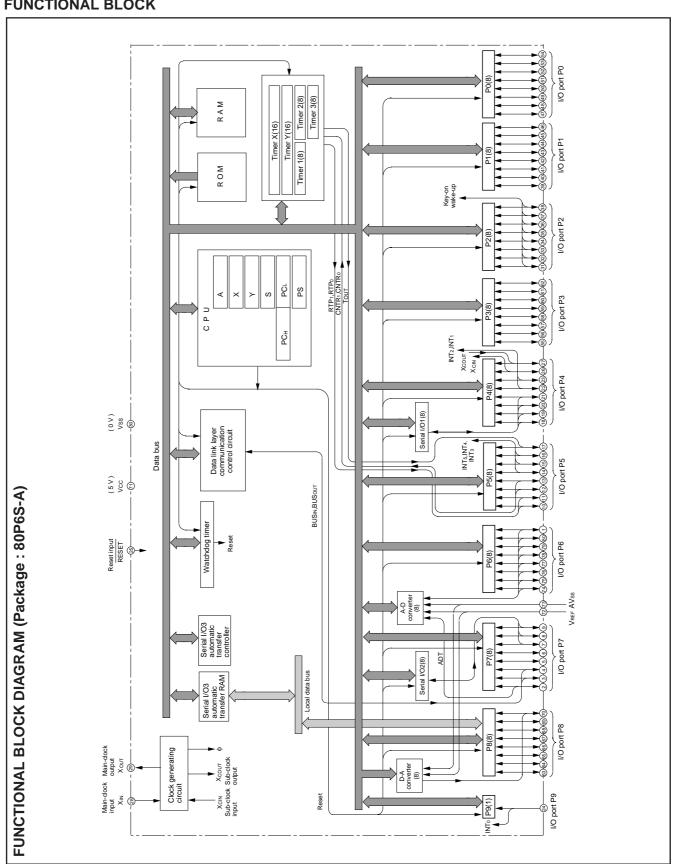

# **FUNCTIONAL BLOCK**

Fig. 3 Functional block diagram

# **PIN DESCRIPTION**

Table 1 Pin description (1)

|                                                          | description (1)         |                                                                                        |                                                                                                  |  |  |  |  |

|----------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin                                                      | Name                    | Functions                                                                              | Function except a port function                                                                  |  |  |  |  |

| Vcc, Vss                                                 | Power source input      | •Apply voltage of 3.0 V – 5.5 V to Vcc, and 0 V to Vss.                                |                                                                                                  |  |  |  |  |

| VREF                                                     | Reference voltage input | •Reference voltage input pin for A-D and D-A converters                                | •Reference voltage input pin for A-D and D-A converters.                                         |  |  |  |  |

| ۸) (                                                     | Analog power source     | •Analog power source input pin for A-D and D-A converte                                | ers.                                                                                             |  |  |  |  |

| AVss                                                     | input                   | •Connect to Vss.                                                                       |                                                                                                  |  |  |  |  |

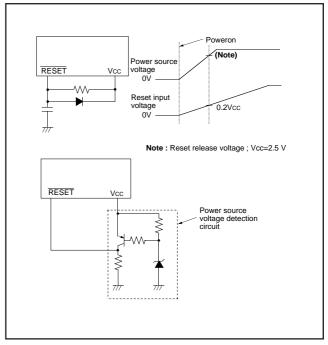

| RESET                                                    | Reset input             | •Reset input pin for active "L."                                                       |                                                                                                  |  |  |  |  |

|                                                          |                         | •Input and output pins for the clock generating circuit.                               |                                                                                                  |  |  |  |  |

| XIN                                                      | Clock input             | Connect a ceramic resonator or quartz-crystal oscillator<br>the oscillation frequency. | between the XIN and XOUT pins to set                                                             |  |  |  |  |

| Xout                                                     | Clock output            | •When an external clock is used, connect the clock sou pin open.                       | rce to the XIN pin and leave the XOUT                                                            |  |  |  |  |

|                                                          |                         | •Feedback resistor is built in between XIN pin and XOUT                                | pin.                                                                                             |  |  |  |  |

| P00-P07                                                  | I/O port P0             | •8-bit CMOS I/O port.                                                                  |                                                                                                  |  |  |  |  |

| P10-P17                                                  | I/O port P1             | •I/O direction register allows each pin to be individually p                           | •I/O direction register allows each pin to be individually programmed as either input or output. |  |  |  |  |

| P20-P27                                                  | I/O port P2             | •CMOS compatible input level.                                                          |                                                                                                  |  |  |  |  |

| P30-P37                                                  | I/O port P3             | •CMOS 3-state output structure.                                                        |                                                                                                  |  |  |  |  |

| P40/XCOUT,<br>P41/XCIN                                   |                         | •8-bit I/O port with the same function as port P0. •CMOS compatible input level.       | •Sub-clock generating circuit I/O pins connect a resonator. (This circuit cannot be operated by  |  |  |  |  |

|                                                          |                         | •CMOS 3-state output structure.                                                        | an external clock.)                                                                              |  |  |  |  |

| P42/INT1,<br>P43/INT2                                    | I/O port P4             |                                                                                        | •Interrupt input pins                                                                            |  |  |  |  |

| P44/RXD,<br>P45/TXD,<br>P46/ <u>SCLK1</u> ,<br>P47/SRDY1 |                         |                                                                                        | •Serial I/O1 function pins                                                                       |  |  |  |  |

| P50/Tout                                                 |                         | •8-bit I/O port with the same function as port P0.                                     | •Timer 2 output pin                                                                              |  |  |  |  |

| P51/INT3-<br>P53/INT5                                    |                         | CMOS compatible input level.     CMOS 3-state output structure.                        | •Interrupt input pins                                                                            |  |  |  |  |

| P54/CNTR0,<br>P55/CNTR1                                  | I/O port P5             | omos o state output structure.                                                         | •Timer X, timer Y function pins                                                                  |  |  |  |  |

| P56/RTP0,<br>P57/RTP1                                    |                         |                                                                                        | •Real time port function pins                                                                    |  |  |  |  |

# **3874 Group**

# SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

# Table 2 Pin description (2)

| Pin                                                | Name          | Functions                                          |                                            |

|----------------------------------------------------|---------------|----------------------------------------------------|--------------------------------------------|

|                                                    |               |                                                    | Function except a port function            |

|                                                    |               | •8-bit I/O port with the same function as port P0. | •A-D converter input pins                  |

| P60/AN0-<br>P67/AN7                                | I/O port P6   | •CMOS compatible input level.                      |                                            |

| 1 O//AIN/                                          |               | CMOS 3-state output structure.                     |                                            |

| P70/SIN2,                                          |               | •8-bit I/O port with the same function as port P0. | •Serial I/O2 function pins                 |

| P71/SOUT2,                                         |               | CMOS compatible input level.                       |                                            |

| P72/SCLK2                                          |               | CMOS 3-state output structure.                     |                                            |

| P73, P74                                           | I/O port P7   |                                                    |                                            |

| P75/BUSOUT,                                        |               |                                                    | Data link layer communication control pins |

| P77/ADT                                            |               |                                                    | •A-D trigger input pin                     |

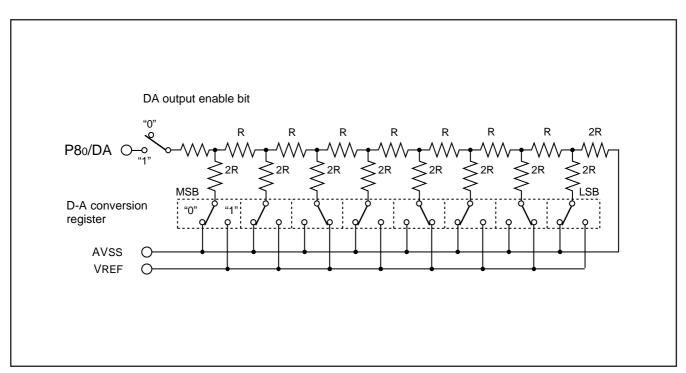

| P80/DA                                             |               | •8-bit I/O port with the same function as port P0. | •D-A converter output pin                  |

| P81                                                |               |                                                    |                                            |

| P82/SOUT3,<br>P83/SIN3,<br>P84/SCLK3,<br>P85/SRDY3 | I/O port P8   |                                                    | •Serial I/O3 function pins                 |

| P86/SBUSY3,<br>P87/SSTB3                           |               |                                                    |                                            |

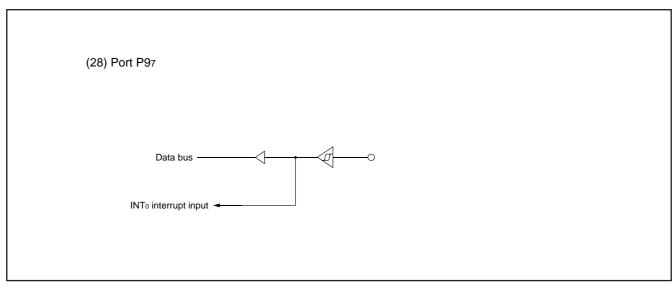

| P97/INTo                                           | Input port P9 | •1-bit input port.                                 | •Interrupt input pin                       |

| F9//IINIO                                          | input port F3 | •CMOS compatible input level.                      |                                            |

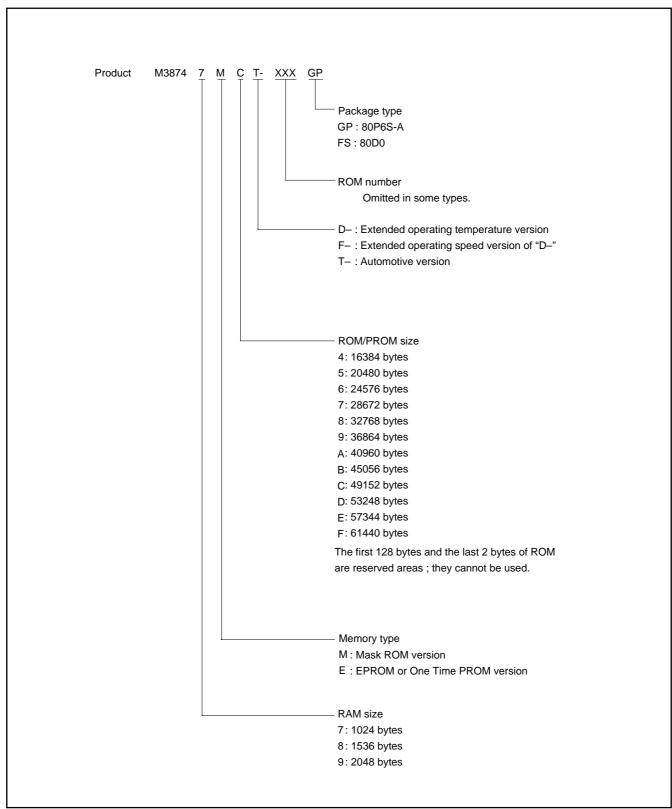

# **PART NUMBERING**

Fig. 4 Part numbering

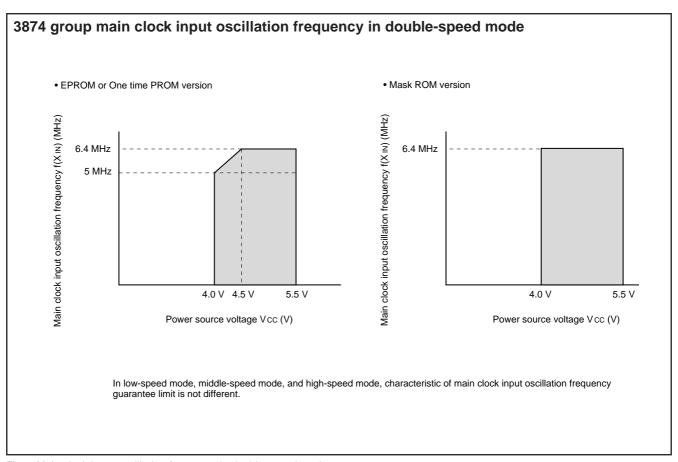

Fig. 5 Main clock input oscillation frequency in double-speed mode

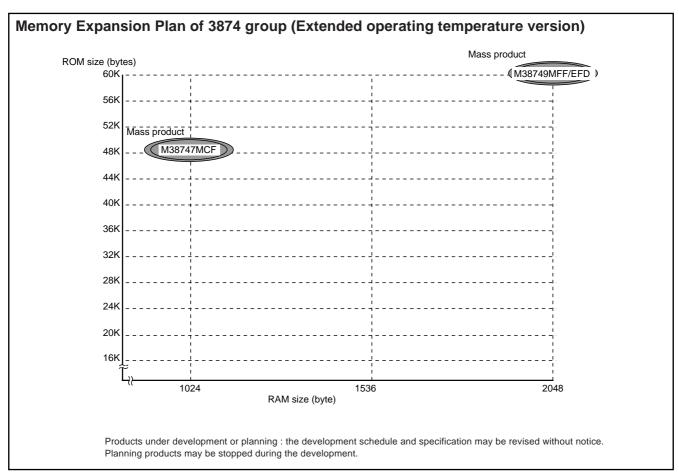

# **GROUP EXPANSION (Extended operating temperature version)**

The 3874 group (extended operating temperature version) is designed for automotive comfort and amusement control such as audio, air-conditioner etc., household appliances, and other consumer applications.

Mitsubishi plans to expand the 3874 group (extended operating temperature version) as follows:

# **Memory Type**

Support for mask ROM, One Time PROM, and EPROM versions

# **Memory Size**

### **Packages**

Fig. 6 Memory expansion plan (Extended operating temperature version)

Currently planning products are listed below.

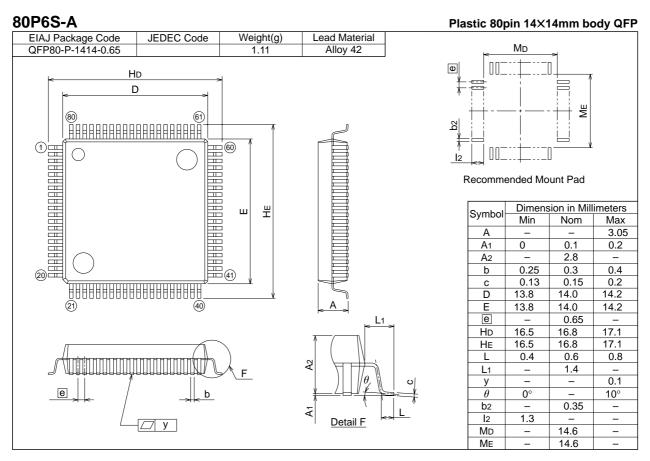

Table 3 Support products

As of March 1998

| Product name | (P) ROM size (bytes)<br>ROM size for User in ( ) | RAM size (bytes) | Package | Remarks                                                                       |

|--------------|--------------------------------------------------|------------------|---------|-------------------------------------------------------------------------------|

| M38749EFDGP  |                                                  |                  | 80P6S-A | One Time PROM version (blank)                                                 |

| M38749EFFS   | 61440<br>(61310)                                 | 2048             | 80D0    | EPROM version (for software development, operating temperature = -20 to 85°C) |

| M38749MFF    |                                                  |                  | 80P6S-A | W 1 50M                                                                       |

| M38747MCF    | 49152<br>(49022)                                 | 1024             | 00F0S-A | Mask ROM version                                                              |

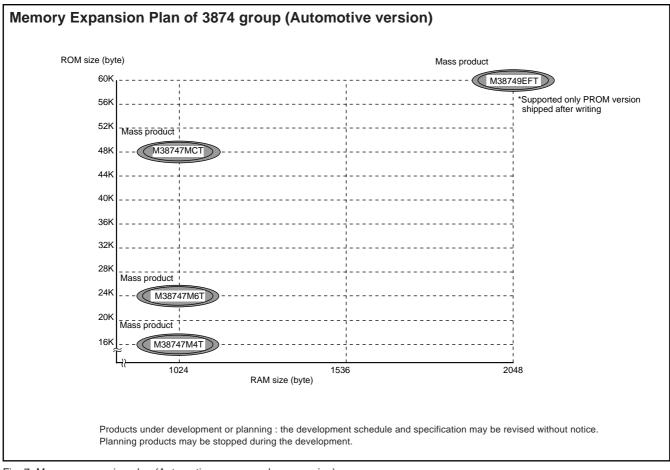

# **GROUP EXPANSION (Automotive version)**

The 3874 group (automotive version) is designed for automotive body electronics control.

Mitsubishi plans to expand the 3874 group (automotive version) as follows:

| ROM/PROM size | 16 K to 60 K bytes               |

|---------------|----------------------------------|

| RAM size      | 1024 to 2048 bytes               |

| Packages      |                                  |

| 80P6S-A       | 0.65 mm-nitch plastic molded OFP |

# **Memory Type**

Support for mask ROM and One Time PROM versions

# **Memory Size**

Fig. 7 Memory expansion plan (Automotive correspondence version)

Currently planning products are listed below.

**Table 4 Support products**

As of March 1998

| Product name | (P) ROM size (bytes)<br>ROM size for User in ( ) | RAM size (bytes) | Package | Remarks               |

|--------------|--------------------------------------------------|------------------|---------|-----------------------|

| M38749EFT    | 61440 (61310)                                    | 2048             |         | One Time PROM version |

| M38747MCT    | 49152 (49022)                                    |                  | 00000 4 |                       |

| M38747M6T    | 24576 (24446)                                    | 1048             | 80P6S-A | Mask ROM version      |

| M38747M4T    | 16384 (16254)                                    |                  |         |                       |

# FUNCTIONAL DESCRIPTION CENTRAL PROCESSING UNIT (CPU)

The 3874 group uses the standard 740 Family instruction set. Refer to the table of 740 Family addressing modes and machine instructions or the 740 Family Software Manual for details on the instruction set.

Machine-resident 740 Family instructions are as follows:

The FST and SLW instructions cannot be used.

The STP, WIT, MUL, and DIV instructions can be used.

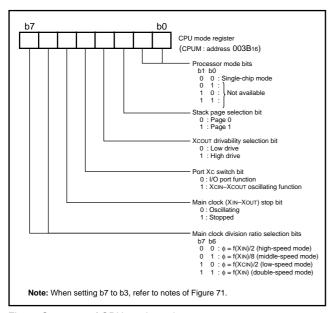

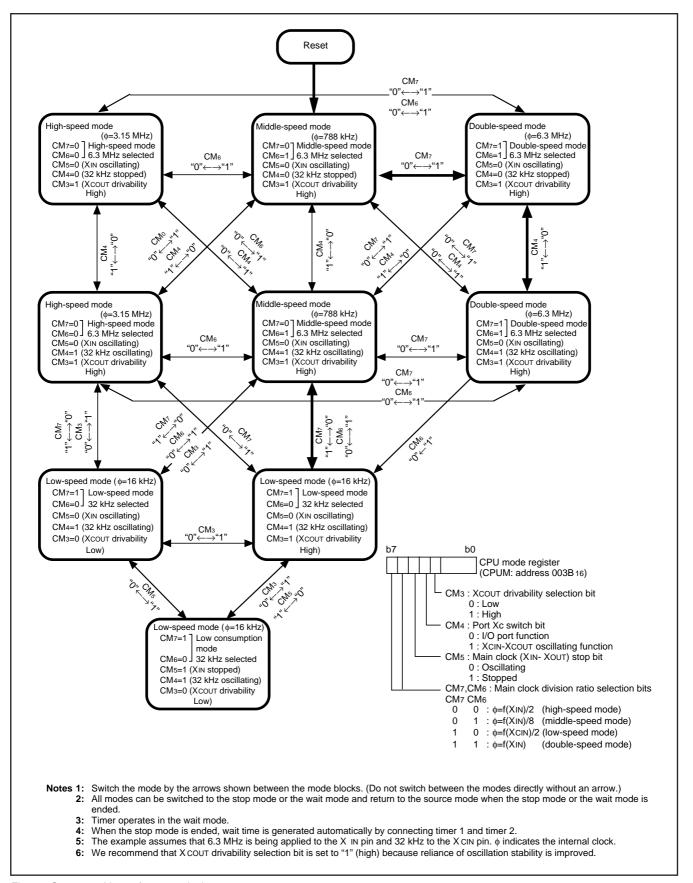

# [CPU Mode Register (CPUM)] 003B16

The CPU mode register contains the stack page selection bit and the internal system clock selection bit etc.

The CPU mode register is allocated at address 003B16.

Fig. 8 Structure of CPU mode register

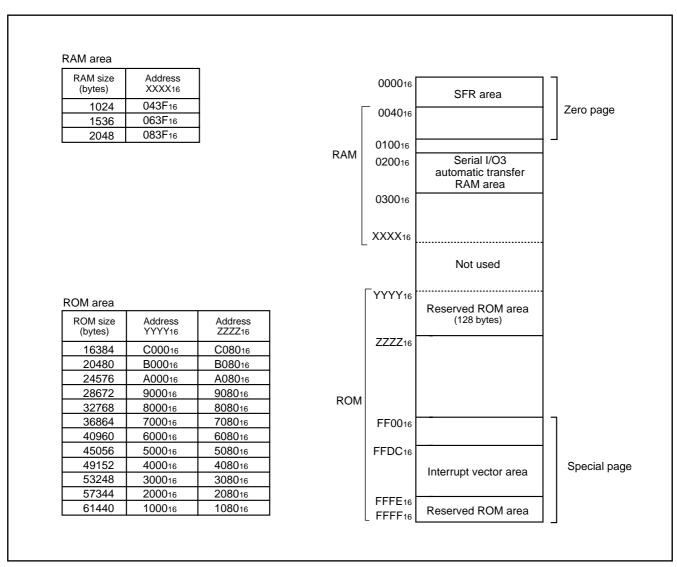

# MEMORY Special Function Register (SFR) Area

The Special Function Register area in the zero page contains control registers such as I/O ports and timers.

#### **RAM**

RAM is used for data storage and for stack area of subroutine calls and interrupts.

### **ROM**

The first 128 bytes and the last 2 bytes of ROM are reserved for device testing and the rest is user area for storing programs.

### **Interrupt Vector Area**

The interrupt vector area contains reset and interrupt vectors.

# Zero Page

Access to this area with only 2 bytes is possible in the zero page addressing mode.

# **Special Page**

Access to this area with only 2 bytes is possible in the special page addressing mode.

Fig. 9 Memory map diagram

| 000016             | Port P0 (P0)                                         | 002016             | Timer X (low-order) (TXL)                                    |

|--------------------|------------------------------------------------------|--------------------|--------------------------------------------------------------|

| 000116             | Port P0 direction register (P0D)                     | 002116             | Timer X (high-order) (TXH)                                   |

| 000216             | Port P1 (P1)                                         | 002216             | Timer Y (low-order) (TYL)                                    |

| 000316             | Port P1 direction register (P1D)                     | 002316             | Timer Y (high-order) (TYH)                                   |

| 000416             | Port P2 (P2)                                         | 002416             | Timer 1 (T1)                                                 |

| 000516             | Port P2 direction register (P2D)                     | 002516             | Timer 2 (T2)                                                 |

| 000616             | Port P3 (P3)                                         | 002616             | Timer 3 (T3)                                                 |

| 000716             | Port P3 direction register (P3D)                     | 002716             | Timer X mode register (TXM)                                  |

| 000816             | Port P4 (P4)                                         | 002816             | Timer Y mode register (TYM)                                  |

| 000916             | Port P4 direction register (P4D)                     | 002916             | Timer 123 mode register (T123M)                              |

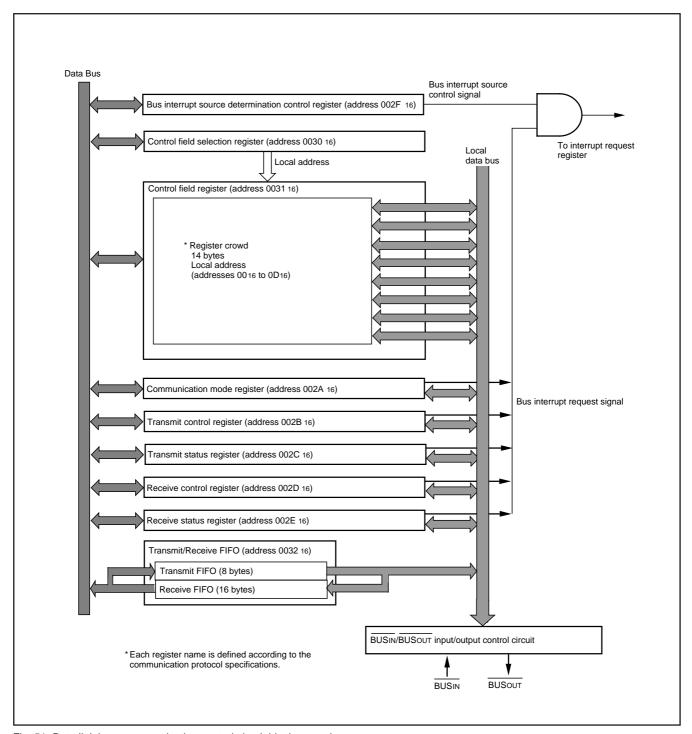

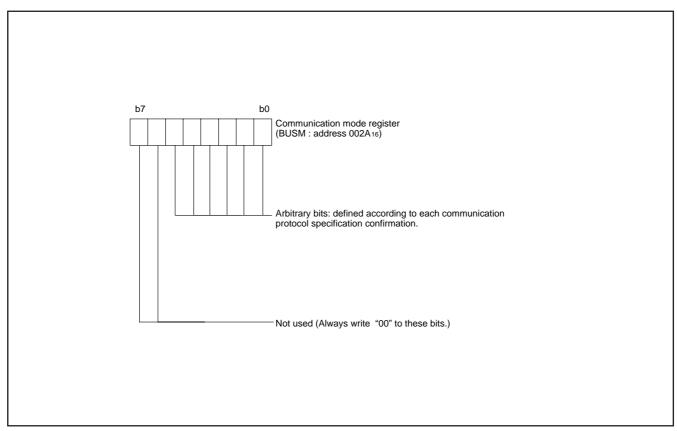

| 000A16             | Port P5 (P5)                                         | 002A16             | Communication mode register (BUSM)                           |

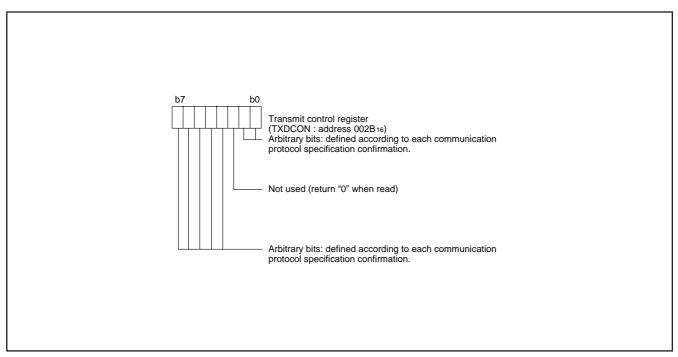

| 000B16             | Port P5 direction register (P5D)                     | 002B <sub>16</sub> | Transmit control register (TXDCON)                           |

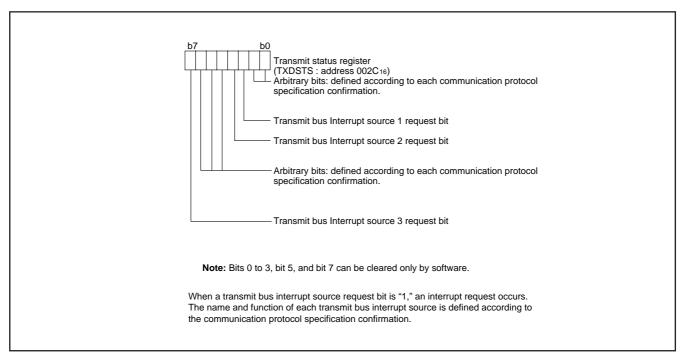

| 000C16             | Port P6 (P6)                                         | 002C16             | Transmit status register (TXDSTS)                            |

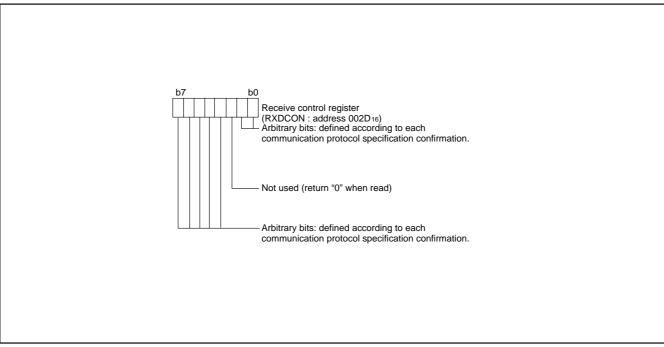

| 000D16             | Port P6 direction register (P6D)                     | 002D16             | Receive control register (RXDCON)                            |

| 000E16             | Port P7 (P7)                                         | 002E16             | Receive status register (RXDSTS)                             |

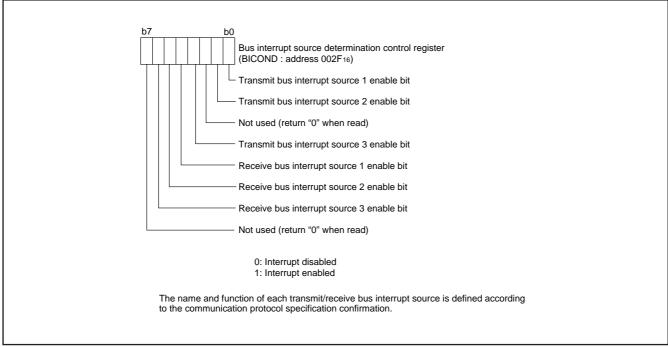

| 000F16             | Port P7 direction register (P7D)                     | 002F16             | Bus interrupt source discrimination control register (BICOND |

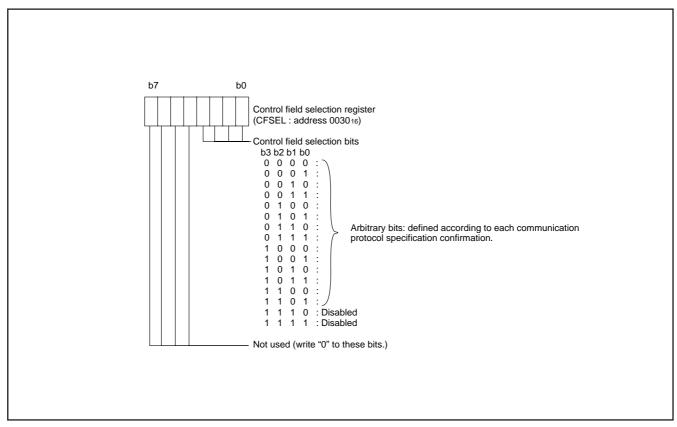

| 001016             | Port P8 (P8)                                         | 003016             | Control field selection register (CFSEL)                     |

| 001116             | Port P8 direction register (P8D)                     | 003116             | Control field register (CF)                                  |

| 001216             | Port P9 (P9)                                         | 003216             | Transmit/Receive FIFO (TRFIFO)                               |

| 001316             | Serial I/O3 register/Transfer counter (SIO3)         | 003316             | PULL UP register (PULLU)                                     |

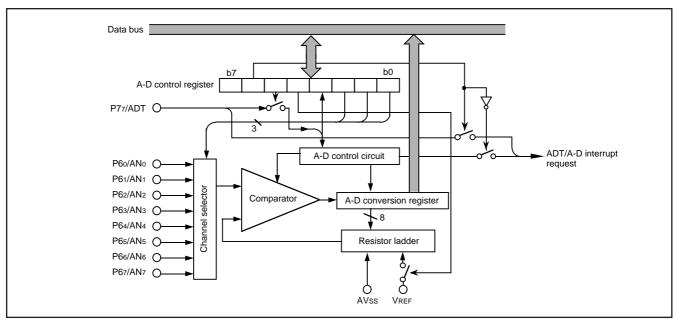

| 001416             | Serial I/O3 control register 1 (SIO3CON1)            | 003416             | A-D control register (ADCON)                                 |

| 001516             | Serial I/O3 control register 2 (SIO3CON2)            | 003516             | A-D/D-A conversion register (AD)                             |

| 001616             | Serial I/O3 control register 3 (SIO3CON3)            | 003616             | Interrupt source discrimination register 2 (IREQD2)          |

| 001716             | Serial I/O3 automatic transfer data pointer (SIO3DP) | 003716             | Interrupt source discrimination control register 2 (ICOND2)  |

| 001816             | Transmit/Receive buffer register (TB/RB)             | 003816             | Interrupt source discrimination register 1 (IREQD1)          |

| 001916             | Serial I/O1 status register (SIO1STS)                | 003916             | Interrupt source discrimination control register 1 (ICOND1)  |

| 001A16             | Serial I/O1 control register (SIO1CON)               | 003A16             | Interrupt edge selection register (INTEDGE)                  |

| 001B <sub>16</sub> | UART control register (UARTCON)                      | 003B <sub>16</sub> | CPU mode register (CPUM)                                     |

| 001C <sub>16</sub> | Baud rate generator (BRG)                            | 003C16             | Interrupt request register 1 (IREQ1)                         |

| 001D16             | Serial I/O2 control register (SIO2CON)               | 003D16             | Interrupt request register 2 (IREQ2)                         |

| 001E <sub>16</sub> | Watchdog timer control register (WDTCON)             | 003E16             | Interrupt control register 1 (ICON1)                         |

| 001F16             | Serial I/O2 register (SIO2)                          | 003F <sub>16</sub> | Interrupt control register 2 (ICON2)                         |

Fig. 10 Memory map of special function register (SFR)

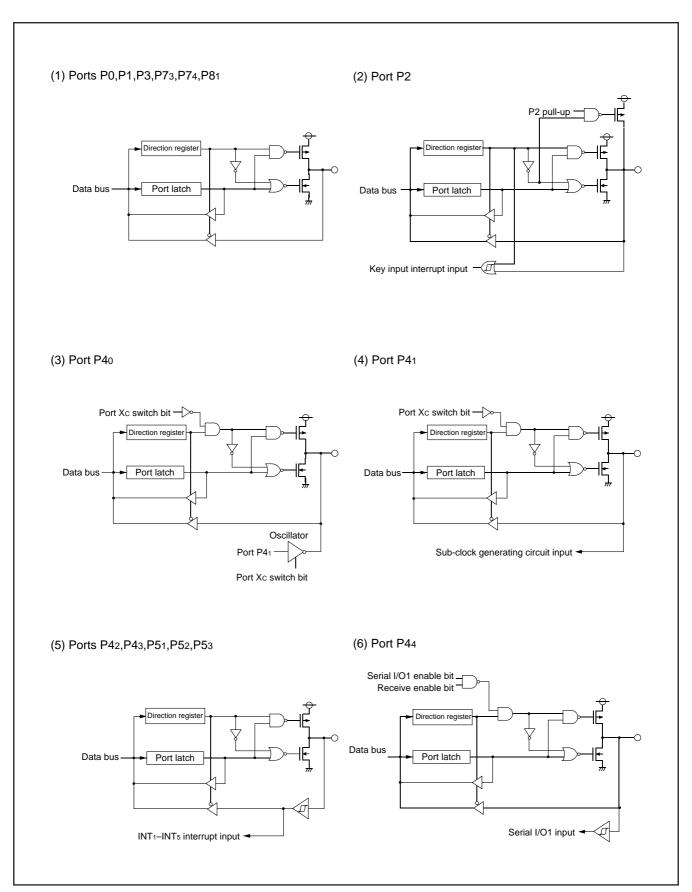

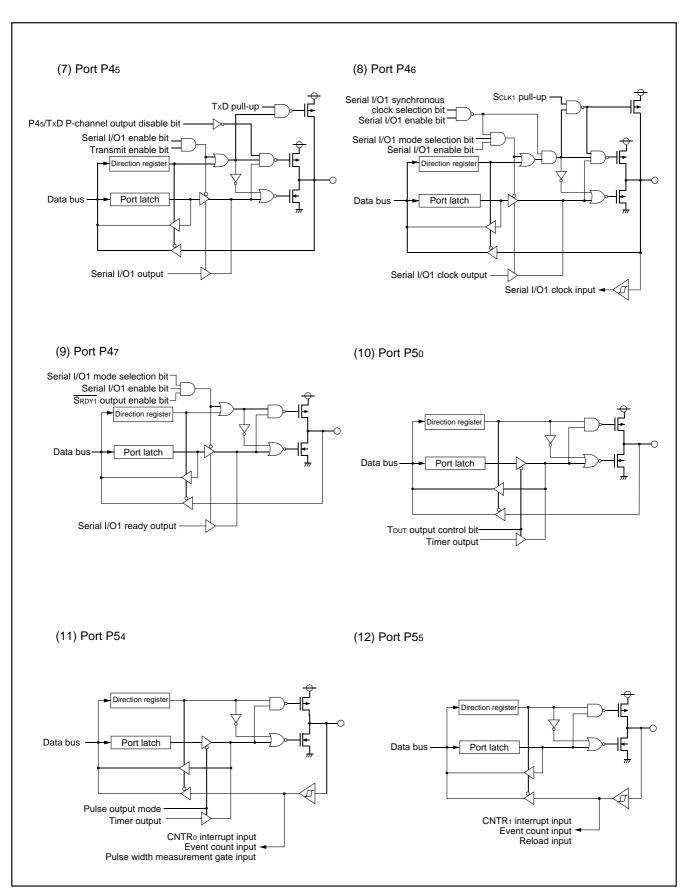

#### I/O PORTS

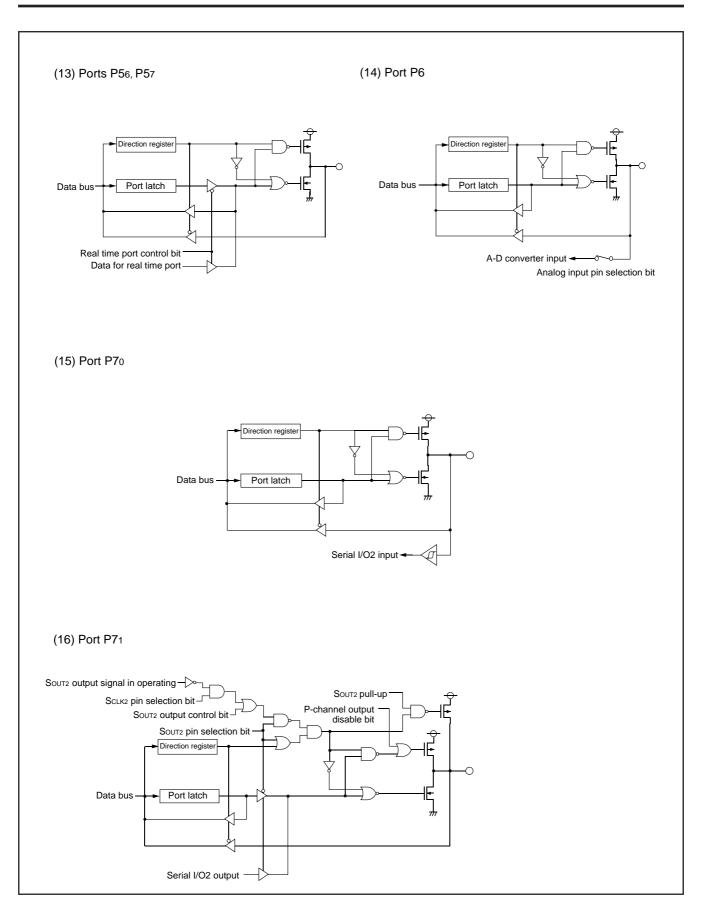

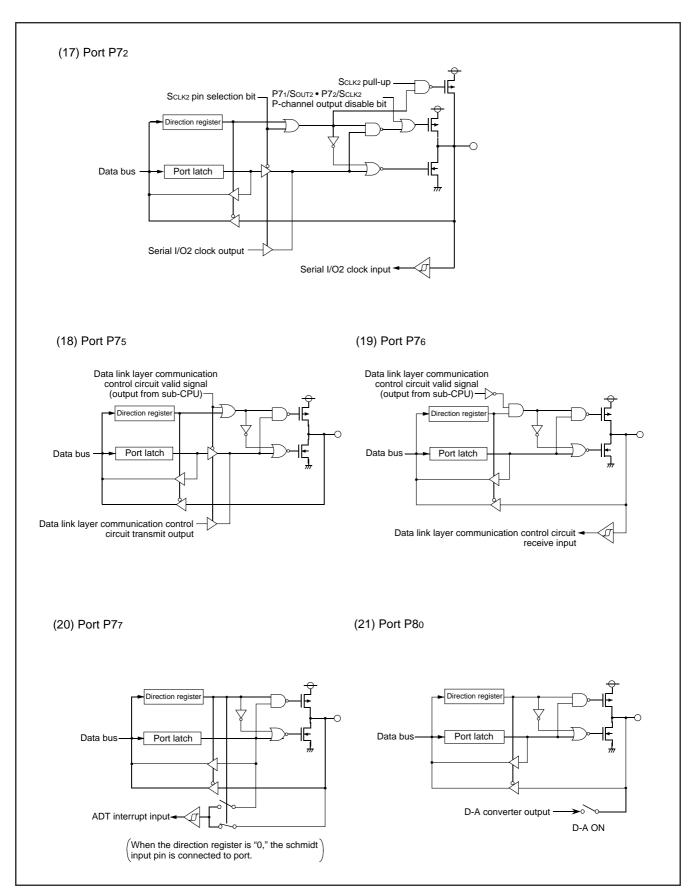

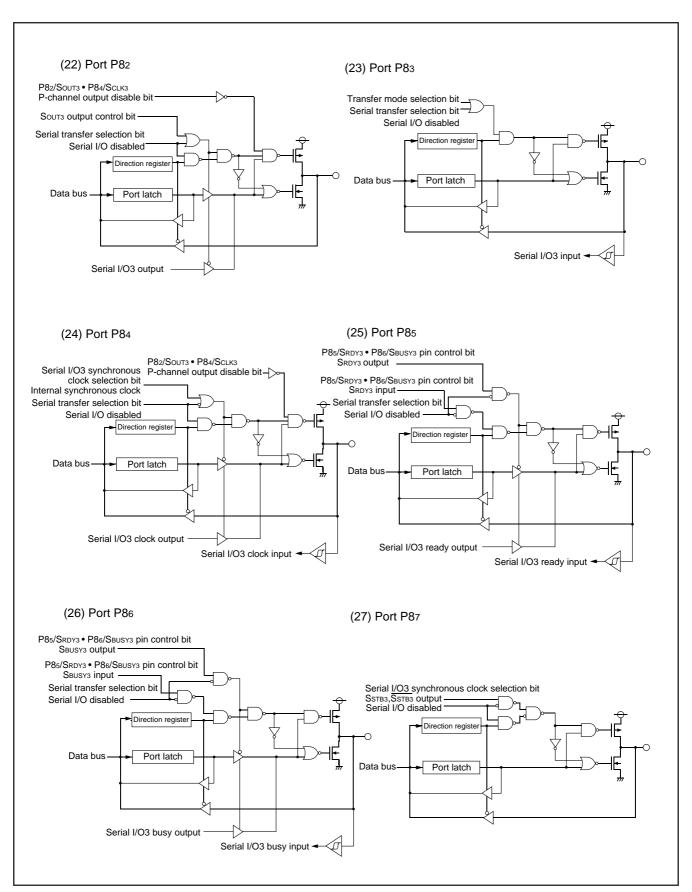

The I/O ports P0–P8 have direction registers which determine the input/output direction of each individual pin. Each bit in a direction register corresponds to one pin, and each pin can be set to be input port or output port.

When "0" is written to the bit corresponding to a pin, that pin becomes an input pin. When "1" is written to that bit, that pin becomes an output pin.

If data is read from a pin which is set to output, the value of the port output latch is read, not the value of the pin itself. Pins set to input are floating. If a pin set to input is written to, only the port output latch is written to and the pin remains floating.

Table 5 I/O port function (1)

| Pin                                | Name    | Input/Output                  | I/O Structure                                     | Non-Port Function                                   | Related SFRs                             | Ref.No.                            |     |

|------------------------------------|---------|-------------------------------|---------------------------------------------------|-----------------------------------------------------|------------------------------------------|------------------------------------|-----|

| P00-P07                            | Port P0 | Input/output, individual bits | •CMOS compatible input level •CMOS 3-state output |                                                     |                                          | (1)                                |     |

| P10-P17                            | Port P1 | Input/output, individual bits | •CMOS compatible input level •CMOS 3-state output |                                                     |                                          |                                    |     |

| P20-P27                            | Port P2 | Input/output, individual bits | •CMOS compatible input level •CMOS 3-state output | •Key input (key-on<br>wake-up) interrupt in-<br>put | •PULL UP register                        | (2)                                |     |

| P30-P37                            | Port P3 | Input/output, individual bits | •CMOS compatible input level •CMOS 3-state output |                                                     | •CPU mode register                       | (1)                                |     |

| P40/XCOUT                          | Port P4 | Input/output,                 | •CMOS compatible                                  | •Sub-clock generating                               | •CPU mode register                       | (3)                                |     |

| P41/XCIN                           |         | individual bits               | input level                                       | circuit I/O                                         |                                          | (4)                                |     |

| P42/INT1,<br>P43/INT2              |         |                               |                                                   | •CMOS 3-state output                                | •External interrupt input                | •Interrupt edge selection register | (5) |

| P44/RxD                            |         |                               |                                                   | •Serial I/O1 function I/O                           | •Serial I/O1 control reg-                | (6)                                |     |

| P45/TxD                            |         |                               |                                                   |                                                     | ister •Serial I/O1 status regis-         | (7)                                |     |

| P46/SCLK1                          |         |                               |                                                   |                                                     | ter                                      | (8)                                |     |

| P47/SRDY1                          |         |                               |                                                   |                                                     | •UART control register •PULL UP register | (9)                                |     |

| Р50/Тоит                           | Port P5 | Input/output, individual bits | •CMOS compatible input level                      | •Timer 2 output                                     | •Timer 123 mode register                 | (10)                               |     |

| P51/INT3,<br>P52/INT4,<br>P53/INT5 |         | •CMOS 3-state output          | •External interrupt input                         | •Interrupt edge selection register                  | (5)                                      |                                    |     |

| P54/CNTR0                          |         |                               |                                                   | •Timer X function I/O                               | •Timer X mode register                   | (11)                               |     |

| P55/CNTR1                          |         |                               |                                                   | •Timer Y function I/O                               | •Timer Y mode register                   | (12)                               |     |

| P56/RTP0                           |         |                               |                                                   | •Real time port function output                     | •Timer X mode register                   | (13)                               |     |

| P57/RTP1                           |         |                               |                                                   | •Real time port function output                     | •Timer Y mode register                   |                                    |     |

| P60/AN0-<br>P67/AN7                | Port P6 | Input/output, individual bits | •CMOS compatible input level •CMOS 3-state output | •A-D converter input                                | •A-D control register                    | (14)                               |     |

Table 6 I/O port function (2)

| Pin        | Name                                  | Input/Output    | I/O Function                                      | Non-Port Function         | Related SFRs                                                                     | Ref.No. |

|------------|---------------------------------------|-----------------|---------------------------------------------------|---------------------------|----------------------------------------------------------------------------------|---------|

| P70/SIN2   | Port P7 Input/output, individual bits |                 | •CMOS compatible input level •CMOS 3-state output | •Serial I/O2 function I/O | •Serial I/O2 control reg-                                                        | (15)    |

| P71/SOUT2  |                                       | individual bits |                                                   |                           | ister •PULL UP register                                                          | (16)    |

| P72/SCLK2  |                                       |                 |                                                   |                           |                                                                                  | (17)    |

| P73,P74    |                                       |                 |                                                   |                           |                                                                                  | (1)     |

| P75/BUSout |                                       |                 |                                                   | •Data link layer commu-   | •Communication mode                                                              | (18)    |

| P76/BUSIN  |                                       |                 |                                                   | nication control I/O      | register                                                                         | (19)    |

|            |                                       |                 |                                                   |                           | <ul> <li>Transmit control register</li> </ul>                                    |         |

|            |                                       |                 |                                                   |                           | •Transmit status register                                                        |         |

|            |                                       |                 |                                                   |                           | •Receive control regiser                                                         |         |

|            |                                       |                 |                                                   |                           | •Receive status register                                                         |         |

|            |                                       |                 |                                                   |                           | <ul> <li>Bus interrupt source<br/>discrimination control<br/>register</li> </ul> |         |

|            |                                       |                 |                                                   |                           | •Control field selection register                                                |         |

|            |                                       |                 |                                                   |                           | <ul> <li>Control field register</li> </ul>                                       |         |

|            |                                       |                 |                                                   |                           | •Transmit/Receive FIFO                                                           |         |

| P77/ADT    |                                       |                 |                                                   | •A-D trigger input        | •A-D control register                                                            | (20)    |

| P80/DA     | Port P8                               | Input/output,   | •CMOS compatible in-                              | •D-A function output      | •A-D control register                                                            | (21)    |

| P81        |                                       | individual bits | put level •CMOS 3-state output                    |                           |                                                                                  | (1)     |

| P82/Sout3  |                                       |                 | -Civios s-state output                            | •Serial I/O3 function I/O | •Serial I/O3 register/                                                           | (22)    |

| P83/SIN3   |                                       |                 |                                                   |                           | Transfer counter                                                                 | (23)    |

| P84/SCLK3  |                                       |                 |                                                   |                           | <ul> <li>Serial I/O3 control register 1</li> </ul>                               | (24)    |

| P85/SRDY3  |                                       |                 |                                                   |                           | •Serial I/O3 control reg-                                                        | (25)    |

| P86/SBUSY3 |                                       |                 |                                                   |                           | ister 2                                                                          | (26)    |

| P87/SSTB3  |                                       |                 |                                                   |                           | <ul> <li>Serial I/O3 control register 3</li> </ul>                               | (27)    |

|            |                                       |                 |                                                   |                           | Serial I/O3 automatic<br>transfer data pointer                                   |         |

| P97/INT0   | Port P9                               | Input           | •CMOS compatible input level                      | •External interrupt input | •Interrupt edge selection register                                               | (28)    |

$\textbf{Note:} \ \mathsf{Make} \ \mathsf{sure} \ \mathsf{that} \ \mathsf{the} \ \mathsf{input} \ \mathsf{level} \ \mathsf{at} \ \mathsf{each} \ \mathsf{pin} \ \mathsf{is} \ \mathsf{either} \ \mathsf{0} \ \mathsf{V} \ \mathsf{or} \ \mathsf{Vcc} \ \mathsf{during} \ \mathsf{execution} \ \mathsf{of} \ \mathsf{the} \ \mathsf{STP} \ \mathsf{instruction}.$

When an input level is at an intermediate potential, a current will flow from Vcc to Vss through the input-stage gate.

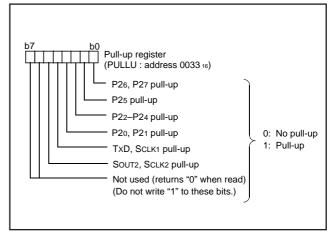

# **Pull-up Control**

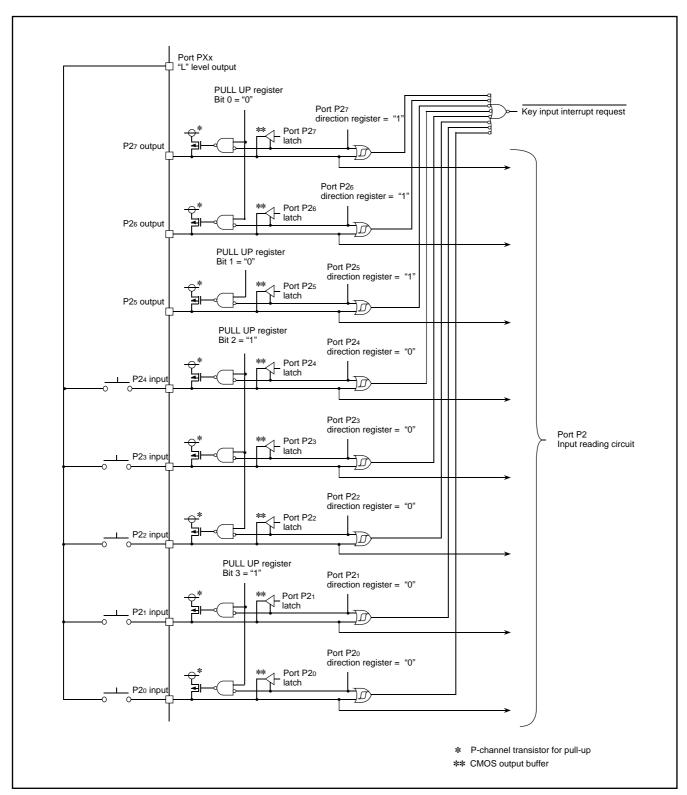

P20–P26, TxD, SCLK1, SOUT2, and SCLK2 can perform pull-up control by setting "1" to the pull-up register (address 003316).

P20–P27's pull-up is valid in the input mode, and TxD, SCLK1, SOUT2, and SCLK2S' pull-up is valid in the output mode.

Fig.11 Structure of Pull-up Register

Fig. 12 Port block diagram (1)

Fig. 13 Port block diagram (2)

Fig. 14 Port block diagram (3)

Fig. 15 Port block diagram (4)

Fig. 16 Port block diagram (5)

Fig. 17 Port block diagram (6)

#### **INTERRUPTS**

Interrupts occur by 27 sources: 10 external, 16 internal, and 1 software

#### Interrupt Control

Each interrupt is controlled by an interrupt request bit, an interrupt enable bit, and the interrupt disable flag except for the software interrupt set by the BRK instruction. An interrupt occurs if the corresponding interrupt request and enable bits are "1" and the interrupt disable flag is "0".

Interrupt enable bits can be set or cleared by software.

Interrupt request bits can be cleared by software, but cannot be set by software.

The BRK instruction cannot be disabled with any flag or bit. The I (interrupt disable) flag disables all interrupts except the BRK instruction interrupt.

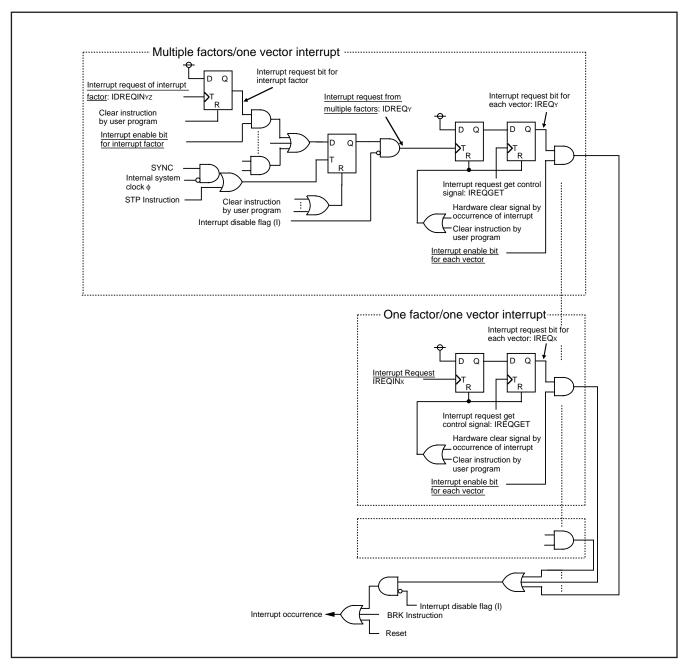

The interrupt control circuit consists of two types of interrupts: "one factor/one vector interrupt" and "multiple factors/one vector interrupt". The configuration is shown in Figure 18.

### **Interrupt Operation**

When an interrupt occurs, the following operations are automatically performed:

- 1. The contents of the program counter and the processor status register are pushed onto the stack.

- 2. The interrupt disable flag is set and the corresponding interrupt request bit for each vector is cleared. (The corresponding interrupt request bit for each interrupt factor is not cleared.)

- 3. The interrupt jump destination address of interrupt which has the highest priority is loaded to the program counter.

## Interrupt Factor Determination

The interrupt request bit for each vector of "multiple factors/one vector interrupt" is set to "1" when the interrupt disable flag (I) is "0" and one of the factor interrupt enable bits is "1" and the corresponding factor interrupt request bit changes from "0" to "1". At this time, if the vector interrupt enable bit is "1", the interrupt occurs. (Note that the interrupt request bit for each vector and the factor interrupt request bit are both edge sense.)

When 2 or more interrupt requests of interrupt factors assigned to one interrupt vector are generated at the same time, confirm the interrupt request bits for each interrupt factor assigned to the vector, and process according to the priority.

If the interrupt request bit for the interrupt factor is "1" and the interrupt enable bits for interrupt factor and each vector are both "1"; for example, when an interrupt of another interrupt factor assigned to the same vector occurs while an interrupt processing routine is executed, the interrupt occurs again after returning. Clear the interrupt request bits which are not necessary or which have been already processed before executing the interrupt flag clear (CLI) or interrupt processing routine return (RTI) instruction.

The interrupt request bits for each interrupt factor are not cleared by hardware after an interrupt vector address branching. Clear these bits by software in the interrupt processing routine. Use the LDM, STA, etc. instructions to do it. Do not use the read-modify-write instruction; for example, the CLB.

#### ■ Notes

When the active edge of an external interrupt (INT0–INT5, CNTR0, CNTR1) is set, the corresponding interrupt request bit may also be set. Therefore, take following sequence:

- (1) Disable the external interrupt which is selected.

- (2) Change the active edge in interrupt edge selection register (in case of CNTR0: Timer X mode register; in case of CNTR1: Timer Y mode register).

- (3) Clear the set interrupt request bit to "0".

- (4) Enable the external interrupt which is selected.

Table 7 Interrupt vector addresses and priority

| Interrupt Sources               | Priority | Vector Addres | · ,                | Interrupt Request                                                                    | Remarks                                                                                                  |

|---------------------------------|----------|---------------|--------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|                                 | ,        | High          | Low                | Generating Conditions                                                                |                                                                                                          |

| Reset (Note 2)                  | 1        | FFFD16        | FFFC16             | At reset                                                                             | Non-maskable                                                                                             |

| INT <sub>0</sub>                | 2        | FFFB16        | FFFA16             | At detection of either rising or falling edge of INTo input                          | External interrupt (active edge selectable)                                                              |

| INT <sub>1</sub>                | 3        | FFF916        | FFF816             | At detection of either rising or falling edge of INT1 input                          | External interrupt (active edge selectable)                                                              |

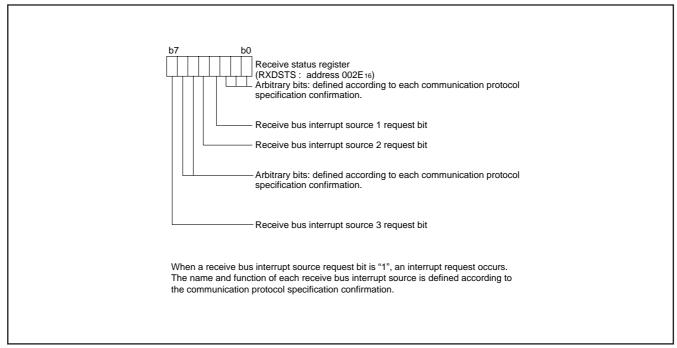

| Receive bus interrupt source 1  | 4        | FFF716        | FFF616             | When receive bus interrupt source 1 request bit becomes "1" from "0"                 | The condition which the receive bus interrupt factor request bit becomes "1" is defined according        |

| Receive bus interrupt source 2  |          |               |                    | When receive bus interrupt source 2 request bit becomes "1" from "0"                 | to each communication protocol specification confirmation.                                               |

| Receive bus interrupt source 3  |          |               |                    | When receive bus interrupt source 3 request bit becomes "1" from "0"                 |                                                                                                          |

| Transmit bus interrupt source 1 | 5        | FFF516        | FFF416             | When transmit bus interrupt source 1 request bit becomes "1" from "0"                | The condition which the transmit<br>bus interrupt factor request bit<br>becomes "1" is defined according |

| Transmit bus interrupt source 2 |          |               |                    | When transmit bus interrupt source 2 request bit becomes "1" from "0"                | to each communication protocol specification confirmation.                                               |

| Transmit bus interrupt source 3 |          |               |                    | When transmit bus interrupt source 3 request bit becomes "1" from "0"                |                                                                                                          |

| Timer X                         | 6        | FFF316        | FFF216             | At timer X underflow                                                                 |                                                                                                          |

| Timer Y                         | 7        | FFF116        | FFF016             | At timer Y underflow                                                                 |                                                                                                          |

| Timer 2                         | 8        | FFEF16        | FFEE16             | At timer 2 underflow                                                                 |                                                                                                          |

| Timer 3                         | 9        | FFED16        | FFEC16             | At timer 3 underflow                                                                 |                                                                                                          |

| INT2                            | 10       | FFEB16        | FFEA <sub>16</sub> | At detection of either rising or falling edge of INT2 input                          | External interrupt (active edge selectable)                                                              |

| Serial I/O3 interrupt           | 11       | FFE916        | FFE816             | At completion of serial I/O3 data transmission/reception                             | Valid only when serial I/O3 is selected                                                                  |

| CNTR <sub>0</sub>               |          |               |                    | At detection of either rising or falling edge of CNTR0 input                         | External interrupt (active edge selectable)                                                              |

| CNTR <sub>1</sub>               | 12       | FFE716        | FFE616             | At detection of either rising or falling edge of CNTR1 input                         | External interrupt (active edge selectable)                                                              |

| Timer 1                         | 13       | FFE516        | FFE416             | At timer 1 underflow                                                                 |                                                                                                          |

| INT3                            | 14       | FFE316        | FFE216             | At detection of either rising or falling edge of INT3 input                          | External interrupt (active edge selectable)                                                              |

| INT4                            |          |               |                    | At detection of either rising or falling edge of INT4 input                          | External interrupt (active edge selectable)                                                              |

| INT5                            |          |               |                    | At detection of either rising or falling edge of INTs input                          | External interrupt (active edge selectable)                                                              |

| ADT                             | 15       | FFE116        | FFE016             | At falling of ADT pin input                                                          | Valid only when ADT interrupt is selected External interrupt (falling valid)                             |

| A-D converter                   |          |               |                    | At completion of A-D converter                                                       | Valid only when A-D converter interrupt is selected                                                      |

| Serial I/O2 interrupt           |          |               |                    | At completion of serial I/O2 data transmission/reception                             | Valid only when serial I/O2 is selected                                                                  |

| Key input (key-<br>on wake-up)  | 16       | FFDF16        | FFDE16             | At falling of port P20 to P25 (at input) input logical level AND                     | External interrupt (falling valid)                                                                       |

| Serial I/O1 receive             |          |               |                    | At completion of serial I/O1 data reception                                          | Valid only when serial I/O1 is selected                                                                  |

| Serial I/O1<br>transmit         |          |               |                    | At completion of serial I/O1 transmission shift or when transmission buffer is empty | Valid only when serial I/O1 is selected                                                                  |

| BRK instruction                 | 17       | FFDD16        | FFDC16             | At BRK instruction execution                                                         | Non-maskable software interrupt                                                                          |

Notes 1: Vector addresses contain interrupt jump destination addresses.

<sup>3:</sup> Either ADT interrupt or A-D converter interrupt can be used. Both ADT interrupt and A-D converter interrupt cannot be used.

<sup>2:</sup> Reset function in the same way as an interrupt with the highest priority.

Fig.18 Interrupt control diagram

# **Timing to Interrupt Request Acceptance**

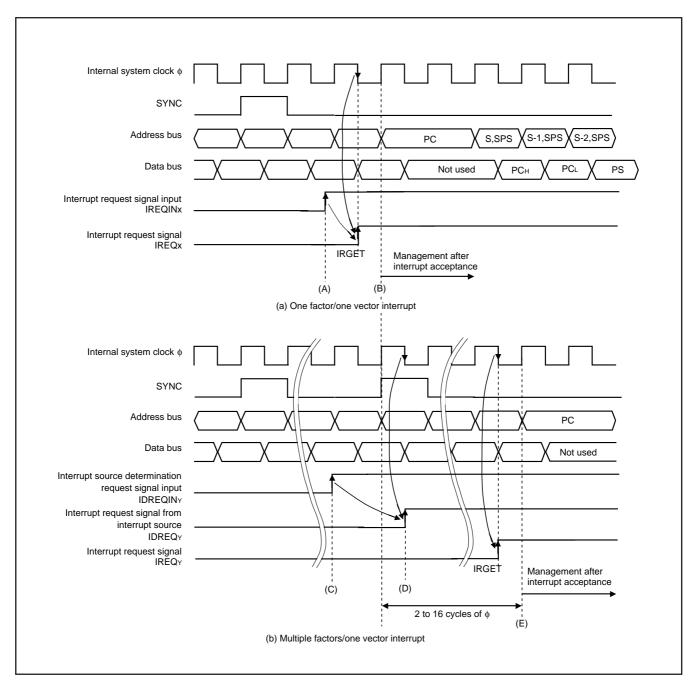

The cycle number of internal system clock required from occurrence to acceptance of an interrupt request depends on the type of interrupt: "multiple factors/one vector" or "one factor/one vector".

For "one factor/one vector interrupt", the CPU starts processing the management after interrupt acceptance at the next instruction execution timing (rising edge of SYNC signal) immediately after the interrupt request is generated. For "multiple factors/one vector interrupt", the CPU starts processing the management after interrupt acceptance at the second instruction execution timing (rising edge of SYNC signal) after the interrupt request for interrupt factor determination is generated. In other words, "multiple factors/one vector interrupt" required one instruction execution cycle number (2 to 16 cycles of internal system clock) more than that of "one factor/one vector interrupt" to begin the interrupt sequence.

Figure 18 shows the interrupt control diagram and Figure 19 shows the timing from occurrence to acceptance of interrupt request.

For "one factor/one vector interrupt", the interrupt request is generated at Timing (A) and the processing after acceptance begins at Timing (B). For "multiple factors/one vector interrupt", the interrupt factor determination request is generated at Timing (C), the interrupt request is generated at Timing (D), and the processing after acceptance begins at Timing (E).

Fig.19 Timing from occurrence to acceptance of interrupt

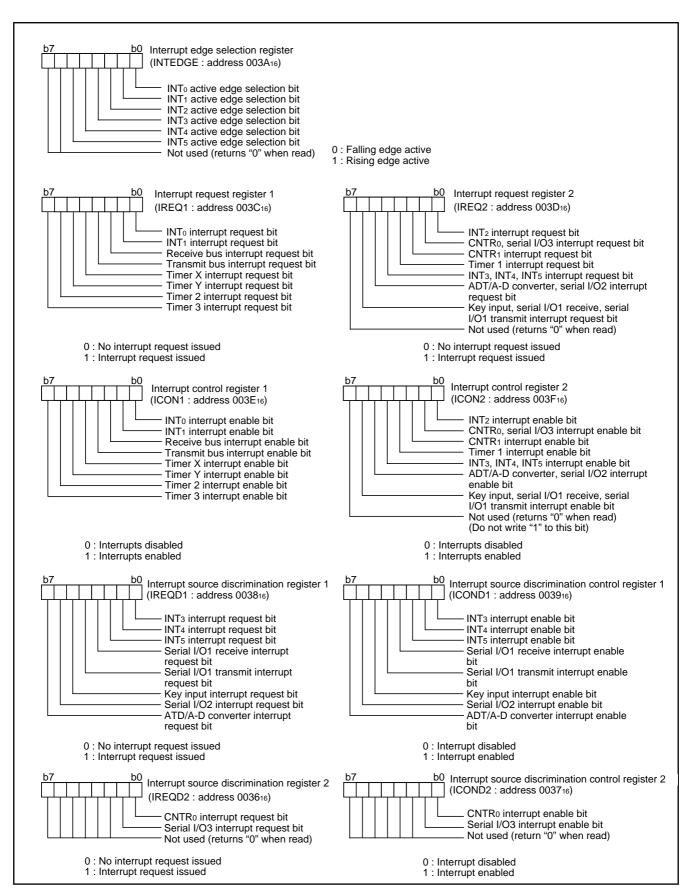

Fig. 20 Structure of interrupt-related registers

# **Key Input Interrupt**

A Key input interrupt request is generated by applying "L" level to any pin of port P2 that have been set to input mode. In other words, it is generated when AND of input level goes from "1" to "0".

An example of using a key input interrupt is shown in Figure 21, where an interrupt request is generated by pressing one of the keys consisted as an active-low key matrix which inputs to ports P20–P24.

Fig. 21 Connection example when using key input interrupt and port P2 block diagram

#### **TIMERS**

The 3874 group has five timers: timer X, timer Y, timer 1, timer 2, and timer 3. Timer X and timer Y are 16-bit timers, and timer 1, timer 2, and timer 3 are 8-bit timers.

All timers are down count timers. When the timer reaches "0016" or "000016", an underflow occurs at the next count pulse and the corresponding timer latch is reloaded into the timer and the count is continued. When a timer underflows, the interrupt request bit cor-

responding to that timer is set to "1".

Read and write operation on 16-bit timer must be performed for both high and low-order bytes. When reading a 16-bit timer, read the high-order byte first. When writing to a 16-bit timer, write the low-order byte first. The 16-bit timer cannot perform the correct operation when reading during the write operation, or when writing during the read operation.

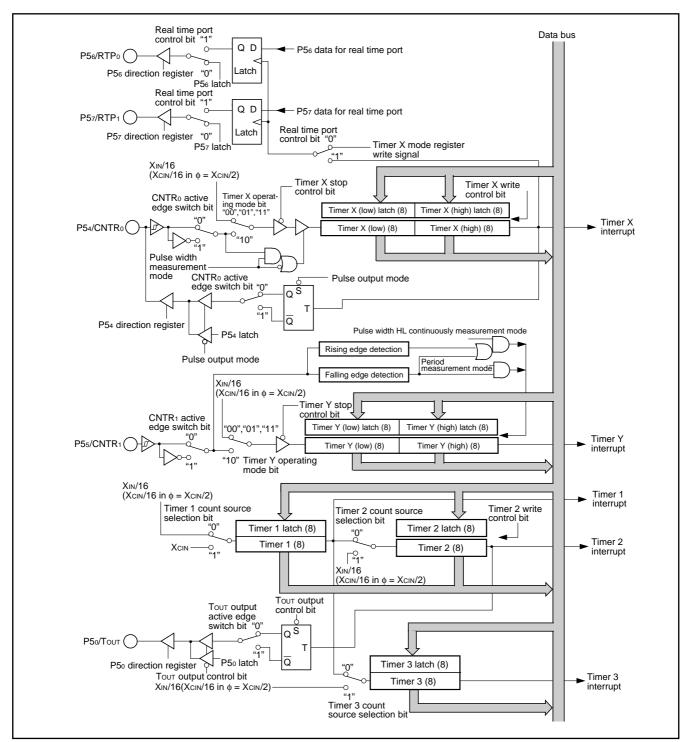

Fig. 22 Timer block diagram

#### Timer X

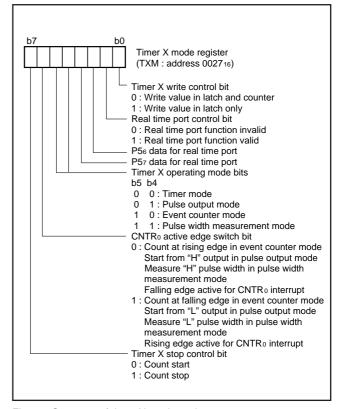

Timer X is a 16-bit timer that can be selected in one of four modes and can be controlled the timer X write and the real time port by setting the timer X mode register.

# (1) Timer Mode

The timer counts f(XIN)/16 (or f(XCIN)/16 in system clock  $\varphi$  = XCIN/ 2).

# (2) Pulse Output Mode

Each time the timer underflows, a signal output from the CNTR0 pin is inverted. Except for this, the operation in pulse output mode is the same as in timer mode. When using a timer in this mode, set the direction register of corresponding port to output mode.

# (3) Event Counter Mode

The timer counts signals input through the CNTRo pin.

Except for this, the operation in event counter mode is the same as in timer mode.

# (4) Pulse Width Measurement Mode

The count source is f(XIN)/16 (or f(XCIN)/16 in system clock  $\phi = XCIN/2$ . If CNTR0 active edge switch bit is "0", the timer counts while the input signal of CNTR0 pin is at "H". If it is "1", the timer counts while the input signal of CNTR0 pin is at "L".

#### ■ Notes

#### ● Timer X write control

If the timer X write control bit is "1", when the value is written in the address of timer X, the value is loaded only in the latch. The value in the latch is loaded in timer X after timer X underflows.

If the timer X write control bit is "0", when the value is written in the address of timer X, the value is loaded in the timer X and the latch at the same time.

When the value is to be written in latch only, if the value is written to the latch at timer X underflows, the value is consequently loaded in the timer X and the latch at the same time. Unexpected value may be set in the high-order counter when the writing in high-order latch and the underflow of timer X are performed at the same timing.

#### ● CNTRo interrupt active edge selection

CNTRo interrupt active edge depends on the CNTRo active edge switch bit.

#### • Real time port control

Data for the real time port are output from ports P56 and P57 each time the timer X underflows. (However, if the real time port control bit is changed from "0" to "1", data are output independent of the timer X operation.) When the data for the real time port is changed while the real time port function is valid, the changed data are output at the next underflow of timer X.

Before using this function, set the corresponding port direction registers to output mode.

Fig. 23 Structure of timer X mode register

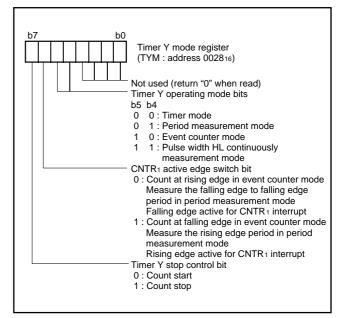

#### Timer Y

Timer Y is a 16-bit timer that can be selected in one of four modes.

# (1) Timer Mode

The timer counts f(XIN)/16 (or f(XCIN)/16 in system clock  $\phi = XCIN/2$ ).

# (2) Period Measurement Mode

CNTR1 interrupt request is generated at rising/falling edge of CNTR1 pin input signal. Simultaneously, the value in timer Y latch is reloaded in timer Y and timer Y continues counting down. Except for the above-mentioned, the operation in period measurement mode is the same as in timer mode.

The timer value just before the reloading at rising/falling of CNTR1 pin input signal is retained until the timer Y is read once after the reload

The rising/falling timing of CNTR1 pin input signal is found by CNTR1 interrupt.

# (3) Event Counter Mode

The timer counts signals input through the CNTR1 pin.

Except for this, the operation in event counter mode is the same as in timer mode.

# (4) Pulse Width HL Continuously Measurement Mode

CNTR1 interrupt request is generated at both rising and falling edges of CNTR1 pin input signal. Except for this, the operation in pulse width HL continuously measurement mode is the same as in period measurement mode.

#### ■ Note

## ● CNTR1 interrupt active edge selection

CNTR1 interrupt active edge depends on the CNTR1 active edge switch bit. However, in pulse width HL continuously measurement mode, CNTR1 interrupt request is generated at both rising and falling edges of CNTR1 pin input signal regardless of the setting of CNTR1 active edge switch bit.

Fig. 24 Structure of timer Y mode register

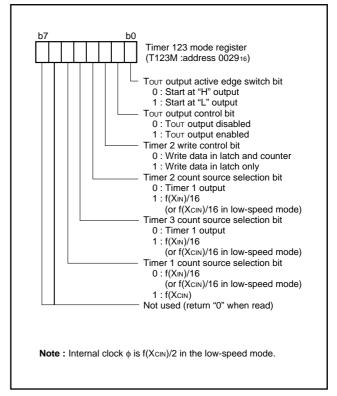

# Timer 1, Timer 2, Timer 3

Timer 1, timer 2, and timer 3 are 8-bit timers. The count source for each timer can be selected by timer 123 mode register.

#### ● Timer 2 write control

When the timer 2 write control bit is "1", and the value is written in the address of timer 2, the value is loaded only in the latch. The value in the latch is loaded in timer 2 after timer 2 underflows.

When the timer 2 write control bit is "0", and the value is written in the address of timer 2, the value is loaded in the timer 2 and the latch at the same time.

#### ● Timer 2 output control

An inversion signal from  $\mathsf{TOUT}$  pin is output each time timer 2 underflows.

In this case, set the port P50 direction register to the output mode.

#### ■ Note

#### • Timer 1 to timer 3

When the count source of timer 1 to 3 is changed, the timer counting value may be changed large because a thin pulse is generated in count input of timer. If timer 1 output is selected as the count source of timer 2 or timer 3, when timer 1 is written, the counting value of timer 2 or timer 3 may be changed large because a thin pulse is generated in timer 1 output.

Therefore, set the value of timer in the order of timer 1, timer 2 and timer 3 after the count source selection of timer 1 to 3.

Fig. 25 Structure of timer 123 mode register

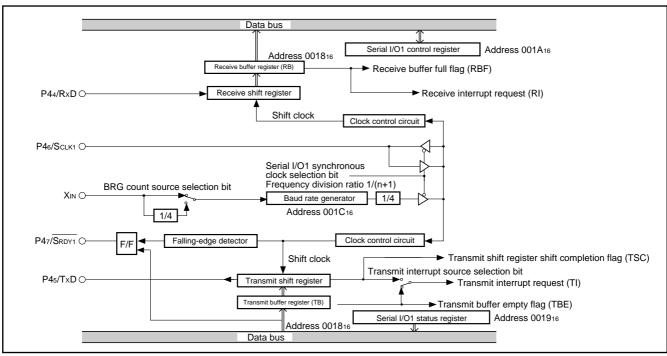

# SERIAL I/O Serial I/O1

Serial I/O can be used as either clock synchronous or asynchronous (UART) serial I/O. A dedicated timer (baud rate generator) is also provided for baud rate generation.

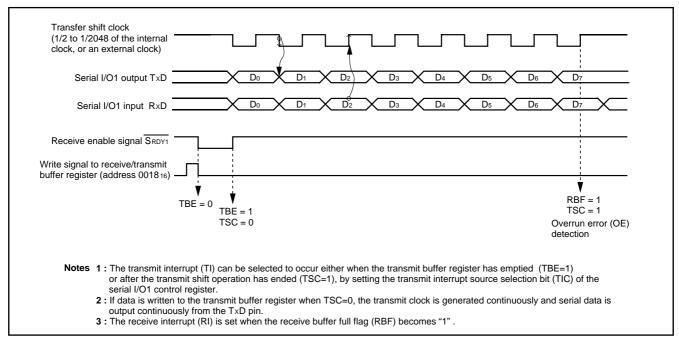

# (1) Clock Synchronous Serial I/O1 Mode

Clock synchronous serial I/O1 mode can be selected by setting the serial I/O1 mode selection bit (b6) of the serial I/O1 control register to "1".

For clock synchronous serial I/O1, the transmitter and the receiver must use the same clock. If an internal clock is used, transfer is started by a write signal to the transmit/receive buffer register (address 001816).

Fig. 26 Block diagram of clock synchronous serial I/O

Fig. 27 Operation of clock synchronous serial I/O1 function

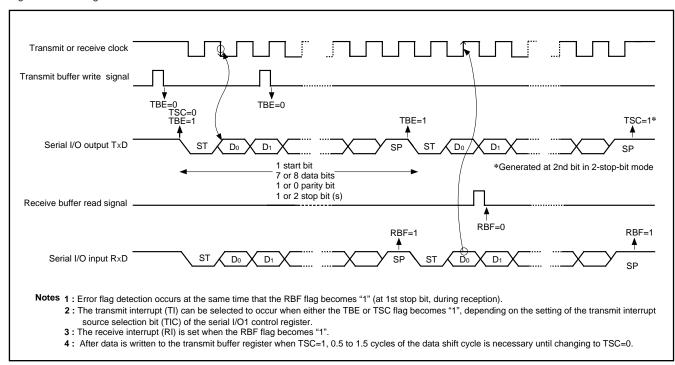

# (2) Asynchronous Serial I/O (UART) Mode

Clock asynchronous serial I/O mode (UART) can be selected by clearing the serial I/O1 mode selection bit (b6) of the serial I/O1 control register to "0".

Eight serial data transfer formats can be selected, and the transfer formats used by a transmitter and receiver must be identical.

The transmit and receive shift registers each have a buffer regis-

ter, but the two buffers have the same address in memory. Since the shift register cannot be written to or read from directly, transmit data is written to the transmit buffer, and receive data is read from the receive buffer.

The transmit buffer can also hold the next data to be transmitted, and the receive buffer register can hold a character while the next character is being received.

Fig. 28 Block diagram of UART serial I/O1

Fig. 29 Operation of UART serial I/O function

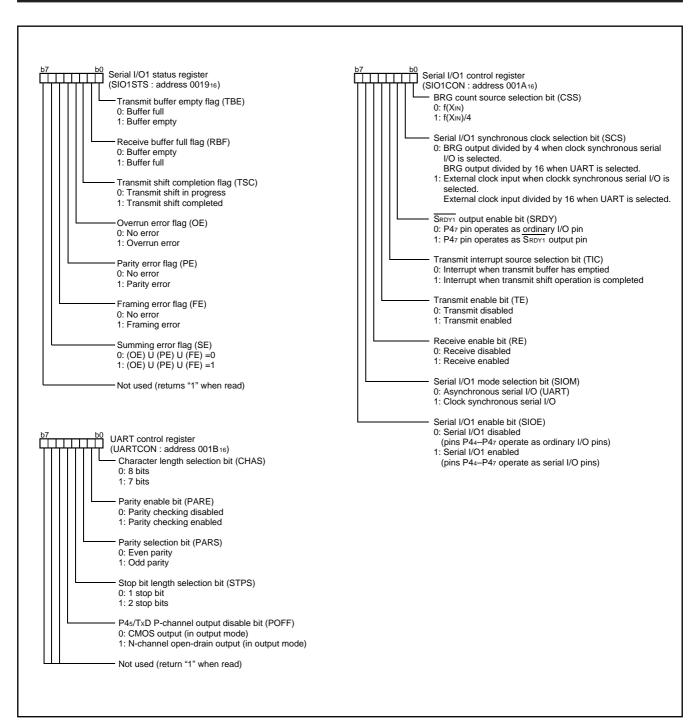

# [Transmit Buffer/Receive Buffer Register (TB/RB)] 001816

The transmit buffer register and the receive buffer register are located at the same address. The transmit buffer register is write-only and the receive buffer register is read-only. If a character bit length is 7 bits, the MSB of data stored in the receive buffer register is "0".

# [Serial I/O1 Status Register (SIO1STS)] 001916

The read-only serial I/O1 status register consists of seven flags (bits 0 to 6) which indicate the operating status of the serial I/O function and various errors.

Three of the flags (bits 4 to 6) are valid only in UART mode.

The receive buffer full flag (bit 1) is cleared to "0" when the receive buffer is read.

If there is an error, it is detected at the same time that data is transferred from the receive shift register to the receive buffer register, and the receive buffer full flag is set. A write to the serial I/O1 status register clears all the error flags OE, PE, FE, and SE (bit 3 to bit 6, respectively). Writing "0" to the serial I/O1 enable bit (bit 7) of the Serial I/O1 control register also clears all the status flags, including the error flags.

All bits of the serial I/O1 status register are initialized to "0" at reset, but if the transmit enable bit (bit 4) of the serial I/O1 control register has been set to "1", the transmit shift register shift completion flag (bit 2) and the transmit buffer empty flag (bit 0) become "1"

# [Serial I/O1 Control Register (SIO1CON)] 001A<sub>16</sub>

The serial I/O1 control register contains eight control bits for the serial I/O1 function.

# [UART Control Register (UARTCON)] 001B16

The UART control register consists of four control bits (bits 0 to 3) which are valid when asynchronous serial I/O is selected and set the data format of a data transfer. One bit in this register (bit 4) is always valid and sets the output structure of the P45/TxD pin and P46/SCLK1 pin.

# [Baud Rate Generator (BRG)] 001C16

The baud rate generator determines the baud rate for serial transfer.

The baud rate generator divides the frequency of the count source by 1/(n + 1), where n is the value written to the baud rate generator

Fig. 30 Structure of serial I/O1 control register

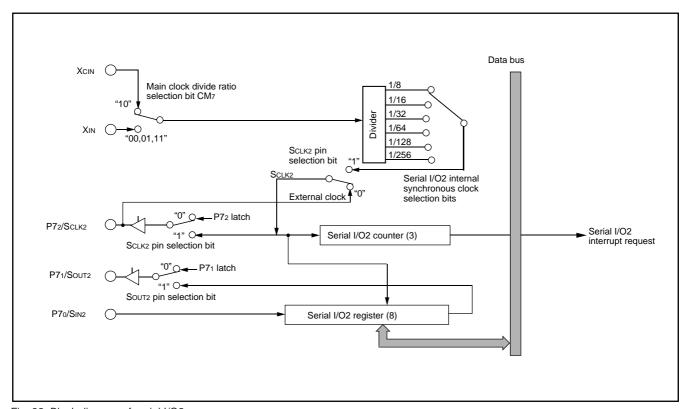

#### Serial I/O2

The Serial I/O2 function can be used only for clock synchronous serial I/O.

For clock synchronous serial I/O2, the transmitter and the receiver must use the same clock. When the internal clock is used, transfer is started by a write signal to the serial I/O2 register.

# [Serial I/O2 Control Register (SIO2CON)] 001D<sub>16</sub>

The serial I/O2 control register contains 8 bits which control various serial I/O functions.

Fig. 31 Structure of serial I/O2 control register

Fig. 32 Block diagram of serial I/O2

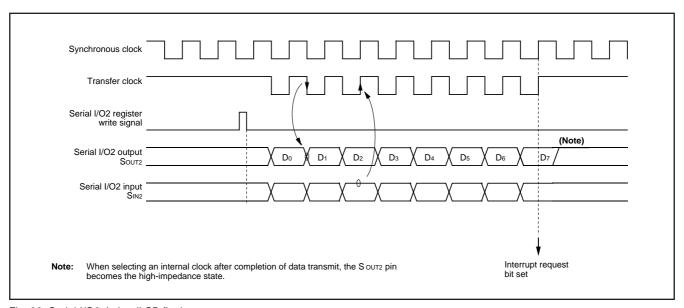

### ●Serial I/O2 Operation

When writing to the serial I/O2 register (001F16), the serial I/O2 counter is set to "7".

After the write is completed, data is output from the SOUT2 pin each time the transfer clock goes from "H" to "L". In addition, each time the transfer clock goes from "L" to "H", the contents of the serial I/O2 register are shifted by 1 bit data is simultaneously received from the SIN2 pin.

When selecting an internal clock as the transfer clock source, the serial I/O2 counter goes to "0" by counting the transfer clock 8 times, and the transfer clock stops at "H", and the interrupt request bit is set to "1". In addition, the Sout2 pin becomes the high-impedance state after the completion of data transfer. (Bit 7 of the serial I/O2 control register does not go to "1" and only the Sout2 pin becomes the high-impedance state.)

When selecting an external clock as the transfer clock source, the interrupt request bit is set when counting the transfer clock 8 times. However, the transfer clock does not stop, so that control the clock externally. The SOUT2 pin does not become the high-impedance state after completion of data transmit.

In order to set the Sout2 pin to the high-impedance state when selecting an external clock, set "1" to bit 7 of the serial I/O2 control register after completion of data transmit. Also, make sure that Sclk2 is at "H" for this process. When the next data is transmitted (falling of transfer clock), bit 7 of the serial I/O2 control register goes to "0" and the Sout2 pin goes to an active state.

Fig. 33 Serial I/O2 timing (LSB first)

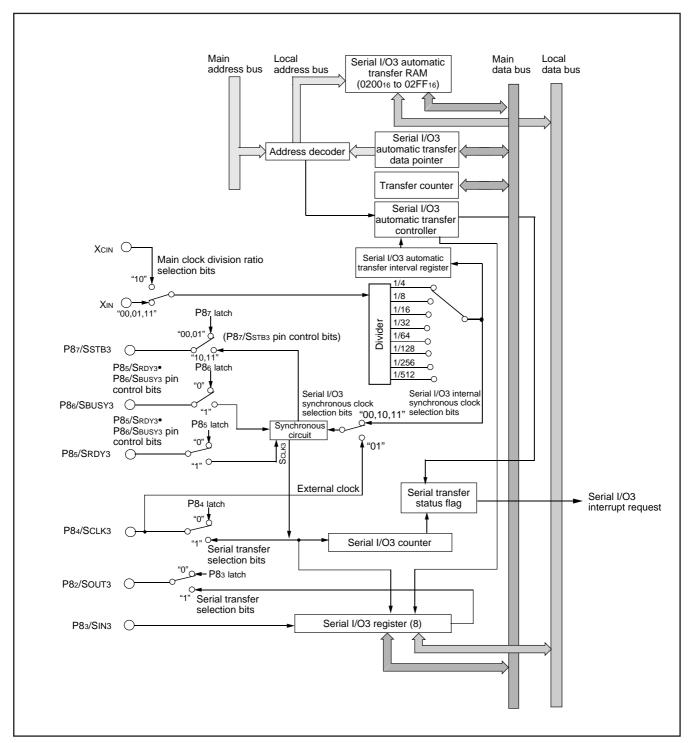

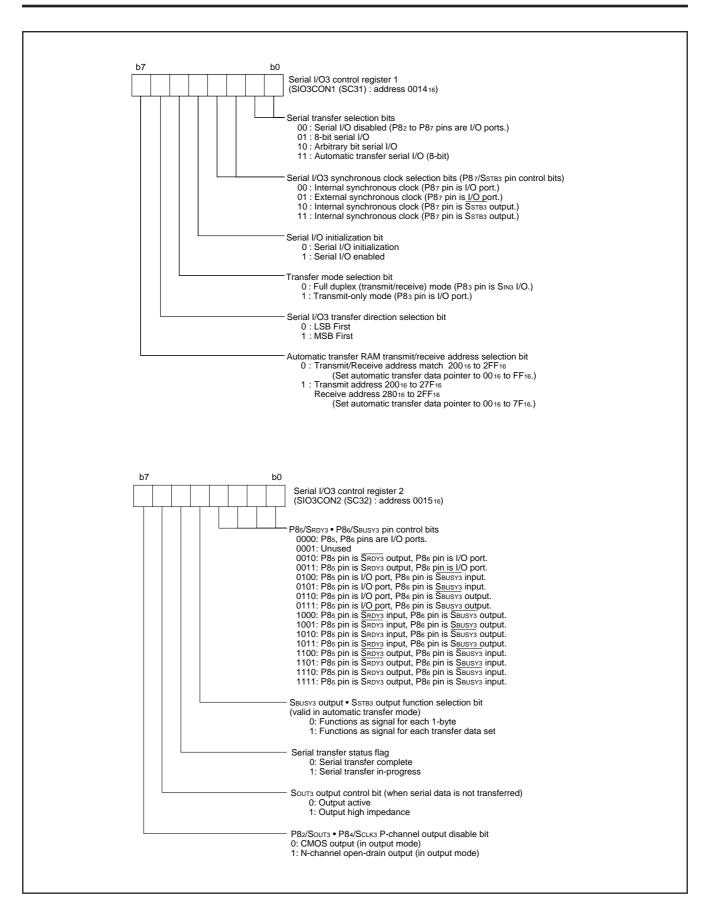

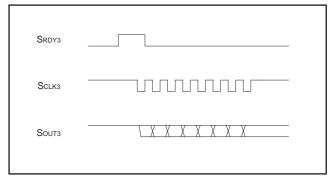

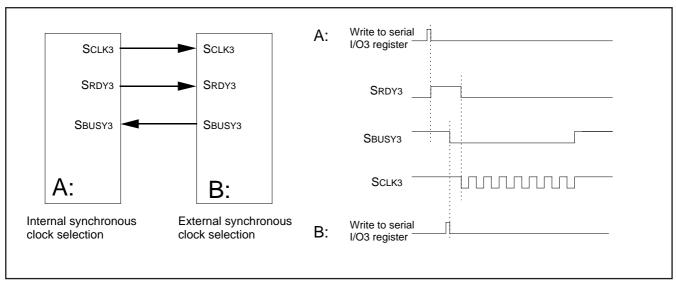

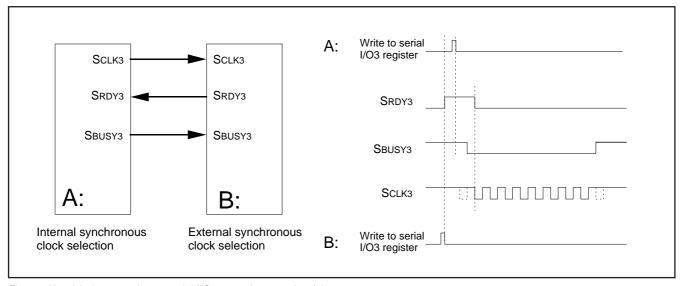

#### Serial I/O3

Serial I/O3 has the following modes: 8-bit serial I/O, arbitrary bits from 1 to 256 serial I/O, up to 256-byte auto-transfer serial I/O. The 8-bit serial I/O transfers through serial I/O3 register (address 001316). The arbitrary bits and auto-transfer serial I/O modes transfer through the 256-byte serial I/O3 auto-transfer RAM (addresses 020016 to 02FF16).

The P85/SRDY3, P86/SBUSY3, and P87/SSTB3 pins all have the handshake input/output signal function and can perform active logic high/low selection.

Fig. 34 Block diagram of serial I/O3

Fig. 35 Structure of serial I/O3 control registers 1 and 2

#### ●Serial I/O3 Operation

An internal or external synchronous clock can be selected as the serial transfer synchronous clock by the serial I/O3 synchronous clock selection bits of the serial I/O3 control register 1.

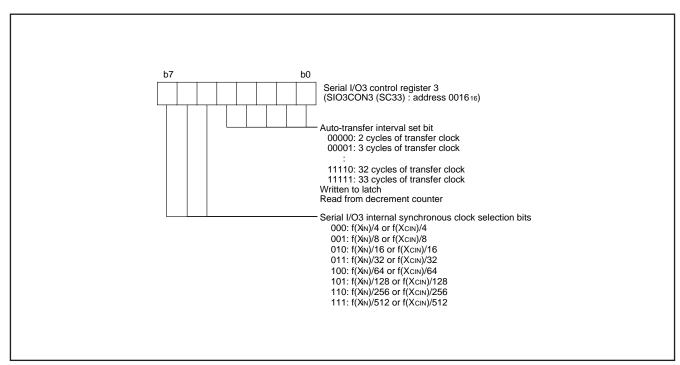

Since the internal synchronous clock has its own built-in divider, 8 types of clocks can be selected by the serial I/O3 internal synchronous clock selection bits of the serial I/O3 control register 3.

Either I/O port or handshake I/O signal function can be selected for the P85/SRDY3, P86/SBUSY3, and P87/SSTB3 pins by the serial I/O3 synchronous clock selection bits (P87/SSTB3 pin control bits) of the serial I/O3 control register 1 or the P85/SRDY3•P86/SBUSY3 pin control bits of the serial I/O3 control register 2.

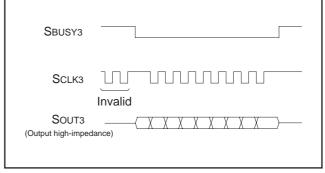

CMOS output or N-channel open-drain output can be selected for the SCLK3 and SOUT3 output pins by the P82/SOUT3 • P84/SCLK3 P-channel output disable bit of the serial I/O3 control register 2.

The Souts output control bit of the serial I/O3 control register 2 can be used to select the status of the Souts pin when serial data is not transferred; either output active or high-impedance. However, when selecting an external synchronous clock, the Souts pin can go to the high-impedance status by setting the Souts output control bit to "1" when Sclk3 input is at "H" after transfer completion. When the next serial transfer begins and Sclk3 goes to "L", the Souts output control bit is automatically reset to "0" and goes to an output active status.

Regardless of selecting an internal or external synchronous clock, the serial transfer has both a full duplex mode as well as a transmit-only mode. These modes are set by the transfer mode selection bit of serial I/O3 control register 1.

LSB first or MSB first can be selected for the input/output order of the serial transfer bit string by the serial I/O3 transfer direction selection bit of serial I/O3 control register 1.

In order to use serial I/O3, the following process must be followed after all of the above set have been completed: First, select any one of 8-bit serial I/O, arbitrary bit serial I/O, or auto-transfer serial I/O by setting the serial transfer selection bits of the serial I/O3 control register 1. Then, enable the serial I/O by setting the serial I/O initialization bit of the serial I/O3 control register 1 to "1".

Whether using an internal or external synchronous clock, set the serial I/O initialization bit to "0" when terminating a serial transfer during the transmission.

Fig. 36 Structure of serial I/O3 control register 3

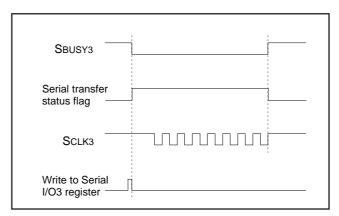

# (1) 8-bit serial I/O mode

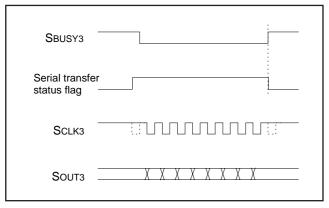

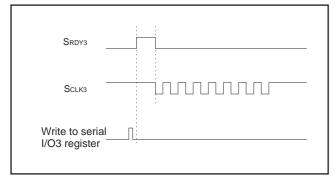

Address 001316 is the serial I/O3 register. When selecting an internal synchronous clock, serial transfer of the 8-bit serial I/O starts by the write signal to the serial I/O3 register (address 001316).

The serial transfer status flag of the serial I/O3 control register 2 indicates the serial I/O3 register status. The flag is set to "1" by a serial I/O3 register write, which triggers a transfer start. After the 8-bit transfer is completed, the flag is reset to "0" and a serial I/O3 interrupt request occurs simultaneously.

When an external synchronous clock is selected, the contents of the serial I/O3 register are continually shifted while the transfer clock inputs to Sclk3. In this case, control the clock externally.

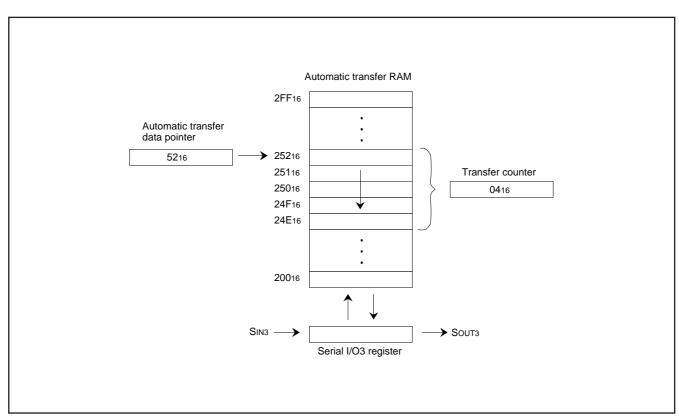

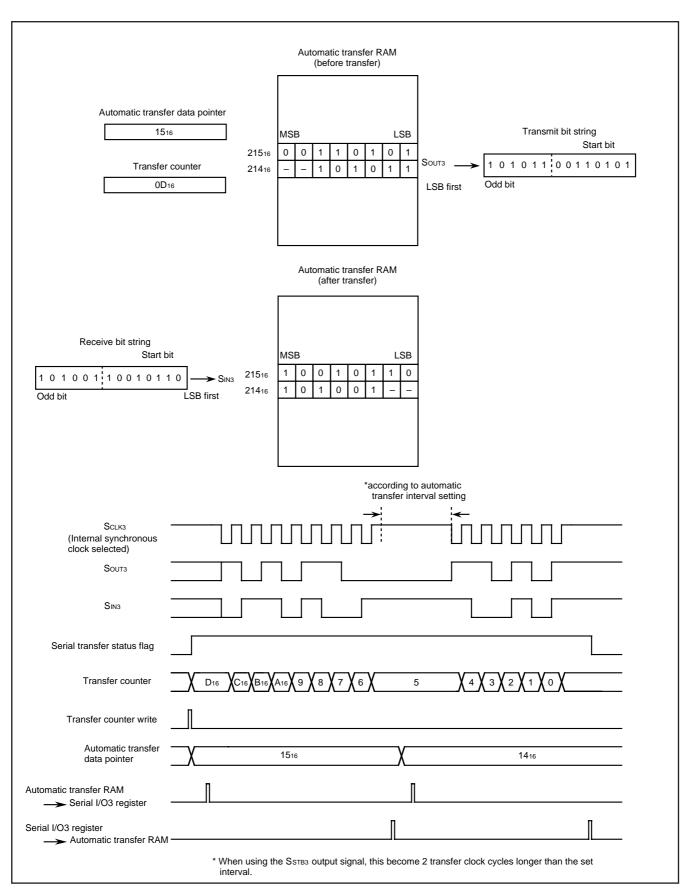

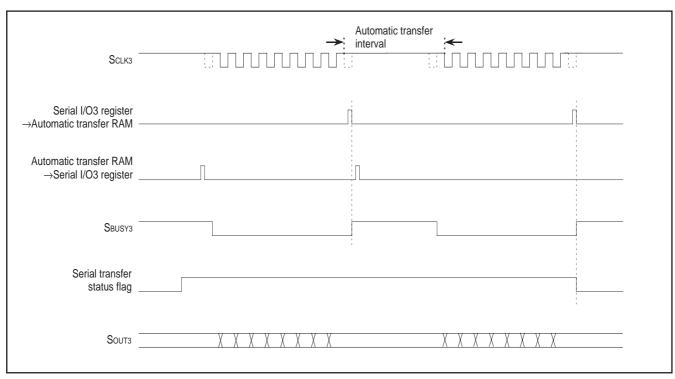

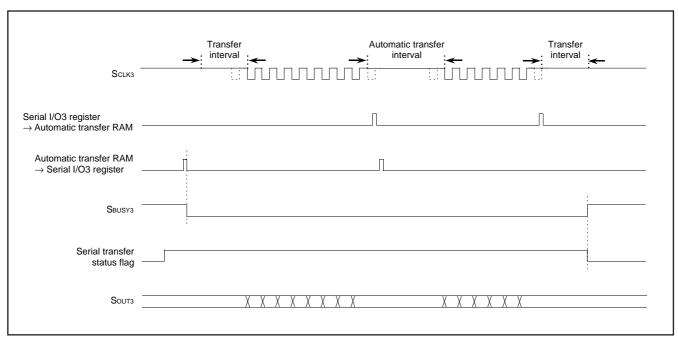

### (2) Auto-transfer serial I/O mode

Since read and write to the serial I/O3 register are controlled by the serial I/O3 automatic transfer controller, address 001316 functions as the transfer counter (in byte units).

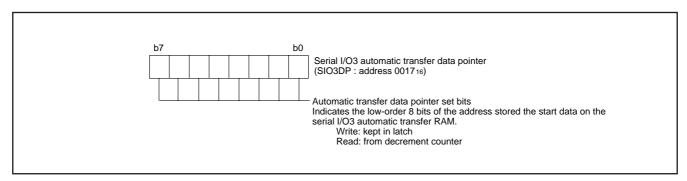

In order to make a serial transfer through the serial I/O3 automatic transfer RAM (addresses 020016 to 02FF16), it is necessary to set the serial I/O3 automatic transfer data pointer before transferring data. The automatic transfer data pointer set bits indicate the low-order 8 bits of the start data stored address. The automatic transfer RAM transmit/receive address select bit can divide the 256-byte serial I/O3 automatic transfer RAM into two areas: 128-byte transmit data area and 128-byte receive data area.

When an internal synchronous clock is selected and any of the following conditions apply, the transfer interval between each 1-byte data can be set by the automatic transfer interval set bits of the serial I/O3 control register 3:

- 1. The handshake signal is not used.

- 2. The handshake signal's SRDY3 output, SBUSY3 output, and SSTB3 output are used independently.

- 3. The handshake signal's output is used in groups: SRDY3/SSTB3 output or SBUSY3/SSTB3.

There are 32 values among 2 and 33 cycles of the transfer clock. When the automatic transfer interval setting is valid and SBUSY3 output is used, and the SBUSY3 and SSTB3 output function as sig-

nal for each transfer data set by the SBUSY3 output•SSTB3 output function selection bit, there is the transfer interval before the first data is transmitted/received, as well as after the last data is transmitted/received. When using SSTB3 output, regardless of the contents of the SBUSY3 output • SSTB3 output function selection bit, this transfer interval become 2 cycles longer than the value set for each 1-byte data. In addition, when using the combined output of SBUSY3 and SSTB3 as the signal for each transfer data set, the transfer interval after completion of transmission/receipt of the last data become 2 cycles longer than the set value.

When selecting an external synchronous clock, the automatic transfer interval cannot be set.

After all of the above bit settings have been completed, and an internal synchronous clock has been selected, serial automatic transfer starts when the value of the number of transfer bytes, decremented by 1, is written to the transfer counter (address 001316). When an external synchronous clock is selected, write the value of the transfer bytes, decremented by 1, to the transfer counter, and input the transfer clock to SCLK3 after 5 or more cycles of internal clock  $\phi$ .

Set the transfer interval of each 1-byte data transmission to 5 or more cycles of the internal clock  $\phi$  after the rising edge of the last bit of a 1-byte data.

Regardless of internal or external synchronous clock, the automatic transfer data pointer and transfer counter are both decremented after receipt of each 1-byte data is completed and it is written to the automatic transfer RAM. The serial transfer status flag is set to "1" by writing to the transfer counter which triggers the start of transmission. After the last data is written to the automatic transfer RAM, the serial transfer status flag is set to "0" and a serial I/O3 interrupt request occurs simultaneously.

The write values of the automatic transfer data pointer set bits and the automatic transfer interval set bits are kept in the latch. As a transfer counter write occurs, each value is transferred to its corresponding decrement counter.

Fig. 37 Structure of serial I/O3 automatic transfer data pointer

# (3) Arbitrary bit serial I/O mode

Since read and write of the serial I/O3 register are controlled by the serial I/O3 automatic transfer controller, address 001316 functions as the transfer counter (in byte units).

After the serial I/O3 automatic transfer data pointer and automatic transfer interval set bits have been set, and an internal synchronous clock selected, serial automatic transfer starts when the value of the number of transfer bits decremented by 1 is written to the transfer counter (address 001316), just as in the automatic transfer serial I/O. When selecting an external synchronous clock, write the value of the transfer bits decremented by 1 to the transfer counter, then input the transfer clock to SCLK3 after 5 or more cycles of internal clock  $\phi$ . The transfer interval after each 8-bit data transfer must be 5 or more cycles of internal clock  $\phi$  after the rising edge of the last bit of the 8-bit data.

When selecting an internal synchronous clock, the automatic transfer interval can be specified regardless of the contents of the selected handshake signal.

In this case, when the automatic transfer interval setting is valid and SBUSY3 output is used there are the transfer interval before the first data is transmitted/received, as well as after the last data is transmitted/received just as in the automatic transfer serial I/O mode. When using SSTB3 output, this transfer interval become 2 cycles longer than the value set for each 8-bit data. In addition, when using the combined output of SBUSY3 and SSTB3, the transfer interval after completion of transmission/receipt of the last data become 2 cycles longer than the set value.

When selecting an external synchronous clock, the automatic transfer interval cannot be specified.

Regardless of internal or external synchronous clock, the automatic transfer data pointer is decremented after each 8-bit data is received and then written to the auto-transfer RAM. The transfer counter is decremented with the transfer clock. The serial transfer status flag is set to "1" by writing to the transfer counter which triggers the start of transmission. After the last data is written to the automatic transfer RAM, the serial transfer status flag is set to "0" and a serial I/O3 interrupt request occurs simultaneously.

The write values of the automatic transfer data pointer set bits and the automatic transfer interval set bits are kept in the latch. As a transfer counter write occurs, each value is transferred to its corresponding decrement counter.

If the last data does not fill 8 bits, the receive data stored in the serial I/O3 automatic transfer RAM become the closest MSB odd bit if the transfer direction select bit is set to LSB first, or the closest LSB odd bit if the transfer direction select bit is set to MSB first.

Fig. 38 Automatic transfer serial I/O operation

Fig. 39 Arbitrary bit serial I/O operation

# **Handshake Signal**

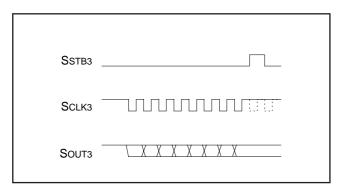

#### ● SSTB3 output signal

The SSTB3 output is a signal to inform an end of transmission/reception to the serial transfer destination . The SSTB3 output signal can be used only when the internal synchronous clock is selected. In the initial status, that is, in the status in which the serial I/O initialization bit (b4) is reset to "0", the SSTB3 output goes to "L", and the  $\overline{\text{SSTB3}}$  output goes to "H".

At the end of transmit/receive operation, when the data of the serial I/O3 register is all output from SOUT3, pulses which are the SSTB3 output of "H" and the  $\overline{\text{SSTB3}}$  output of "L" are output in the period of 1 cycle of the transfer clock. After that, each pulse is returned to the initial status in which SSTB3 output goes to "L" and the  $\overline{\text{SSTB3}}$  output goes to "H".

Furthermore, after 1 cycle, the serial transfer status flag (b5) is reset to "0"

In the automatic transfer serial I/O mode, whether making the SSTB3 output active at an end of each 1-byte data or after completion of transfer of all data can be selected by the SBUSY3 output • SSTB3 output function selection bit (b4 of address 001516) of serial I/O3 control register 2.

Fig. 40 SSTB3 output operation

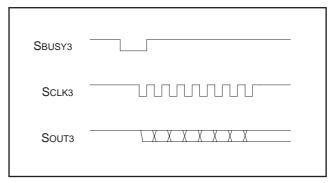

#### ● SBUSY3 input signal

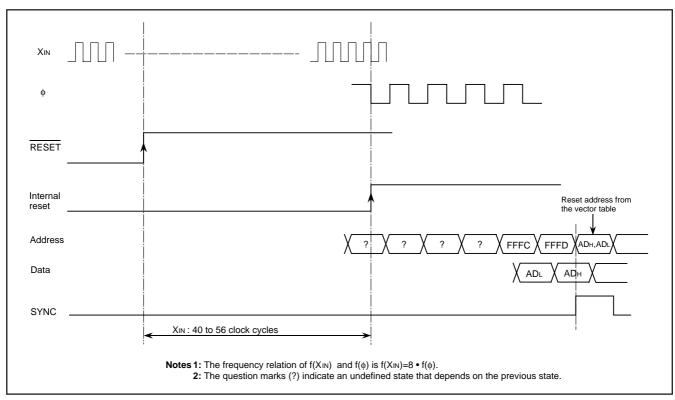

The SBUSY3 input is a signal which receives a request for a stop of transmission/reception from the serial transfer destination.

When the internal synchronous clock is selected, input an "H" level signal into the Sbusy3 input and an "L" level signal into the  $\overline{\text{Sbusy3}}$  input in the initial status in which transfer is stopped.