# 32K x 68-bit Entry NETWORK SEARCH ENGINE

PRELIMINARY DATA

# **FEATURES SUMMARY**

- 32K DATA ENTRIES IN 68-BIT MODE

- TABLE MAY BE PARTITIONED INTO UP TO FOUR (4) QUADRANTS (Data entry width in each octant is configurable as 34, 68, 136, or 272 bits.)

- UP TO 83 MILLION SUSTAINED SEARCHES PER SECOND IN 68-BIT and 136-BIT CONFIGURATIONS

- UP TO 41.5 MILLION SEARCHES PER SECOND IN 34-BIT and 272-BIT CONFIGURATIONS

- SEARCHES ANY SUB-FIELD IN A SINGLE CYCLE

- OFFERS BIT-BY-BIT and GLOBAL MASKING

- SYNCHRONOUS, PIPELINED OPERATION

- UP TO 31 SEARCH ENGINES CASCADABLE WITHOUT PERFORMANCE DEGRADATION

- WHEN CASCADED, THE DATABASE ENTRIES CAN SCALE FROM 248K TO 1984K DEPENDING ON THE WIDTH OF THE ENTRY

- GLUELESS INTERFACE TO INDUSTRY-STANDARD SRAMS

- SIMPLE HARDWARE INSTRUCTION INTERFACE

- IEEE 1149.1 TEST ACCESS PORT

- OPERATING SUPPLY VOLTAGES INCLUDE: V<sub>DD</sub> (Operating Supply Voltage) = 1.8V V<sub>DDQ</sub> (Operating Supply Voltage for I/O) = 2.5 or 3.3V

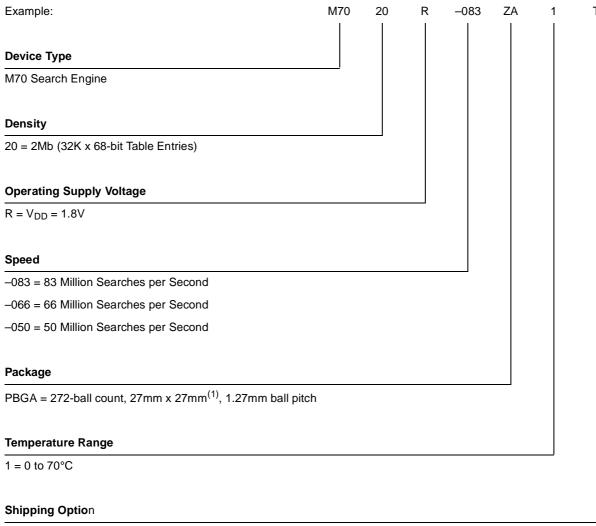

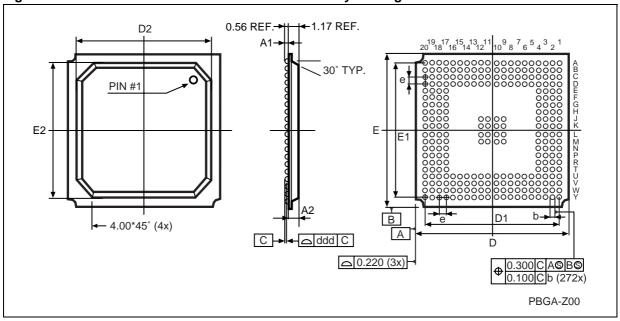

- 272 PBGA, 27mm x 27mm

272-ball PBGA

27mm x 27mm

December 2001 1/150

# M7020R

# **TABLE OF CONTENTS**

| DESCRIPTION                                                | ļ |

|------------------------------------------------------------|---|

| Overview         8           Performance         8         |   |

| Applications                                               |   |

| Product Range (Table 1.)                                   |   |

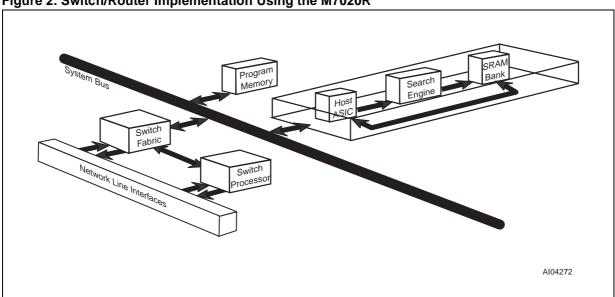

| Switch/Router Implementation Using the M7020R (Figure 2.)  |   |

| Signal Names (Table 2.)                                    |   |

| Connections (Figure 3.)                                    |   |

| MAXIMUM RATING                                             | • |

| Absolute Maximum Ratings (Table 3.)                        | • |

| DC AND AC PARAMETERS13                                     | į |

| DC and AC Measurement Conditions (Table 4.)                |   |

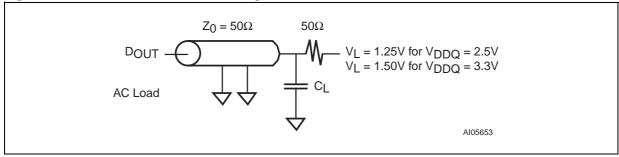

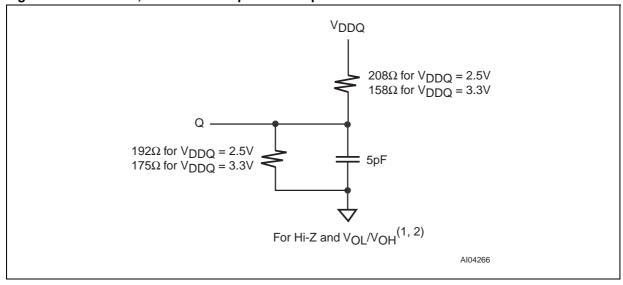

| M7020R 2.5, or 3.3V AC Testing Load (Figure 5.)            |   |

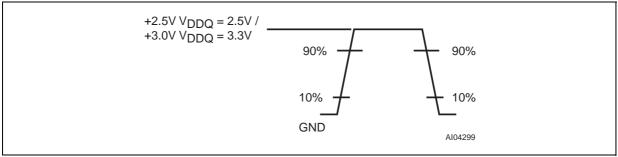

| M7020R 2.5, or 3.3V Input Waveform (Figure 6.)             |   |

| M7020R 2.5, or 3.3V I/O Output Load Equivalent (Figure 7.) |   |

| Capacitance (Table 5.)                                     |   |

| DC Characteristics (Table 6.)                              |   |

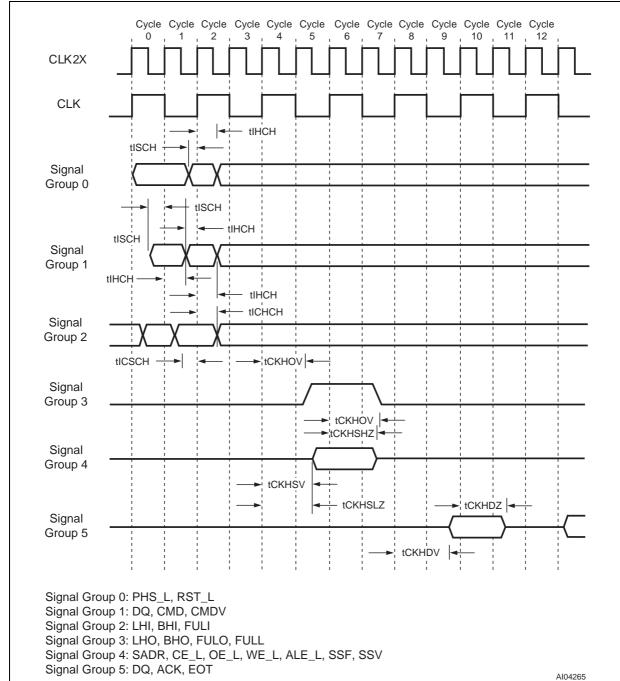

| AC Timing Waveforms with CLK2X (Figure 8.)                 |   |

| OPERATION                                                  |   |

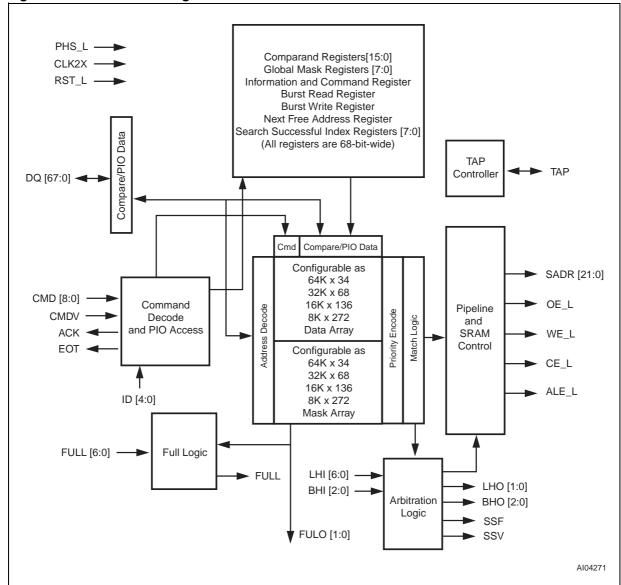

| CMD Bus and DQ Bus18                                       | ł |

| Database Entry (Data Array and Mask Array)                 |   |

| Arbitration Logic                                          |   |

| Pipeline and SRAM Control                                  |   |

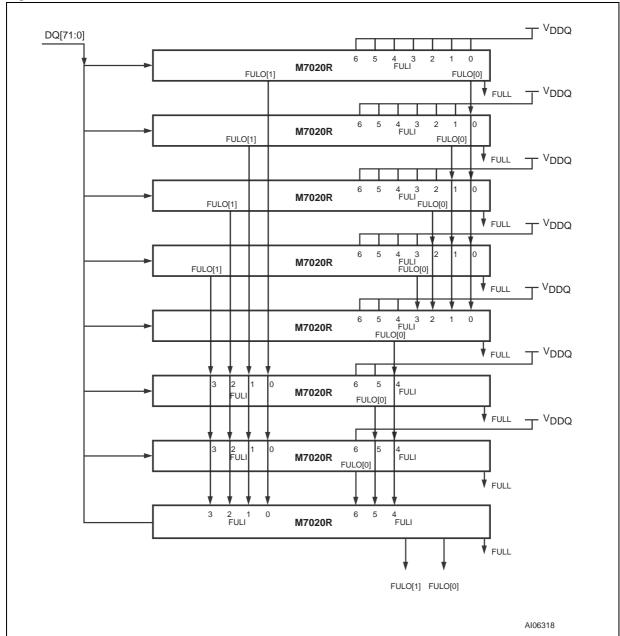

| Full Logic                                                 |   |

| CONNECTION DESCRIPTIONS19                                  | ) |

| Clocks and Reset                                           | ) |

| CMD and DQ Bus                                             | ) |

| SRAM Interface                                             | , |

| Cascade Interface                                          | ) |

| Device Identification                                      | ) |

| Supplies                                                   |   |

| Test Access Port                                           | ) |

| CLOCKS                                                     | ) |

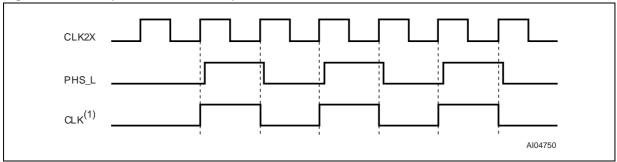

| Clocks (CLK2X and PHS_L) (Figure 9.)                       | ) |

| REGISTERS       21         Register Overview (Table 8.)       21         Comparand Registers       22         Mask Registers       22         Comparand Register Selection During SEARCH and LEARN Instructions (Figure 10.)       22         Addressing the Global Masks Register Array (Figure 11.)       22         SEARCH-Successful Registers (SSR) Description (Table 9.)       23         SEARCH-Successful Register (SSR) Description (Table 9.)       23         The Command Register       24         Command Register Field Descriptions (Table 10.)       24         The Information Register       25         Information Register Field Descriptions (Table 11.)       25         The Read Burst Address Register (RBURREG)       26         The Write Burst Address Register (RBURREG)       26         The Write Burst Register Description (Table 12.)       26         Write Burst Register Description (Table 12.)       26         Write Burst Register Description (Table 13.)       26         NFA Register (Table 14.)       26         SEARCH ENGINE ARCHITECTURE       27         Data and Mask Addressing       27         M7020R Database Width Configuration (Figure 13.)       28         MUII-width Configuration Example (Figure 13.)       28         MODAD D                                                                               |                                                                            |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----|

| Comparand Registers         22           Mask Registers         22           Comparand Register Selection During SEARCH and LEARN Instructions (Figure 10.)         22           Addressing the Global Masks Register Array (Figure 11.)         22           SEARCH-Successful Registers (SSR[0:7])         23           SEARCH-Successful Register (SSR) Description (Table 9.)         23           The Command Register         24           Command Register Field Descriptions (Table 10.)         24           The Information Register Field Descriptions (Table 11.)         25           Information Register Field Descriptions (Table 11.)         25           The Read Burst Address Register (RBURREG)         26           The Write Burst Address Register (WBURREG)         26           The NFA Register         26           Read Burst Register Description (Table 12.)         26           Write Burst Register Description (Table 13.)         26           NFA Register (Table 14.)         26           SEARCH ENGINE ARCHITECTURE         27           Data and Mask Addressing         27           M7020R Database Width Configuration (Figure 12.)         27           Bit Position Match (Table 15.)         28           M07020R Data and Mask Array Addressing (Figure 13.)         28           M0702                                    | EGISTERS                                                                   | 21 |

| Mask Registers       22         Comparand Register Selection During SEARCH and LEARN Instructions (Figure 10.)       22         Addressing the Global Masks Register Array (Figure 11.)       22         SEARCH-Successful Registers (SSR[0:7])       23         SEARCH-Successful Register (SSR) Description (Table 9.)       23         The Command Register       24         Command Register Field Descriptions (Table 10.)       24         The Information Register.       25         Information Register Field Descriptions (Table 11.)       25         The Read Burst Address Register (RBURREG)       26         The Write Burst Address Register (WBURREG)       26         The NFA Register       26         Read Burst Register Description (Table 12.)       26         Write Burst Register Description (Table 13.)       26         NFA Register (Table 14.)       26         SEARCH ENGINE ARCHITECTURE       27         Data and Mask Addressing       27         M7020R Database Width Configuration (Figure 12.)       27         Bit Position Match (Table 15.)       28         M07020R Data and Mask Array Addressing (Figure 13.)       28         M7020R Data and Mask Array Addressing (Figure 14.)       28         COMMAND CODES AND PARAMETERS       29 <td< td=""><td></td><td></td></td<>                                                   |                                                                            |    |

| Comparand Register Selection During SEARCH and LEARN Instructions (Figure 10.)         22           Addressing the Global Masks Register Array (Figure 11.)         22           SEARCH-Successful Registers (SSR) (SSR) (Description (Table 9.)         23           The Command Register (SSR) Description (Table 9.)         23           The Command Register Field Descriptions (Table 10.)         24           Command Register Field Descriptions (Table 10.)         24           The Information Register         25           Information Register Field Descriptions (Table 11.)         25           The Write Burst Address Register (RBURREG)         26           The Write Burst Address Register (WBURREG)         26           The NFA Register Description (Table 12.)         26           Write Burst Register Description (Table 13.)         26           Write Burst Register Description (Table 13.)         26           NFA Register (Table 14.)         26           SEARCH ENGINE ARCHITECTURE         27           Data and Mask Addressing         27           M7020R Database Width Configuration (Figure 12.)         27           Bit Position Match (Table 15.)         28           MILL-width Configuration Example (Figure 13.)         28           M7020R Data and Mask Array Addressing (Figure 14.)         28           COMMAN |                                                                            |    |

| Addressing the Global Masks Register Array (Figure 11.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •                                                                          |    |

| SEARCH-Successful Registers (SSR) Description (Table 9.).       23         SEARCH-Successful Register (SSR) Description (Table 9.).       23         The Command Register       24         Command Register Field Descriptions (Table 10.)       24         The Information Register Field Descriptions (Table 11.)       25         Information Register Field Descriptions (Table 11.)       25         The Read Burst Address Register (RBURREG)       26         The Write Burst Address Register (WBURREG)       26         The NFA Register       26         Read Burst Register Description (Table 12.)       26         Write Burst Register Description (Table 13.)       26         NFA Register (Table 14.)       26         SEARCH ENGINE ARCHITECTURE       27         Data and Mask Addressing       27         M7020R Database Width Configuration (Figure 12.)       27         Bit Position Match (Table 15.)       28         Multi-width Configuration Example (Figure 13.)       28         M7020R Data and Mask Array Addressing (Figure 14.)       28         COMMAND CODES AND PARAMETERS       29         Command Codes       29         Command Parameters (Table 17.)       29         XEAD COMMAND.       31         Burst READ of the Data and Mask Arrays (BLEN                                                                                | , , , , , , , , , , , , , , , , , , , ,                                    |    |

| SEARCH-Successful Register (SSR) Description (Table 9.)       23         The Command Register       24         Command Register Field Descriptions (Table 10.)       24         The Information Register Field Descriptions (Table 11.)       25         Information Register Field Descriptions (Table 11.)       25         The Read Burst Address Register (RBURREG)       26         The Write Burst Address Register (WBURREG)       26         The NFA Register       26         Read Burst Register Description (Table 12.)       26         Write Burst Register Description (Table 13.)       26         NFA Register (Table 14.)       26         SEARCH ENGINE ARCHITECTURE       27         Data and Mask Addressing       27         M7020R Database Width Configuration (Figure 12.)       27         Bit Position Match (Table 15.)       28         MV020R Data and Mask Array Addressing (Figure 13.)       28         M7020R Data and Mask Array Addressing (Figure 14.)       28         COMMAND CODES AND PARAMETERS       29         Command Codes       29         Command Parameters (Table 17.)       29         READ COMMAND.       30         Single Location READ Cycle Timing (Figure 15.)       31         Burst READ of the Data and Mask Arrays (BLEN = 4) (Fi                                                                               |                                                                            |    |

| The Command Register       24         Command Register Field Descriptions (Table 10.)       24         The Information Register       25         Information Register Field Descriptions (Table 11.)       25         The Read Burst Address Register (RBURREG)       26         The Write Burst Address Register (WBURREG)       26         The NFA Register       26         Read Burst Register Description (Table 12.)       26         Write Burst Register Description (Table 13.)       26         NFA Register (Table 14.)       26         SEARCH ENGINE ARCHITECTURE       27         Data and Mask Addressing       27         M7020R Database Width Configuration (Figure 12.)       27         Bit Position Match (Table 15.)       28         Multi-width Configuration Example (Figure 13.)       28         M7020R Data and Mask Array Addressing (Figure 14.)       28         COMMAND CODES AND PARAMETERS       29         Command Codes       29         Command Parameters (Table 17.)       29         READ COMMAND.       30         Single Location READ Cycle Timing (Figure 15.)       31         Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)       31         Burst READ Ofmand Parameters (Table 18.)       32 <tr< td=""><td>· · · · · · · · · · · · · · · · · · ·</td><td></td></tr<>                                      | · · · · · · · · · · · · · · · · · · ·                                      |    |

| Command Register Field Descriptions (Table 10.)       24         The Information Register       25         Information Register Field Descriptions (Table 11.)       25         The Read Burst Address Register (RBURREG)       26         The Write Burst Address Register (WBURREG)       26         The NFA Register       26         Read Burst Register Description (Table 12.)       26         Write Burst Register Description (Table 13.)       26         NFA Register (Table 14.)       26         SEARCH ENGINE ARCHITECTURE       27         Data and Mask Addressing       27         M7020R Database Width Configuration (Figure 12.)       27         Bit Position Match (Table 15.)       28         Multi-width Configuration Example (Figure 13.)       28         M7020R Data and Mask Array Addressing (Figure 14.)       28         COMMAND CODES AND PARAMETERS       29         Command Codes       29         Command Parameters (Table 16.)       29         Command Parameters (Table 17.)       29         READ COMMAND.       30         Single Location READ Cycle Timing (Figure 15.)       31         Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)       31         Burst READ Command Parameters (Table 18.)       32 </td <td></td> <td></td>                                                                           |                                                                            |    |

| The Information Register       25         Information Register Field Descriptions (Table 11.)       25         The Read Burst Address Register (RBURREG)       26         The Write Burst Address Register (WBURREG)       26         The NFA Register       26         Read Burst Register Description (Table 12.)       26         Write Burst Register Description (Table 13.)       26         NFA Register (Table 14.)       26         SEARCH ENGINE ARCHITECTURE       27         Data and Mask Addressing       27         M7020R Database Width Configuration (Figure 12.)       27         Bit Position Match (Table 15.)       28         Multi-width Configuration Example (Figure 13.)       28         M7020R Data and Mask Array Addressing (Figure 14.)       28         COMMAND CODES AND PARAMETERS       29         Command Codes       29         Command Codes (Table 16.)       29         Command Parameters (Table 17.)       29         READ COMMAND.       30         Single Location READ Cycle Timing (Figure 15.)       31         Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)       31         READ Command Parameters (Table 18.)       32         Data and Mask Array, SRAM Read Address Format (Table 19.)       32 <td>· · · · · · · · · · · · · · · · · · ·</td> <td></td>                                            | · · · · · · · · · · · · · · · · · · ·                                      |    |

| Information Register Field Descriptions (Table 11.)       25         The Read Burst Address Register (RBURREG)       26         The Write Burst Address Register (WBURREG)       26         The NFA Register       26         Read Burst Register Description (Table 12.)       26         Write Burst Register Description (Table 13.)       26         NFA Register (Table 14.)       26         SEARCH ENGINE ARCHITECTURE       27         Data and Mask Addressing       27         M7020R Database Width Configuration (Figure 12.)       27         Bit Position Match (Table 15.)       28         Multi-width Configuration Example (Figure 13.)       28         M7020R Data and Mask Array Addressing (Figure 14.)       28         COMMAND CODES AND PARAMETERS       29         Command Codes.       29         Command Parameters (Table 16.)       29         Command Parameters (Table 17.)       29         READ COMMAND.       30         Single Location READ Cycle Timing (Figure 15.)       31         Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)       31         READ Command Parameters (Table 18.)       32         Data and Mask Array, SRAM Read Address Format (Table 19.)       32         READ Address Format for Internal Registers (Table                                                                               | Command Register Field Descriptions (Table 10.)                            | 24 |

| The Read Burst Address Register (RBURREG)       26         The Write Burst Address Register (WBURREG)       26         The NFA Register       26         Read Burst Register Description (Table 12.)       26         Write Burst Register Description (Table 13.)       26         NFA Register (Table 14.)       26         SEARCH ENGINE ARCHITECTURE       27         Data and Mask Addressing       27         M7020R Database Width Configuration (Figure 12.)       27         Bit Position Match (Table 15.)       28         Multi-width Configuration Example (Figure 13.)       28         M7020R Data and Mask Array Addressing (Figure 14.)       28         COMMAND CODES AND PARAMETERS       29         Command Codes.       29         Command Codes (Table 16.)       29         Command Parameters (Table 17.)       29         READ COMMAND.       30         Single Location READ Cycle Timing (Figure 15.)       31         Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)       31         READ Command Parameters (Table 18.)       32         Data and Mask Array, SRAM Read Address Format (Table 19.)       32         READ Address Format for Internal Registers (Table 20.)       33                                                                                                                                           | · · · · · · · · · · · · · · · · · · ·                                      |    |

| The Write Burst Address Register (WBURREG)       26         The NFA Register       26         Read Burst Register Description (Table 12.)       26         Write Burst Register Description (Table 13.)       26         NFA Register (Table 14.)       26         SEARCH ENGINE ARCHITECTURE       27         Data and Mask Addressing       27         M7020R Database Width Configuration (Figure 12.)       27         Bit Position Match (Table 15.)       28         Multi-width Configuration Example (Figure 13.)       28         M7020R Data and Mask Array Addressing (Figure 14.)       28         COMMAND CODES AND PARAMETERS       29         Command Codes       29         Command Codes (Table 16.)       29         Command Parameters (Table 17.)       29         READ COMMAND.       30         Single Location READ Cycle Timing (Figure 15.)       31         Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)       31         READ Command Parameters (Table 18.)       32         Data and Mask Array, SRAM Read Address Format (Table 19.)       32         READ Address Format for Internal Registers (Table 20.)       33                                                                                                                                                                                                       | Information Register Field Descriptions (Table 11.)                        | 25 |

| The NFA Register       26         Read Burst Register Description (Table 12.)       26         Write Burst Register Description (Table 13.)       26         NFA Register (Table 14.)       26         SEARCH ENGINE ARCHITECTURE       27         Data and Mask Addressing       27         M7020R Database Width Configuration (Figure 12.)       27         Bit Position Match (Table 15.)       28         Multi-width Configuration Example (Figure 13.)       28         M7020R Data and Mask Array Addressing (Figure 14.)       28         COMMAND CODES AND PARAMETERS       29         Command Codes       29         Command Codes (Table 16.)       29         Command Parameters (Table 17.)       29         READ COMMAND.       30         Single Location READ Cycle Timing (Figure 15.)       31         Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)       31         READ Command Parameters (Table 18.)       32         Data and Mask Array, SRAM Read Address Format (Table 19.)       32         READ Address Format for Internal Registers (Table 20.)       33                                                                                                                                                                                                                                                                   | The Read Burst Address Register (RBURREG)                                  | 26 |

| Read Burst Register Description (Table 12.)       26         Write Burst Register Description (Table 13.)       26         NFA Register (Table 14.)       26         SEARCH ENGINE ARCHITECTURE       27         Data and Mask Addressing       27         M7020R Database Width Configuration (Figure 12.)       27         Bit Position Match (Table 15.)       28         Multi-width Configuration Example (Figure 13.)       28         M7020R Data and Mask Array Addressing (Figure 14.)       28         COMMAND CODES AND PARAMETERS       29         Command Codes       29         Command Codes (Table 16.)       29         Command Parameters (Table 17.)       29         READ COMMAND       30         Single Location READ Cycle Timing (Figure 15.)       31         Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)       31         READ Command Parameters (Table 18.)       32         Data and Mask Array, SRAM Read Address Format (Table 19.)       32         READ Address Format for Internal Registers (Table 20.)       33                                                                                                                                                                                                                                                                                                      | The Write Burst Address Register (WBURREG)                                 | 26 |

| Write Burst Register Description (Table 13.)       26         NFA Register (Table 14.)       26         SEARCH ENGINE ARCHITECTURE       27         Data and Mask Addressing       27         M7020R Database Width Configuration (Figure 12.)       27         Bit Position Match (Table 15.)       28         Multi-width Configuration Example (Figure 13.)       28         M7020R Data and Mask Array Addressing (Figure 14.)       28         COMMAND CODES AND PARAMETERS       29         Command Codes       29         Command Codes (Table 16.)       29         Command Parameters (Table 17.)       29         READ COMMAND       30         Single Location READ Cycle Timing (Figure 15.)       31         Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)       31         READ Command Parameters (Table 18.)       32         Data and Mask Array, SRAM Read Address Format (Table 19.)       32         READ Address Format for Internal Registers (Table 20.)       33                                                                                                                                                                                                                                                                                                                                                                   | The NFA Register                                                           | 26 |

| NFA Register (Table 14.).       26         SEARCH ENGINE ARCHITECTURE       27         Data and Mask Addressing       27         M7020R Database Width Configuration (Figure 12.)       27         Bit Position Match (Table 15.)       28         Multi-width Configuration Example (Figure 13.)       28         M7020R Data and Mask Array Addressing (Figure 14.)       28         COMMAND CODES AND PARAMETERS       29         Command Codes       29         Command Parameters       29         Command Parameters (Table 16.)       29         Command Parameters (Table 17.)       29         READ COMMAND       30         Single Location READ Cycle Timing (Figure 15.)       31         Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)       31         READ Command Parameters (Table 18.)       32         Data and Mask Array, SRAM Read Address Format (Table 19.)       32         READ Address Format for Internal Registers (Table 20.)       33                                                                                                                                                                                                                                                                                                                                                                                       | Read Burst Register Description (Table 12.)                                | 26 |

| SEARCH ENGINE ARCHITECTURE       27         Data and Mask Addressing       27         M7020R Database Width Configuration (Figure 12.)       27         Bit Position Match (Table 15.)       28         Multi-width Configuration Example (Figure 13.)       28         M7020R Data and Mask Array Addressing (Figure 14.)       28         COMMAND CODES AND PARAMETERS       29         Command Codes       29         Command Codes (Table 16.)       29         Command Parameters (Table 17.)       29         READ COMMAND         Single Location READ Cycle Timing (Figure 15.)       31         Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)       31         READ Command Parameters (Table 18.)       32         Data and Mask Array, SRAM Read Address Format (Table 19.)       32         READ Address Format for Internal Registers (Table 20.)       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Write Burst Register Description (Table 13.)                               | 26 |

| Data and Mask Addressing       27         M7020R Database Width Configuration (Figure 12.)       27         Bit Position Match (Table 15.)       28         Multi-width Configuration Example (Figure 13.)       28         M7020R Data and Mask Array Addressing (Figure 14.)       28         COMMAND CODES AND PARAMETERS       29         Command Codes       29         Command Codes (Table 16.)       29         Command Parameters (Table 16.)       29         Command Parameters (Table 17.)       29         READ COMMAND       30         Single Location READ Cycle Timing (Figure 15.)       31         Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)       31         READ Command Parameters (Table 18.)       32         Data and Mask Array, SRAM Read Address Format (Table 19.)       32         READ Address Format for Internal Registers (Table 20.)       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | NFA Register (Table 14.)                                                   | 26 |

| Data and Mask Addressing       27         M7020R Database Width Configuration (Figure 12.)       27         Bit Position Match (Table 15.)       28         Multi-width Configuration Example (Figure 13.)       28         M7020R Data and Mask Array Addressing (Figure 14.)       28         COMMAND CODES AND PARAMETERS       29         Command Codes       29         Command Codes (Table 16.)       29         Command Parameters (Table 16.)       29         Command Parameters (Table 17.)       29         READ COMMAND       30         Single Location READ Cycle Timing (Figure 15.)       31         Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)       31         READ Command Parameters (Table 18.)       32         Data and Mask Array, SRAM Read Address Format (Table 19.)       32         READ Address Format for Internal Registers (Table 20.)       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            |    |

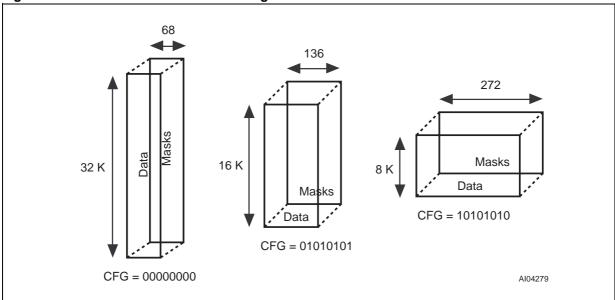

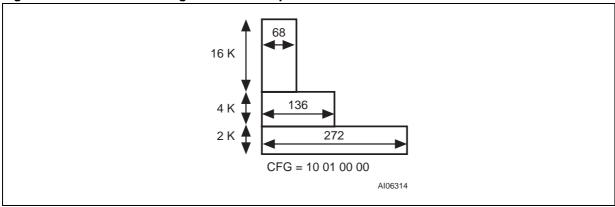

| M7020R Database Width Configuration (Figure 12.)       27         Bit Position Match (Table 15.)       28         Multi-width Configuration Example (Figure 13.)       28         M7020R Data and Mask Array Addressing (Figure 14.)       28         COMMAND CODES AND PARAMETERS       29         Command Codes       29         Commands and Command Parameters       29         Command Codes (Table 16.)       29         Command Parameters (Table 17.)       29         READ COMMAND       30         Single Location READ Cycle Timing (Figure 15.)       31         Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)       31         READ Command Parameters (Table 18.)       32         Data and Mask Array, SRAM Read Address Format (Table 19.)       32         READ Address Format for Internal Registers (Table 20.)       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |    |

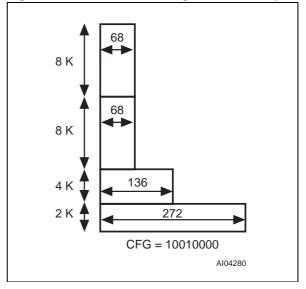

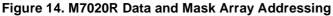

| Bit Position Match (Table 15.)       28         Multi-width Configuration Example (Figure 13.)       28         M7020R Data and Mask Array Addressing (Figure 14.)       28         COMMAND CODES AND PARAMETERS       29         Command Codes       29         Commands and Command Parameters       29         Command Codes (Table 16.)       29         Command Parameters (Table 17.)       29         READ COMMAND       30         Single Location READ Cycle Timing (Figure 15.)       31         Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)       31         READ Command Parameters (Table 18.)       32         Data and Mask Array, SRAM Read Address Format (Table 19.)       32         READ Address Format for Internal Registers (Table 20.)       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Data and Mask Addressing                                                   | 27 |

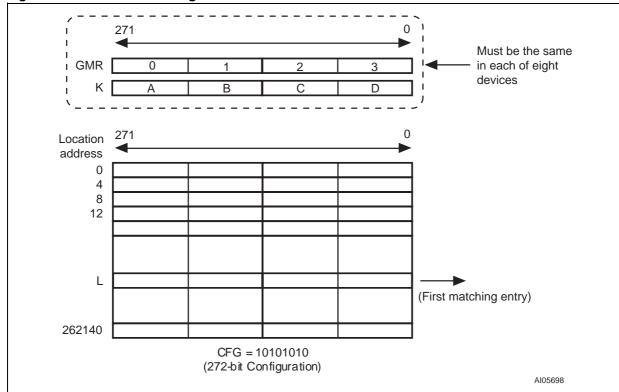

| Multi-width Configuration Example (Figure 13.)       28         M7020R Data and Mask Array Addressing (Figure 14.)       28         COMMAND CODES AND PARAMETERS       29         Command Codes       29         Commands and Command Parameters       29         Command Codes (Table 16.)       29         Command Parameters (Table 17.)       29         READ COMMAND       30         Single Location READ Cycle Timing (Figure 15.)       31         Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)       31         READ Command Parameters (Table 18.)       32         Data and Mask Array, SRAM Read Address Format (Table 19.)       32         READ Address Format for Internal Registers (Table 20.)       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | M7020R Database Width Configuration (Figure 12.)                           | 27 |

| M7020R Data and Mask Array Addressing (Figure 14.)       28         COMMAND CODES AND PARAMETERS       29         Command Codes       29         Commands and Command Parameters       29         Command Codes (Table 16.)       29         Command Parameters (Table 17.)       29         READ COMMAND       30         Single Location READ Cycle Timing (Figure 15.)       31         Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)       31         READ Command Parameters (Table 18.)       32         Data and Mask Array, SRAM Read Address Format (Table 19.)       32         READ Address Format for Internal Registers (Table 20.)       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Bit Position Match (Table 15.)                                             | 28 |

| COMMAND CODES AND PARAMETERS       29         Command Codes       29         Commands and Command Parameters       29         Command Codes (Table 16.)       29         Command Parameters (Table 17.)       29         READ COMMAND       30         Single Location READ Cycle Timing (Figure 15.)       31         Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)       31         READ Command Parameters (Table 18.)       32         Data and Mask Array, SRAM Read Address Format (Table 19.)       32         READ Address Format for Internal Registers (Table 20.)       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Multi-width Configuration Example (Figure 13.)                             | 28 |

| Command Codes.       29         Commands and Command Parameters       29         Command Codes (Table 16.)       29         Command Parameters (Table 17.)       29         READ COMMAND.       30         Single Location READ Cycle Timing (Figure 15.)       31         Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)       31         READ Command Parameters (Table 18.)       32         Data and Mask Array, SRAM Read Address Format (Table 19.)       32         READ Address Format for Internal Registers (Table 20.)       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | M7020R Data and Mask Array Addressing (Figure 14.)                         | 28 |

| Command Codes.       29         Commands and Command Parameters       29         Command Codes (Table 16.)       29         Command Parameters (Table 17.)       29         READ COMMAND.       30         Single Location READ Cycle Timing (Figure 15.)       31         Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)       31         READ Command Parameters (Table 18.)       32         Data and Mask Array, SRAM Read Address Format (Table 19.)       32         READ Address Format for Internal Registers (Table 20.)       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                            |    |

| Commands and Command Parameters       29         Command Codes (Table 16.)       29         Command Parameters (Table 17.)       29         READ COMMAND.       30         Single Location READ Cycle Timing (Figure 15.)       31         Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)       31         READ Command Parameters (Table 18.)       32         Data and Mask Array, SRAM Read Address Format (Table 19.)       32         READ Address Format for Internal Registers (Table 20.)       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | OMMAND CODES AND PARAMETERS                                                | 29 |

| Command Codes (Table 16.)       29         Command Parameters (Table 17.)       29         READ COMMAND.       30         Single Location READ Cycle Timing (Figure 15.)       31         Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)       31         READ Command Parameters (Table 18.)       32         Data and Mask Array, SRAM Read Address Format (Table 19.)       32         READ Address Format for Internal Registers (Table 20.)       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Command Codes                                                              | 29 |

| Command Parameters (Table 17.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Commands and Command Parameters                                            | 29 |

| Single Location READ Cycle Timing (Figure 15.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Command Codes (Table 16.)                                                  | 29 |

| Single Location READ Cycle Timing (Figure 15.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Command Parameters (Table 17.)                                             | 29 |

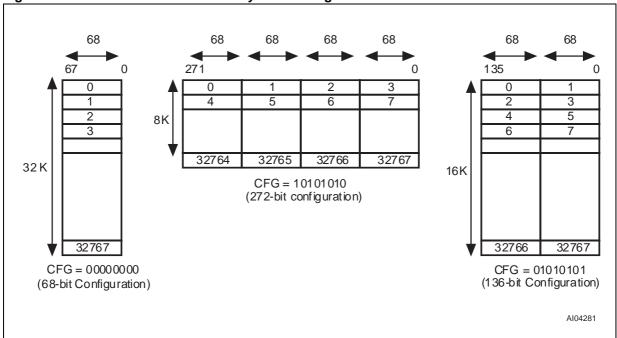

| Single Location READ Cycle Timing (Figure 15.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                            |    |

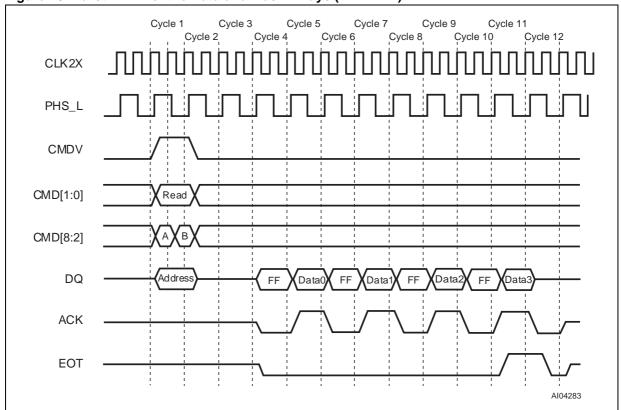

| Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | EAD COMMAND                                                                | 30 |

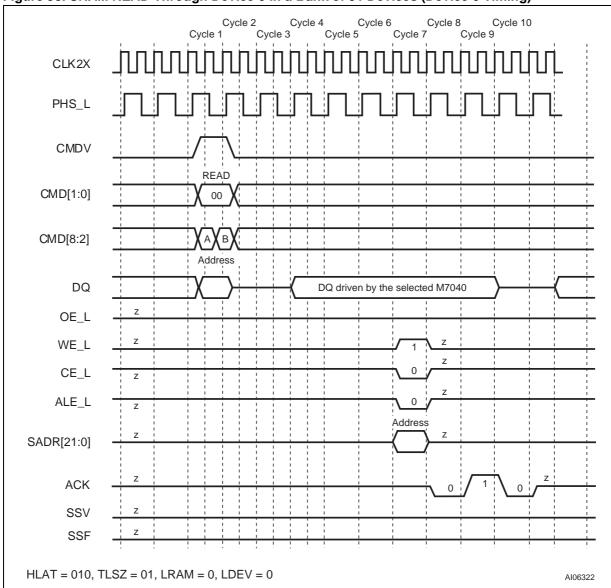

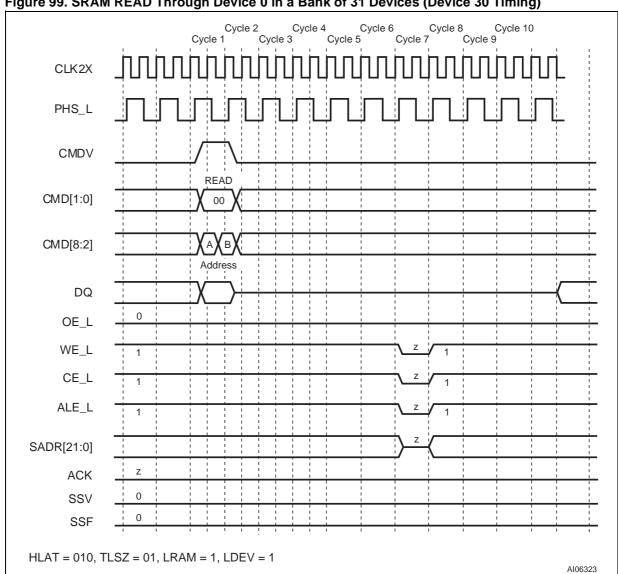

| READ Command Parameters (Table 18.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Single Location READ Cycle Timing (Figure 15.)                             | 31 |

| READ Command Parameters (Table 18.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Burst READ of the Data and Mask Arrays (BLEN = 4) (Figure 16.)             | 31 |

| READ Address Format for Internal Registers (Table 20.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                            |    |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Data and Mask Array, SRAM Read Address Format (Table 19.)                  | 32 |

| READ Address Format for Data and Mask Arrays (Table 21.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | READ Address Format for Internal Registers (Table 20.)                     | 33 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | READ Address Format for Data and Mask Arrays (Table 21.)                   | 33 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                            |    |

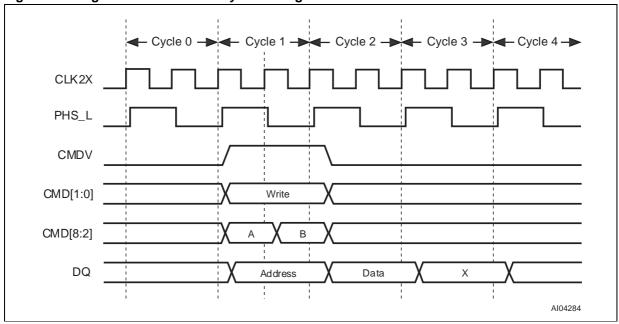

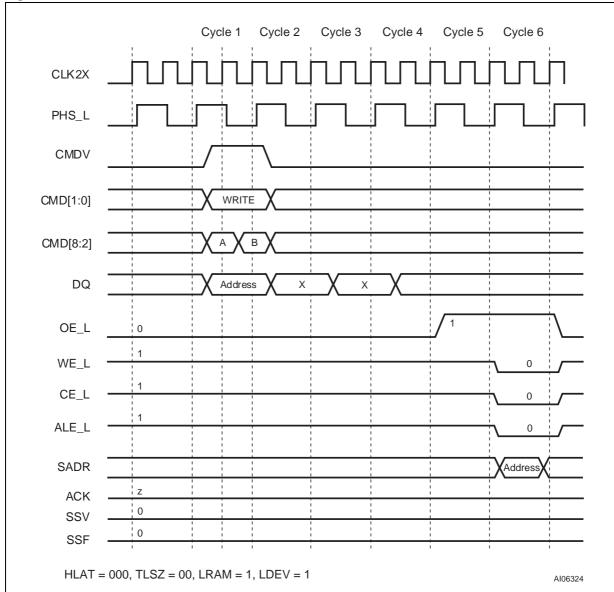

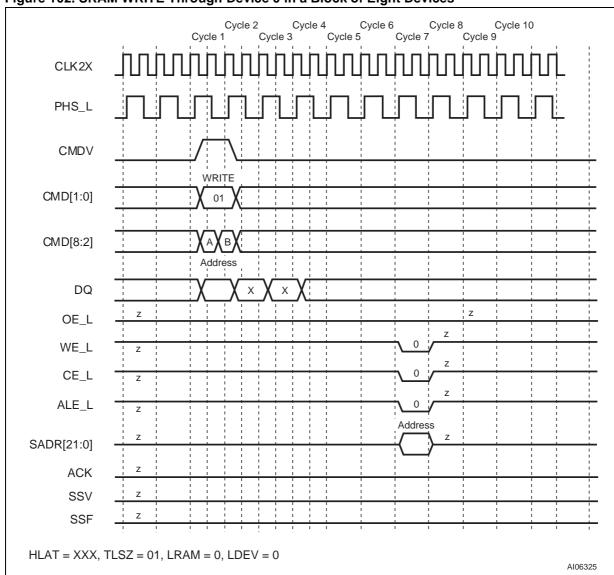

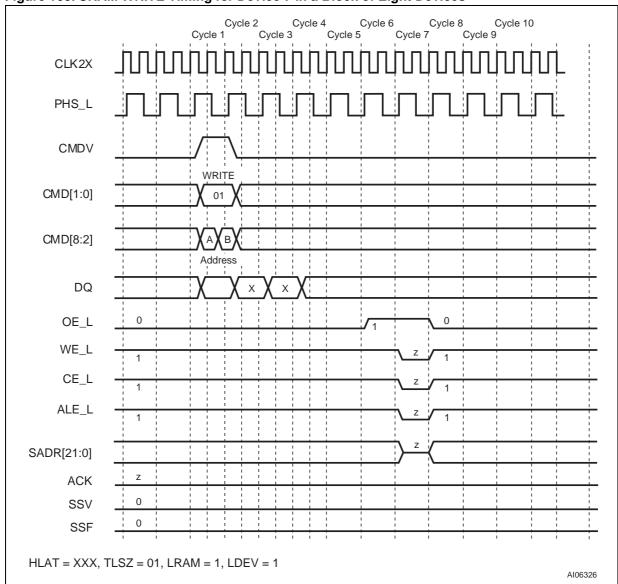

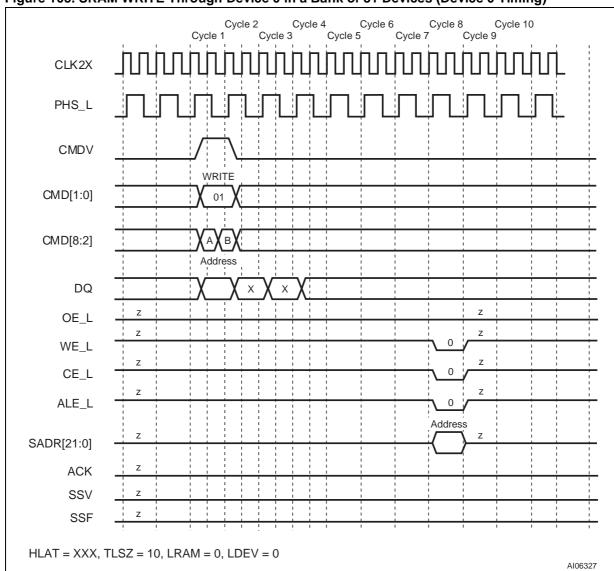

| VRITE COMMAND33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RITE COMMAND                                                               | 33 |

| Single Location WRITE Cycle Timing (Figure 17.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Single Location WRITE Cycle Timing (Figure 17.)                            | 34 |

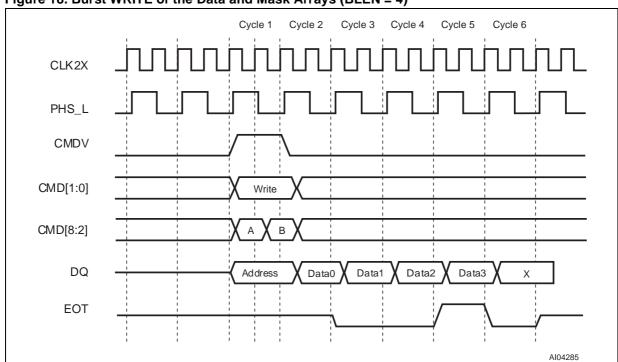

| Burst WRITE of the Data and Mask Arrays (BLEN = 4) (Figure 18.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Burst WRITE of the Data and Mask Arrays (BLEN = 4) (Figure 18.)            | 35 |

| (Single) WRITE Address Format for Data and Mask Arrays or SRAM (Table 22.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (Single) WRITE Address Format for Data and Mask Arrays or SRAM (Table 22.) | 35 |

| WRITE Address Format for Internal Registers (Table 23.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                            |    |

| WRITE Address Format for Data and Mask Array (Burst Write) (Table 24.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | WRITE Address Format for Data and Mask Array (Burst Write) (Table 24.)     | 36 |

# M7020R

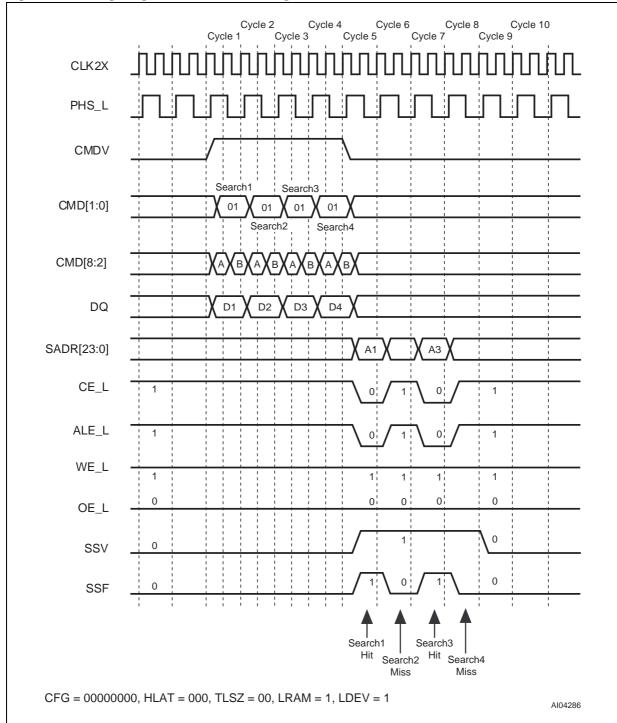

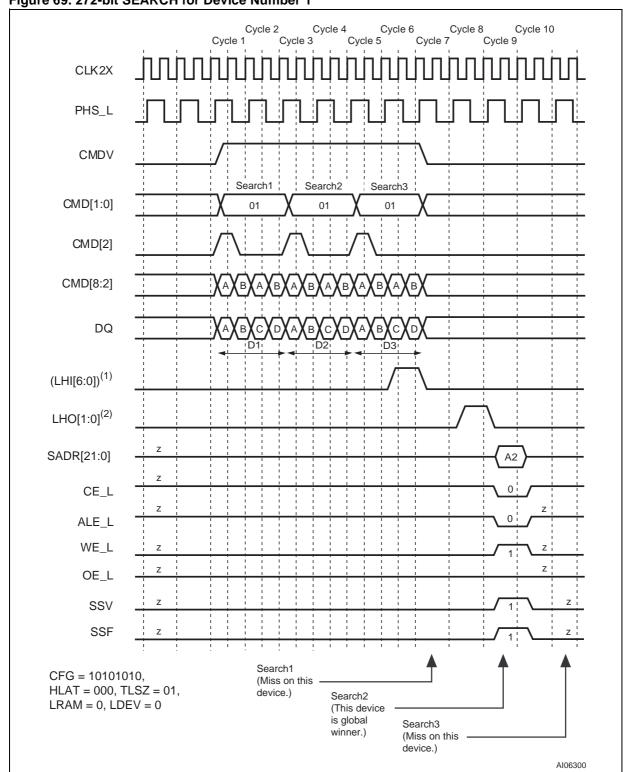

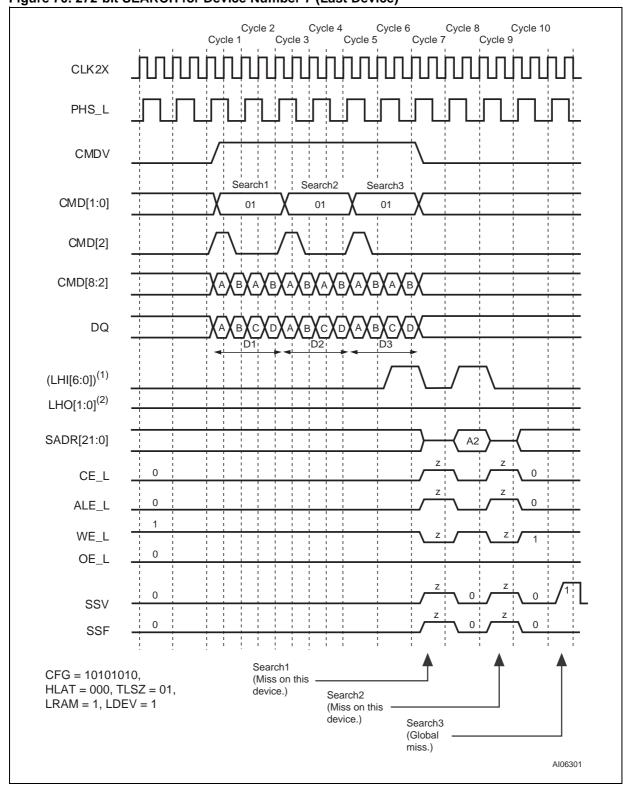

| SE | ARCH COMMAND                                                                                | . 36 |

|----|---------------------------------------------------------------------------------------------|------|

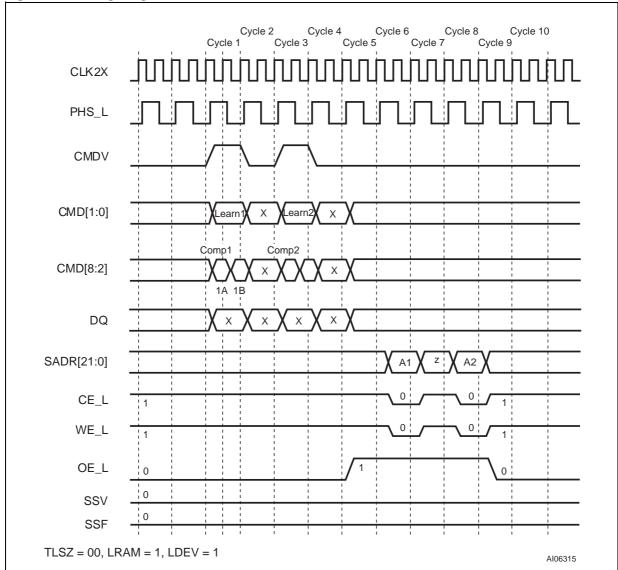

|    | 68-bit Configuration with Single Device                                                     | . 36 |

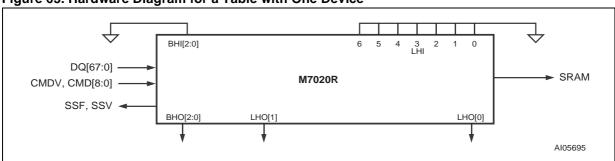

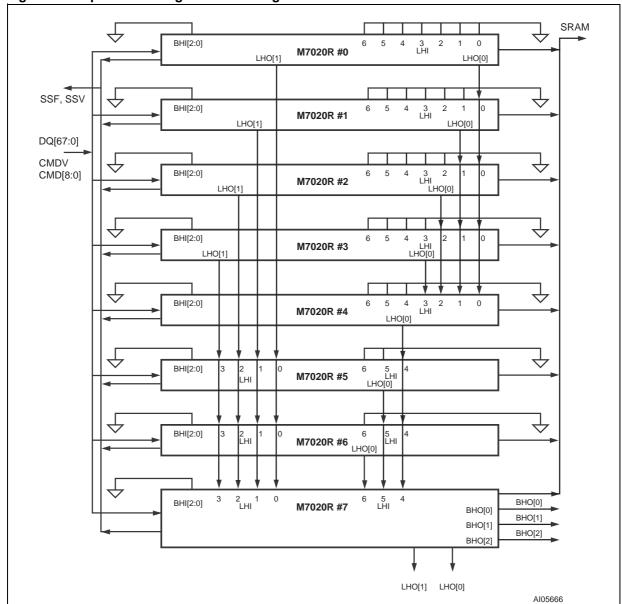

|    | Hardware Diagram for a Table with One Device (Figure 19.)                                   | . 37 |

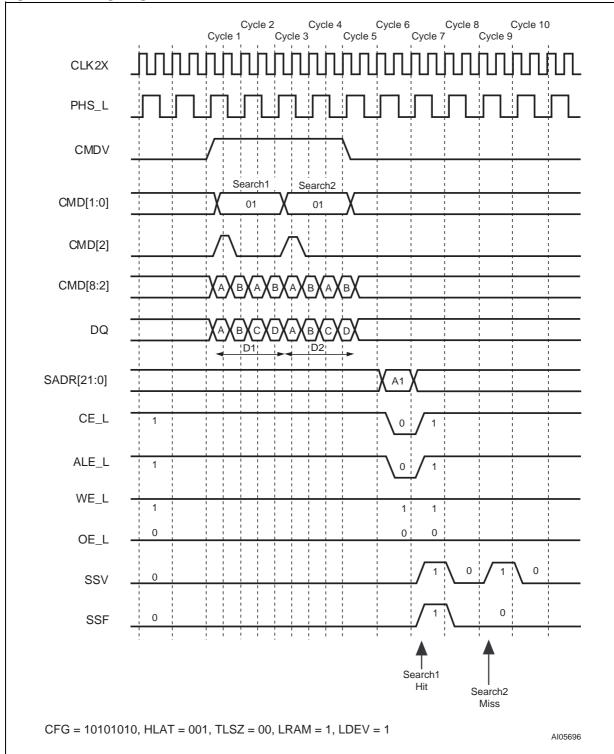

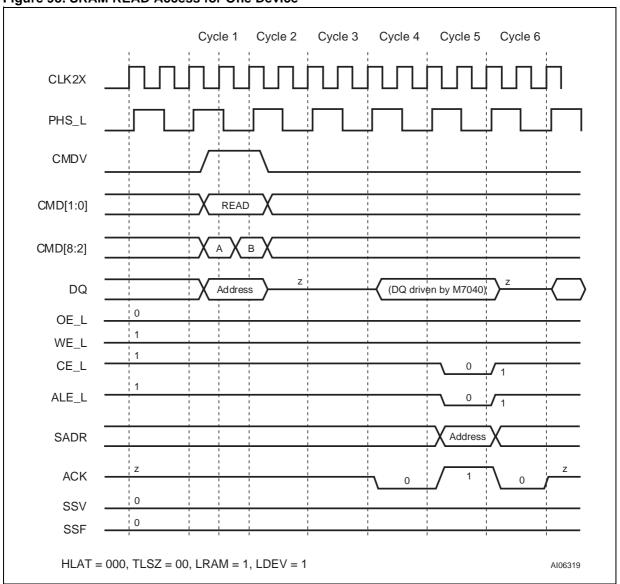

|    | Timing Diagram for a 68-bit Configuration SEARCH for One Device (Figure 20.)                |      |

|    | x68 Table with One Device (Figure 21.)                                                      | . 39 |

|    | Latency of SEARCH from Instruction to SRAM Access Cycle, 68-bit, 1 Device (Table 25.)       | . 39 |

|    | Shift of SSF and SSV from SADR (Table 26.)                                                  | . 39 |

|    | 68-bit SEARCH on Tables Configured as x68 Using up to Eight M7020R Devices                  | . 40 |

|    | Hit/Miss Assumption (Table 27.)                                                             |      |

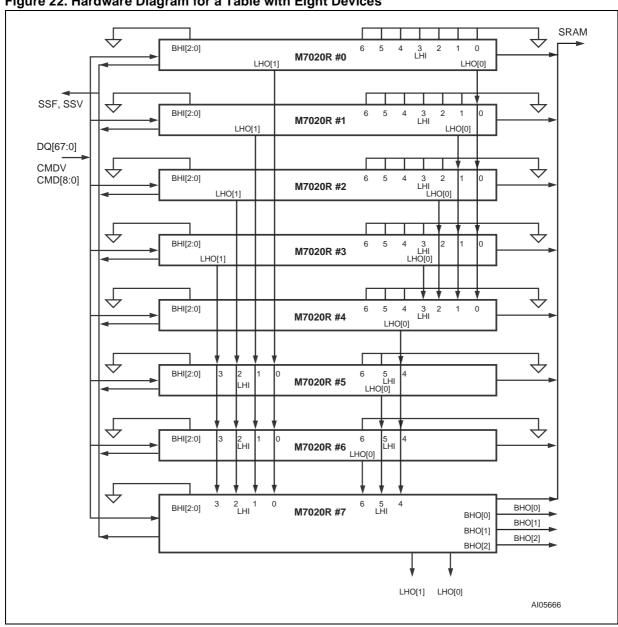

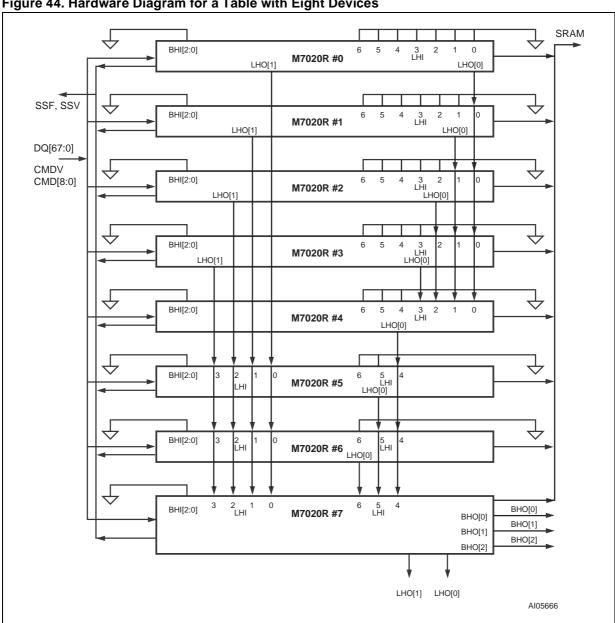

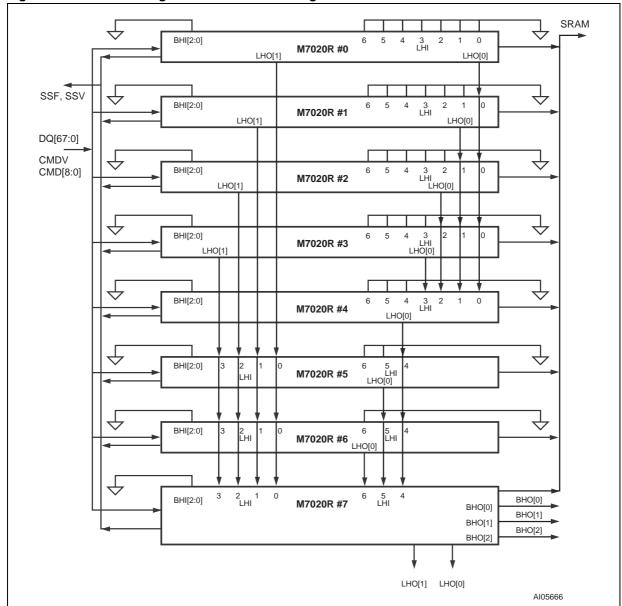

|    | Hardware Diagram for a Table with Eight Devices (Figure 22.)                                | . 41 |

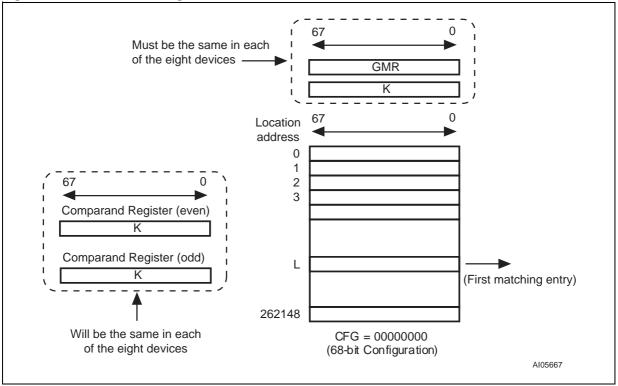

|    | x68 Table with Eight Devices (Figure 23.)                                                   | . 42 |

|    | Timing Diagrams for x68 Using up to Eight M7020R Devices                                    | . 43 |

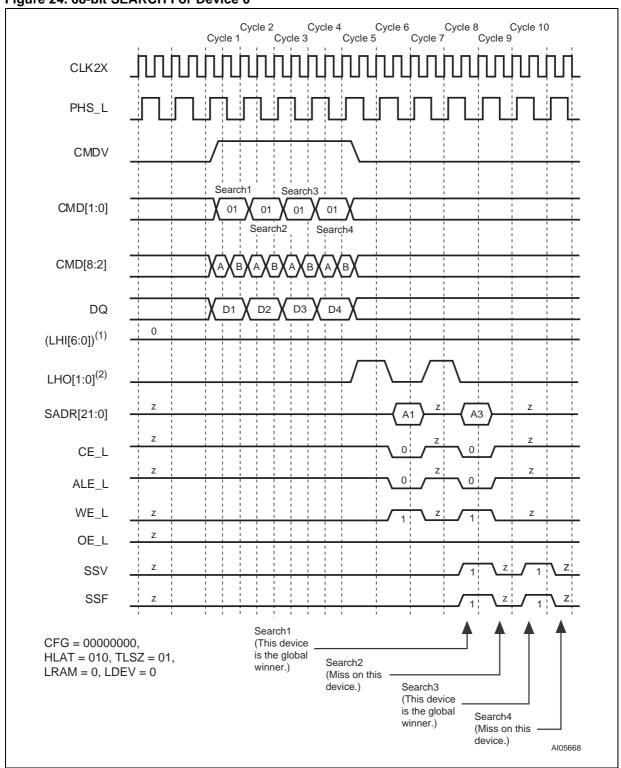

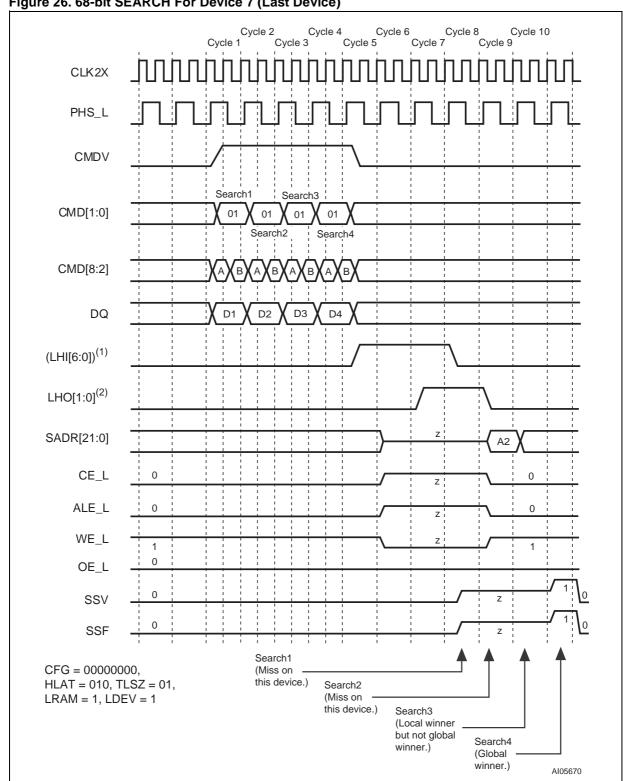

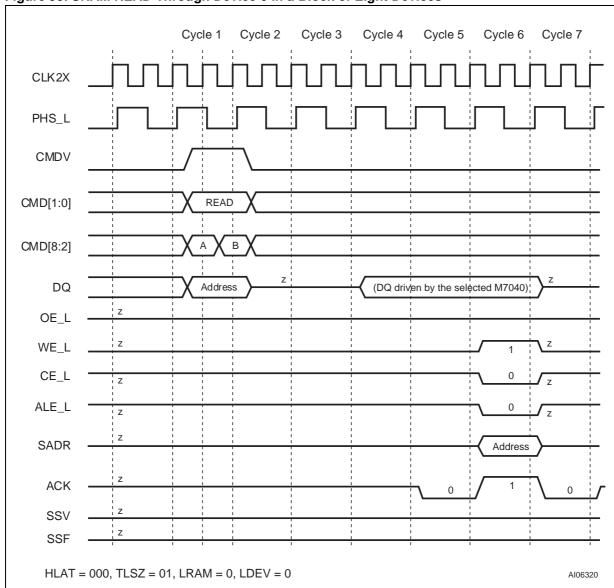

|    | 68-bit SEARCH For Device 0 (Figure 24.)                                                     | . 43 |

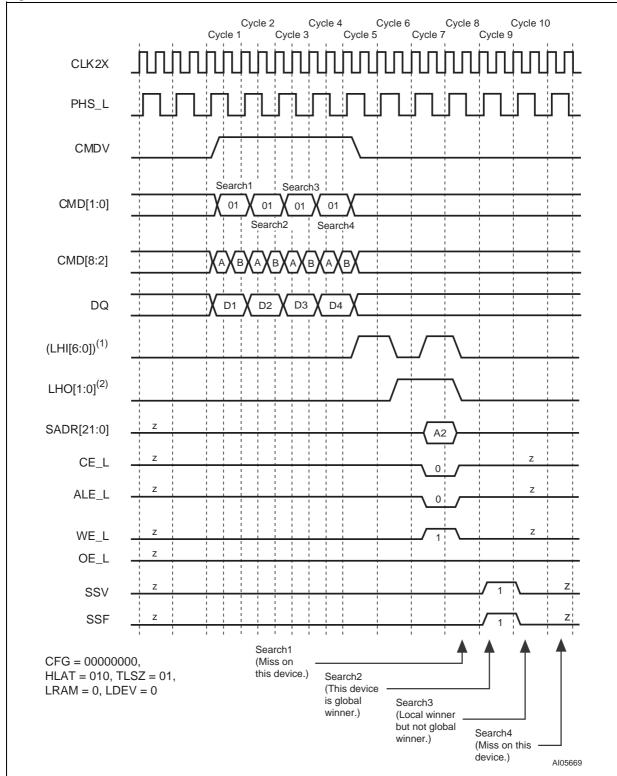

|    | 68-bit SEARCH For Device 1 (Figure 25.)                                                     | . 44 |

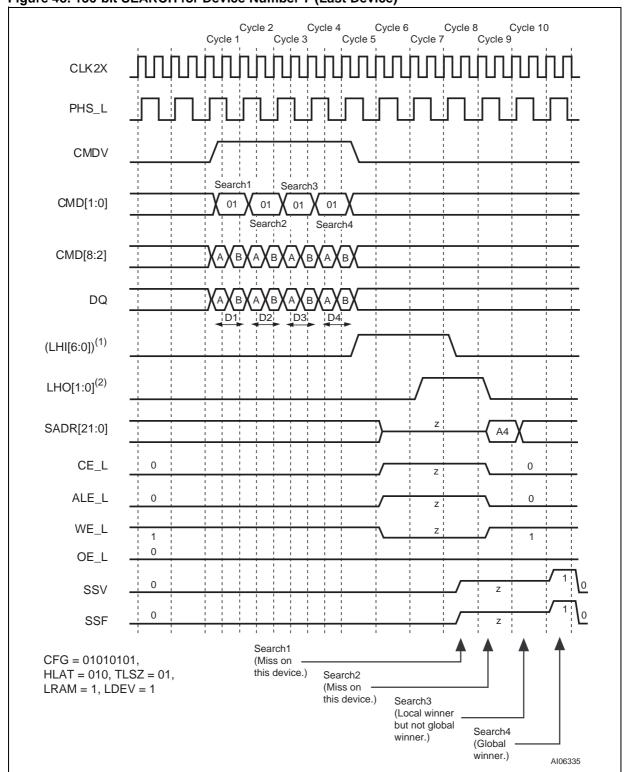

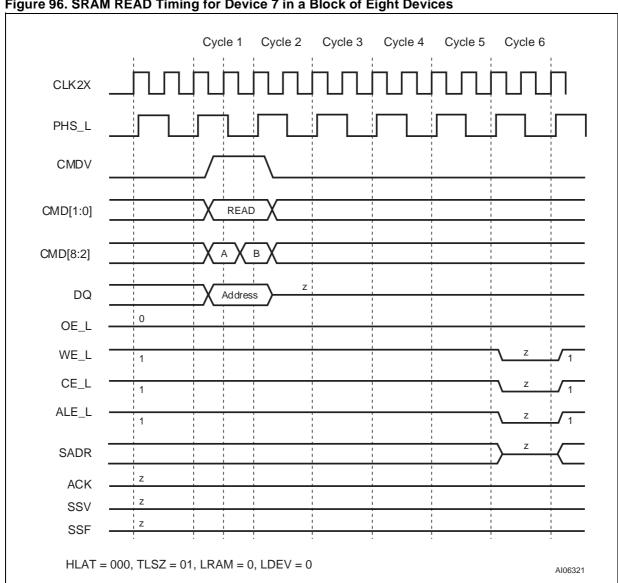

|    | 68-bit SEARCH For Device 7 (Last Device) (Figure 26.)                                       | . 45 |

|    | Latency of SEARCH from Instruction to SRAM Access Cycle, 68-bit, Up to 8 Devices (Table 28. | ) 46 |

|    | Shift of SSF and SSV from SADR (Table 29.)                                                  | . 46 |

|    | 68-bit SEARCH on Tables Configured as x68 Using Up To 31 M7020R Devices                     | . 46 |

|    | Hit/Miss Assumption (Table 30.)                                                             | . 47 |

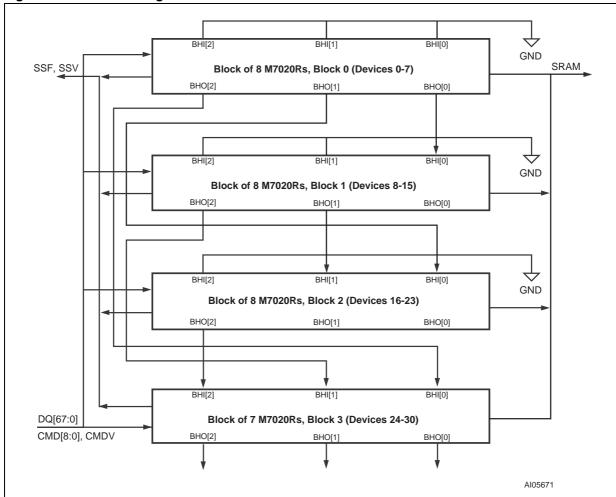

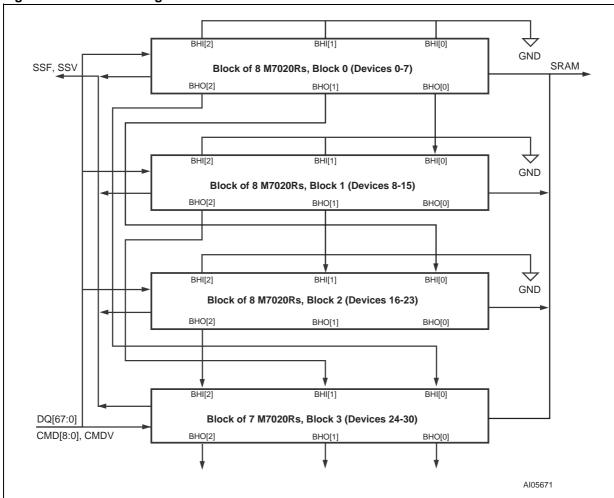

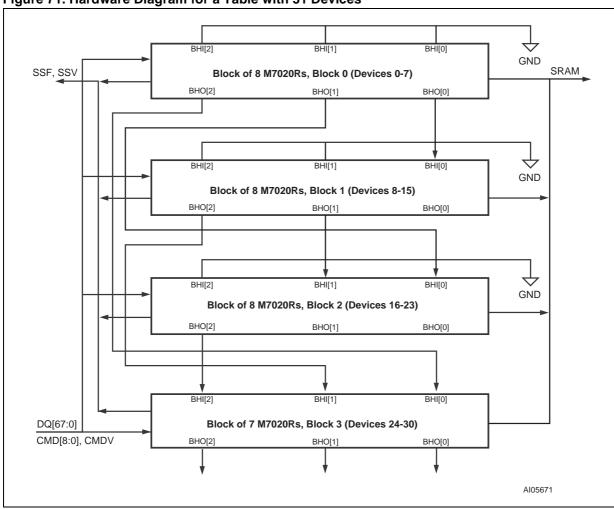

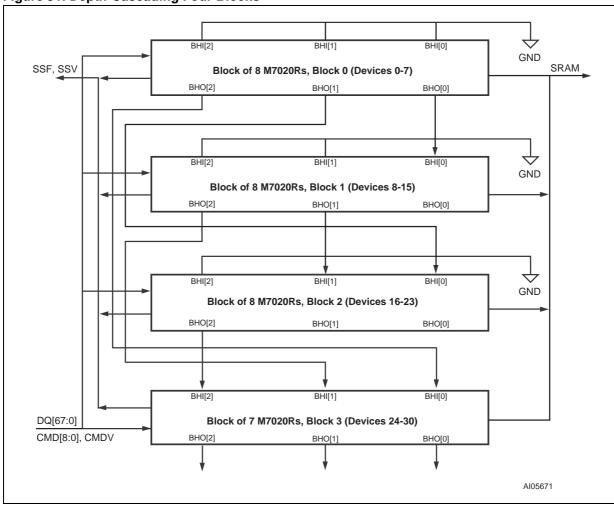

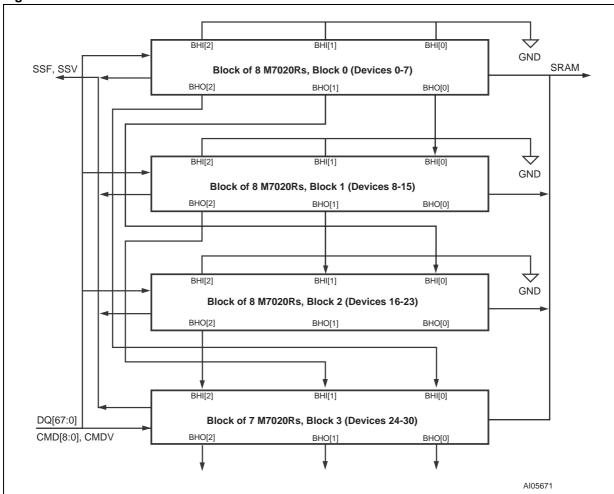

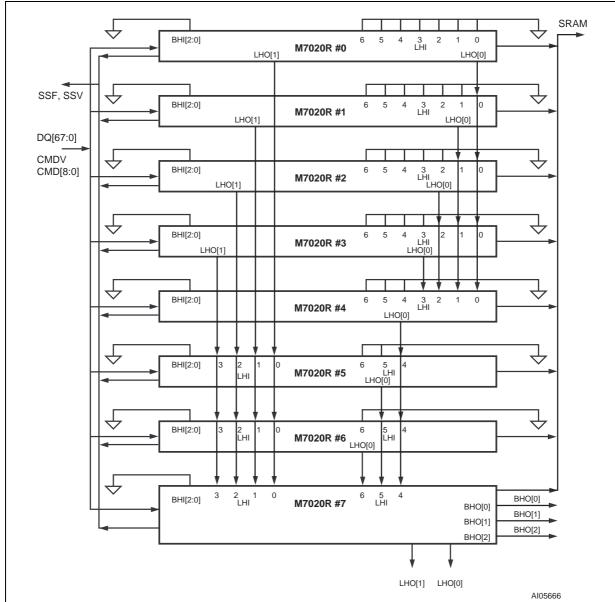

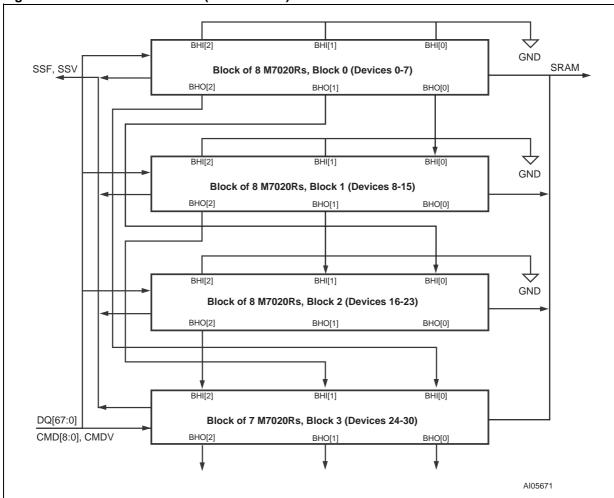

|    | Hardware Diagram for a Table with 31 Devices (Figure 27.)                                   | . 48 |

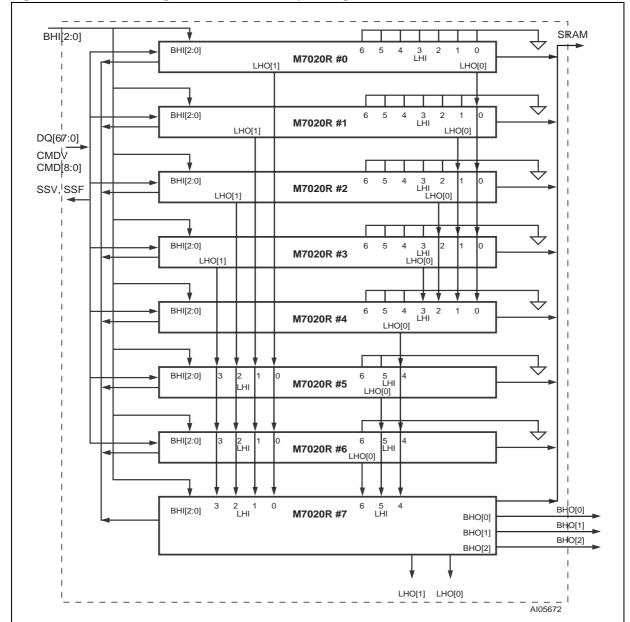

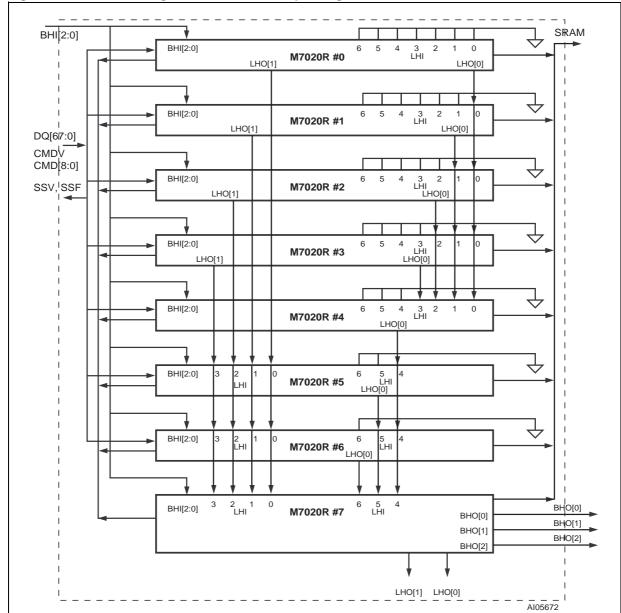

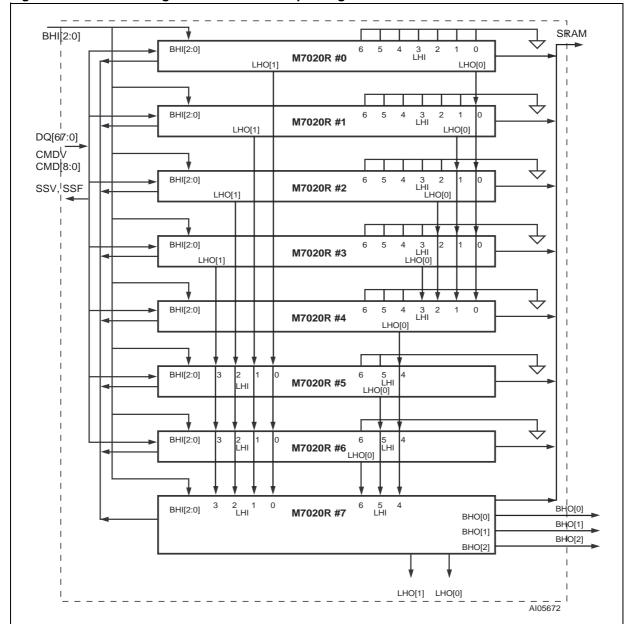

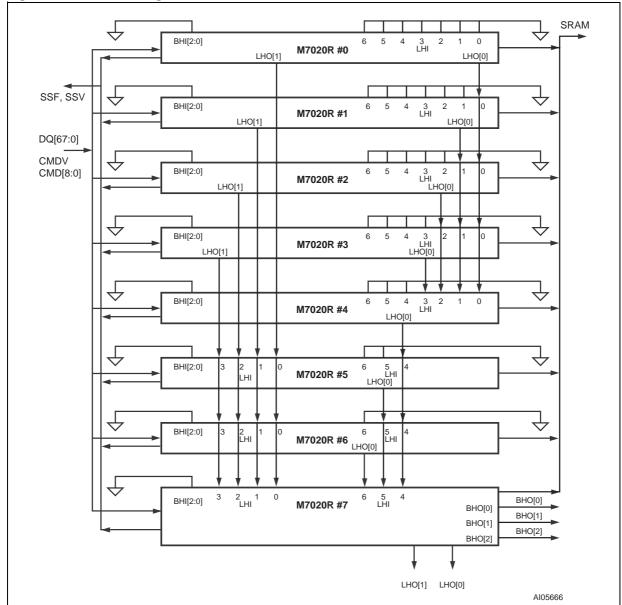

|    | Hardware Diagram for a Block of Up To Eight Devices (Figure 28.)                            | . 49 |

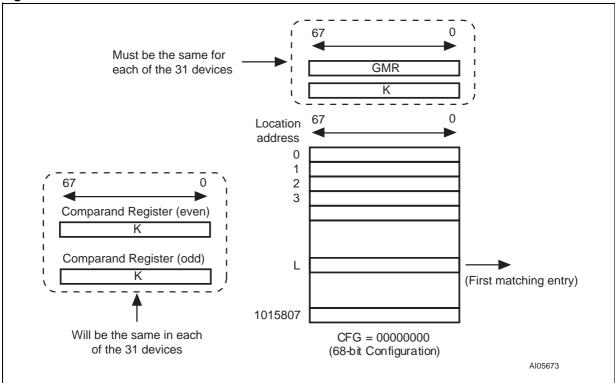

|    | x68 Table with 31 Devices (Figure 29.)                                                      | . 50 |

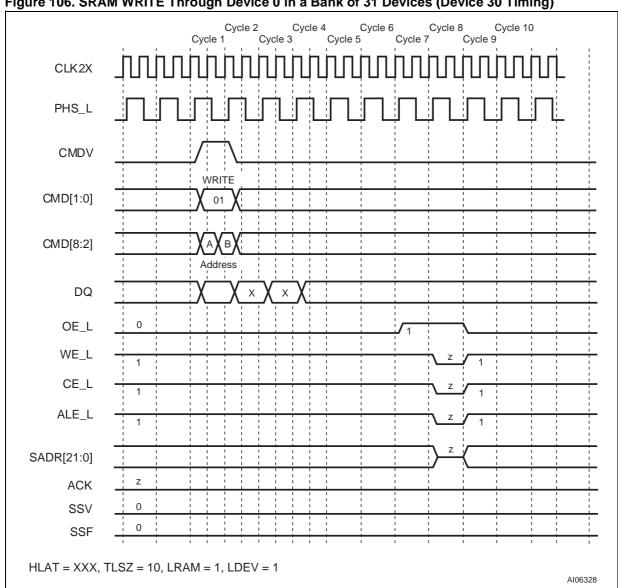

|    | Timing Diagrams for x68 Using Up To 31 M7020R Devices                                       | . 51 |

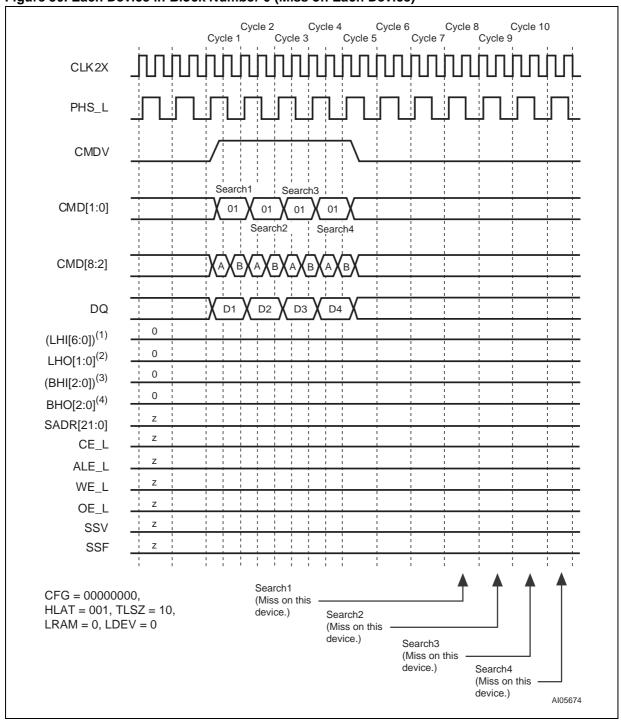

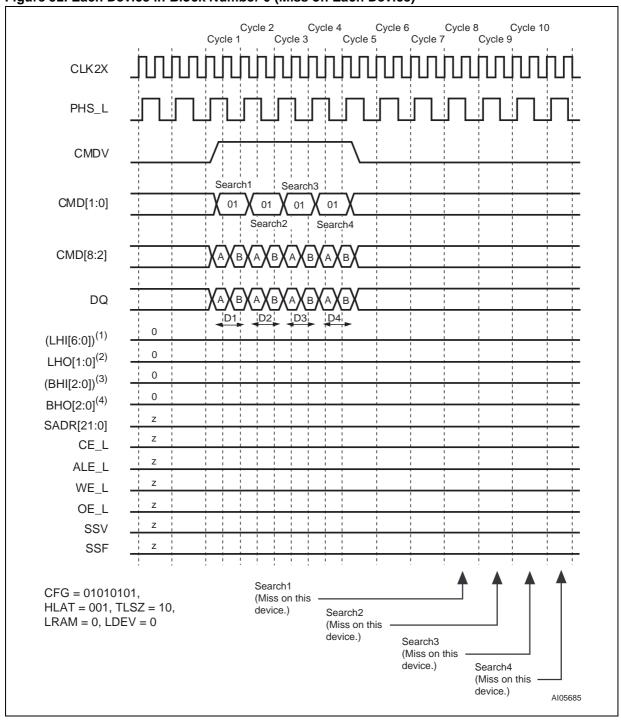

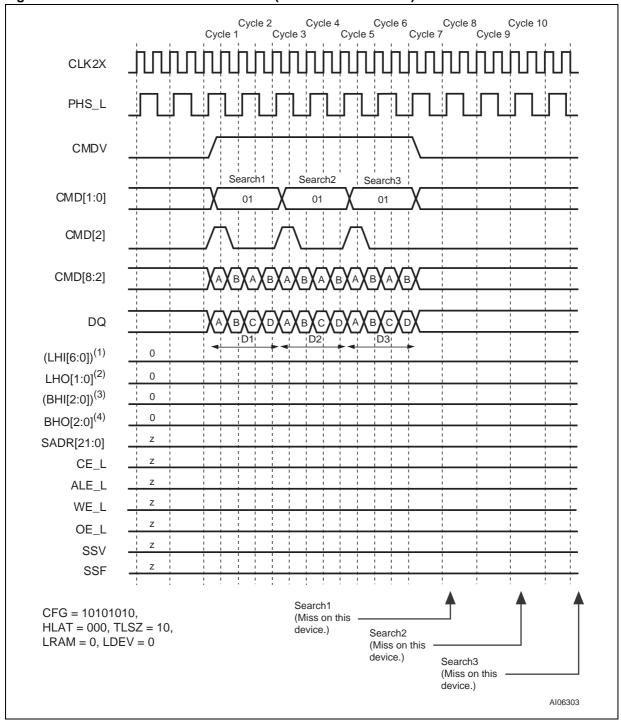

|    | Each Device in Block Number 0 (Miss on Each Device) (Figure 30.)                            | . 51 |

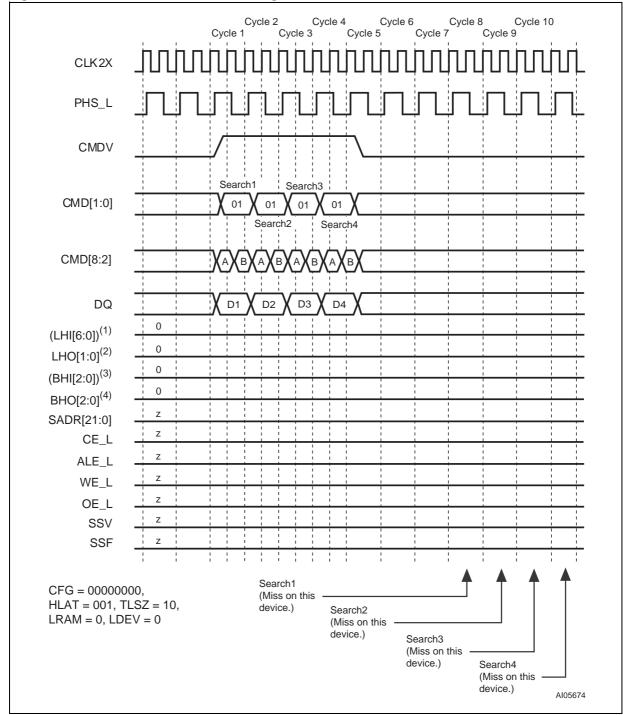

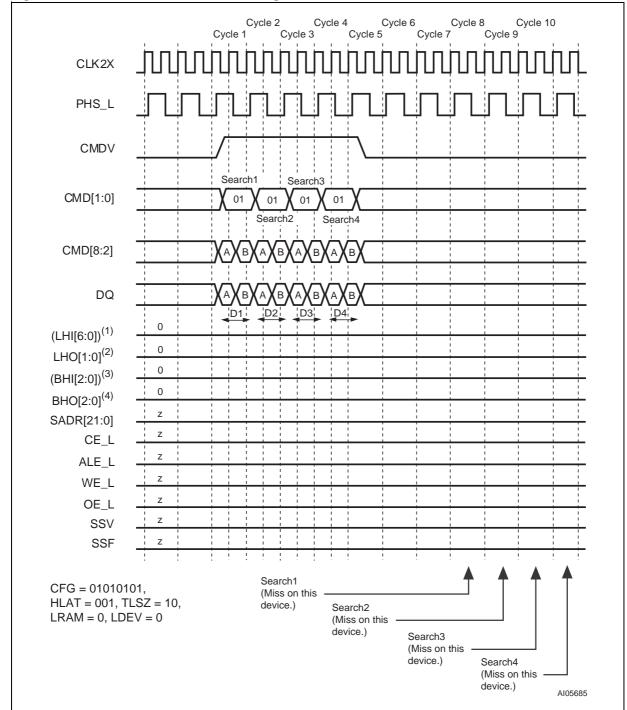

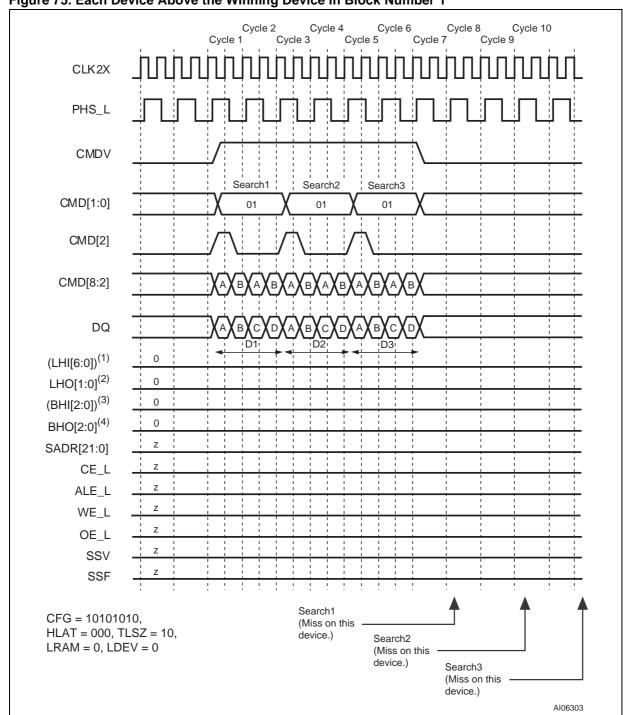

|    | Each Device Above the Winning Device in Block Number 1 (Figure 31.)                         | . 52 |

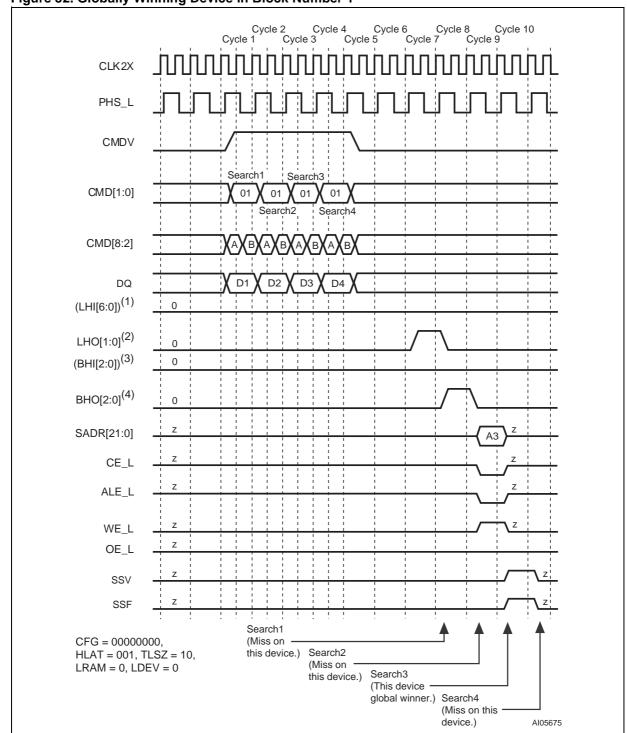

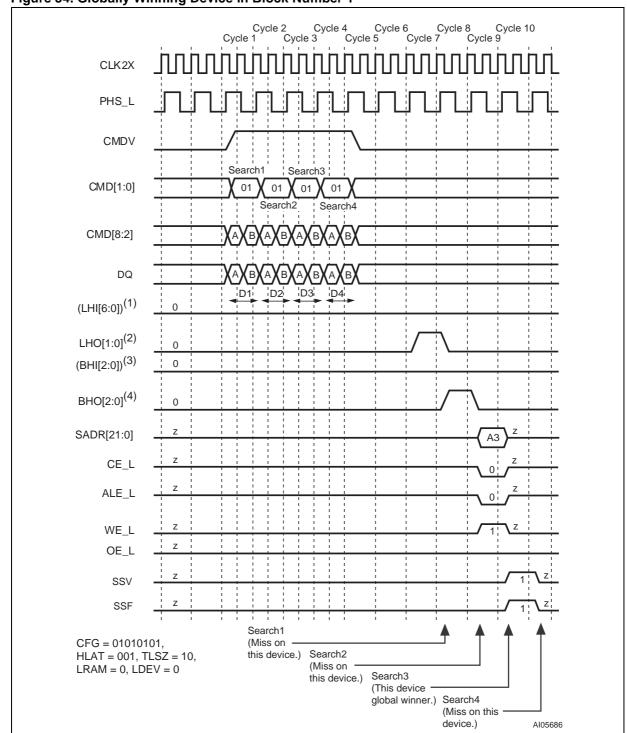

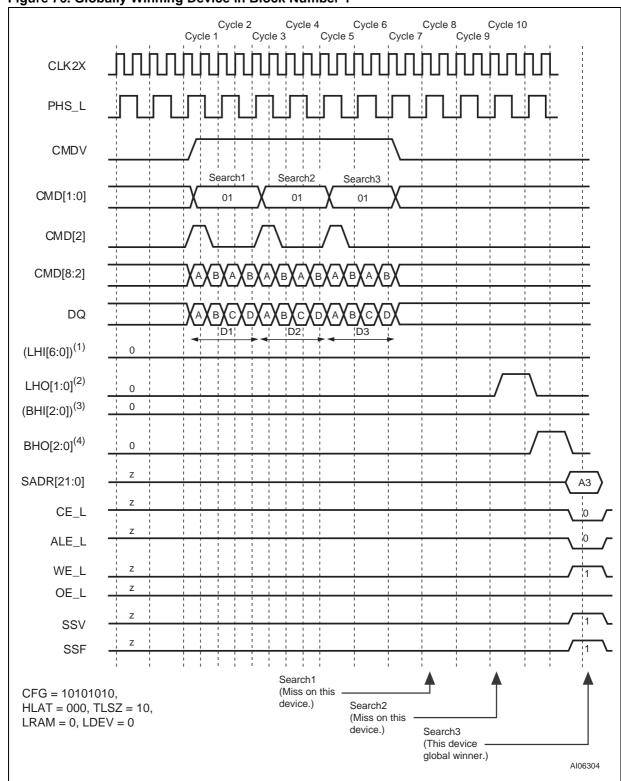

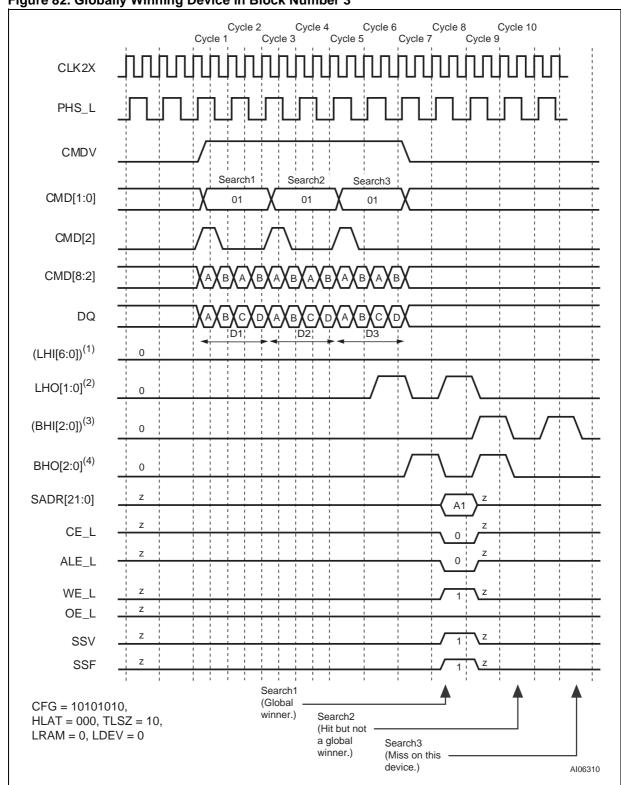

|    | Globally Winning Device in Block Number 1 (Figure 32.)                                      | . 53 |

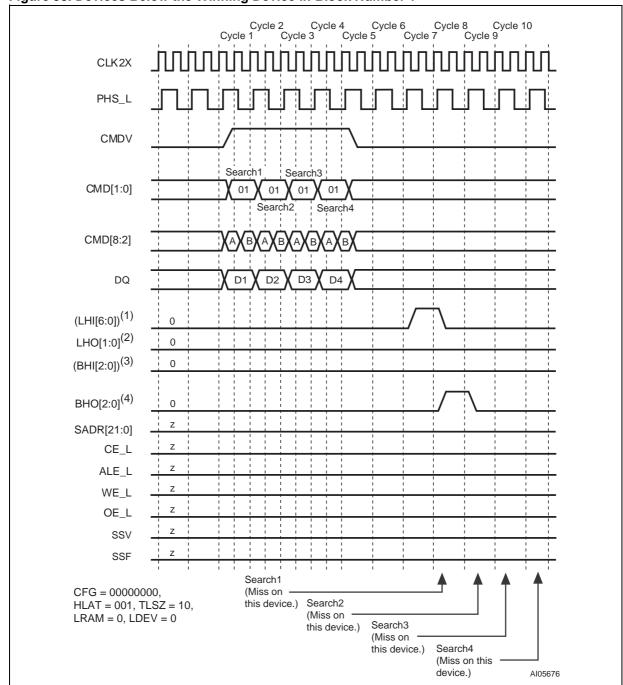

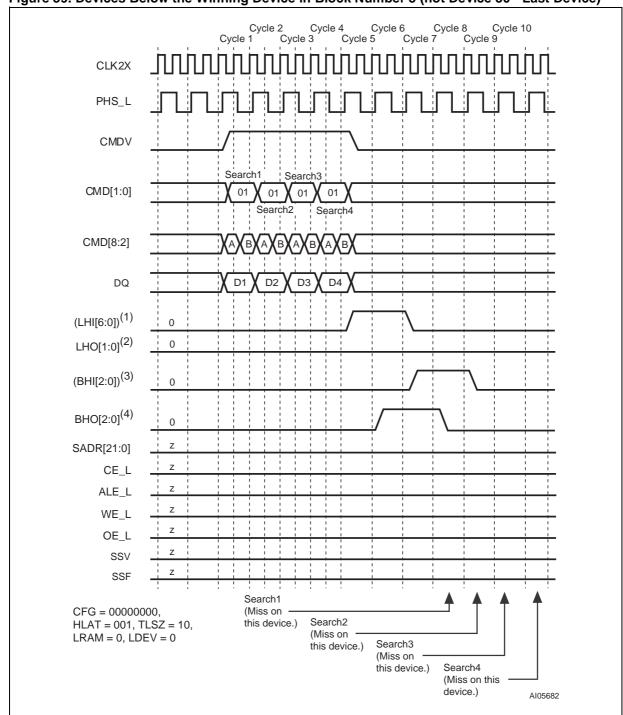

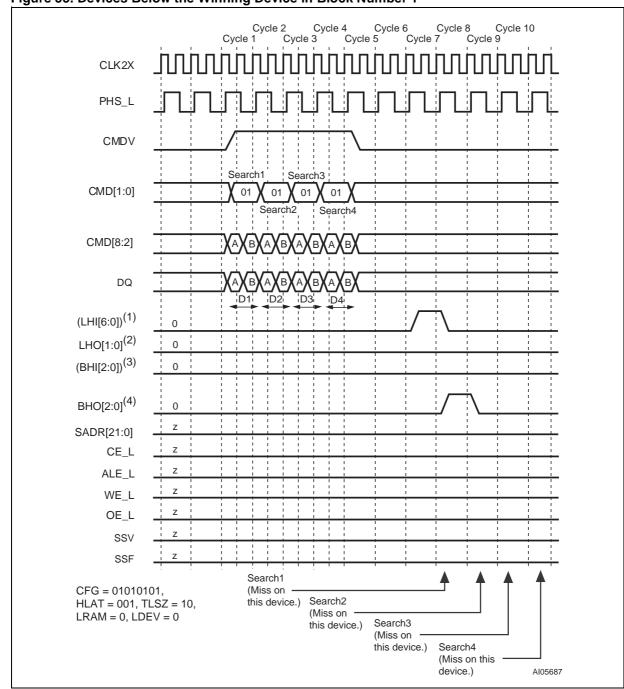

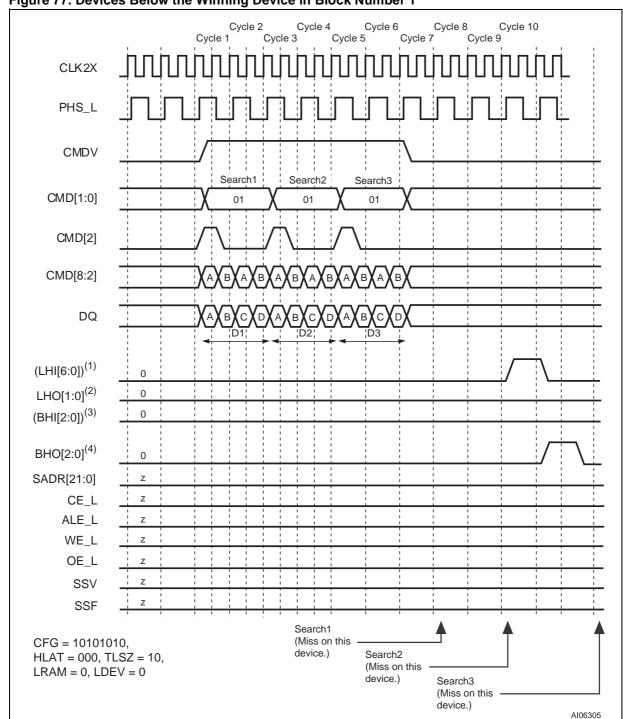

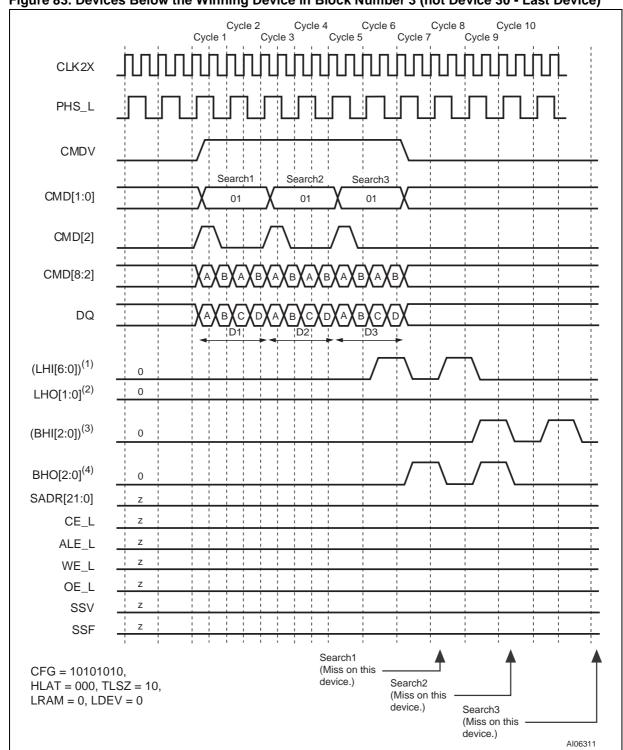

|    | Devices Below the Winning Device in Block Number 1 (Figure 33.)                             | . 54 |

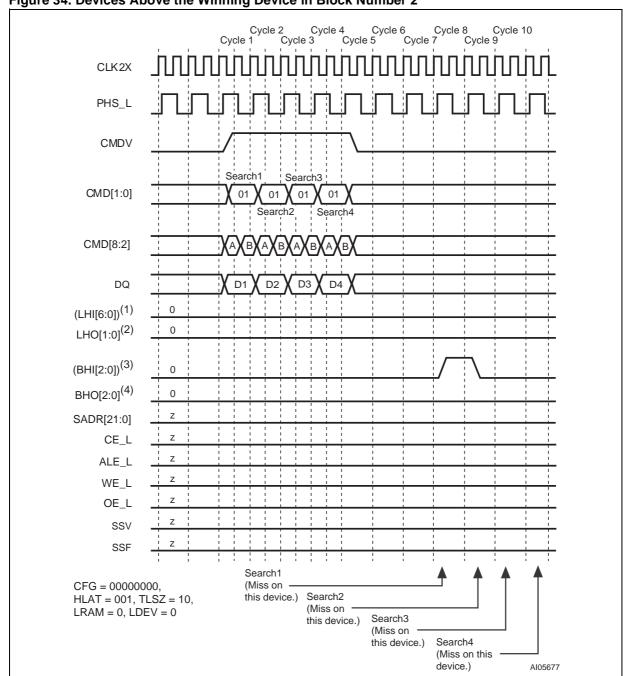

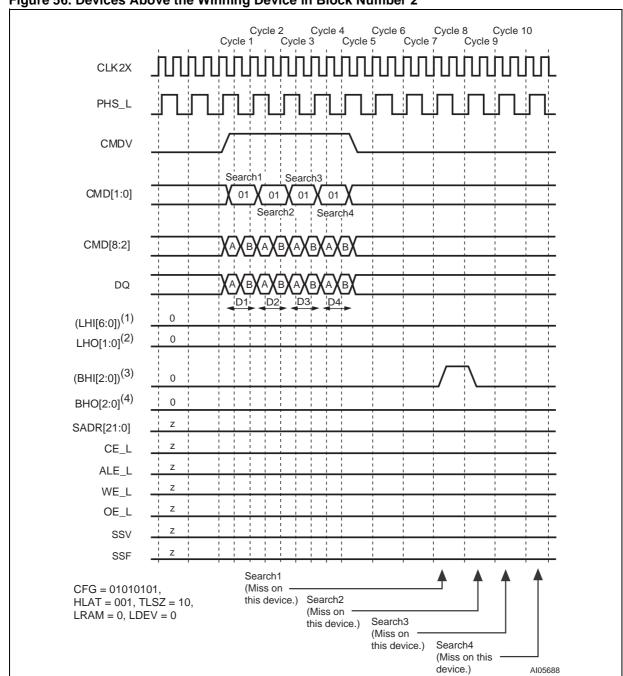

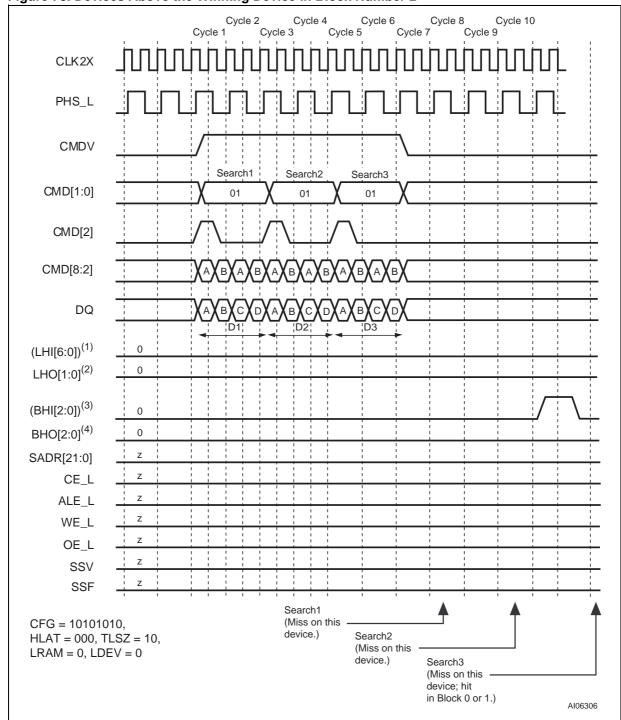

|    | Devices Above the Winning Device in Block Number 2 (Figure 34.)                             | . 55 |

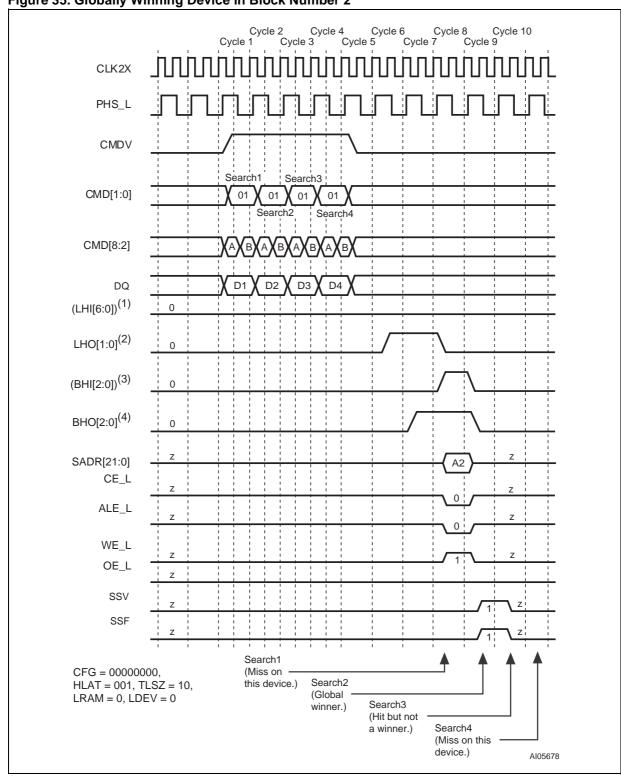

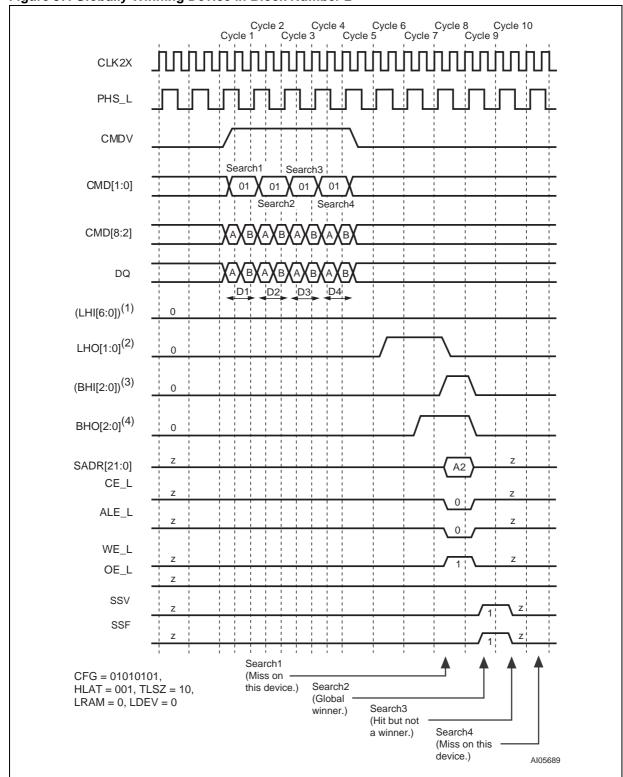

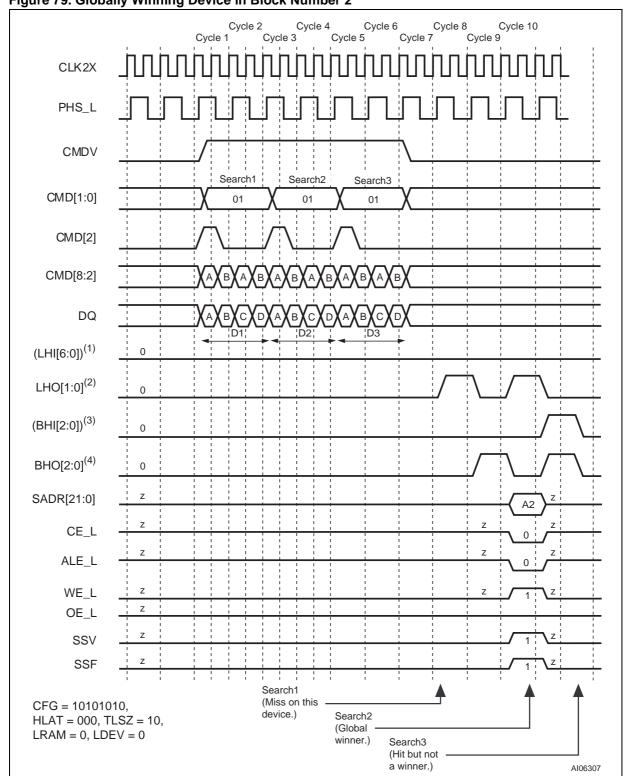

|    | Globally Winning Device in Block Number 2 (Figure 35.)                                      | . 56 |

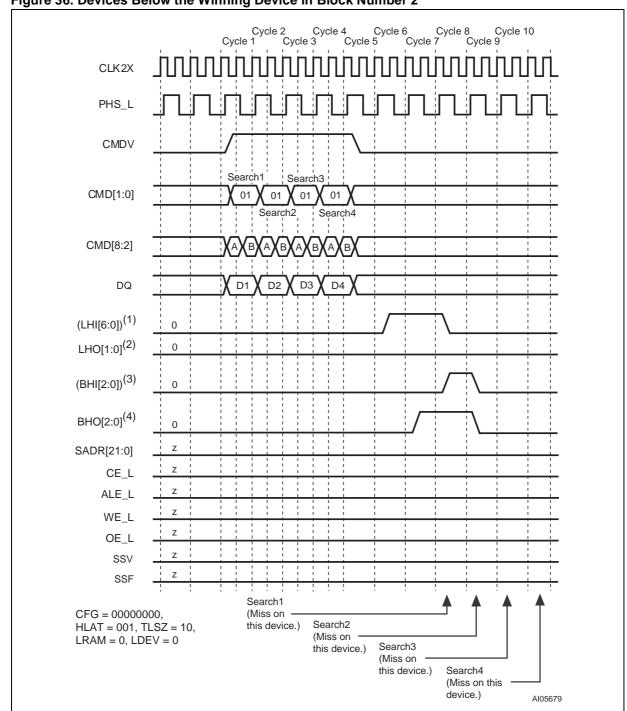

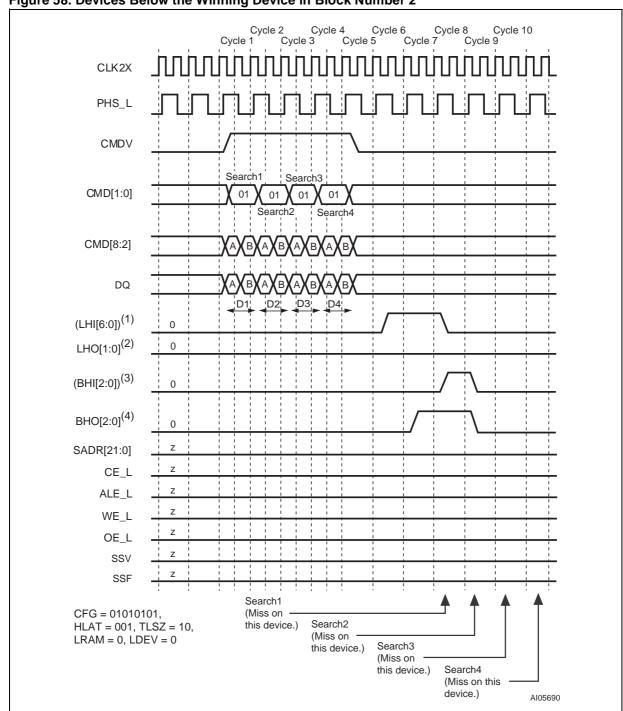

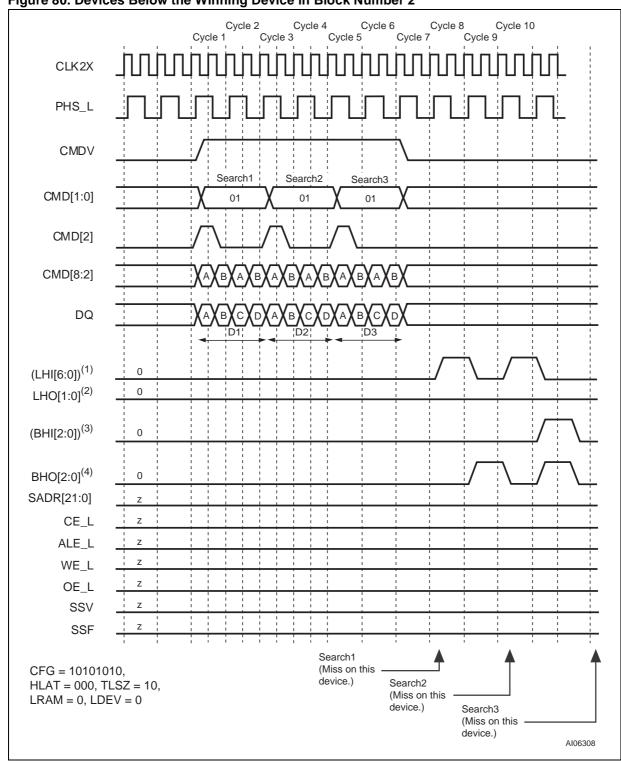

|    | Devices Below the Winning Device in Block Number 2 (Figure 36.)                             | . 57 |

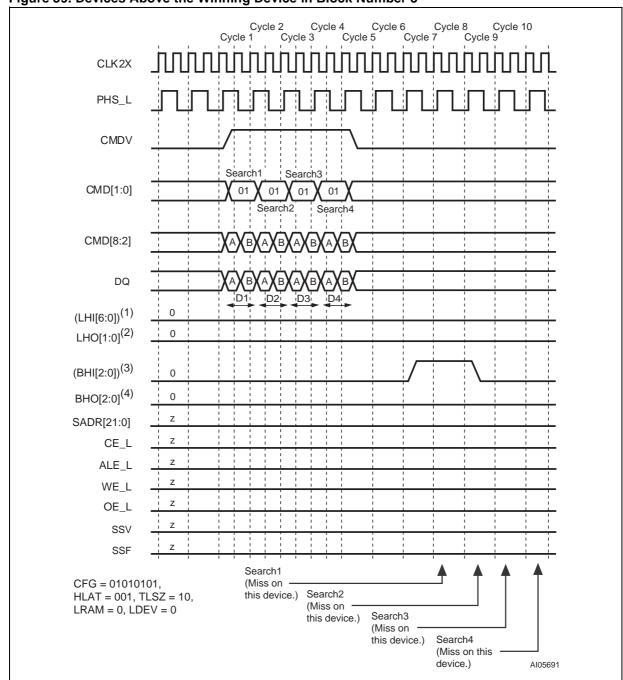

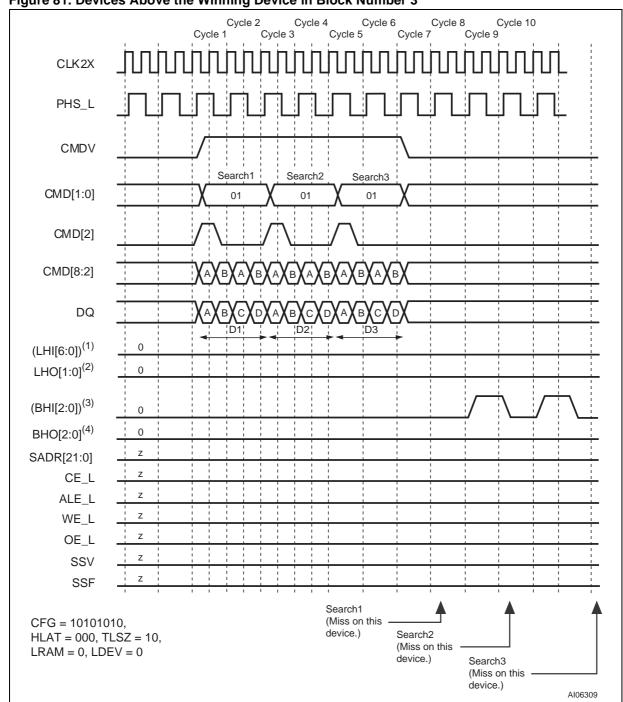

|    | Devices Above the Winning Device in Block Number 3 (Figure 37.)                             | . 58 |

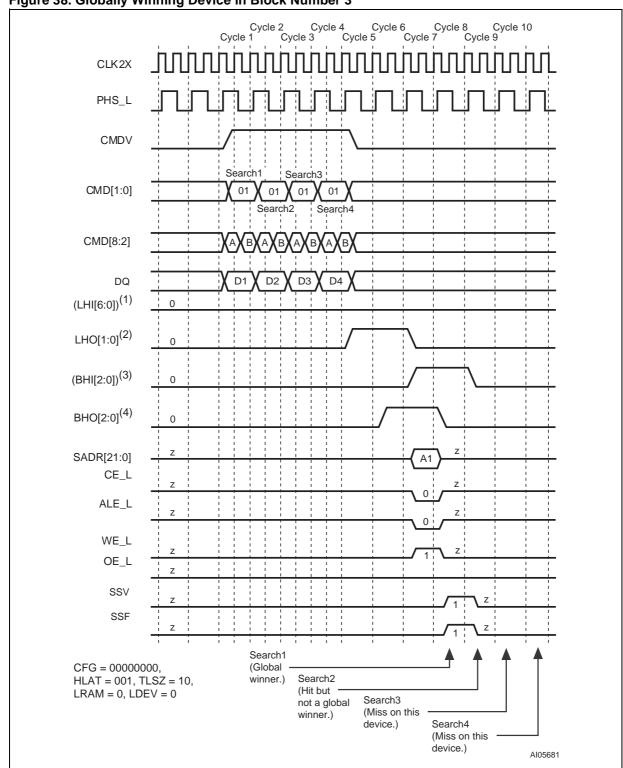

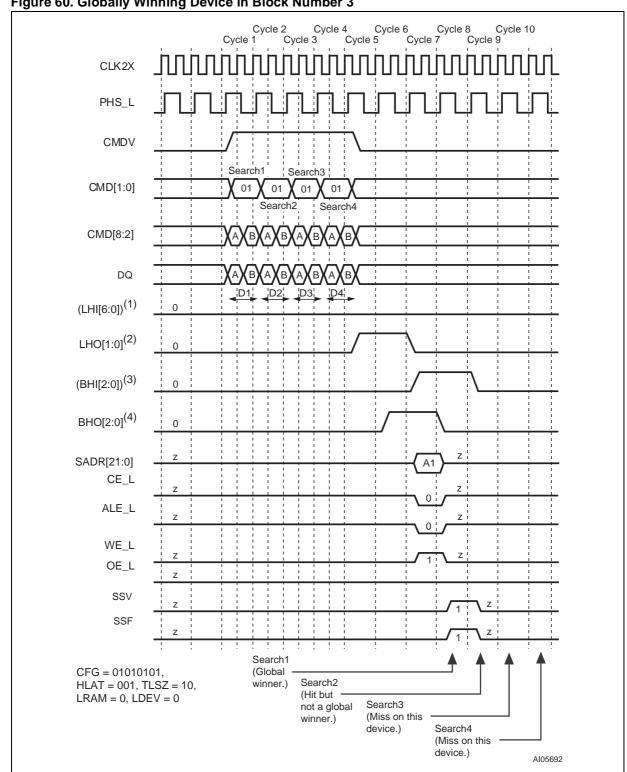

|    | Globally Winning Device in Block Number 3 (Figure 38.)                                      | . 59 |

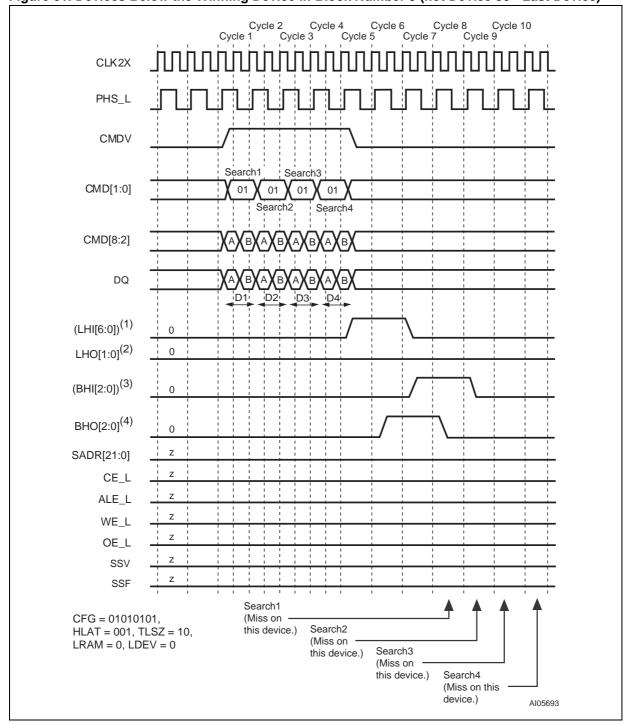

|    | Devices Below the Winning Device in Block Number 3 (not Device 30 - Last Device)            | . 60 |

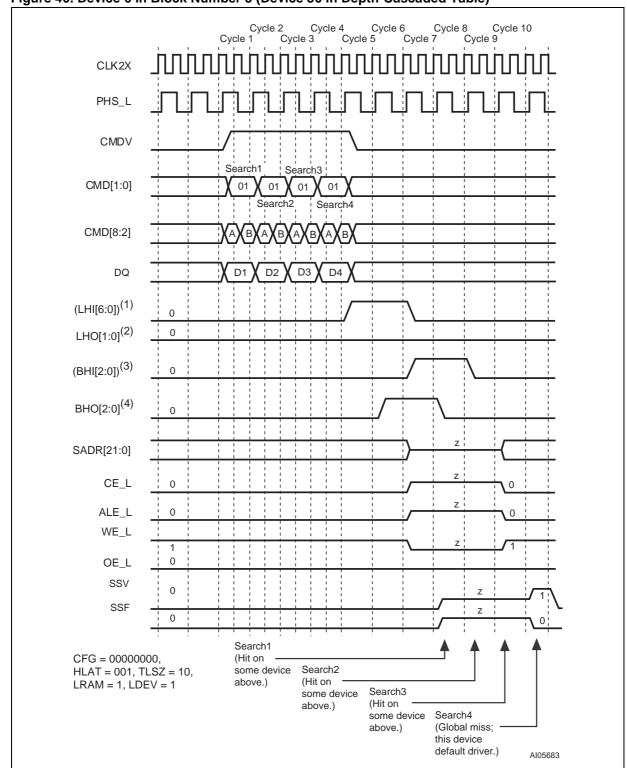

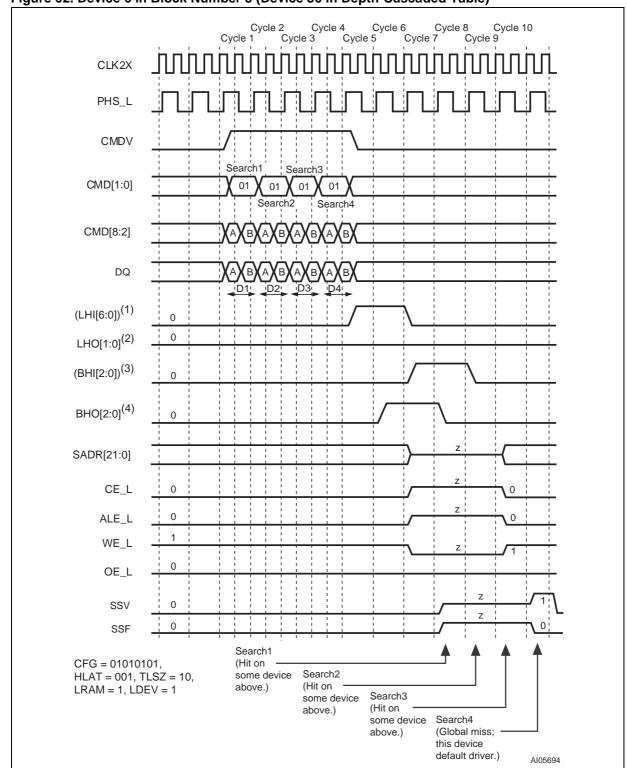

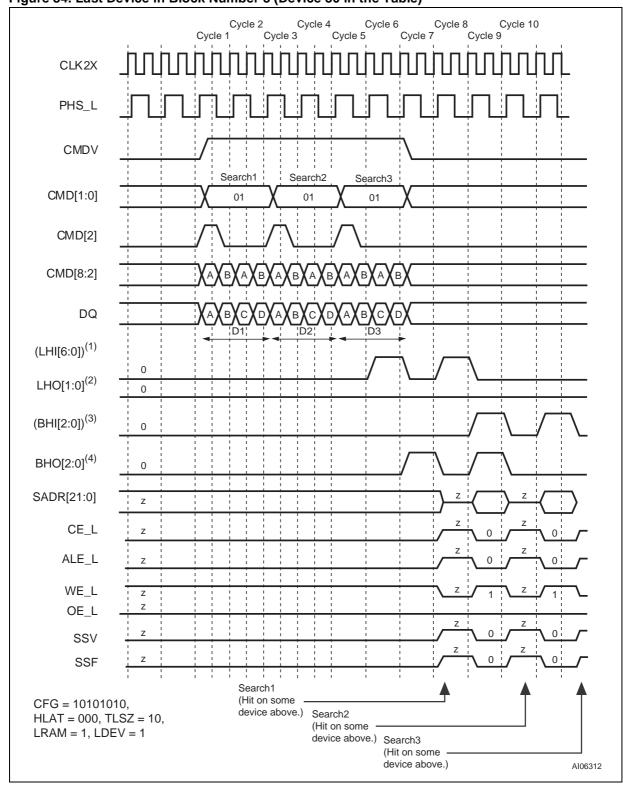

|    | Device 6 in Block Number 3 (Device 30 in Depth-Cascaded Table) (Figure 40.)                 | . 61 |

|    | Latency of SEARCH from Instruction to SRAM Access Cycle, 68-bit, Up to 31 Devices           | . 62 |

|    | Shift of SSF and SSV from SADR (Table 32.)                                                  | . 62 |

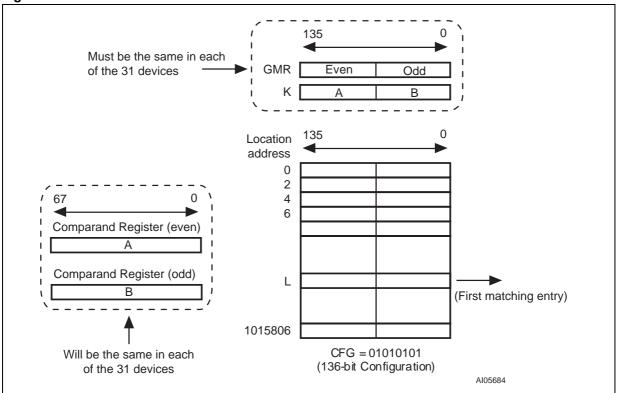

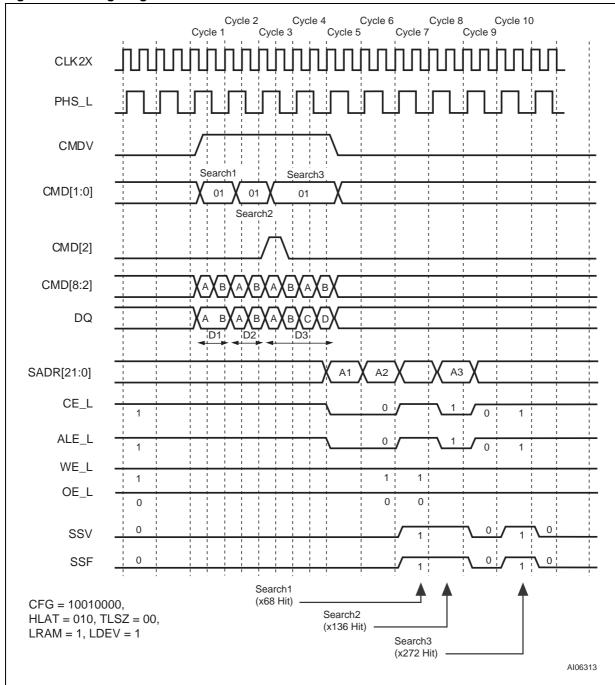

|    | 136-bit Configuration with Single Device                                                    | . 62 |

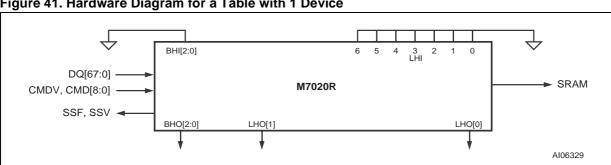

|    | Hardware Diagram for a Table with 1 Device (Figure 41.)                                     | . 63 |

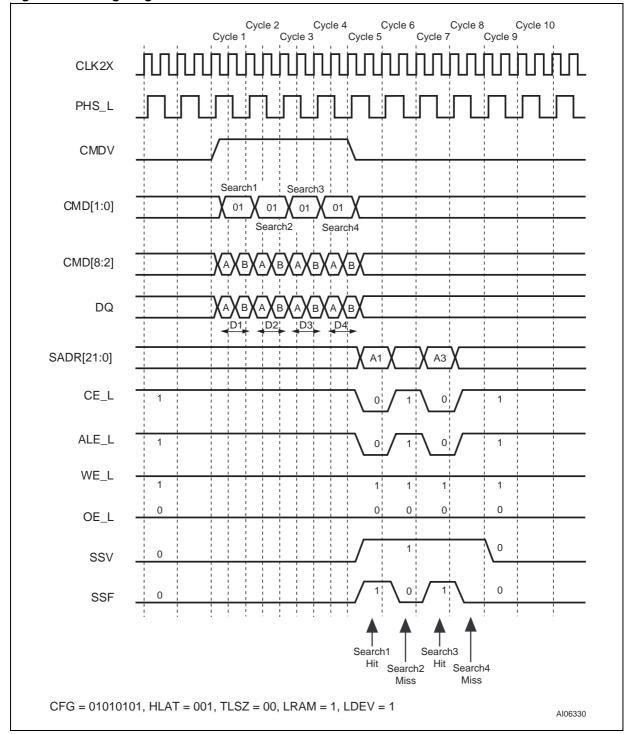

|    | Timing Diagram for a 136-bit SEARCH for One Device (Figure 42.)                             | . 64 |

|    | x136 Table with One Device (Figure 43.)                                                     |      |

|    | Latency of SEARCH from Instruction to SRAM Access Cycle, 136-bit, 1 Device (Table 33.)      | . 65 |

|    | Shift of SSF and SSV from SADR (Table 34.)                                                  |      |

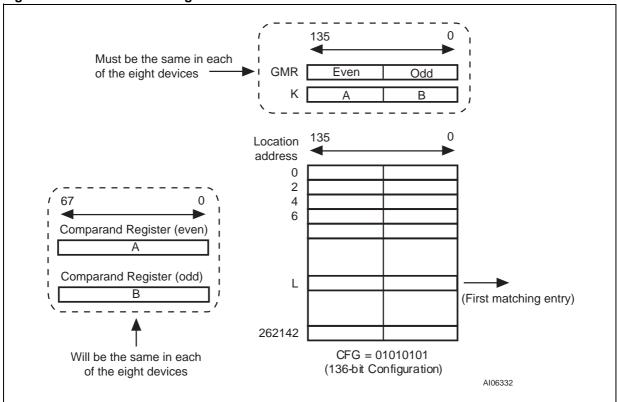

| 136-bit Search on Tables Configured as x136 Using Up to Eight M7020R Devices                                                 | . 66 |

|------------------------------------------------------------------------------------------------------------------------------|------|

| Hit/Miss Assumption (Table 35.)                                                                                              |      |

| Hardware Diagram for a Table with Eight Devices (Figure 44.)                                                                 |      |

| x136 Table with Eight Devices (Figure 45.)                                                                                   |      |

| Timing Diagrams for x136 Using Up to Eight M7020R Devices                                                                    |      |

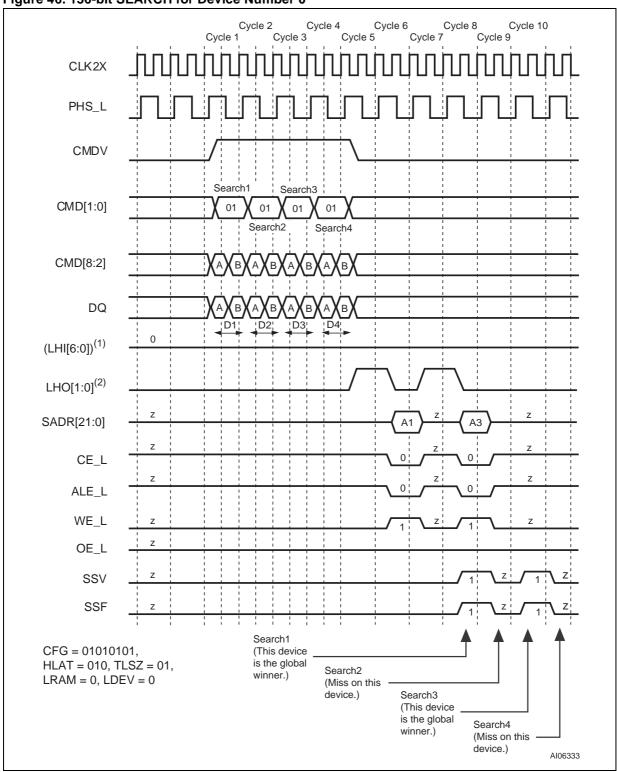

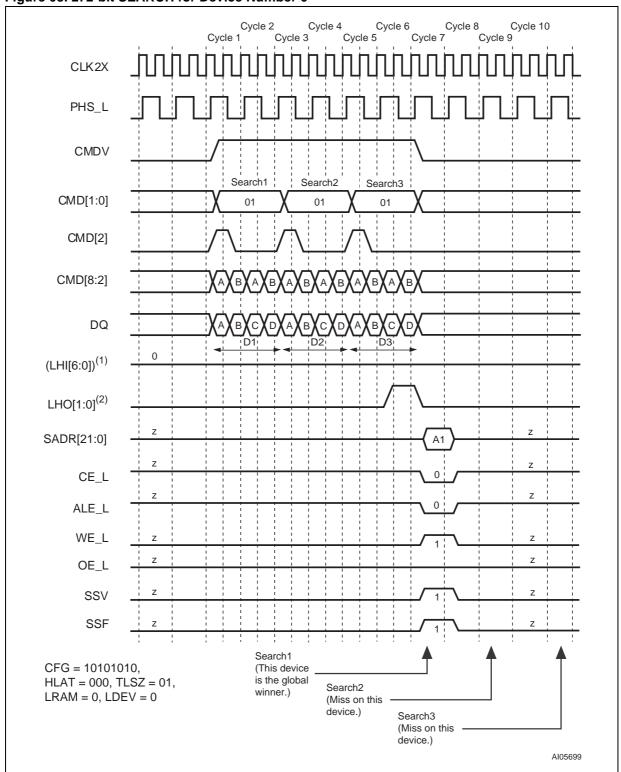

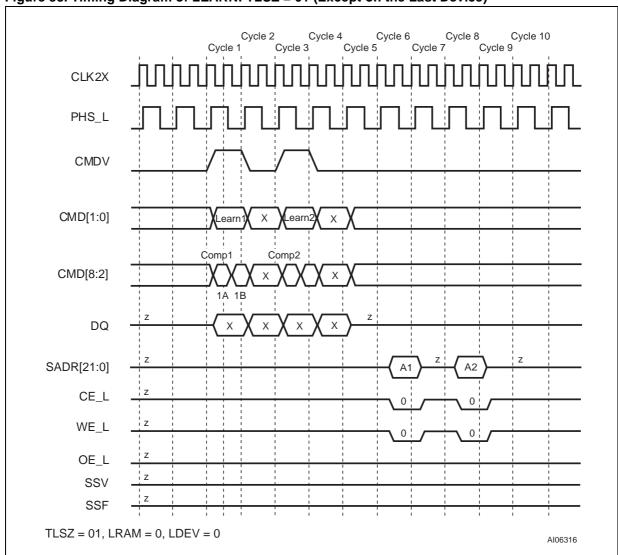

| 136-bit SEARCH for Device Number 0 (Figure 46.)                                                                              |      |

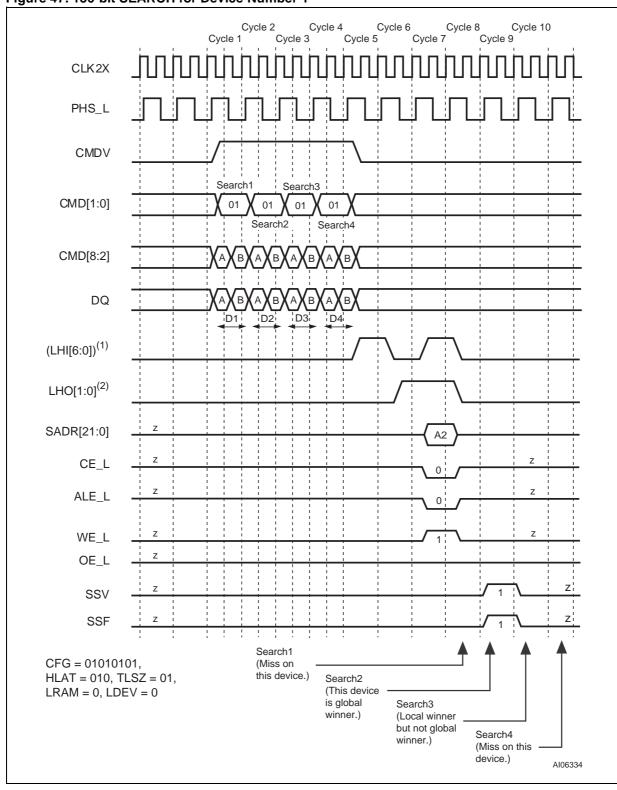

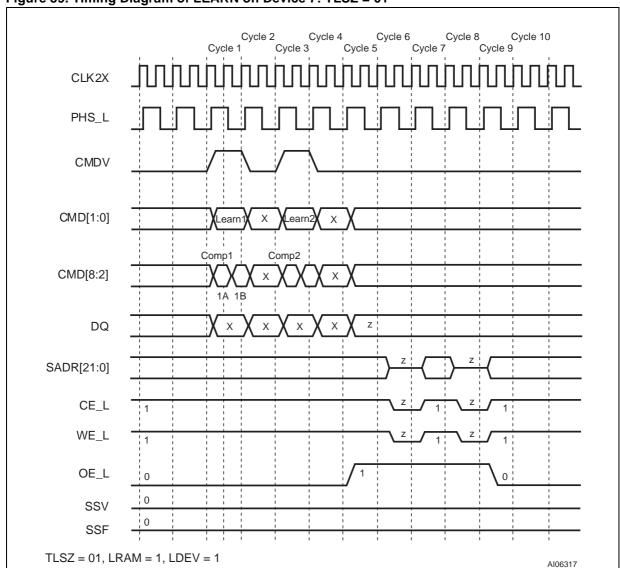

| 136-bit SEARCH for Device Number 1 (Figure 47.)                                                                              |      |

| 136-bit SEARCH for Device Number 7 (Last Device) (Figure 48.)                                                                |      |

| Latency of SEARCH from Instruction to SRAM Access Cycle, 136-bit, Up to 8 Devices Shift of SSF and SSV from SADR (Table 37.) |      |

|                                                                                                                              |      |

| 136-bit Search on Tables Configured as x136 Using Up to 31 M7020R Devices                                                    |      |

| Hit/Miss Assumption (Table 38.)                                                                                              |      |

| Hardware Diagram for a Table with 31 Devices (Figure 49.)                                                                    |      |

| Hardware Diagram for a Block of Up to Eight Devices (Figure 50.)                                                             |      |

| x136 Table with 31 Devices (Figure 51.)                                                                                      |      |

| Timing Diagrams for x136 Using Up to 31 M7020R Devices                                                                       |      |

| Each Device in Block Number 0 (Miss on Each Device) (Figure 52.)                                                             |      |

| Each Device Above the Winning Device in Block Number 1 (Figure 53.)                                                          |      |

| Globally Winning Device in Block Number 1 (Figure 54.)                                                                       |      |

| Devices Above the Winning Device in Block Number 2 (Figure 56.)                                                              |      |

| Globally Winning Device in Block Number 2 (Figure 57.)                                                                       |      |

| Devices Below the Winning Device in Block Number 2 (Figure 58.)                                                              |      |

| Devices Above the Winning Device in Block Number 3 (Figure 59.)                                                              |      |