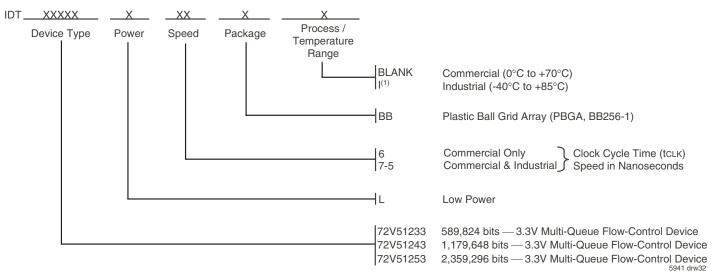

## 3.3V MULTI-QUEUE FLOW-CONTROL DEVICES (4 QUEUES) 18 BIT WIDE CONFIGURATION

589,824 bits 1,179,648 bits 2,359,296 bits

## IDT72V51233 IDT72V51243 IDT72V51253

## **FEATURES:**

- Choose from among the following memory density options:

- IDT72V51233 Total Available Memory = 589,824 bits

- IDT72V51243 Total Available Memory = 1,179,648 bits

- IDT72V51253 Total Available Memory = 2,359,296 bits

- Configurable from 1 to 4 Queues

- Queues may be configured at master reset from the pool of Total Available Memory in blocks of 512 x 18 or 1,024 x 9

- Independent Read and Write access per queue

- User programmable via serial port

- Default multi-queue device configurations -IDT72V51233: 8,192 x 18 x 4Q or 16,384 x 9 x 4Q -IDT72V51243: 16,384 x 18 x 4Q or 32,768 x 9 x 4Q -IDT72V51253: 32,768 x 18 x 4Q or 65,536 x 9 x 4Q

- 100% Bus Utilization, Read and Write on every clock cycle

- 166 MHz High speed operation (6ns cycle time)

- 3.7ns access time

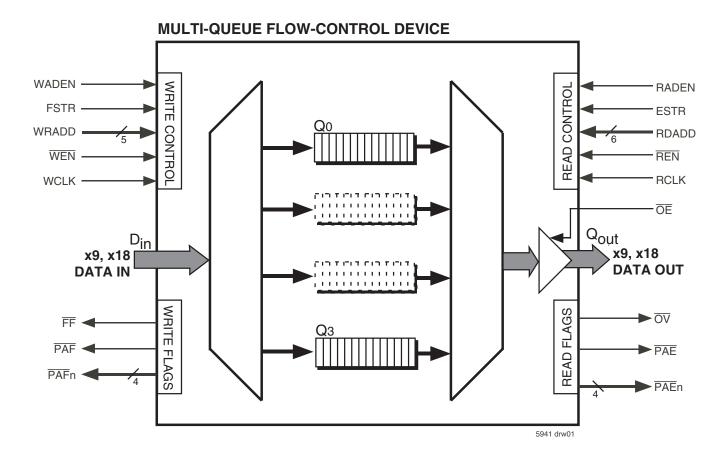

## FUNCTIONAL BLOCK DIAGRAM

- Individual, Active queue flags (OV, FF, PAE, PAF)

- 4 bit parallel flag status on both read and write ports

- Provides continuous PAE and PAF status of up to 4 Queues

- Global Bus Matching (All Queues have same Input Bus Width and Output Bus Width)

- User Selectable Bus Matching Options:

- x18in to x18out

- x9in to x18out

- x18in to x9out

- x9in to x9out

- FWFT mode of operation on read port

- Partial Reset, clears data in single Queue

- Expansion of up to 8 multi-queue devices in parallel is available

- JTAG Functionality (Boundary Scan)

- Available in a 256-pin PBGA, 1mm pitch, 17mm x 17mm

- HIGH Performance submicron CMOS technology

- Industrial temperature range (-40°C to +85°C) is available

$\mathsf{IDT}$  and the  $\mathsf{IDT}$  logo are registered trademarks of Integrated Device Technology, Inc.

## **COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES**

**JUNE 2003**

#### COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

#### IDT72V51233/72V51243/72V51253 3.3V, MULTI-QUEUE FLOW-CONTROL DEVICES (4 QUEUES) 18 BIT WIDE CONFIGURATION 589,824, 1,179,648 and 2,359,296 bits

## **DESCRIPTION:**

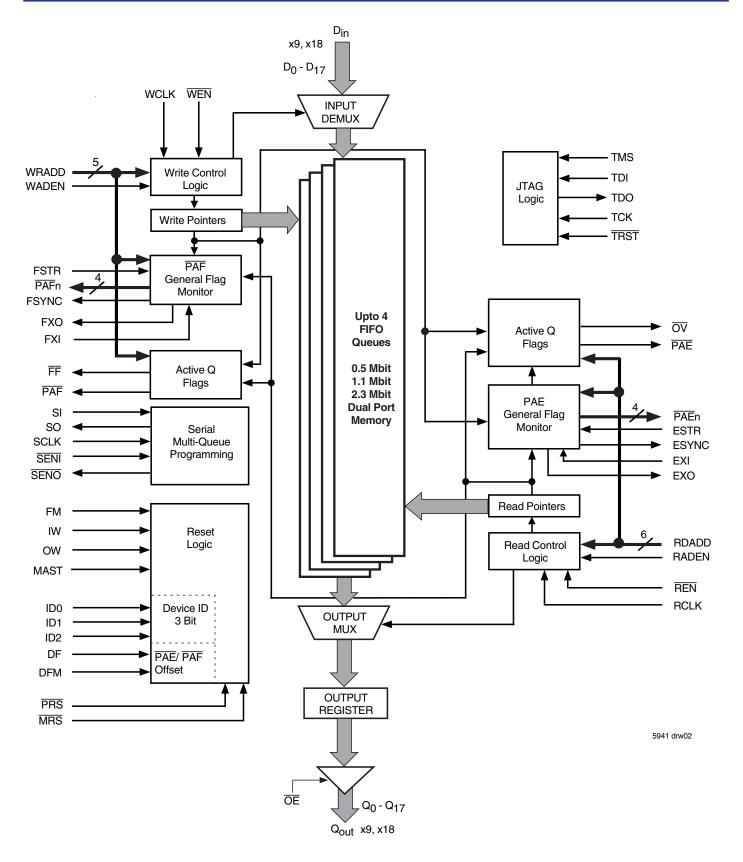

The IDT72V51233/72V51243/72V51253 multi-queue flow-control devices are single chip within which anywhere between 1 and 4 discrete FIFO queues can be setup. All queues within the device have a common data input bus, (write port) and a common data output bus, (read port). Data written into the write port is directed to a respective queue via an internal de-multiplex operation, addressed by the user. Data read from the read port is accessed from a respective queue via an internal multiplex operation, addressed by the user. Data write and read scan be performed at high speeds up to 166MHz, with access times of 3.7ns. Data write and read operations are totally independent of each other, a queue maybe selected on the write port and a different queue on the read port or both ports may select the same queue simultaneously.

The device provides Full flag and Output Valid flag status for the queue selected for write and read operations respectively. Also a Programmable Almost Full and Programmable Almost Empty flag for each queue is provided. Two 4 bit programmable flag busses are available, providing status of all queues, including queues not selected for write or read operations, these flag busses provide an individual flag per queue.

Bus Matching is available on this device, either port can be 9 bits or 18 bits wide. When Bus Matching is used the device ensures the logical transfer of data throughput in a Little Endian manner.

The user has full flexibility configuring queues within the device, being able to program the total number of queues between 1 and 4, the individual queue depths being independent of each other. The programmable flag positions are also user programmable. All programming is done via a dedicated serial port. If the user does not wish to program the multi-queue device, a default option is available that configures the device in a predetermined manner.

Both Master Reset and Partial Reset pins are provided on this device. A Master Reset latches in all configuration setup pins and must be performed before programming of the device can take place. A Partial Reset will reset the read and write pointers of an individual queue, provided that the queue is selected on both the write port and read port at the time of partial reset.

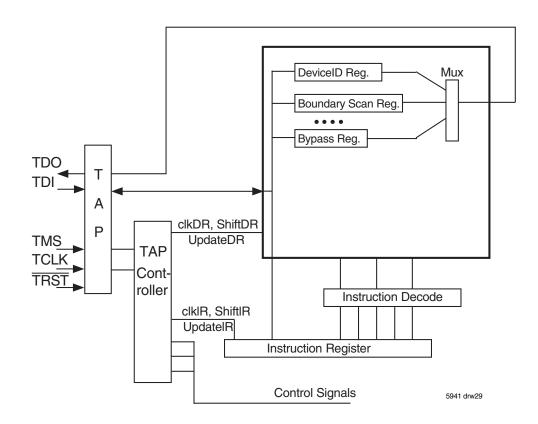

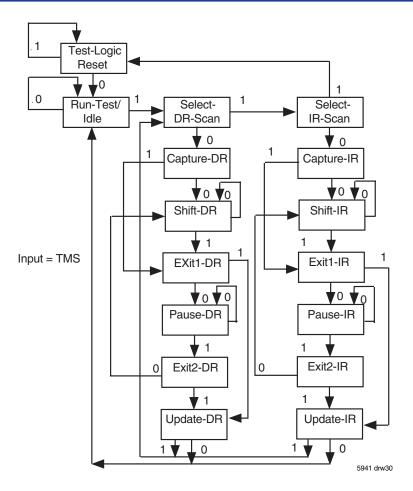

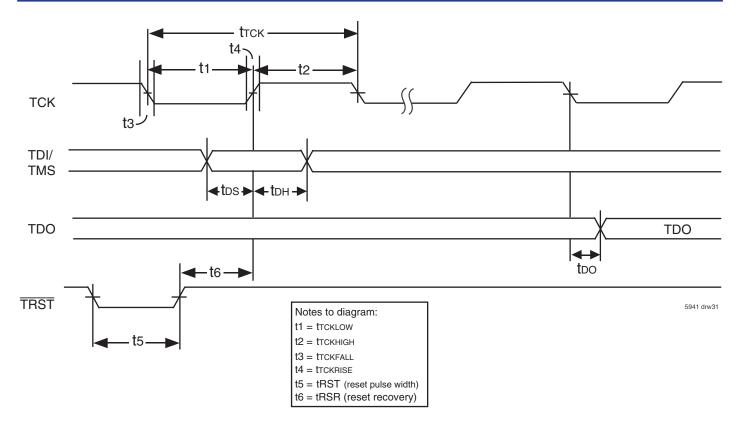

A JTAG test port is provided, here the multi-queue flow-control device has a fully functional Boundary Scan feature, compliant with IEEE 1149.1 Standard Test Access Port and Boundary Scan Architecture.

See Figure 1, *Multi-Queue Flow-Control Device Block Diagram* for an outline of the functional blocks within the device.

# IDT72V51233/72V51243/72V51253 3.3V, MULTI-QUEUE FLOW-CONTROL DEVICES (4 QUEUES) 18 BIT WIDE CONFIGURATION 589,824, 1,179,648 and 2,359,296 bits

Figure 1. Multi-Queue Flow-Control Device Block Diagram

## **PIN CONFIGURATION**

/ A1 BALL PAD CORNER

|    |             | ~           | DALL       |           |           |                            |           |          |          |          |          |          |           |             |             |             |

|----|-------------|-------------|------------|-----------|-----------|----------------------------|-----------|----------|----------|----------|----------|----------|-----------|-------------|-------------|-------------|

| Α  | O<br>D14    | O<br>D13    | O<br>D12   | O<br>D10  | O<br>D7   | O<br>D4                    | O<br>D1   | О<br>тск | O<br>TDO | O<br>ID1 | O<br>Q3  | O<br>Q6  | O<br>Q9   | O<br>Q12    | O<br>Q14    | O<br>Q15    |

| в  | O<br>D15    | O<br>D16    | O<br>D11   | O<br>D9   | O<br>D6   | O<br>D3                    | O<br>D0   | O<br>TMS | O        | O<br>ID0 | O<br>Q2  | O<br>Q5  | O<br>Q8   | O<br>Q11    | O<br>Q13    | O<br>DNC    |

| С  | O<br>D17    | O<br>GND    | O<br>GND   | O<br>D8   | O<br>D5   | O<br>D2                    | O<br>TRST | O<br>GND | O<br>ID2 | O<br>Q0  | O<br>Q1  | O<br>Q4  | O<br>Q7   | O<br>Q10    | O<br>Q17    | O<br>DNC    |

| D  | O<br>GND    |             |            | O<br>vcc  | Ovcc      | O                          | Ovcc      | Ovcc     | Ovcc     | O<br>vcc | Ovcc     | Ovcc     | Ovcc      | O<br>Q16    | O<br>DNC    | O<br>DNC    |

| Е  | O<br>GND    | O<br>GND    |            | Ovcc      | Ovcc      | O                          | Ovcc      |          |          | Ovcc     | Ovcc     | Ovcc     | Ovcc      | O           | O<br>DNC    | O<br>DNC    |

| F  | O<br>GND    | O<br>GND    | O<br>GND   | O<br>vcc  | O<br>vcc  | O<br>GND                   | O<br>GND  | O<br>GND | O<br>GND | O<br>GND | O<br>GND | O<br>vcc | Ovcc      | O<br>DNC    | O<br>DNC    | O<br>DNC    |

| G  | O<br>GND    | O<br>GND    | O<br>GND   | O<br>vcc  | Ovcc      | O<br>GND                   | O<br>GND  | O<br>GND | O<br>GND |          | O<br>GND | Ovcc     | Ovcc      | O<br>DNC    | O<br>DNC    | O<br>DNC    |

| н  | O<br>GND    |             | O<br>GND   | Ovcc      |           | O<br>GND                   |           |          |          |          |          |          | O<br>vcc  | O           | O           | O<br>DNC    |

| J  | O<br>GND    |             |            | Ovcc      |           |                            |           |          |          |          |          |          | Ovcc      |             | O<br>DNC    | O<br>DNC    |

| к  | O<br>GND    | O<br>GND    |            | O<br>VCC  | O<br>vcc  | O<br>GND                   |           |          |          |          |          | Ovcc     | O<br>vcc  |             | O<br>MAST   | O<br>FM     |

| L  | O<br>SI     | O           | O          | Ovcc      | O         |                            |           |          |          |          |          | Ovcc     | Ovcc      |             | O           | O<br>ow     |

| М  |             |             | O<br>so    | Ovcc      | O         | O<br>vcc                   | O<br>vcc  |          |          | O<br>VCC | Ovcc     | O        | Ovcc      |             |             | O<br>RDADD1 |

| Ν  | O<br>WRADD1 | O<br>WRADD0 | O<br>SCLK  | Ovcc      | O         | Ovcc                       | Ovcc      | Ovcc     | O        | Ovcc     | Ovcc     | O        | Ovcc      | O<br>RDADD2 |             | O<br>GND    |

| Ρ  | O<br>GND    | O<br>GND    | O<br>GND   | O         | O<br>PAF3 | O<br>DNC                   | O<br>DNC  | OFF      | Ov       | O<br>PAE | O        | O<br>DNC | O<br>PAE3 | O<br>RDADD3 | O<br>RDADD4 | O<br>RDADD5 |

| R  | O<br>WRADD3 | O<br>WRADD2 | O<br>FSYNC | O<br>FSTR | O<br>PAF2 | O<br>DNC                   | O<br>DNC  |          | O<br>DNC | O<br>DNC | O<br>DNC | O<br>DNC | O<br>PAE2 | O<br>RADEN  | O           | O           |

| т  | WRADD4      | O<br>FXI    | O<br>FXO   |           | O<br>PAF1 | $\bigcup_{\overline{WEN}}$ | O         | O<br>PRS |          | ORCLK    |          | O        | O<br>PAE1 | O<br>PAE0   | O           | OEXI        |

|    | 1           | 2           | 3          | 4         | 5         | 6                          | 7         | 8        | 9        | 10       | 11       | 12       | 13        | 14          | 15          | 16          |

| E: |             |             |            |           |           |                            |           |          |          |          |          |          |           |             | 59          | 941 drw03   |

NOTE:

1. DNC - Do Not Connect.

PBGA (BB256-1, order code: BB) TOP VIEW

# IDT72V51233/72V51243/72V51253 3.3V, MULTI-QUEUE FLOW-CONTROL DEVICES (4 QUEUES) 18 BIT WIDE CONFIGURATION 589,824, 1,179,648 and 2,359,296 bits

#### COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

## **DETAILED DESCRIPTION**

## MULTI-QUEUE STRUCTURE

The IDT multi-queue flow-control device has a single data input port and single data output port with up to 4 FIFO queues in parallel buffering between the two ports. The user can setup between 1 and 4 Queues within the device. These queues can be configured to utilize the total available memory, providing the user with full flexibility and ability to configure the queues to be various depths, independent of one another.

## MEMORY ORGANIZATION/ ALLOCATION

The memory is organized into what is known as "blocks", each block being 512 x 18 or 1,024 x 9 bits. When the user is configuring the number of queues and individual queue sizes the user must allocate the memory to respective queues, in units of blocks, that is, a single queue can be made up from 0 to m blocks, where m is the total number of blocks available within a device. Also the total size of any given queue must be in increments of 512 x 18 or 1,024 x 9. For the IDT72V51233, IDT72V51243 and IDT72V51253 the Total Available Memory is 64, 128 and 256 blocks respectively (a block being 512 x 18 or 1,024 x 9). If any port is configured for x18 bus width, a block size is 512 x 18. If both the write and read ports are configured for x9 bus width, a block size is 1,024 x 9. Queues can be built from these blocks to make any size queue desired and any number of queues desired.

## **BUS WIDTHS**

The input port is common to all queues within the device, as is the output port. The device provides the user with Bus Matching options such that the input port and output port can be either x9 or x18 bits wide, the read and write port widths being set independently of one another. Because the ports are common to all queues the width of the queues is not individually set, so that the input width of all queues are equal and the output width of all queues are equal.

## WRITING TO & READING FROM THE MULTI-QUEUE

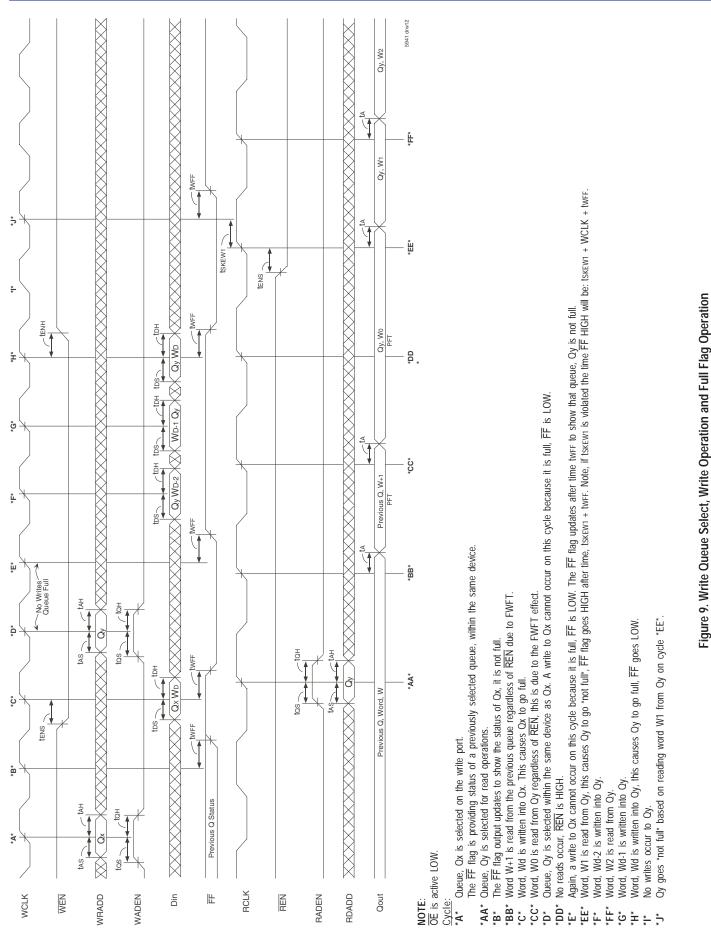

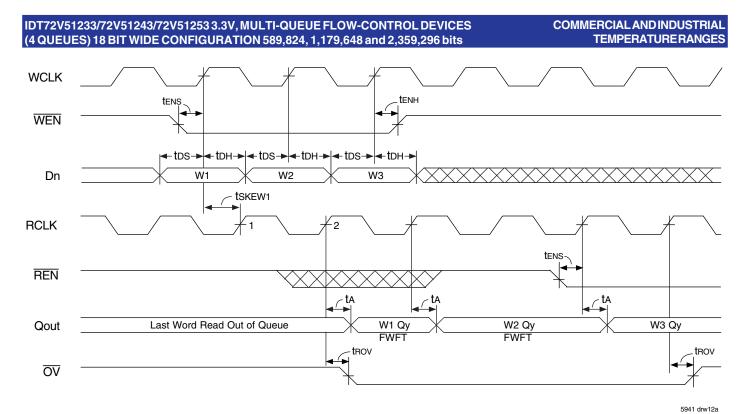

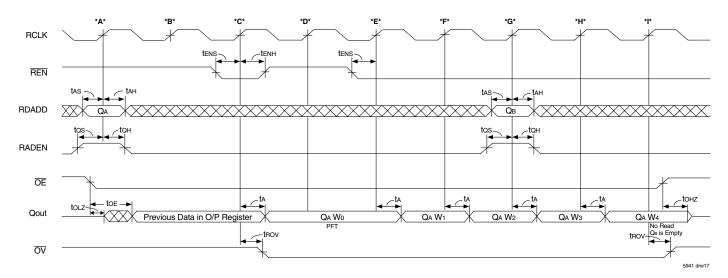

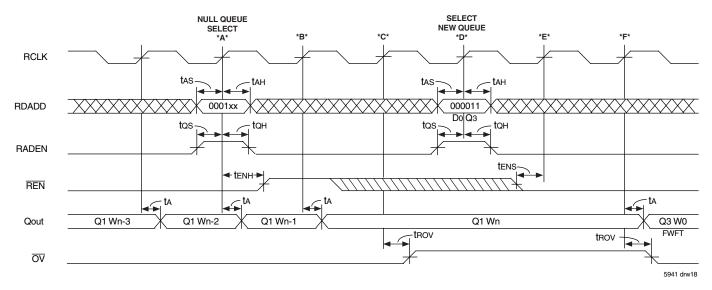

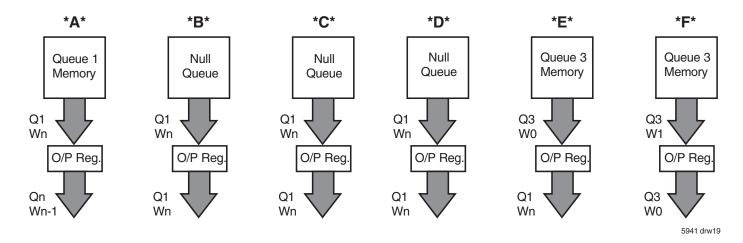

Data being written into the device via the input port is directed to a discrete queue via the write queue select address inputs. Conversely, data being read from the device read port is read from a queue selected via the read queue select address inputs. Data can be simultaneously written into and read from the same queue or different queues. Once a queue is selected for data writes or reads, the writing and reading operation is performed in the same manner as conventional IDT synchronous FIFO, utilizing clocks and enables, there is a single clock and enable per port. When a specific queue is addressed on the write port, data placed on the data inputs is written to that queue sequentially based on the rising edge of a write clock provided setup and hold times are met. Conversely, data is read on to the output port after an access time from a rising edge on a read clock.

The operation of the write port is comparable to the function of a conventional FIFO operating in standard IDT mode. Write operations can be performed on the write port provided that the queue currently selected is not full, a full flag output provides status of the selected queue. The operation of the read port is comparable to the function of a conventional FIFO operating in FWFT mode. When a queue is selected on the output port, the next word in that queue will automatically fall through to the output register. All subsequent words from that queue if that queue is empty, the read port provides an Output Valid flag indicating when data read out is valid. If the user switches to a queue that is empty, the last word from the previous queue will remain on the output register.

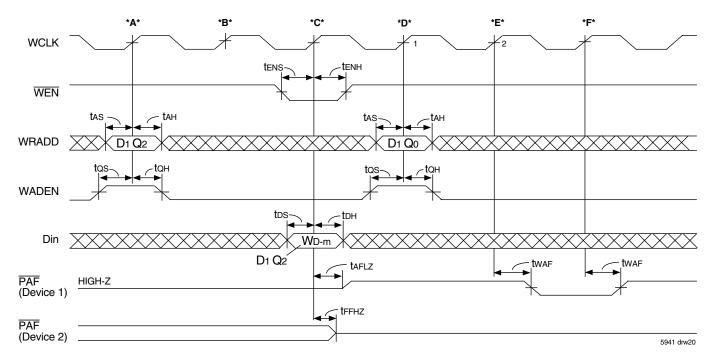

As mentioned, the write port has a full flag, providing full status of the selected queue. Along with the full flag a dedicated almost full flag is provided, this almost full flag is similar to the almost full flag of a conventional IDT FIFO. The device

provides a user programmable almost full flag for all 4 queues and when a respective queue is selected on the write port, the almost full flag provides status for that queue. Conversely, the read port has an output valid flag, providing status of the data being read from the queue selected on the read port. As well as the output valid flag the device provides a dedicated almost empty flag. This almost empty flag is similar to the almost empty flag of a conventional IDT FIFO. The device provides a user programmable almost empty flag for all 4 queues and when a respective queue is selected on the read port, the almost empty flag provides status for that queue.

## **PROGRAMMABLE FLAG BUSSES**

In addition to these dedicated flags, full & almost full on the write port and output valid & almost empty on the read port, there are two flag status busses. An almost full flag status bus is provided, this bus is 4 bits wide. Also, an almost empty flag status bus is provided, again this bus is 4 bits wide. The purpose of these flag busses is to provide the user with a means by which to monitor the data levels within queues that may not be selected on the write or read port. As mentioned, the device provides almost full and almost empty registers (programmable by the user) for each of the 4 queues in the device.

The 4 bit PAEn and 4 bit PAFn busses provide a discrete status of the Almost Empty and Almost Full conditions of all 4 queue's. If the device is programmed for less than 4 queue's, then there will be a corresponding number of active outputs on the PAEn and PAFn busses.

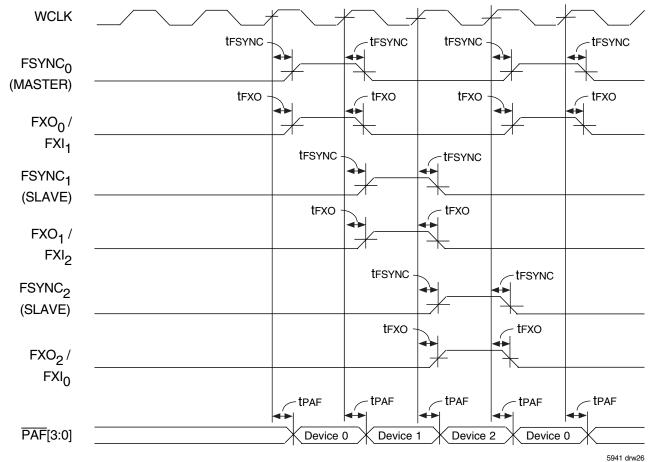

The flag busses can provide a continuous status of all queues. If devices are connected in expansion mode the individual flag busses can be left in a discrete form, providing constant status of all queues, or the busses of individual devices can be connected together to produce a single bus of 4 bits. The device can then operate in a "Polled" or "Direct" mode.

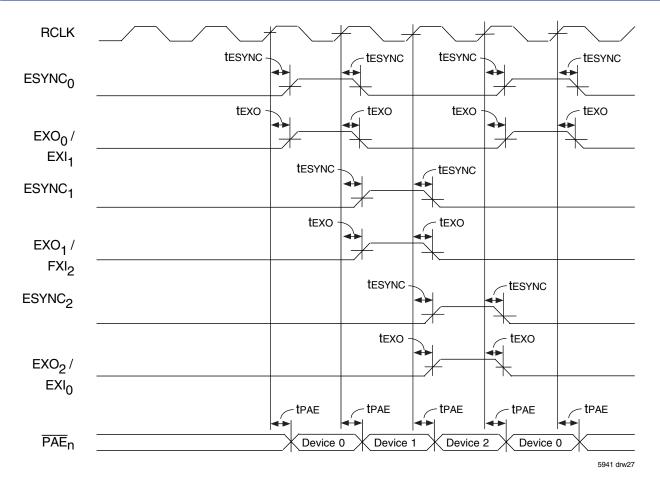

When operating in polled mode the flag bus provides status of each device sequentially, that is, on each rising edge of a clock the flag bus is updated to show the status of each device in order. The rising edge of the write clock will update the Almost Full bus and a rising edge on the read clock will update the Almost Empty bus.

When operating in direct mode the device driving the flag bus is selected by the user. The user addresses the device that will take control of a respective flag bus, these PAFn and PAEn flag busses operating independently of one another. Addressing of the Almost Full flag bus is done via the write port and addressing of the Almost Empty flag bus is done via the read port.

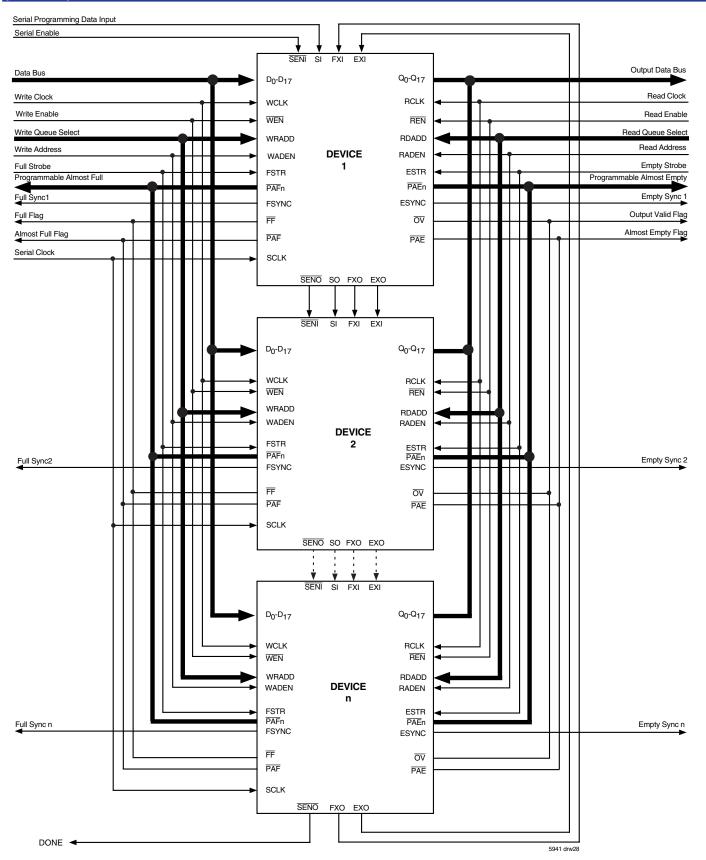

## **EXPANSION**

Expansion of multi-queue devices is also possible, up to 8 devices can be connected in a parallel fashion providing the possibility of both depth expansion or queue expansion. Depth Expansion means expanding the depths of individual queues. Queue expansion means increasing the total number of queues available. Depth expansion is possible by virtue of the fact that more memory blocks within a multi-queue device can be allocated to increase the depth of a queue. For example, depth expansion of 8 devices provides the possibility of 8 queues of 32K x 18 deep within the IDT72V51233, 64K x 18 deep within the IDT72V51253, each queue being setup within a single device utilizing all memory blocks available to produce a single queue. This is the deepest queue that can setup within a device.

For queue expansion of the 4 queue device, a maximum number of 32 (8 x 4) queues may be setup, each queue being 4K x18 or 2K x 9 deep, if less queues are setup, then more memory blocks will be available to increase queue depths if desired. When connecting multi-queue devices in expansion mode all respective input pins (data & control) and output pins (data & flags), should be "connected" together between individual devices.

## **PIN DESCRIPTIONS**

| Symbol &<br>Pin No.                           | Name                      | I/O TYPE        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------|---------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[17:0]<br>Din (See Pin<br>table for details) | Data Input Bus            | LVTTL<br>INPUT  | These are the 18 data input pins. Data is written into the device via these input pins on the rising edge of WCLK provided that WEN is LOW. Due to bus matching not all inputs may be used, any unused inputs should be tied LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DF <sup>(1)</sup><br>(L3)                     | Default Flag              | LVTTL<br>INPUT  | If the user requires default programming of the multi-queue device, this pin must be setup before Master Reset and must not toggle during any device operation. The state of this input at master reset determines the value of the PAE/PAF flag offsets. If DF is LOW the value is 8, if DF is HIGH the value is 128.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DFM <sup>(1)</sup><br>(L2)                    | DefaultMode               | LVTTL<br>INPUT  | The multi-queue device requires programming after master reset. The user can do this serially via the serial port, or the user can use the default method. If DFM is LOW at master reset then serial mode will be selected, if HIGH then default mode is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ESTR<br>(R15)                                 | PAEn Flag Bus<br>Strobe   | LVTTL<br>INPUT  | If direct operation of the PAEn bus has been selected, the ESTR input is used in conjunction with RCLK and the RDADD bus to select a device for its queues to be placed on to the PAEn bus outputs. A device addressed via the RDADD bus is selected on the rising edge of RCLK provided that ESTR is HIGH. If Polled operations has been selected, ESTR should be tied inactive, LOW. Note, that a PAEn flag bus selection cannot be made, (ESTR must NOT go active) until programming of the part has been completed and SENO has gone LOW.                                                                                                                                                                                                                                                                                        |

| ESYNC<br>(R16)                                | PAEn Bus Sync             | LVTTL<br>OUTPUT | ESYNC is an output from the multi-queue device that provides a synchronizing pulse for the PAEn bus during Polled operation of the PAEn bus. During Polled operation each devices queue status flags are loaded on to the PAEn bus outputs sequentially based on RCLK. The first RCLK rising edge loads device 1 on to PAEn, the second RCLK rising edge loads device 2 and so on. During the RCLK cycle that a selected device is placed on to the PAEn bus, the ESYNC output will be HIGH.                                                                                                                                                                                                                                                                                                                                         |

| EXI<br>(T16)                                  | PAEn Bus<br>Expansion In  | LVTTL<br>INPUT  | The EXI input is used when multi-queue devices are connected in expansion mode and Polled $\overline{PAEn}$ /<br>bus operation has been selected. EXI of device 'N' connects directly to EXO of device 'N-1'. The EXI<br>receives a token from the previous device in a chain. In single device mode the EXI input must be tied<br>LOW if the $\overline{PAEn}$ bus is operated in direct mode. If the $\overline{PAEn}$ bus is operated in polled mode the EXI input<br>must be connected to the EXO output of the same device. In expansion mode the EXI of the first device<br>should be tied LOW, when direct mode is selected.                                                                                                                                                                                                  |

| EXO<br>(T15)                                  | PAEn Bus<br>Expansion Out | LVTTL<br>OUTPUT | EXO is an output that is used when multi-queue devices are connected in expansion mode and Polled PAEn bus operation has been selected. EXO of device 'N' connects directly to EXI of device 'N+1'. This pin pulses HIGH when device N places its PAE status on to the PAEn bus with respect to RCLK. This pulse (token) is then passed on to the next device in the chain 'N+1' and on the next RCLK rising edge the first quadrant of device N+1 will be loaded on to the PAEn bus. This continues through the chain and EXO of the last device is then looped back to EXI of the first device. The ESYNC output of each device in the chain provides synchronization to the user of this looping event.                                                                                                                           |

| FF<br>(P8)                                    | Full Flag                 | LVTTL<br>OUTPUT | This pin provides the full flag output for the active queue, that is, the queue selected on the input port for write operations, (selected via WCLK, WRADD bus and WADEN). On the WCLK cycle after a queue selection, this flag will show the status of the newly selected queue. Data can be written to this queue on the next cycle provided FF is HIGH. This flag has High-Impedance capability, this is important during expansion of devices, when the FF flag output of up to 8 devices may be connected together on a common line. The device with a queue selected takes control of the FF bus, all other devices place their FF output into High-Impedance. When a queue selection is made on the write port this output will switch from High-Impedance control on the next WCLK cycle. This flag is synchronized to WCLK. |

| FM <sup>(1)</sup><br>(K16)                    | Flag Mode                 | LVTTL<br>INPUT  | This pin is setup before a master reset and must not toggle during any device operation. The state of the FM pin during Master Reset will determine whether the PAFn and PAEn flag busses operate in either Polled or Direct mode. If this pin is HIGH the mode is Polled, if LOW then it will be Direct.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FSTR<br>(R4)                                  | PAFn Flag Bus<br>Strobe   | LVTTL<br>INPUT  | If direct operation of the PAFn bus has been selected, the FSTR input is used in conjunction with WCLK and the WRADD bus to select a device for its queues to be placed on to the PAFn bus outputs. A device addressed via the WRADD bus is selected on the rising edge of WCLK provided that FSTR is HIGH. If Polled operations has been selected, FSTR should be tied inactive, LOW. Note, that a PAFn flag bus selection cannot be made, (FSTR must NOT go active) until programming of the part has been completed and SENO has gone LOW.                                                                                                                                                                                                                                                                                        |

| Symbol &<br>Pin No.                                      | Name                      | I/O TYPE        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------|---------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FSYNC<br>(R3)                                            | PAFn Bus Sync             | LVTTL<br>OUTPUT | FSYNC is an output from the multi-queue device that provides a synchronizing pulse for the PAFn bus during Polled operation of the PAFn bus. During Polled operation each quadrant of queue status flags is loaded on to the PAFn bus outputs sequentially based on WCLK. The first WCLK rising edge loads device1 on to the PAFn bus outputs, the second WCLK rising edge loads device 2 and so on. During the WCLK cycle that a selected device is placed on to the PAFn bus, the FSYNC output will be HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| FXI<br>(T2)                                              | PAFn Bus<br>Expansion In  | LVTTL<br>INPUT  | The FXI input is used when multi-queue devices are connected in expansion mode and Polled $\overline{PAFn}$ bus operation has been selected . FXI of device 'N' connects directly to FXO of device 'N-1'. The FXI receives a token from the previous device in a chain. In single device mode the FXI input must be tied LOW if the $\overline{PAFn}$ bus is operated in direct mode. If the $\overline{PAFn}$ bus is operated in polled mode the FXI input must be connected to the FXO output of the same device. In expansion mode the FXI of the first device should be tied LOW, when direct mode is selected.                                                                                                                                                                                                                                                                                                                                                                |

| FXO<br>(T3)                                              | PAFn Bus<br>Expansion Out | LVTTL<br>OUTPUT | FXO is an output that is used when multi-queue devices are connected in expansion mode and Polled $\overline{PAFn}$ bus operation has been selected . FXO of device 'N' connects directly to FXI of device 'N+1'. This pin pulses HIGH when device N places its $\overline{PAF}$ status onto the $\overline{PAFn}$ bus with respect to WCLK. This pulse (token) is then passed on to the next device in the chain 'N+1' and on the next WCLK rising edge the first quadrant of device N+1 will be loaded on to the $\overline{PAFn}$ bus. This continues through the chain and FXO of the last device is then looped back to FXI of the first device. The FSYNC output of each device in the chain provides synchronization to the user of this looping event.                                                                                                                                                                                                                     |

| ID[2:0] <sup>(1)</sup><br>(ID2-C9<br>ID1-A10<br>ID0-B10) | Device ID Pins            | LVTTL<br>INPUT  | For the 4Q multi-queue device the WRADD address bus is 5 bits and RDADD address bus is 6 bits wide.<br>When a queue selection takes place the 3MSb's of this address bus are used to address the specific device<br>(the LSb's are used to address the queue within that device). During write/read operations the 3 MSb's<br>of the address are compared to the device ID pins. The first device in a chain of multi-queue's (connected<br>in expansion mode), may be setup as '000', the second as '001' and so on through to device 8 which is<br>'111', however the ID does not have to match the device order. In single device mode these pins should<br>be setup as '000' and the 3 MSb's of the WRADD and RDADD address busses should be tied LOW. The<br>ID[2:0] inputs setup a respective devices ID during master reset. These ID pins must not toggle during<br>any device operation. Note, the device selected as the 'Master' does not have to have the ID of '000'. |

| IW <sup>(1)</sup><br>(L15)                               | Input Width               | LVTTL<br>INPUT  | IW selects the bus width for the data input bus. If IW is LOW during a Master Reset then the bus width is x18, if HIGH then it is x9.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MAST <sup>(1)</sup><br>(K15)                             | Master Device             | LVTTL<br>INPUT  | The state of this input at Master Reset determines whether a given device (within a chain of devices), is the Master device or a Slave. If this pin is HIGH, the device is the master, if it is LOW then it is a Slave. The master device is the first to take control of all outputs after a master reset, all slave devices go to High-Impedance, preventing bus contention. If a multi-queue device is being used in single device mode, this pin must be set HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MRS<br>(T9)                                              | Master Reset              | LVTTL<br>INPUT  | A master reset is performed by taking MRS from HIGH to LOW, to HIGH. Device programming is required after master reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| OE<br>(M14)                                              | Output Enable             | LVTTL<br>INPUT  | The Output enable signal is an Asynchronous signal used to provide three-state control of the multi-queue data output bus, Qout. If a device has been configured as a "Master" device, the Qout data outputs will be in a Low Impedance condition if the $\overline{OE}$ input is LOW. If $\overline{OE}$ is HIGH then the Qout data outputs will be in High Impedance. If a device is configured a "Slave" device, then the Qout data outputs will always be in High Impedance until that device has been selected on the Read Port, at which point $\overline{OE}$ provides three-state of that respective device.                                                                                                                                                                                                                                                                                                                                                               |

| <del>0V</del><br>(P9)                                    | Output Valid Flag         | LVTTL<br>OUTPUT | This output flag provides output valid status for the data word present on the multi-queue flow-control device data output port, Qout. This flag is therefore, 2-stage delayed to match the data output path delay. That is, there is a 2 RCLK cycle delay from the time a given queue is selected for reads, to the time the $\overline{OV}$ flag represents the data in that respective queue. When a selected queue on the read port is read to empty, the $\overline{OV}$ flag will go HIGH, indicating that data on the output bus is not valid. The $\overline{OV}$ flag also has High-Impedance capability, required when multiple devices are used and the $\overline{OV}$ flags are tied together.                                                                                                                                                                                                                                                                        |

| OW <sup>(1)</sup><br>(L16)                               | Output Width              | LVTTL<br>INPUT  | OW selects the bus width for the data output bus. If OW is LOW during a Master Reset then the bus width is x18, if HIGH then it is $x9$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Symbol &<br>Pin No.                                    | Name                                     | I/O TYPE        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------|------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAE<br>(P10)                                           | Programmable<br>Almost-Empty Flag        | LVTTL<br>OUTPUT | This pin provides the Almost-Empty flag status for the queue that has been selected on the output port for read operations, (selected via RCLK, RDADD and RADEN). This pin is LOW when the selected queue is almost-empty. This flag output may be duplicated on one of the PAEn bus lines. This flag is synchronized to RCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PAEn<br>(PAE3-P13<br>PAE2-R13<br>PAE1-T13<br>PAE0-T14) | Programmable<br>Almost-Empty<br>Flag Bus | LVTTL<br>OUTPUT | On the 4Q device the PAEn bus is 4 bits wide. This output bus provides PAE status of all 4 queues, within a selected device. During queue read/write operations these outputs provide programmable empty flag status in either director polled mode. The mode of flag operation is determined during master reset via the state of the FM input. This flag bus is capable of High-Impedance state, this is important during expansion of multi-queue devices. During direct operation the PAEn bus is updated to show the PAE status of queues within a selected device. Selection is made using RCLK, ESTR and Flag Bus RDADD. During Polled operation the PAEn bus is loaded with the PAE status of multi-queue flow-control devices sequentially based on the rising edge of RCLK.  |

| PAF<br>(R8)                                            | Programmable<br>Almost-Full Flag         | LVTTL<br>OUTPUT | This pin provides the Almost-Full flag status for the queue that has been selected on the input port for write operations, (selected via WCLK, WRADD and WADEN). This pin is LOW when the selected queue is almost-full. This flag output may be duplicated on one of the PAFn bus lines. This flag is synchronized to WCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PAFn<br>(PAE3-P5<br>PAE2-R5<br>PAE1-T5<br>PAE0-T4)     | Programmable<br>Almost-Full<br>Flag Bus  | LVTTL<br>OUTPUT | On the 4Q device the PAFn bus is 4 bits wide. This output bus provides PAF status of all 4 queues, within a selected device. During queue read/write operations these outputs provide programmable full flag status, in either direct or polled mode. The mode of flag operation is determined during master reset via the state of the FM input. This flag bus is capable of High-Impedance state, this is important during expansion of multi-queue devices. During direct operation the PAFn bus is updated to show the PAF status of a queues within a selected device. Selection is made using WCLK, FSTR, WRADD and WADEN. During Polled operation the PAFn bus is loaded with the PAF status of multi-queue flow-control devices sequentially based on the rising edge of WCLK. |

| PRS<br>(T8)                                            | Partial Reset                            | LVTTL<br>INPUT  | A Partial Reset can be performed on a single queue selected within the multi-queue device. Before a Partial Reset can be performed on a queue, that queue must be selected on both the write port and read port 2 clock cycles before the reset is performed. A Partial Reset is then performed by taking PRS LOW for one WCLK cycle and one RCLK cycle. The Partial Reset will only reset the read and write pointers to the first memory location, none of the devices configuration will be changed.                                                                                                                                                                                                                                                                                |

| Q[17:0]<br>Qout (See Pin<br>table for details)         | Data Output Bus                          | LVTTL<br>OUTPUT | These are the 18 data output pins. Data is read out of the device via these output pins on the rising edge of RCLK provided that $\overline{REN}$ is LOW, $\overline{OE}$ is LOW and the queue is selected. Due to bus matching not all outputs may be used, any unused outputs should not be connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RADEN<br>(R14)                                         | Read Address<br>Enable                   | LVTTL<br>INPUT  | The RADEN input is used in conjunction with RCLK and the RDADD address bus to select a queue to be read from. A queue addressed via the RDADD bus is selected on the rising edge of RCLK provided that RADEN is HIGH. RADEN should be asserted (HIGH) only during a queue change cycle(s). RADEN should not be permanently tied HIGH. RADEN cannot be HIGH for the same RCLK cycle as ESTR. Note, that a read queue selection cannot be made, (RADEN must NOT go active) until programming of the part has been completed and SENO has gone LOW.                                                                                                                                                                                                                                       |

| RCLK<br>(T10)                                          | Read Clock                               | LVTTL<br>INPUT  | When enabled by $\overline{\text{REN}}$ , the rising edge of RCLK reads data from the selected queue via the output bus<br>Qout. The queue to be read is selected via the RDADD address bus and a rising edge of RCLK while<br>RADEN is HIGH. A rising edge of RCLK in conjunction with ESTR and RDADD will also select the device<br>to be placed on the PAEn bus during direct flag operation. During polled flag operation the PAEn bus is<br>cycled with respect to RCLK and the ESYNC signal is synchronized to RCLK. The PAE and $\overline{OV}$ outputs<br>are all synchronized to RCLK. During device expansion the EXO and EXI signals are based on RCLK.<br>RCLK must be continuous and free-running.                                                                        |

| RDADD<br>[5:0]<br>(See next page<br>for details)       | Read Address Bus                         | LVTTL<br>INPUT  | For the 4Q device the RDADD bus is 6 bits. The RDADD bus is a dual purpose address bus. The first function of RDADD is to select a queue to be read from. The least significant 2 bits of the bus, RDADD[1:0] are used to address 1 of 4 possible queues within a multi-queue device. Address pin, RDADD[2] provides the user with a Null-Q address. If the user does not wish to address one of the 4 queues, a Null-Q can be addressed using this pin. The Null-Q operation is discussed in more detail later. The most significant 3 bits, RDADD[5:3] are used to select 1 of 8 possible multi-queue devices that may be connected in expansion mode. These 3 MSB's will address a device with the matching ID code. The address present                                            |

| Symbol &<br>Pin No.                                                                                                               | Name                    | I/O TYPE        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDADD<br>[5:0]<br>(Continued)<br>(RDADD5-P16<br>RDADD4-P15<br>RDADD3-P14<br>RDADD2-N14<br>RDADD2-N14<br>RDADD1-M16<br>RDADD0-M15) | Read Address Bus        | LVTTL<br>INPUT  | on the RDADD bus will be selected on a rising edge of RCLK provided that RADEN is HIGH, (note, that data can be placed on to the Qout bus, read from the previously selected queue on this RCLK edge). On the next rising RCLK edge after a read queue select, a data word from the previous queue will be placed onto the outputs, Qout, regardless of the REN input. Two RCLK rising edges after read queue select, data will be placed on to the Qout outputs from the newly selected queue, regardless of REN due to the first word fall through effect. The second function of the RDADD bus is to select the device of queues to be loaded on to the PAEn bus during strobed flag mode. The most significant 3 bits, RDADD[5:3] are again used to select 1 of 8 possible multi-queue devices that may be connected in expansion mode. Address bits RDADD[2:0] are don't care during device selection. The device address present on the RDADD bus will be selected on the rising edge of RCLK provided that ESTR is HIGH, (note, that data can be placed on to the Qout bus, read from the previously selected queue on this RCLK edge). Please refer to Table 2 for details on RDADD bus. |

| REN<br>(T11)                                                                                                                      | Read Enable             | LVTTL<br>INPUT  | The REN input enables read operations from a selected queue based on a rising edge of RCLK. A queue to be read from can be selected via RCLK, RADEN and the RDADD address bus regardless of the state of REN. Data from a newly selected queue will be available on the Qout output bus on the second RCLK cycle after queue selection regardless of REN due to the FWFT operation. A read enable is not required to cycle the PAEn bus (in polled mode) or to select the device , (in direct mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

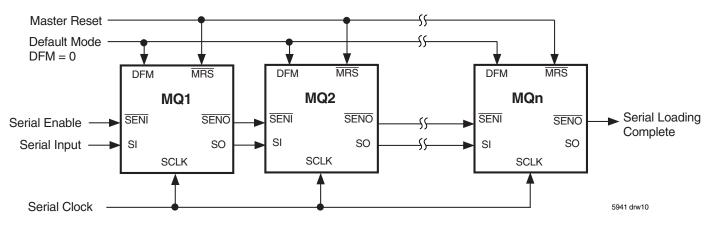

| SCLK<br>(N3)                                                                                                                      | Serial Clock            | LVTTL<br>INPUT  | If serial programming of the multi-queue device has been selected during master reset, the SCLK input clocks the serial data through the multi-queue device. Data setup on the SI input is loaded into the device on the rising edge of SCLK provided that SENI is enabled, LOW. When expansion of devices is performed the SCLK of all devices should be connected to the same source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SENI<br>(M2)                                                                                                                      | Serial Input Enable     | LVTTL<br>INPUT  | During serial programming of a multi-queue device, data loaded onto the SI input will be clocked into the part (via a rising edge of SCLK), provided the SENI input of that device is LOW. If multiple devices are cascaded, the SENI input should be connected to the SENO output of the previous device. So when serial loading of a given device is complete, its SENO output goes LOW, allowing the next device in the chain to be programmed (SENO will follow SENI of a given device once that device is programmed). The SENI input of the master device (or single device), should be controlled by the user.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SENO<br>(M1)                                                                                                                      | Serial Output<br>Enable | LVTTL<br>OUTPUT | This output is used to indicate that serial programming or default programming of the multi-queue device has been completed. SENO follows SENI once programming of a device is complete. Therefore, SENO will go LOW after programming provided SENI is LOW, once SENI is taken HIGH again, SENO will also go HIGH. When the SENO output goes LOW, the device is ready to begin normal read/write operations. If multiple devices are cascaded and serial programming of the devices will be used, the SENO output should be connected to the SENI input of the next device in the chain. When serial programming of the first device is complete, SENO will go LOW, thereby taking the SENI input of the next device LOW and so on throughout the chain. When a given device in the chain is fully programmed the SENO output essentially follows the SENI input. The user should monitor the SENO output of the final device in the chain. When this output goes LOW, serial loading of all devices has been completed.                                                                                                                                                                        |

| SI<br>(L1)                                                                                                                        | Serial In               | LVTTL<br>INPUT  | During serial programming this pin is loaded with the serial data that will configure the multi-queue devices.<br>Data present on SI will be loaded on a rising edge of SCLK provided that SENI is LOW. In expansion<br>mode the serial data input is loaded into the first device in a chain. When that device is loaded and its SENO<br>has gone LOW, the data present on SI will be directly output to the SO output. The SO pin of the first device<br>connects to the SI pin of the second and so on. The multi-queue device setup registers are shift registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SO<br>(M3)                                                                                                                        | SerialOut               | LVTTL<br>OUTPUT | This output is used in expansion mode and allows serial data to be passed through devices in the chain to complete programming of all devices. The SI of a device connects to SO of the previous device in the chain. The SO of the final device in a chain should not be connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TCK <sup>(2)</sup><br>(A8)                                                                                                        | JTAG Clock              | LVTTL<br>INPUT  | Clock input for JTAG function. One of four terminals required by IEEE Standard 1149.1-1990. Test operations of the device are synchronous to TCK. Data from TMS and TDI are sampled on the rising edge of TCK and outputs change on the falling edge of TCK. If the JTAG function is not used this signal needs to be tied to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TDI <sup>(2)</sup><br>(B9)                                                                                                        | JTAG Test Data<br>Input | LVTTL<br>INPUT  | One of four terminals required by IEEE Standard 1149.1-1990. During the JTAG boundary scan operation, test data serially loaded via the TDI on the rising edge of TCK to either the Instruction Register, ID Register and Bypass Register. An internal pull-up resistor forces TDI HIGH if left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Symbol &<br>Pin No.                                                               | Name                     | I/O TYPE        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------|--------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDO <sup>(2)</sup><br>(A9)                                                        | JTAG Test Data<br>Output | LVTTL<br>OUTPUT | One of four terminals required by IEEE Standard 1149.1-1990. During the JTAG boundary scan operation, test data serially loaded output via the TDO on the falling edge of TCK from either the Instruction Register, ID Register and Bypass Register. This output is high impedance except when shifting, while in SHIFT-DR and SHIFT-IR controller states.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TMS <sup>(2)</sup><br>(B8)                                                        | JTAG Mode Select         | LVTTL<br>INPUT  | TMS is a serial input pin. One of four terminals required by IEEE Standard 1149.1-1990. TMS directs the device through its TAP controller states. An internal pull-up resistor forces TMS HIGH if left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TRST <sup>(2)</sup><br>(C7)                                                       | JTAG Reset               | LVTTL<br>INPUT  | $\overline{\text{TRST}}$ is an asynchronous reset pin for the JTAG controller. The JTAG TAP controller does not automatically reset upon power-up, thus it must be reset by either this signal or by setting TMS= HIGH for five TCK cycles. If the TAP controller is not properly reset then the outputs will always be in high-impedance. If the JTAG function is used but the user does not want to use TRST, then TRST can be tied with MRS to ensure proper queue operation. If the JTAG function is not used then this signal needs to be tied to GND. An internal pull-up resistor forces TRST HIGH if left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| WADEN<br>(P4)                                                                     | Write Address<br>Enable  | LVTTL<br>INPUT  | The WADEN input is used in conjunction with WCLK and the WRADD address bus to select a queue to be written in to. A queue addressed via the WRADD bus is selected on the rising edge of WCLK provided that WADEN is HIGH. WADEN should be asserted (HIGH) only during a queue change cycle(s). WADEN should not be permanently tied HIGH. WADEN cannot be HIGH for the same WCLK cycle as FSTR. Note, that a write queue selection cannot be made, (WADEN must NOT go active) until programming of the part has been completed and SENO has gone LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| WCLK<br>(T7)                                                                      | Write Clock              | LVTTL<br>INPUT  | When enabled by WEN, the rising edge of WCLK writes data into the selected queue via the input bus,<br>Din. The queue to be written to is selected via the WRADD address bus and a rising edge of WCLK while<br>WADEN is HIGH. A rising edge of WCLK in conjunction with FSTR and WRADD will also select the device<br>to be placed on the PAFn bus during direct flag operation. During polled flag operation the PAFn bus is<br>cycled with respect to WCLK and the FSYNC signal is synchronized to WCLK. The PAFn, PAF and FF<br>outputs are all synchronized to WCLK. During device expansion the FXO and FXI signals are based on<br>WCLK. The WCLK must be continuous and free-running.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

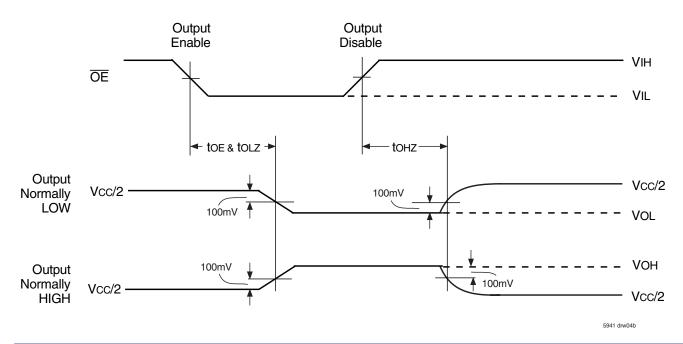

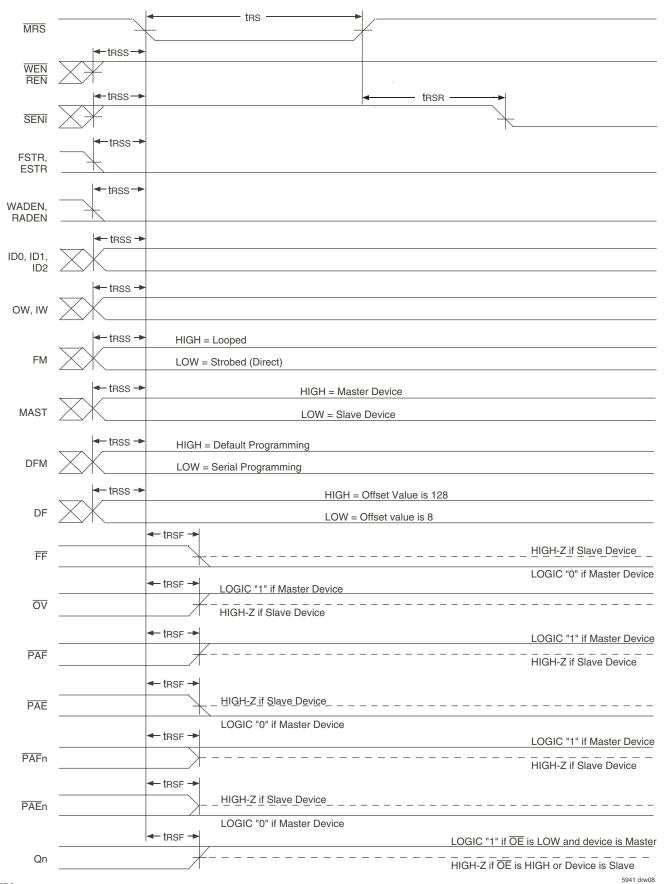

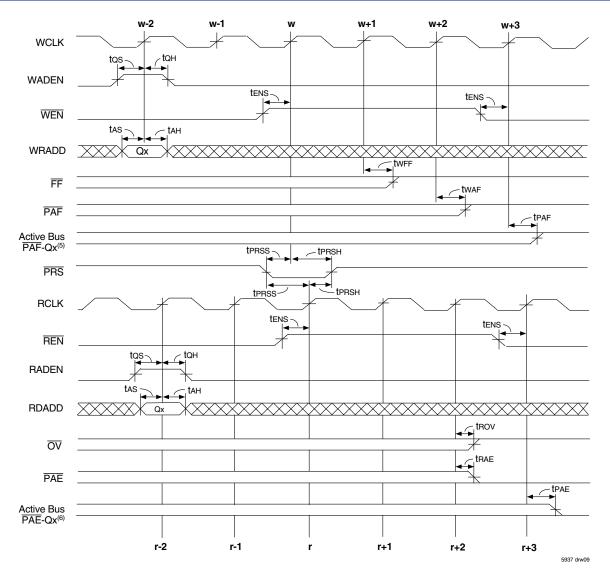

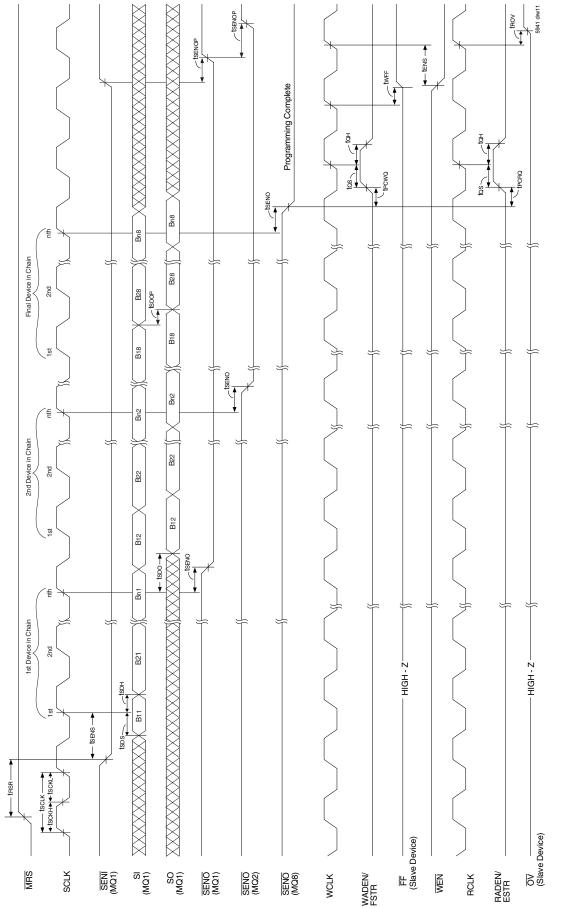

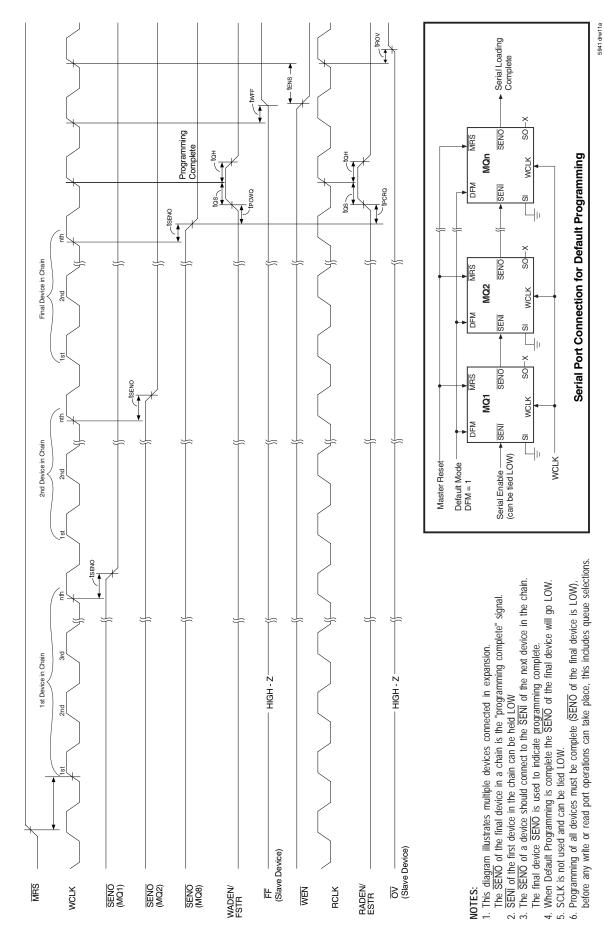

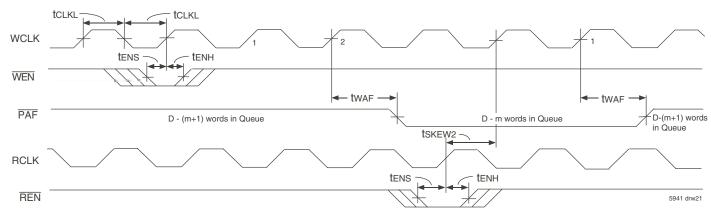

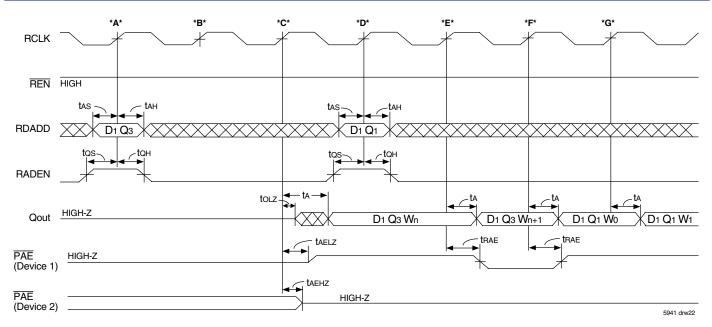

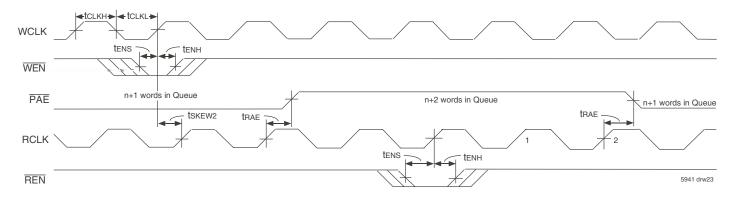

| WEN<br>(T6)                                                                       | Write Enable             | LVTTL<br>INPUT  | The $\overline{\text{WEN}}$ input enables write operations to a selected queue based on a rising edge of WCLK. A queue to be written to can be selected via WCLK, WADEN and the WRADD address bus regardless of the state of $\overline{\text{WEN}}$ . Data present on Din can be written to a newly selected queue on the second WCLK cycle after queue selection provided that $\overline{\text{WEN}}$ is LOW. A write enable is not required to cycle the $\overline{\text{PAFn}}$ bus (in polled mode) or to select the device, (in direct mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |