# 3.3 VOLT TIME SLOT INTERCHANGE DIGITAL SWITCH

IDT72V8980

256 x 256

# **FEATURES:**

- 256 x 256 channel non-blocking switch

- Serial Telecom Bus Compatible (ST-BUS<sup>®</sup>)

- 8 RX inputs—32 channels at 64 Kbit/s per serial line

- 8 TX output—32 channels at 64 Kbit/s per serial line

- Three-state serial outputs

- Microprocessor Interface (8-bit data bus)

- 3.3V Power Supply

- Available in 44-pin Plastic Leaded Chip Carrier (PLCC), 48-pin Small Shrink Outline Package (SSOP), 48-pin Plastic Small Outline (TSSOP) and 44-pin Plastic Quad Flatpack (PQFP)

- Operating Temperature Range -40°C to +85°C

## **DESCRIPTION:**

The IDT72V8980 is a ST-BUS $^{\circ}$  compatible digital switch controlled by a microprocessor. The IDT72V8980 can handle as many as 256, 64 Kbit/s input and output channels. Those 256 channels are divided into 8 serial inputs and

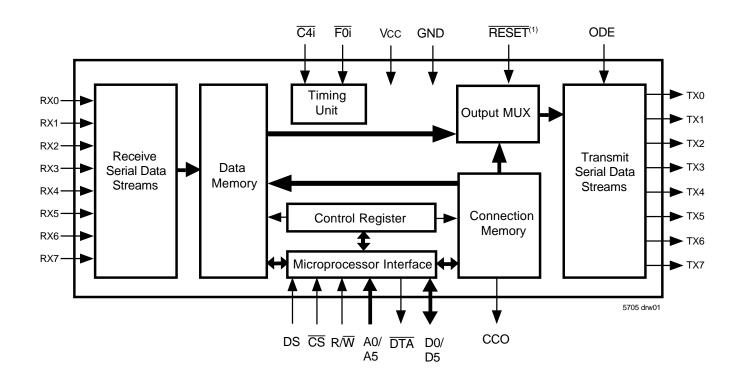

FUNCTIONAL BLOCK DIAGRAM

outputs, each of which consists of 32 channels (64 Kbit/s per channel) to form a multiplexed 2.048 Mb/s stream.

# **FUNCTIONAL DESCRIPTION**

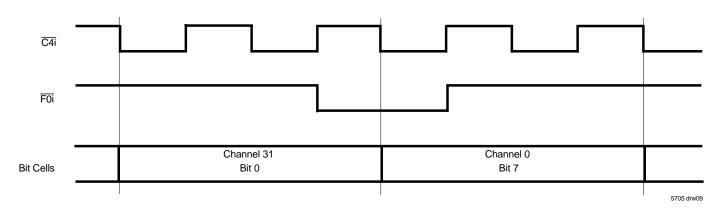

A functional block diagram of the IDT72V8980 device is shown on below. The serial ST-BUS<sup>®</sup> streams operate continuously at 2.048 Mb/s and are arranged in 125µs wide frames each containing 32, 8-bit channels. Eight input (RX0-7) and eight output (TX0-7) serial streams are provided in the IDT72V8980 device allowing a complete 256 x 256 channel non-blocking switch matrix to be constructed. The serial interface clock (C4i) for the device is 4.096 MHz.

The received serial data is internally converted to a parallel format by the on chip serial-to-parallel converters and stored sequentially in a 256-position Data Memory. By using an internal counter that is reset by the input 8 KHz frame pulse,  $\overline{F0i}$ , the incoming serial data streams can be framed and sequentially addressed.

#### NOTE:

## **JANUARY 2001**

<sup>1.</sup> The RESET Input is only provided on the TSSOP and SSOP package.

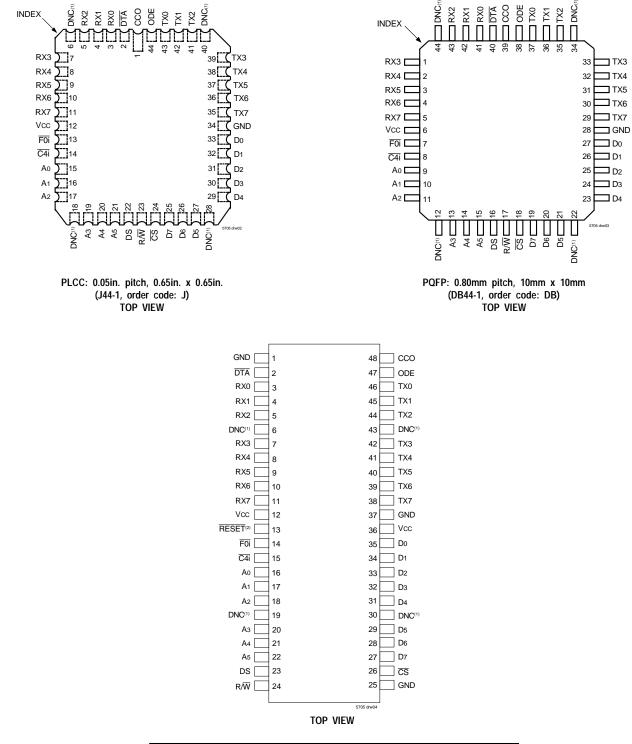

## **PIN CONFIGURATION**

| Package Type                              | <b>Reference Identifier</b> | Order Code |

|-------------------------------------------|-----------------------------|------------|

| SSOP: 0.025in. pitch, 0.625in. x 0.295in. | SO48-1                      | PV         |

| TSSOP: 0.50mm pitch, 12.50mm x 6.10mm     | SO48-2                      | PA         |

## NOTES:

1. DNC - Do Not Connect

<sup>2.</sup> The  $\ensuremath{\overline{\mathsf{RESET}}}$  Input is only provided on the TSSOP and SSOP package.

# **PIN DESCRIPTIONS**

| SYMBOL | NAME                                    | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|-----------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND    | Ground.                                 |     | Ground Rail.                                                                                                                                                                                                                                                                                                                                                                                                |

| Vcc    | Vcc                                     |     | +3.3 Volt Power Supply.                                                                                                                                                                                                                                                                                                                                                                                     |

| DTA    | Data Acknowledgment<br>(Open Drain)     | 0   | This active LOW output indicates that a data bus transfer is complete. A pull-up resistor is required at this output.                                                                                                                                                                                                                                                                                       |

| RX0-7  | RX Input 0 to 7                         | Ι   | Serial data input streams. These streams have 32 channels at data rates of 2.048 Mb/s.                                                                                                                                                                                                                                                                                                                      |

| F0i    | Frame Pulse                             | Ι   | This input identifies frame synchronization signals formatted to ST-BUS <sup>®</sup> specifications.                                                                                                                                                                                                                                                                                                        |

| C4i    | Clock                                   | Ι   | 4.096 MHz serial clock for shifting data in and out of the data streams.                                                                                                                                                                                                                                                                                                                                    |

| A0-A5  | Address 0 to 5                          | Ι   | These lines provide the address to IDT72V8980 internal registers.                                                                                                                                                                                                                                                                                                                                           |

| DS     | Data Strobe                             | I   | This is the input for the active HIGH data strobe on the microprocessor interface. This input operates with $\overline{CS}$ to enable the internal read and write generation.                                                                                                                                                                                                                               |

| R/W    | Read/Write                              | I   | This input controls the direction of the data bus lines (D0-D7) during a microprocessor access.                                                                                                                                                                                                                                                                                                             |

| CS     | Chip Select                             | Ι   | Active LOW input enabling a microprocessor read or write of control register or internal memories.                                                                                                                                                                                                                                                                                                          |

| D0-D7  | Data Bus 0 to 7                         | I/O | These pins provide microprocessor access to data in the internal control register. Connection Memory HIGH, Connection Memory LOW and data memory.                                                                                                                                                                                                                                                           |

| TX0-7  | TX Outputs 0 to 7                       | 0   | Serial data output streams. These streams are composed of 32, 64 Kbit/s channels at data rates of 2.048 Mb/s.                                                                                                                                                                                                                                                                                               |

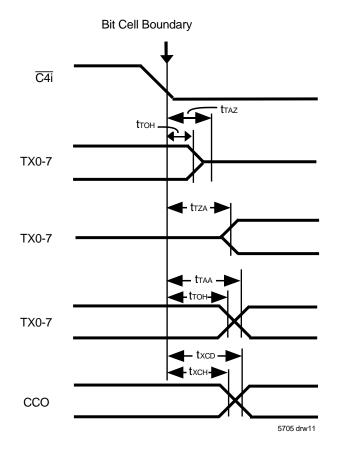

| ODE    | Output Drive Enable                     | Ι   | This is an output enable for the TX0-7 serial outputs. If this input is LOW, TX0-7 are high-impedance. If this is HIGH, each channel may still be put into high-impedance by software control.                                                                                                                                                                                                              |

| ССО    | Control Channel Output                  | 0   | This output is a 2.048 Mb/s line which contains 256 bits per frame. The level of each bit is controlled by the contents of the CCO bit in the Connection Memory HIGH locations.                                                                                                                                                                                                                             |

| RESET  | Device Reset<br>(Schmitt Trigger Input) |     | This input (active LOW) puts the IDT72V8980 in its reset state that clears the device internal counters, registers and brings TX0-7 and microport data outputs to a high-impedance state. The time constant for a power up reset circuit must be a minimum of five times the rise time of the power supply. In normal operation, the RESET pin must be held LOW for a minimum of 100ns to reset the device. |

## **FUNCTIONAL DESCRIPTION (Cont'd)**

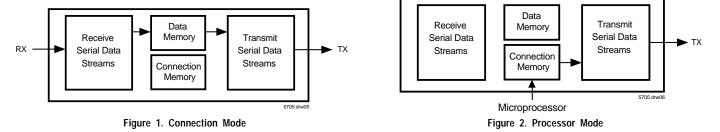

Data to be output on the serial streams may come from two sources: Data Memory or Connection Memory. The Connection Memory is 16 bits wide and is split into two 8-bit blocks—Connection Memory HIGH and Connection Memory LOW. Each location in Connection Memory is associated with a particular channel in the output stream so as to provide a one-to-one correspondence between the two memories. This correspondence allows for per channel control for each TX output stream. In Processor Mode, data output on the TX stream is taken from the Connect Memory Low and originates from the microprocessor (Figure 2). Where as in Connection Mode (Figure 1), data is read from Data Memory using the address in Connection Memory. Data destined for a particular channel on the serial output stream is read during the previous channel time slot to allow time for memory access and internal parallelto-serial conversion.

#### **CONNECTION MODE**

In Connection Mode, the addresses of input source for all output channels are stored in the Connect Memory Low. The Connect Memory Low locations are mapped to corresponding 8-bit x 32-channel output. The contents of the Data Memory at the selected address are then transferred to the parallel-to-serial converters. By having the output channel to specify the input channel through the connect memory, input channels can be broadcast to several output channels.

## PROCESSOR MODE

In Processor Mode the CPU writes data to specific Connect Memory Low locations which are to be output on the TX streams. The contents of the Connect Memory Low are transferred to the parallel-to-serial converter one channel before it is to be output and are transmitted each frame to the output until it is changed by the CPU.

## CONTROL

The Connect Memory High bits (Table 4) control the per-channel functions available in the IDT72V8980. Output channels are selected into specific modes such as: Processor Mode or Connection mode and Output Drivers Enabled or in three-state condition. There is also one bit to control the state of the CCO output pin.

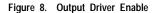

## **OUTPUT DRIVE ENABLE (ODE)**

The ODE pin is the master output control pin. If the ODE input is held LOW all TDM outputs will be placed in high impedance regardless Connect Memory High programming. However, if ODE is HIGH, the contents of Connect Memory High control the output state on a per-channel basis.

#### **DELAY THROUGH THE IDT72V8980**

The transfer of information from the input serial streams to the output serial streams results in a delay through the device. The delay through the IDT72V8980

device varies according to the combination of input and output streams and the movement within the stream from channel to channel. Data received on an input stream must first be stored in Data Memory before it is sent out.

As information enters the IDT72V8980 it must first pass through an internal serial-to-parallel converter. Likewise, before data leaves the device, it must pass through the internal parallel-to-serial converter. This data preparation has an effect on the channel positioning in the frame immediately following the incoming frame—mainly, data cannot leave in the same time slot, on in the time slot immediately following. Therefore, information that is to be output in the same channel position as the information is input, relative to the frame pulse, will be output in the following frame. As well, information switched to the channel immediately following the input channel will not be output in the time slot immediately following but in the next timeslot allocated to the output channel, one frame later.

Whether information can be output during a following timeslot after the information entered the IDT72V8980 depends on which RX stream the channel information enters on and which TX stream the information leaves on. This situation is caused by the order in which input stream information is placed into Data Memory and the order in which stream information is queued for output. Table 1 shows the allowable input/output stream combinations for the minimum 2 channel delay.

## **SOFTWARE CONTROL**

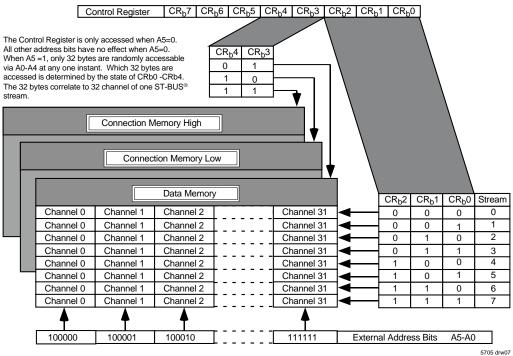

If the A5 address line input is LOW then the IDT72V8980 Internal Control Register is addressed. If A5 input line is high, then the remaining address input lines are used to select the 32 possible channels per input or output stream. The address input lines and the Stream Address bits (STA) of the Control register give the user the capability of selecting all positions of IDT72V8980 Data and Connection memories. The IDT72V8980 memory mapping is illustrated in Table 2 and Figure 3.

The data in the control register consists of Memory Select and Stream Address bits, Split Memory and Processor Mode bits. In Split Memory mode (Bit 7 of the Control register) reads are from the Data Memory and writes are to the Connect Memory as specified by the Memory Select Bits (Bits 4 and 3 of the Control Register). The Memory Select bits allow the Connect Memory High or LOW or the Data Memory to be chosen, and the Stream Address bits define internal memory subsections corresponding to input or output streams.

The Processor Enable bit (bit 6) places EVERY output channel on every output stream in Processor Mode; i.e., the contents of the Connect Memory LOW (CML, see Table 5) are output on the TX output streams once every frame unless the ODE input pin is LOW. If PE bit is HIGH, then the IDT72V8980 behaves as if bits 2 (Channel Source) and 0 (Output Enable) of every Connect Memory High (CMH) locations were set to HIGH, regardless of the actual value. If PE is LOW, then bit 2 and 0 of each Connect Memory High location operates normally. In this case, if bit 2 of the CMH is HIGH, the associated TX output channel is in Processor Mode. If bit 2 of the CMH is LOW, then the contents of the CML define the source information (stream and channel) of the time slot that is to be switched to an output.

4

If the ODE input pin is LOW, then all the serial outputs are high-impedance. If ODE is HIGH, then bit 0 (Output Enable) of the CMH location enables (if HIGH) or disables (if LOW) the output stream and channel.

The contents of bit 1 (CCO) of each Connection Memory High Location (see Table 4) is output on CCO pin once every frame. The CCO pin is a 2.048 Mb/s output, which carries 256 bits. If CCO bit is set HIGH, the corresponding bit on CCO output is transmitted HIGH. If CCO is LOW, the corresponding bit on the CCO output is transmitted in LOW. The contents of the 256 CCO bits of the CMH are transmitted sequentially on to the CCO output pin and are synchronous to the TX streams. To allow for delay in any external control circuitry the contents of the CCO bit is output one channel before the corresponding channel on the TX streams. For example, the contents of CCO bit in position 0 (corresponding to TX0, CH0) is transmitted synchronously with the TX channel 31, bit 7. Bit 1's of CMH for channel 1 of streams 0-7 are output synchronously with TX channel 0 bits 7-0.

## **INITIALIZATION OF THE IDT72V8980**

On initialization or power up, the contents of the Connection Memory High can be in any state. This is a potentially hazardous condition when multiple TX

| Input | Output Stream |

|-------|---------------|

| 0     | 1,2,3,4,5,6,7 |

| 1     | 3,4,5,6,7     |

| 2     | 5,6,7         |

| 3     | 7             |

| 4     | 1,2,3,4,5,6,7 |

| 5     | 3,4,5,6,7     |

| 6     | 5,6,7         |

| 7     | 7             |

Table 1. Input Stream to Output Stream Combinations that can Provide the Minimum 2-Channel Delay

outputs are tied together to form matrices. The ODE pin should be held low on power up to keep all outputs in the high impedance condition until the contents of the CMH are programmed.

During the microprocessor initialization routine, the microprocessor should program the desired active paths through the matrices, and put all other channels into the high impedance state. Care should be taken that no two connected TX outputs drive the bus simultaneously. With the CMH setup, the microprocessor controlling the matrices can bring the ODE signal high to relinquish high impedance state control to the Connection Memory High bits outputs.

The reset pin is designed to be used with board reset circuitry. During reset the TX serial streams will be put into high-impedance and the state of internal registers and counters will be reset. As the connection memory can be in any state after a power up, the ODE pin should be used to hold the TX streams in high-impedance until the per-channel output enable control in the connection memory high is appropriately programmed. The main difference between ODE and reset is, reset alters the state of the registers and counters where as ODE controls only the high-impedance state of the TX streams. RESET input is only provided on the TSSOP and SSOP package.

| A5 | A4 | A3 | A2 | A1 | A0 | HEX ADDRESS | LOCATION                        |

|----|----|----|----|----|----|-------------|---------------------------------|

| 0  | Х  | Х  | Х  | Х  | Х  | 00-1F       | Control Register <sup>(1)</sup> |

| 1  | 0  | 0  | 0  | 0  | 0  | 20          | Channel 0 <sup>(2)</sup>        |

| 1  | 0  | 0  | 0  | 0  | 1  | 21          | Channel 1 <sup>(2)</sup>        |

| •  | ٠  | •  | •  | •  | •  | •           | •                               |

| •  | •  | •  | •  | •  | •  | •           | •                               |

| •  | •  | •  | •  | •  | •  | •           | •                               |

| 1  | 1  | 1  | 1  | 1  | 1  | 3F          | Channel 31 <sup>(2)</sup>       |

NOTES:

1. Writing to the Control Register is the only fast transaction.

2. Memory and stream are specified by the contents of the Control Register.

Table 2. Address Mapping

#### Figure 3. Address Mapping

|     |                                 | Mode Control<br>Bits                                                                                                                                                                                                                                                                                                              | (unused) |         | ry Select<br>Bits |          | n Addres | s Bits                    |                                                  |

|-----|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|-------------------|----------|----------|---------------------------|--------------------------------------------------|

|     |                                 | 7 6                                                                                                                                                                                                                                                                                                                               | 5        | 4       | 3                 | 2        | 1        | 0                         |                                                  |

| Bit | Name                            |                                                                                                                                                                                                                                                                                                                                   |          |         | Des               | cription | l        |                           |                                                  |

| 7   | SM (Split Memory)               | When 1, all subsequent reads are from the Data Memory and writes are to the Connection Memory LOW, except when the Control Register is accessed again. When 0, the Memory Select bits specify the memory for the operations. In either case, the Stream Address Bits select the subsection of the memory which is made available. |          |         |                   |          |          | pecify the memory for the |                                                  |

| 6   | PE (Processor Mode)             | When 1, the contents of the pin is LOW. When 0, the 0                                                                                                                                                                                                                                                                             |          |         |                   |          |          |                           | utput streams except when the ODE hat is output. |

| 5   |                                 | unused                                                                                                                                                                                                                                                                                                                            |          |         |                   |          |          |                           |                                                  |

| 4-3 | MS1-MS0<br>(Memory Select Bits) | 0-0 - Not to be used.<br>0-1 - Data Memory (read<br>1-0 - Connection Memory<br>1-1 - Connection Memory                                                                                                                                                                                                                            | LŐW      | he micr | oprocess          | or port) |          |                           |                                                  |

| 2-0 | STA2-0<br>(Stream Address Bits) | The number expressed in<br>subsection of memory ma                                                                                                                                                                                                                                                                                |          |         |                   |          |          | ut or outp                | out stream which corresponds to the              |

#### Table 3. Control Register Configuration

| No Corresponding Memory<br>- These bits give 0s if readPer Channel Control Bits76543210 |                     |                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|-----------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit                                                                                     | Name                | Description                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 2                                                                                       | CS (Channel Source) | When 1, the contents of the corresponding location in Connection Memory LOW are output on the location's channel and stream. When 0, the contents of the corresponding location in Connection Memory LOW act as an address for the Data Memory and determine the source of the connection to the location's channel and stream. |  |  |  |  |  |

| 1                                                                                       | CCO (CCO Bit)       | This bit is output on the CCO pin one channel early. The CCO bit for stream 0 is output first.                                                                                                                                                                                                                                  |  |  |  |  |  |

| 0                                                                                       | OE (Output Enable)  | If the ODE pin is HIGH and bit 6 of the Control Register is 0, then this bit enables the output drive for the location's channel and stream. This allows individuals channels on individuals streams to be made high-impedance, allowing switching matrices to be constructed. A 1 enables the driver and a 0 disables it.      |  |  |  |  |  |

Table 4. Connection Memory High Register

|                    |                                                                                                                                                                                                                                                                                                                                                                                                    | Stream Address BitsChannel Address Bits76543210                                                                                                                                                                                                                    |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit                | Name                                                                                                                                                                                                                                                                                                                                                                                               | Description                                                                                                                                                                                                                                                        |  |  |  |  |

| 7-5 <sup>(1)</sup> | Stream Address Bits*                                                                                                                                                                                                                                                                                                                                                                               | The number expressed in binary notation on these 3 bits are the number of the stream for the source of the connection.<br>Bit 7 is the most significant bit, e.g., If bit 7 is 1, bit 6 is 0 and bit 5 is 0 then the source of the connection is a channel on RX4. |  |  |  |  |

| 4-0 <sup>(1)</sup> | 4-0 <sup>(1)</sup> Channel Address Bits* The number expressed in binary notation on these 5 bits is the number of the channel which is the source of the connection (the stream where the channel lies is defined by bits 7, 6 and 5). Bit 4 is the most significant bit, e.g., if bit 4 is 1, bit 3 is 0, bit 2 is 0, bit 1 is 1 and bit 0 is 1, then the source of the connection is channel 19. |                                                                                                                                                                                                                                                                    |  |  |  |  |

#### NOTE:

1. If bit 2 of the corresponding Connection HIGH location is 1 or bit 6 of the Control Register is 1, then these entire 8 bits are output on the channel and stream associated with this location. Otherwise, the bits are used as indicated to define the source of the connection which is output on the channel and stream associated with this location.

#### Table 5. Connection Memory Low Register

| Symbol | Parameter                  | Min.      | Max.     | Unit |

|--------|----------------------------|-----------|----------|------|

|        | Vcc - GND                  | -0.3      | 5        | ٧    |

| Vi     | Voltage on Digital Inputs  | GND - 0.3 | Vcc +0.3 | ٧    |

| Vo     | Voltage on Digital Outputs | GND - 0.3 | Vcc +0.3 | ٧    |

| lo     | Current at Digital Outputs |           | 20       | mA   |

| Ts     | Storage Temperature        | -55       | +125     | °C   |

| Pd     | Package Power Dissapation  |           | 1        | W    |

## ABSOLUTE MAXIMUM RATINGS (1)

NOTE:

1. Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

# RECOMMENDED OPERATING CONDITIONS

| Symbol | Parameter                           | Min. | Тур.(1) | Мах. | Unit |

|--------|-------------------------------------|------|---------|------|------|

| Vcc    | Positive Supply                     | 3.0  |         | 3.6  | V    |

| Vi     | Input Voltage                       | 0.7  | _       | Vcc  | V    |

| Тор    | Operating Temperature<br>Commercial | -40  | 25      | +85  | °C   |

NOTE:

1. Typical figures are at 25°C and are for design aid only; not guaranteed and not subject to production testing.

## **DC ELECTRICAL CHARACTERISTICS**

| Symbol | Parameter              | Min. | Тур.(1) | Max. | Units | Test Conditions        |

|--------|------------------------|------|---------|------|-------|------------------------|

| lcc    | Supply Current         | —    | 3       | 5    | mA    | Outputs Unloaded       |

| Vih    | Input High Voltage     | 2.0  |         |      | V     |                        |

| Vil    | Input Low Voltage      | —    |         | 0.8  | V     |                        |

| ١L     | InputLeakage           | —    |         | 15   | μA    | Vibetween GND and Vcc  |

| Сі     | Input Capacitance      |      |         | 10   | pF    |                        |

| Vон    | Output High Voltage    | 2.4  |         | _    | V     | Iон = 10mA             |

| Іон    | Output High Current    | 10   |         |      | mA    | Sourcing. VOH = 2.4V   |

| Vol    | Output Low Voltage     |      |         | 0.4  | V     | Iol = 5mA              |

| IOL    | Output Low Current     | 5    |         | _    | mA    | Sinking. VoL = 0.4V    |

| loz    | High Impedance Leakage |      |         | 5    | μA    | Vo between GND and Vcc |

| Со     | Output Pin Capacitance |      |         | 10   | pF    |                        |

NOTE:

1. Typical figures are at 25°C and are for design aid only; not guaranteed and not subject to production testing.

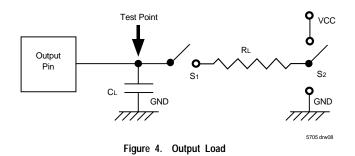

S1 is open circuit except when testing output levels or high impedance states.

S2 is switched to Vcc or GND when testing output levels or high impedance states.

7

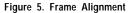

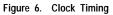

# AC ELECTRICAL CHARACTERISTICS (1)—CLOCK TIMING

| Symbol | Characteristics             | Min. | Typ. <sup>(2)</sup> | Max. | Unit |

|--------|-----------------------------|------|---------------------|------|------|

| tclk   | Clock Period <sup>(3)</sup> |      | 244                 |      | ns   |

| tсн    | Clock Width High            |      | 122                 |      | ns   |

| tCL    | Clock Width Low             | 110  | 122                 | 150  | ns   |

| tctt   | Clock Transition Time       |      | 20                  |      | ns   |

| tFPS   | Frame Pulse Setup Time      | 5    | 20                  | 190  | ns   |

| tFPH   | Frame Pulse Hold Time       | 5    | 20                  | 190  | ns   |

| tFPW   | Frame Pulse Width           |      | 244                 |      | ns   |

NOTE:

1. Timing is over recommended temperature and power supply voltages.

2. Typical figures are at 25°C and are for design aid only; not guaranteed and not subject to production testing.

3. Contents of Connection Memory are not lost if the clock stops, however, TX output go into the high impedance state.

# AC ELECTRICAL CHARACTERISTICS (1)— SERIAL STREAM TIMING

| Symbol     | Characteristics                | Min. | Typ. <sup>(2)</sup> | Max. | Unit   | Test Conditions                        |

|------------|--------------------------------|------|---------------------|------|--------|----------------------------------------|

| ttaz       | TX0-7 Delay - Active to High Z | —    | 30                  | 45   | ns     | $R_L = 1K\Omega^{(3)}, C_L = 150pF$    |

| ttza       | TX0-7 Delay - High Z to Active | —    | 45                  | 60   | ns     | C <sub>L</sub> = 150pF                 |

| <b>TAA</b> | TX0-7 Delay - Active to Active | —    | 40                  | 60   | ns     | C <sub>L</sub> = 150pF                 |

| tтон       | TX0-7 Hold Time                | 20   | 45                  |      | ns     | C <sub>L</sub> = 150pF                 |

| toed       | Output Driver Enable Delay     | —    | 45                  | 60   | ns     | $R_L = 1K\Omega^{(3)}, C_L = 150pF$    |

| tхсн       | External Control Hold Time     | 5    | 50                  |      | ns     | C <sub>L</sub> = 150pF                 |

| txcd       | External Control Delay         | —    | 15                  | 30   | ns     | C <sub>L</sub> = 150pF                 |

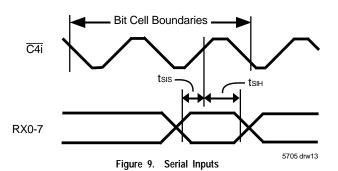

| tsis       | Serial Input Setup Time        | 10   | 20                  | —    | ns     |                                        |

| tsih       | Serial Input Hold Time         | 10   | 20                  | —    | ns     |                                        |

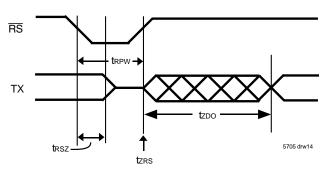

| tRSZ       | Reset to High Z                | 5    | 30                  |      | ns     |                                        |

| tzrs       | High Z to Reset                | 0    |                     | —    | ns     |                                        |

| tzdo       | High Z to Valid Data           |      | 32                  |      | cycles | C4i cycles                             |

| tRPW       | Reset Pulse Width              | 100  |                     |      | ns     | $R_L = 1K\Omega^{(3)}$ , $C_L = 150pF$ |

#### NOTE:

1. Timing is over recommended temperature and power supply voltages.

2. Typical figures are at 25°C and are for design aid only; not guaranteed and not subject to production testing.

3. High Impedance is measured by pulling to the appropriate rail with R<sub>L</sub>, with timing corrected to cancel time taken to discharge C<sub>L</sub>.

# AC ELECTRICAL CHARACTERISTICS (1)—PROCESSOR BUS

| Symbol       | Characteristics             | Min. | Typ. <sup>(2)</sup> | Max. | Unit   | Test Conditions                                 |

|--------------|-----------------------------|------|---------------------|------|--------|-------------------------------------------------|

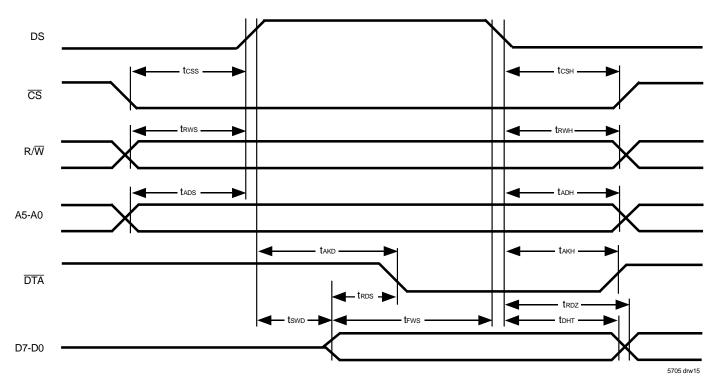

| tcss         | Chip Select Setup Time      | 0    | _                   | —    | ns     |                                                 |

| trws         | Read/Write Setup Time       | 5    | —                   | —    | ns     |                                                 |

| tads         | Address Setup Time          | 5    |                     | —    | ns     |                                                 |

| <b>t</b> akd | Acknowledgment Delay Fast   | _    | 40                  | 60   | ns     | C <sub>L</sub> = 150pF                          |

| <b>t</b> AKD | Acknowledgment Delay Slow   |      |                     | 4.5  | cycles | C4i cycles <sup>(4)</sup>                       |

| tFWS         | Fast Write Data Setup Time  | 10   | —                   | —    | ns     |                                                 |

| tswd         | Slow Write Data Delay       | —    | 2.0                 | 1.7  | cycles | C4i cycles                                      |

| tRDS         | Read Data Setup Time        |      |                     | 0.5  | cycles | $\overline{C4i}$ cycles, C <sub>L</sub> = 150pF |

| <b>t</b> DHT | Data Hold Time Read         | 20   | 50                  | 75   | ns     | $R_{L} = 1K\Omega^{(3)}, C_{L} = 150pF$         |

| <b>t</b> DHT | Data Hold Time Write        | 10   | _                   | —    | ns     |                                                 |

| trdz         | Read Data to High Impedance | 10   | 50                  | —    | ns     | $R_{L} = 1K\Omega^{(3)}, C_{L} = 150pF$         |

| tCSH         | Chip Select Hold Time       | 0    | 5                   | —    | ns     |                                                 |

| trwh         | Read/Write Hold Time        | 0    | 5                   | —    | ns     |                                                 |

| tadh         | Address Hold Time           | 0    | 5                   |      | ns     |                                                 |

| tакн         | Acknowledgment Hold Time    | _    | 20                  | 40   | ns     | $R_{L} = 1K\Omega^{(3)}, C_{L} = 150pF$         |

NOTE:

1. Timing is over recommended temperature and power supply voltages.

2. Typical figures are at 25°C and are for design aid only; not guaranteed and not subject to production testing.

3. High Impedance is measured by pulling to the appropriate rail with  $R_L$ , with timing corrected to cancel time taken to discharge  $C_L$ .

4. Processor accesses are dependent on the C4i clock, and so some things are expressed as multiples of the C4i.

Figure 11. Processor Bus

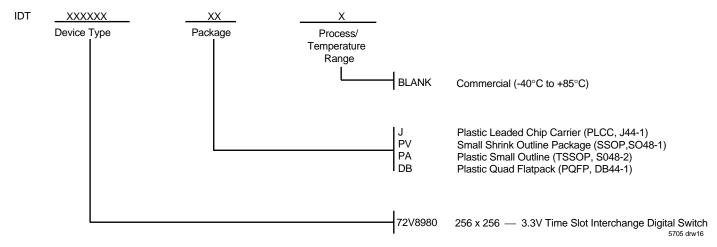

## **ORDERING INFORMATION**

## **DATASHEET DOCUMENT HISTORY**

5/23/2000 8/18/2000 01/24/2001 pgs.1, 2, and 11. pgs. 1, 2 and 11. pgs. 1 and 7.

*CORPORATE HEADQUARTERS* 2975 Stender Way Santa Clara, CA 95054 for SALES: 800-345-7015 or 408-727-6116 fax: 408-492-8674 www.idt.com\*

## for Tech Support: 408-330-1753 email:FIFOhelp@idt.com J Pkg: www.idt.com/docs/PSC4008.pdf PV Pkg: www.idt.com/docs/PSC4029.pdf PA Pkg: www.idt.com/docs/PSC4039.pdf DB Pkg: www.idt.com/docs/PSC4082.pdf

\*To search for sales office near you, please click the sales button found on our home page or dial the 800# above and press 2. The IDT logo is a registered trademark of Integrated Device Technology, Inc. and the ST-BUS\* is a trademark of Mitel Corp.