# Ultralow Noise Precision High Speed Op Amps

### **FEATURES**

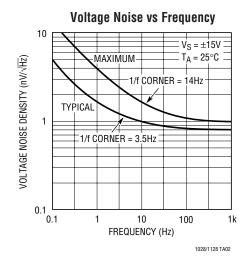

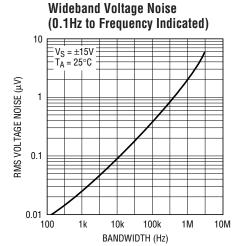

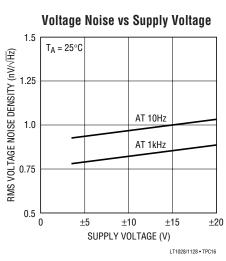

Voltage Noise

1.1nV/ $\sqrt{\text{Hz}}$  Max at 1kHz 0.85nV/ $\sqrt{\text{Hz}}$  Typ at 1kHz 1.0nV/ $\sqrt{\text{Hz}}$  Typ at 10Hz 35nV<sub>P-P</sub> Typ, 0.1Hz to 10Hz

Voltage and Current Noise 100% Tested

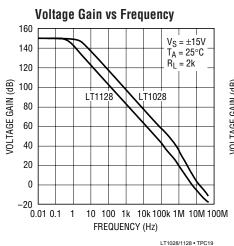

■ Gain-Bandwidth Product LT1028: 50MHz Min

LT1128: 13MHz Min

Slew Rate

LT1028: 11V/µs Min LT1128: 5V/µs Min ■ Offset Voltage: 40µV Max

■ Drift with Temperature: 0.8µV/°C Max

Voltage Gain: 7 Million MinAvailable in 8-Pin SO Package

### **APPLICATIONS**

- Low Noise Frequency Synthesizers

- High Quality Audio

- Infrared Detectors

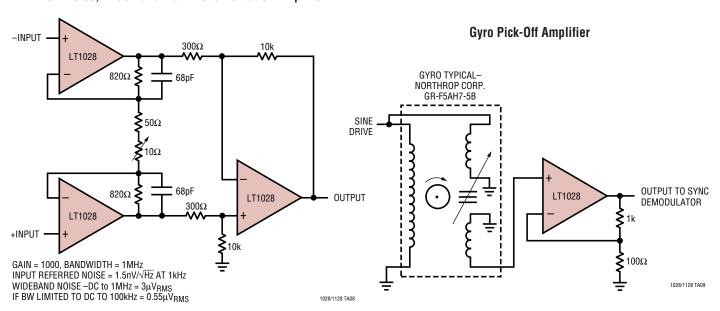

- Accelerometer and Gyro Amplifiers

- 350Ω Bridge Signal Conditioning

- Magnetic Search Coil Amplifiers

- Hydrophone Amplfiers

### DESCRIPTION

The LT®1028(gain of –1 stable)/LT1128(gain of +1 stable) achieve a new standard of excellence in noise performance with 0.85nV/ $\sqrt{\text{Hz}}$  1kHz noise, 1.0nV/ $\sqrt{\text{Hz}}$  10Hz noise. This ultralow noise is combined with excellent high speed specifications (gain-bandwidth product is 75MHz for LT1028, 20MHz for LT1128), distortion-free output, and true precision parameters (0.1 $\mu$ V/°C drift, 10 $\mu$ V offset voltage, 30 million voltage gain). Although the LT1028/LT1128 input stage operates at nearly 1mA of collector current to achieve low voltage noise, input bias current is only 25nA.

The LT1028/LT1128's voltage noise is less than the noise of a  $50\Omega$  resistor. Therefore, even in very low source impedance transducer or audio amplifier applications, the LT1028/LT1128's contribution to total system noise will be negligible.

7, LTC and LT are registered trademarks of Linear Technology Corporation

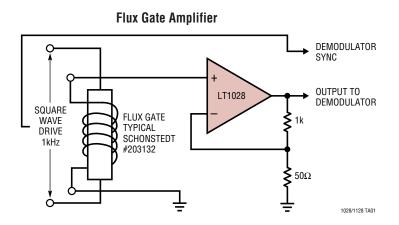

### TYPICAL APPLICATION

## **ABSOLUTE MAXIMUM RATINGS** (Note 1)

| Supply Voltage                      |                     |

|-------------------------------------|---------------------|

| –55°C to 105°C                      | ±22V                |

| 105°C to 125°C                      | ±16V                |

| Differential Input Current (Note 9) | ±25mA               |

| Input Voltage Equa                  | I to Supply Voltage |

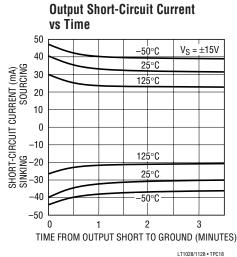

| Output Short Circuit Duration       | Indefinite          |

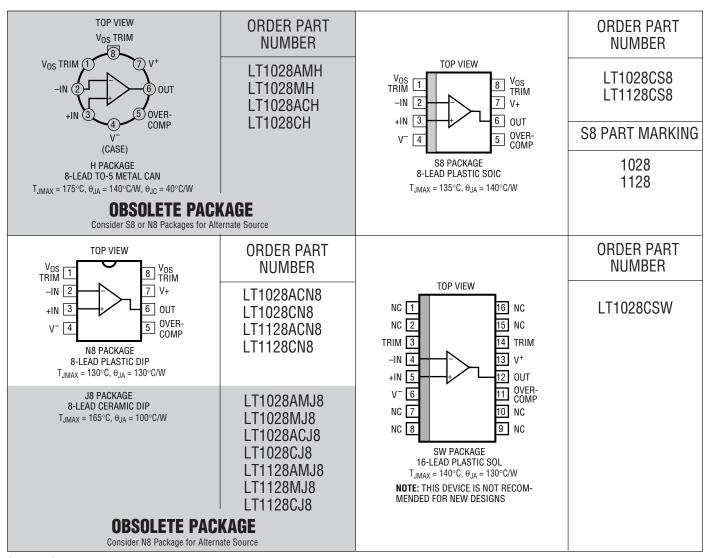

### PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges.

# **ELECTRICAL CHARACTERISTICS** $v_{\text{S}} = \pm 15 \text{V}, \, T_{\text{A}} = 25^{\circ}\text{C}, \, \text{unless otherwise noted}.$

|                     |                               |                                       |        |       | 1028AM<br>1128AM |      |       | 1028M/(<br>1128M/( |      |                   |

|---------------------|-------------------------------|---------------------------------------|--------|-------|------------------|------|-------|--------------------|------|-------------------|

| SYMBOL              | PARAMETER                     | CONDITIONS                            |        | MIN   | TYP              | MAX  | MIN   | TYP                | MAX  | UNITS             |

| $\overline{V_{0S}}$ | Input Offset Voltage          | (Note 2)                              |        |       | 10               | 40   |       | 20                 | 80   | μV                |

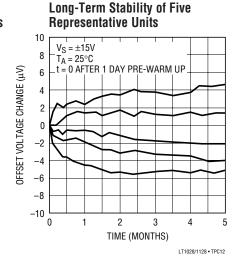

| ΔV <sub>OS</sub>    | Long Term Input Offset        | (Note 3)                              |        |       | 0.3              |      |       | 0.3                |      | μV/Mo             |

| ∆Time               | Voltage Stability             |                                       |        |       |                  |      |       |                    |      |                   |

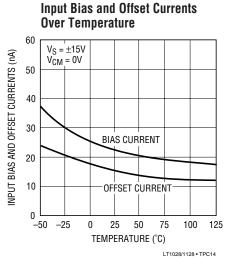

| los                 | Input Offset Current          | $V_{CM} = 0V$                         |        |       | 12               | 50   |       | 18                 | 100  | nA                |

| $I_{B}$             | Input Bias Current            | $V_{CM} = 0V$                         |        |       | ±25              | ±90  |       | ±30                | ±180 | nA                |

| <u>e</u> n          | Input Noise Voltage           | 0.1Hz to 10Hz (Note 4)                |        |       | 35               | 75   |       | 35                 | 90   | nV <sub>P-P</sub> |

|                     | Input Noise Voltage Density   | f <sub>0</sub> = 10Hz (Note 5)        |        |       | 1.00             | 1.7  |       | 1.0                | 1.9  | nV/√Hz            |

|                     |                               | $f_0 = 1000$ Hz, 100% test            |        |       | 0.85             | 1.1  |       | 0.9                | 1.2  | nV/√Hz            |

| In                  | Input Noise Current Density   | f <sub>0</sub> = 10Hz (Note 4 and 6   |        |       | 4.7              | 10.0 |       | 4.7                | 12.0 | pA/√Hz            |

|                     |                               | $f_0 = 1000$ Hz, 100% test            | ed     |       | 1.0              | 1.6  |       | 1.0                | 1.8  | pA/√Hz            |

|                     | Input Resistance              |                                       |        |       | 000              |      |       | 000                |      | Mo                |

|                     | Common Mode Differential Mode |                                       |        |       | 300<br>20        |      |       | 300<br>20          |      | MΩ<br>kΩ          |

|                     | Input Capacitance             |                                       |        |       | 5                |      |       | 5                  |      | pF                |

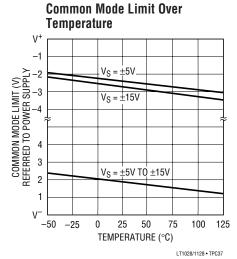

|                     | Input Voltage Range           |                                       |        | ±11.0 | ±12.2            |      | ±11.0 | ±12.2              |      | V                 |

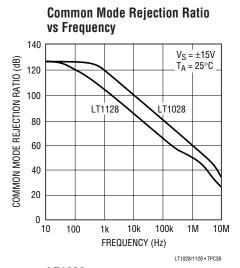

| CMRR                | Common Mode Rejection Ratio   | V <sub>CM</sub> = ±11V                |        | 114   | 126              |      | 110   | 126                |      | dB                |

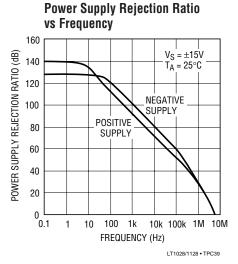

| PSRR                | Power Supply Rejection Ratio  | $V_{S} = \pm 4V \text{ to } \pm 18V$  |        | 117   | 133              |      | 110   | 132                |      | dB                |

| A <sub>VOL</sub>    | Large-Signal Voltage Gain     | $R_1 \ge 2k, V_0 = \pm 12V$           |        | 7.0   | 30.0             |      | 5.0   | 30.0               |      | V/µV              |

| AVUL                | Large dignar voltage dam      | $R_1 \ge 1k$ , $V_0 = \pm 10V$        |        | 5.0   | 20.0             |      | 3.5   | 20.0               |      | V/μV              |

|                     |                               | $R_L \ge 600\Omega$ , $V_0 = \pm 10V$ |        | 3.0   | 15.0             |      | 2.0   | 15.0               |      | V/µV              |

| V <sub>OUT</sub>    | Maximum Output Voltage Swing  | $R_L \ge 2k$                          |        | ±12.3 | ±13.0            |      | ±12.0 | ±13.0              |      | V                 |

|                     |                               | $R_L \ge 600\Omega$                   |        | ±11.0 | ±12.2            |      | ±10.5 | ±12.2              |      | V                 |

| SR                  | Slew Rate                     | A <sub>VCL</sub> = −1                 | LT1028 | 11.0  | 15.0             |      | 11.0  | 15.0               |      | V/µs              |

|                     |                               | A <sub>VCL</sub> = -1                 | LT1128 | 5.0   | 6.0              |      | 4.5   | 6.0                |      | V/µs              |

| GBW                 | Gain-Bandwidth Product        | $f_0 = 20kHz$ (Note 7)                | LT1028 | 50    | 75               |      | 50    | 75                 |      | MHz               |

|                     |                               | f <sub>0</sub> = 200kHz (Note 7)      | LT1128 | 13    | 20               |      | 11    | 20                 |      | MHz               |

| Z <sub>0</sub>      | Open-Loop Output Impedance    | $V_0 = 0, I_0 = 0$                    |        |       | 80               |      |       | 80                 |      | Ω                 |

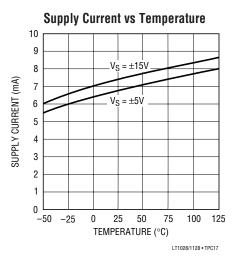

| IS                  | Supply Current                |                                       |        |       | 7.4              | 9.5  |       | 7.6                | 10.5 | mA                |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the temperature range $-55^{\circ}C \le T_A \le 125^{\circ}C$ . $V_S = \pm 15V$ , unless otherwise noted.

|                  |                              |                                        |   |       | T1028A<br>T1128A |      |       | .T1028N<br>.T1128N |      |       |

|------------------|------------------------------|----------------------------------------|---|-------|------------------|------|-------|--------------------|------|-------|

| SYMBOL           | PARAMETER                    | CONDITIONS                             |   | MIN   | TYP              | MAX  | MIN   | TYP                | MAX  | UNITS |

| $V_{OS}$         | Input Offset Voltage         | (Note 2)                               | • |       | 30               | 120  |       | 45                 | 180  | μV    |

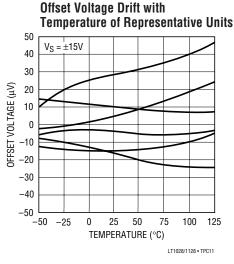

| $\Delta V_{OS}$  | Average Input Offset Drift   | (Note 8)                               | • |       | 0.2              | 0.8  |       | 0.25               | 1.0  | μV/°C |

| ∆Temp            |                              |                                        |   |       |                  |      |       |                    |      |       |

| I <sub>OS</sub>  | Input Offset Current         | V <sub>CM</sub> = 0V                   | • |       | 25               | 90   |       | 30                 | 180  | nA    |

| I <sub>B</sub>   | Input Bias Current           | V <sub>CM</sub> = 0V                   | • |       | ±40              | ±150 |       | ±50                | ±300 | nA    |

|                  | Input Voltage Range          |                                        | • | ±10.3 | ±11.7            |      | ±10.3 | ±11.7              |      | V     |

| CMRR             | Common Mode Rejection Ratio  | $V_{CM} = \pm 10.3V$                   | • | 106   | 122              |      | 100   | 120                |      | dB    |

| PSRR             | Power Supply Rejection Ratio | $V_S = \pm 4.5 V \text{ to } \pm 16 V$ | • | 110   | 130              |      | 104   | 130                |      | dB    |

| A <sub>VOL</sub> | Large-Signal Voltage Gain    | $R_L \ge 2k, V_0 = \pm 10V$            | • | 3.0   | 14.0             |      | 2.0   | 14.0               |      | V/µV  |

|                  |                              | $R_L \ge 1k, V_0 = \pm 10V$            |   | 2.0   | 10.0             |      | 1.5   | 10.0               |      | V/µV  |

| $V_{OUT}$        | Maximum Output Voltage Swing | $R_L \ge 2k$                           | • | ±10.3 | ±11.6            |      | ±10.3 | ±11.6              |      | V     |

| I <sub>S</sub>   | Supply Current               |                                        | • |       | 8.7              | 11.5 |       | 9.0                | 13.0 | mA    |

### **ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the temperature range

$0^{\circ}C \leq T_A \leq 70^{\circ}C$ .  $V_S = \pm 15V$ , unless otherwise noted.

|                                   |                              |                                                            |   |               | T1028A<br>T1128A | _    | l             | LT10280<br>LT11280 |      |              |

|-----------------------------------|------------------------------|------------------------------------------------------------|---|---------------|------------------|------|---------------|--------------------|------|--------------|

| SYMBOL                            | PARAMETER                    | CONDITIONS                                                 |   | MIN           | TYP              | MAX  | MIN           | TYP                | MAX  | UNITS        |

| $V_{OS}$                          | Input Offset Voltage         | (Note 2)                                                   | • |               | 15               | 80   |               | 30                 | 125  | μV           |

| $\Delta V_{OS} \over \Delta Temp$ | Average Input Offset Drift   | (Note 8)                                                   | • |               | 0.1              | 8.0  |               | 0.2                | 1.0  | μV/°C        |

| I <sub>OS</sub>                   | Input Offset Current         | V <sub>CM</sub> = 0V                                       | • |               | 15               | 65   |               | 22                 | 130  | nA           |

| I <sub>B</sub>                    | Input Bias Current           | V <sub>CM</sub> = 0V                                       | • |               | ±30              | ±120 |               | ±40                | ±240 | nA           |

|                                   | Input Voltage Range          |                                                            | • | ±10.5         | ±12.0            |      | ±10.5         | ±12.0              |      | V            |

| CMRR                              | Common Mode Rejection Ratio  | $V_{CM} = \pm 10.5V$                                       | • | 110           | 124              |      | 106           | 124                |      | dB           |

| PSRR                              | Power Supply Rejection Ratio | $V_S = \pm 4.5 \text{V to } \pm 18 \text{V}$               | • | 114           | 132              |      | 107           | 132                |      | dB           |

| A <sub>VOL</sub>                  | Large-Signal Voltage Gain    | $R_L \ge 2k, V_0 = \pm 10V$<br>$R_L \ge 1k, V_0 = \pm 10V$ | • | 5.0<br>4.0    | 25.0<br>18.0     |      | 3.0<br>2.5    | 25.0<br>18.0       |      | V/μV<br>V/μV |

| V <sub>OUT</sub>                  | Maximum Output Voltage Swing | $R_L \ge 2k$<br>$R_L \ge 600\Omega$ (Note 10)              | • | ±11.5<br>±9.5 | ±12.7<br>±11.0   |      | ±11.5<br>±9.0 | ±12.7<br>±10.5     |      | V            |

| I <sub>S</sub>                    | Supply Current               |                                                            | • |               | 8.0              | 10.5 |               | 8.2                | 11.5 | mA           |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the temperature range $-40^{\circ}\text{C} \le T_A \le 85^{\circ}\text{C}$ . $V_S = \pm 15V$ , unless otherwise noted. (Note 11)

|                  |                              |                                              |   |       | T1028A<br>T1128A | -    |       | T10280<br>T11280 |      |       |

|------------------|------------------------------|----------------------------------------------|---|-------|------------------|------|-------|------------------|------|-------|

| SYMBOL           | PARAMETER                    | CONDITIONS                                   |   | MIN   | TYP              | MAX  | MIN   | TYP              | MAX  | UNITS |

| V <sub>OS</sub>  | Input Offset Voltage         |                                              | • |       | 20               | 95   |       | 35               | 150  | μV    |

| $\Delta V_{OS}$  | Average Input Offset Drift   | (Note 8)                                     | • |       | 0.2              | 0.8  |       | 0.25             | 1.0  | μV/°C |

| $\Delta Temp$    |                              |                                              |   |       |                  |      |       |                  |      |       |

| I <sub>0S</sub>  | Input Offset Current         | V <sub>CM</sub> = 0V                         | • |       | 20               | 80   |       | 28               | 160  | nA    |

| I <sub>B</sub>   | Input Bias Current           | $V_{CM} = 0V$                                | • |       | ±35              | ±140 |       | ±45              | ±280 | nA    |

|                  | Input Voltage Range          |                                              | • | ±10.4 | ±11.8            |      | ±10.4 | ±11.8            |      | V     |

| CMRR             | Common Mode Rejection Ratio  | $V_{CM} = \pm 10.5V$                         | • | 108   | 123              |      | 102   | 123              |      | dB    |

| PSRR             | Power Supply Rejection Ratio | $V_S = \pm 4.5 \text{V to } \pm 18 \text{V}$ | • | 112   | 131              |      | 106   | 131              |      | dB    |

| A <sub>VOL</sub> | Large-Signal Voltage Gain    | $R_L \ge 2k, V_0 = \pm 10V$                  | • | 4.0   | 20.0             |      | 2.5   | 20.0             |      | V/µV  |

|                  |                              | $R_L \ge 1 k, V_0 = \pm 10 V$                |   | 3.0   | 14.0             |      | 2.0   | 14.0             |      | V/µV  |

| V <sub>OUT</sub> | Maximum Output Voltage Swing | $R_L \ge 2k$                                 | • | ±11.0 | ±12.5            |      | ±11.0 | ±12.5            |      | V     |

| I <sub>S</sub>   | Supply Current               |                                              | • |       | 8.5              | 11.0 |       | 8.7              | 12.5 | mA    |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

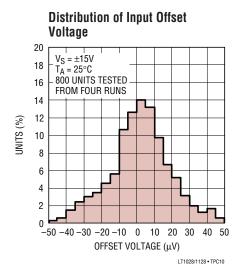

**Note 2:** Input Offset Voltage measurements are performed by automatic test equipment approximately 0.5 sec. after application of power. In addition, at  $T_A = 25^{\circ}C$ , offset voltage is measured with the chip heated to approximately 55°C to account for the chip temperature rise when the device is fully warmed up.

**Note 3:** Long Term Input Offset Voltage Stability refers to the average trend line of Offset Voltage vs. Time over extended periods after the first 30 days of operation. Excluding the initial hour of operation, changes in  $V_{OS}$  during the first 30 days are typically  $2.5\mu V$ .

Note 4: This parameter is tested on a sample basis only.

**Note 5:** 10Hz noise voltage density is sample tested on every lot with the exception of the S8 and S16 packages. Devices 100% tested at 10Hz are available on request.

**Note 6:** Current noise is defined and measured with balanced source resistors. The resultant voltage noise (after subtracting the resistor noise

on an RMS basis) is divided by the sum of the two source resistors to obtain current noise. Maximum 10Hz current noise can be inferred from 100% testing at 1kHz.

**Note 7:** Gain-bandwidth product is not tested. It is guaranteed by design and by inference from the slew rate measurement.

Note 8: This parameter is not 100% tested.

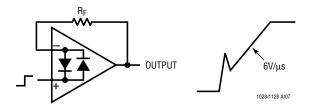

**Note 9:** The inputs are protected by back-to-back diodes. Current-limiting resistors are not used in order to achieve low noise. If differential input voltage exceeds  $\pm 1.8V$ , the input current should be limited to 25mA.

**Note 10:** This parameter guaranteed by design, fully warmed up at  $T_A = 70^{\circ}$ C. It includes chip temperature increase due to supply and load currents

**Note 11:** The LT1028/LT1128 are designed, characterized and expected to meet these extended temperature limits, but are not tested at -40°C and 85°C. Guaranteed I grade parts are available. Consult factory.

#### **10Hz Voltage Noise Distribution** 180 $V_S = \pm 15V$ $T_A = 25^{\circ}C$ 500 UNITS 160 140 MEASURED FROM 4 RUNS 120 NUMBER OF UNITS 100 80 60 40 20 0 0.8 1.0 1.2 1.4 1.6 1.8 2.0 0.6 VOLTAGE NOISE DENSITY (nV/√Hz) LT1020/1120 • TPC01

#### Wideband Noise, DC to 20kHz

VERTICAL SCALE = 0.5μV/DIV HORIZONTAL SCALE = 0.5ms/DIV

LT1028/1128 • TPC03

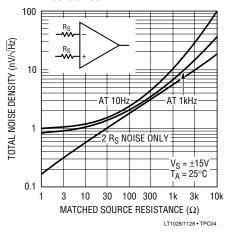

#### Total Noise vs Matched Source Resistance

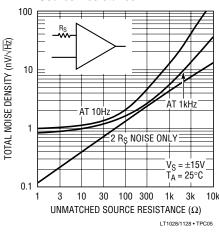

Total Noise vs Unmatched Source Resistance

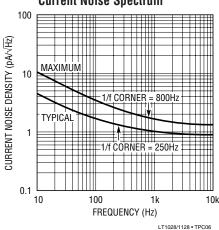

**Current Noise Spectrum**

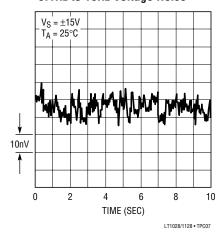

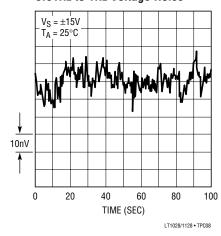

#### 0.1Hz to 10Hz Voltage Noise

#### 0.01Hz to 1Hz Voltage Noise

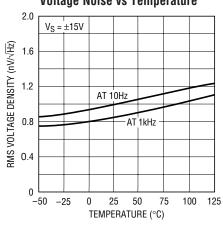

**Voltage Noise vs Temperature**

LT1028/1128 • TPC09

LT1028/1128 • TPC22

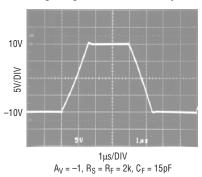

LT1028 **Large-Signal Transient Response**

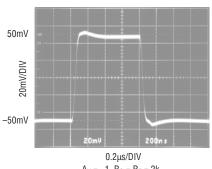

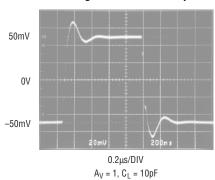

LT1028 **Small-Signal Transient Response**

$A_V = -1$ ,  $R_S = R_F = 2k$   $C_F = 15pF$ ,  $C_L = 80pF$

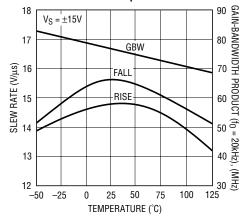

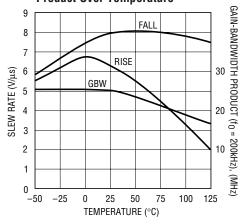

LT1028 Slew Rate, Gain-Bandwidth **Product Over Temperature**

LT1028/1128 • TPC30

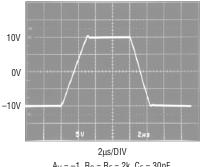

LT1128 **Large-Signal Transient Response**

$A_V = -1$ ,  $R_S = R_F = 2k$ ,  $C_F = 30pF$

LT1128 **Small-Signal Transient Response**

LT1128 Slew Rate, Gain-Bandwidth **Product Over Temperature**

LT1028/1128 • TPC33

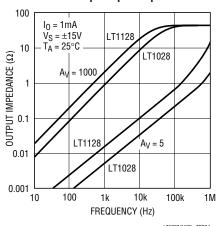

**Closed-Loop Output Impedance**

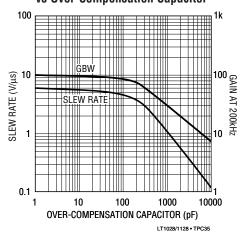

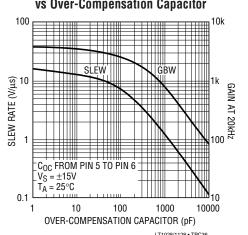

LT1128 Slew Rate, Gain-Bandwidth Product vs Over-Compensation Capacitor

LT1028 Slew Rate, Gain-Bandwidth Product vs Over-Compensation Capacitor

LT1028/1128 • TPC36

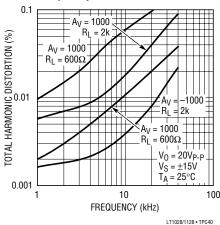

LT1028 Total Harmonic Distortion vs Frequency and Load Resistance

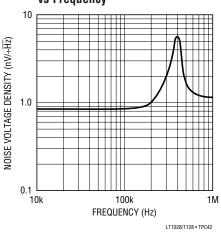

High Frequency Voltage Noise vs Frequency

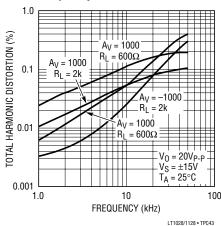

LT1128 Total Harmonic Distortion vs Frequency and Load Resistance

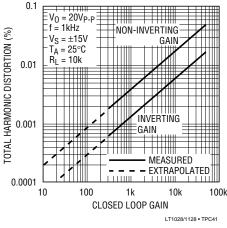

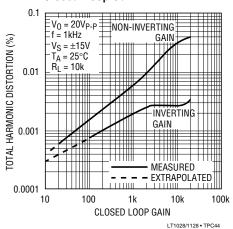

LT1128 Total Harmonic Distortion vs Closed-Loop Gain

### **APPLICATIONS INFORMATION-NOIS€**

#### **Voltage Noise vs Current Noise**

The LT1028/LT1128's less than  $1nV/\sqrt{Hz}$  voltage noise is three times better than the lowest voltage noise heretofore available (on the LT1007/1037). A necessary condition for such low voltage noise is operating the input transistors at nearly 1mA of collector currents, because voltage noise is inversely proportional to the square root of the collector current. Current noise, however, is directly proportional to the square root of the collector current. Consequently, the LT1028/LT1128's current noise is significantly higher than on most monolithic op amps.

Therefore, to realize truly low noise performance it is important to understand the interaction between voltage noise  $(e_n)$ , current noise  $(I_n)$  and resistor noise  $(r_n)$ .

#### **Total Noise vs Source Resistance**

The total input referred noise of an op amp is given by

$$e_t = [e_n^2 + r_n^2 + (I_n R_{eq})^2]^{1/2}$$

where  $R_{eq}$  is the total equivalent source resistance at the two inputs, and  $% \left( 1\right) =\left( 1\right) \left( 1\right) \left$

$$r_n = \sqrt{4kTR_{eq}} = 0.13\sqrt{R_{eq}}$$

in nV/ $\sqrt{Hz}$  at 25°C

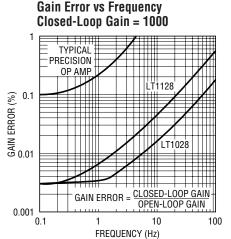

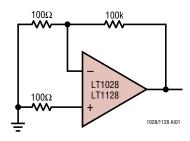

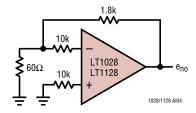

As a numerical example, consider the total noise at 1kHz of the gain 1000 amplifier shown below.

$$\begin{split} R_{eq} &= 100\Omega + 100\Omega \mid \mid 100k \approx 200\Omega \\ r_n &= 0.13\sqrt{200} = 1.84 \text{nV} \sqrt{\text{Hz}} \\ e_n &= 0.85 \text{nV} \sqrt{\text{Hz}} \\ I_n &= 1.0 \text{pA} / \sqrt{\text{Hz}} \\ e_t &= \left[0.85^2 + 1.84^2 + (1.0 \times 0.2)^2\right]^{1/2} = 2.04 \text{nV} / \sqrt{\text{Hz}} \\ \text{Output noise} &= 1000 \ e_t = 2.04 \mu \text{V} / \sqrt{\text{Hz}} \end{split}$$

At very low source resistance ( $R_{eq} < 40\Omega$ ) voltage noise dominates. As  $R_{eq}$  is increased resistor noise becomes the

largest term, as in the example above, and the LT1028/LT1128's voltage noise becomes negligible. As  $R_{eq}$  is further increased, current noise becomes important. At 1kHz, when  $R_{eq}$  is in excess of 20k, the current noise component is larger than the resistor noise. The total noise versus matched source resistance plot illustrates the above calculations.

The plot also shows that current noise is more dominant at low frequencies, such as 10Hz. This is because resistor noise is flat with frequency, while the 1/f corner of current noise is typically at 250Hz. At 10Hz when  $R_{eq} > 1k$ , the current noise term will exceed the resistor noise.

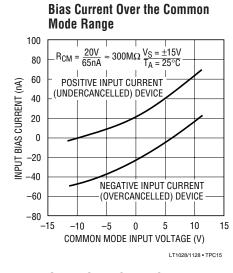

When the source resistance is unmatched, the total noise versus unmatched source resistance plot should be consulted. Note that total noise is lower at source resistances below 1k because the resistor noise contribution is less. When  $R_{\rm S} > 1k$  total noise is not improved, however. This is because bias current cancellation is used to reduce input bias current. The cancellation circuitry injects two correlated current noise components into the two inputs. With matched source resistors the injected current noise creates a common-mode voltage noise and gets rejected by the amplifier. With source resistance in one input only, the cancellation noise is added to the amplifier's inherent noise.

In summary, the LT1028/LT1128 are the optimum amplifiers for noise performance, provided that the source resistance is kept low. The following table depicts which op amp manufactured by Linear Technology should be used to minimize noise, as the source resistance is increased beyond the LT1028/LT1128's level of usefulness.

Best Op Amp for Lowest Total Noise vs Source Resistance

| SOURCE RESIS-              | BEST OP AMP       |                |  |  |  |  |

|----------------------------|-------------------|----------------|--|--|--|--|

| TANCE( $\Omega$ ) (Note 1) | AT LOW FREQ(10Hz) | WIDEBAND(1kHz) |  |  |  |  |

| 0 to 400                   | LT1028/LT1128     | LT1028/LT1128  |  |  |  |  |

| 400 to 4k                  | LT1007/1037       | LT1028/LT1128  |  |  |  |  |

| 4k to 40k                  | LT1001            | LT1007/1037    |  |  |  |  |

| 40k to 500k                | LT1012            | LT1001         |  |  |  |  |

| 500k to 5M                 | LT1012 or LT1055  | LT1012         |  |  |  |  |

| >5M                        | LT1055            | LT1055         |  |  |  |  |

Note 1: Source resistance is defined as matched or unmatched, e.g.,  $R_S = 1k$  means: 1k at each input, or 1k at one input and zero at the other.

### APPLICATIONS INFORMATION—NOIS€

#### Noise Testing - Voltage Noise

The LT1028/LT1128's RMS voltage noise density can be accurately measured using the Quan Tech Noise Analyzer, Model 5173 or an equivalent noise tester. Care should be taken, however, to subtract the noise of the source resistor used. Prefabricated test cards for the Model 5173 set the device under test in a closed-loop gain of 31 with a  $60\Omega$  source resistor and a 1.8k feedback resistor. The noise of this resistor combination is  $0.13\sqrt{58} = 1.0\text{nV}/\sqrt{\text{Hz}}$ . An LT1028/LT1128 with  $0.85\text{nV}/\sqrt{\text{Hz}}$  noise will read  $(0.85^2 + 1.0^2)^{1/2} = 1.31\text{nV}/\sqrt{\text{Hz}}$ . For better resolution, the resistors should be replaced with a  $10\Omega$  source and  $300\Omega$  feedback resistor. Even a  $10\Omega$  resistor will show an apparent noise which is 8% to 10% too high.

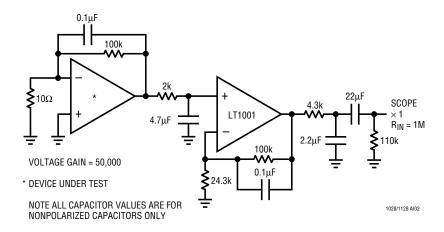

The 0.1Hz to 10Hz peak-to-peak noise of the LT1028/LT1128 is measured in the test circuit shown. The frequency response of this noise tester indicates that the 0.1Hz corner is defined by only one zero. The test time to measure 0.1Hz to 10Hz noise should not exceed 10 seconds, as this time limit acts as an additional zero to eliminate noise contributions from the frequency band below 0.1Hz.

Measuring the typical 35nV peak-to-peak noise performance of the LT1028/LT1128 requires special test precautions:

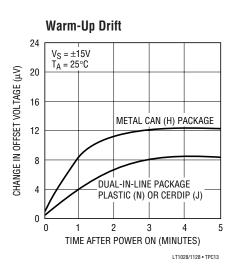

- (a) The device should be warmed up for at least five minutes. As the op amp warms up, its offset voltage changes typically  $10\mu V$  due to its chip temperature increasing  $30^{\circ}C$  to  $40^{\circ}C$  from the moment the power supplies are turned on. In the 10 second measurement interval these temperature-induced effects can easily exceed tens of nanovolts.

- (b) For similar reasons, the device must be well shielded from air current to eliminate the possibility of thermoelectric effects in excess of a few nanovolts, which would invalidate the measurements.

- (c) Sudden motion in the vicinity of the device can also "feedthrough" to increase the observed noise.

A noise-voltage density test is recommended when measuring noise on a large number of units. A 10Hz noise-voltage density measurement will correlate well with a 0.1Hz to 10Hz peak-to-peak noise reading since both results are determined by the white noise and the location of the 1/f corner frequency.

#### 0.1Hz to 10Hz Noise Test Circuit

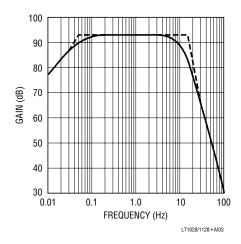

#### 0.1Hz to 10Hz Peak-to-Peak Noise Tester Frequency Response

### **APPLICATIONS INFORMATION-NOIS€**

### Noise Testing - Current Noise

Current noise density  $(I_n)$  is defined by the following formula, and can be measured in the circuit shown:

$$I_{n} = \frac{\left[e_{n0}^{2} - (31 \times 18.4 \text{nV}/\sqrt{\text{Hz}})^{2}\right]^{1/2}}{20 \text{k} \times 31}$$

If the Quan Tech Model 5173 is used, the noise reading is input-referred, therefore the result should not be divided by 31; the resistor noise should not be multiplied by 31.

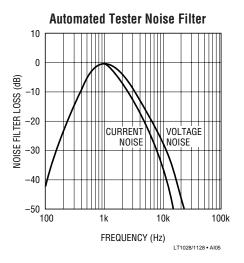

#### 100% Noise Testing

The 1kHz voltage and current noise is 100% tested on the LT1028/LT1128 as part of automated testing; the approximate frequency response of the filters is shown. The limits on the automated testing are established by extensive correlation tests on units measured with the Quan Tech Model 5173.

10Hz voltage noise density is sample tested on every lot. Devices 100% tested at 10Hz are available on request for an additional charge.

10Hz current noise is not tested on every lot but it can be inferred from 100% testing at 1kHz. A look at the current noise spectrum plot will substantiate this statement. The only way 10Hz current noise can exceed the guaranteed limits is if its 1/f corner is higher than 800Hz and/or its white noise is high. If that is the case then the 1kHz test will fail.

### APPLICATIONS INFORMATION

#### General

The LT1028/LT1128 series devices may be inserted directly into OP-07, OP-27, OP-37, LT1007 and LT1037 sockets with or without removal of external nulling components. In addition, the LT1028/LT1128 may be fitted to 5534 sockets with the removal of external compensation components.

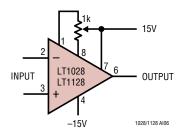

#### Offset Voltage Adjustment

The input offset voltage of the LT1028/LT1128 and its drift with temperature, are permanently trimmed at wafer testing to a low level. However, if further adjustment of  $V_{OS}$  is necessary, the use of a 1k nulling potentiometer will not degrade drift with temperature. Trimming to a value other

than zero creates a drift of  $(V_{OS}/300)\mu V/^{\circ}C$ , e.g., if  $V_{OS}$  is adjusted to  $300\mu V$ , the change in drift will be  $1\mu V/^{\circ}C$ .

The adjustment range with a 1k pot is approximately +1.1mV.

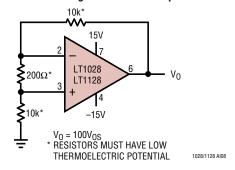

#### Offset Voltage and Drift

Thermocouple effects, caused by temperature gradients across dissimilar metals at the contacts to the input

### APPLICATIONS INFORMATION

terminals, can exceed the inherent drift of the amplifier unless proper care is exercised. Air currents should be minimized, package leads should be short, the two input leads should be close together and maintained at the same temperature.

The circuit shown to measure offset voltage is also used as the burn-in configuration for the LT1028/LT1128.

#### Test Circuit for Offset Voltage and Offset Voltage Drift with Temperature

### **Unity-Gain Buffer Applications (LT1128 Only)**

When  $R_F \le 100\Omega$  and the input is driven with a fast, large-signal pulse (>1V), the output waveform will look as shown in the pulsed operation diagram.

During the fast feedthrough-like portion of the output, the input protection diodes effectively short the output to the input and a current, limited only by the output short-circuit protection, will be drawn by the signal generator. With  $R_F \geq 500\Omega,$  the output is capable of handling the current requirements (I $_L \leq 20 \text{mA}$  at 10V) and the amplifier stays in its active mode and a smooth transition will occur.

As with all operational amplifiers when  $R_F > 2k$ , a pole will be created with  $R_F$  and the amplifier's input capacitance, creating additional phase shift and reducing the phase margin. A small capacitor (20pF to 50pF) in parallel with  $R_F$  will eliminate this problem.

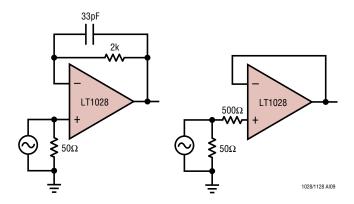

#### Frequency Response

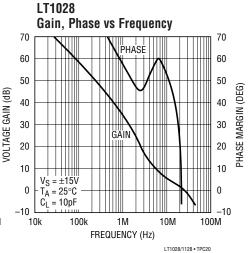

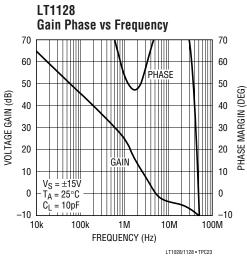

The LT1028's Gain, Phase vs Frequency plot indicates that the device is stable in closed-loop gains greater than +2 or -1 because phase margin is about  $50^{\circ}$  at an open-loop gain of 6dB. In the voltage follower configuration phase margin seems inadequate. This is indeed true when the output is shorted to the inverting input and the noninverting input is driven from a  $50\Omega$  source impedance. However, when feedback is through a parallel R-C network (provided  $C_F < 68 pF$ ), the LT1028 will be stable because of interaction between the input resistance and capacitance and the feedback network. Larger source resistance at the noninverting input has a similar effect. The following voltage follower configurations are stable:

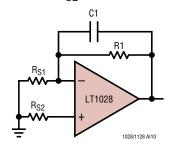

Another configuration which requires unity-gain stability is shown below. When  $C_F$  is large enough to effectively short the output to the input at 15 MHz, oscillations can occur. The insertion of  $R_{S2} \geq 500\Omega$  will prevent the LT1028 from oscillating. When  $R_{S1} \geq 500\Omega$ , the additional noise contribution due to the presence of  $R_{S2}$  will be minimal. When  $R_{S1} \leq 100\Omega$ ,  $R_{S2}$  is not necessary, because  $R_{S1}$  represents a heavy load on the output through the  $C_F$  short. When  $100\Omega < R_{S1} < 500\Omega$ ,  $R_{S2}$  should match  $R_{S1}$ . For example,  $R_{S1} = R_{S2} = 300\Omega$  will be stable. The noise increase due to  $R_{S2}$  is 40%.

### APPLICATIONS INFORMATION

If C<sub>F</sub> is only used to cut noise bandwidth, a similar effect can be achieved using the over-compensation terminal.

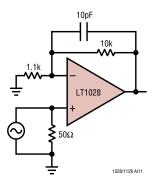

The Gain, Phase plot also shows that phase margin is about 45° at gain of 10 (20dB). The following configura-

tion has a high ( $\approx$ 70%) overshoot without the 10pF capacitor because of additional phase shift caused by the feedback resistor – input capacitance pole. The presence of the 10pF capacitor cancels this pole and reduces overshoot to 5%.

#### **Over-Compensation**

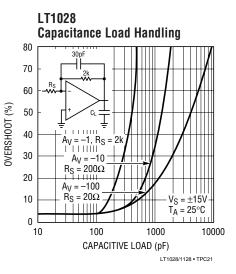

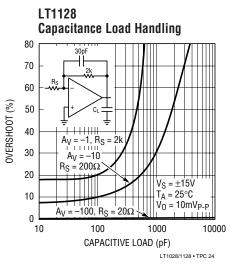

The LT1028/LT1128 are equipped with a frequency over-compensation terminal (Pin 5). A capacitor connected between Pin 5 and the output will reduce noise bandwidth. Details are shown on the Slew Rate, Gain-Bandwidth Product vs Over-Compensation Capacitor plot. An additional benefit is increased capacitive load handling capability.

### TYPICAL APPLICATIONS

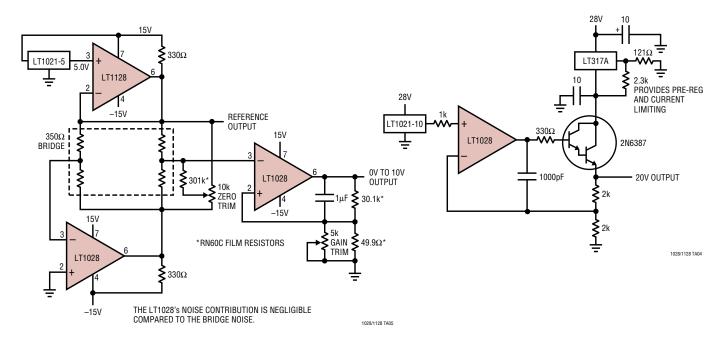

Strain Gauge Signal Conditioner with Bridge Excitation

#### Low Noise Voltage Regulator

### TYPICAL APPLICATIONS

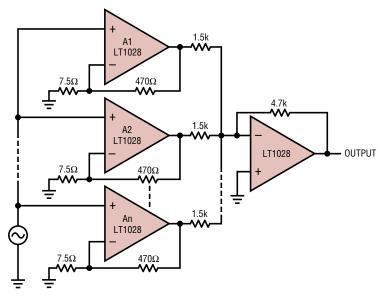

#### **Paralleling Amplifiers to Reduce Voltage Noise**

- 1. ASSUME VOLTAGE NOISE OF LT1028 AND 7.5 $\Omega$  SOURCE RESISTOR = 0.9nV/ $\sqrt{\text{Hz}}$ .

- 2. GAIN WITH n LT1028s IN PARALLEL =  $n \times 200$ . 3. OUTPUT NOISE =  $\sqrt{n} \times 200 \times 0.9$ nV/ $\sqrt{\text{Hz}}$ .

- 3. OUTPUT NOISE =  $\sqrt{\ln \times 200 \times 0.5}$  NOISE =  $\frac{0.9}{\ln \times 200} = \frac{0.9}{\sqrt{n}} \text{ nV/}\sqrt{\text{Hz}}$ .

- 5. NOISE CURRENT AT INPUT INCREASES  $\sqrt{n}$  TIMES.

- 6. IF n = 5, GAIN = 1000, BANDWIDTH = 1MHz, RMS NOISE, DC TO 1MHz =  $\frac{2\mu V}{\sqrt{r}}$  = 0.9 $\mu$ V. 1028/1128 TA03

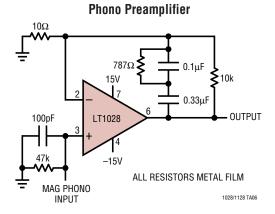

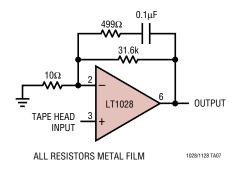

#### **Tape Head Amplifier**

#### Low Noise, Wide Bandwidth Instrumentation Amplifier

### TYPICAL APPLICATIONS

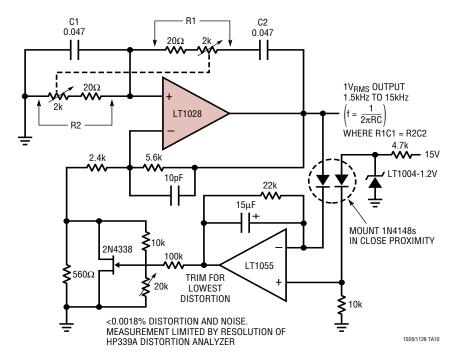

#### Super Low Distortion Variable Sine Wave Oscillator

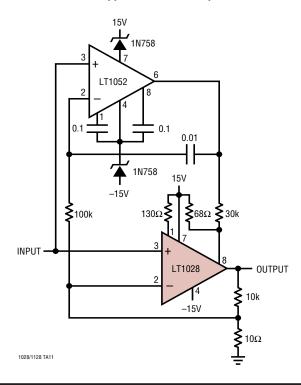

#### **Chopper-Stabilized Amplifier**

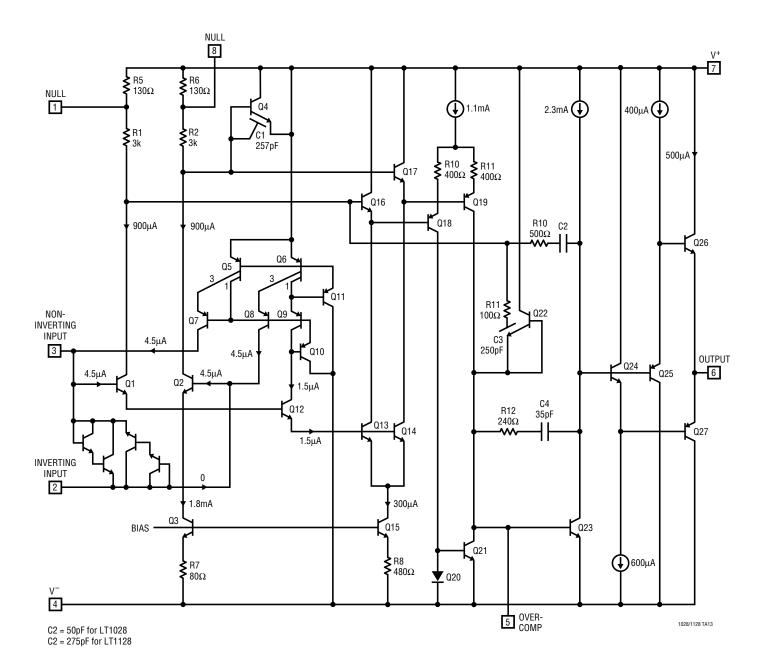

# **SCHEMATIC DIAGRAM**

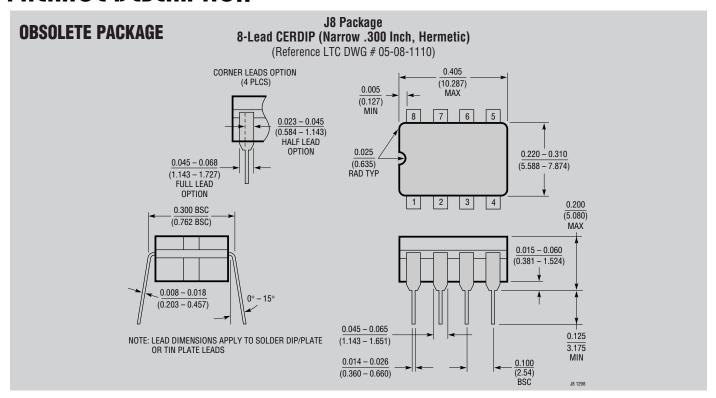

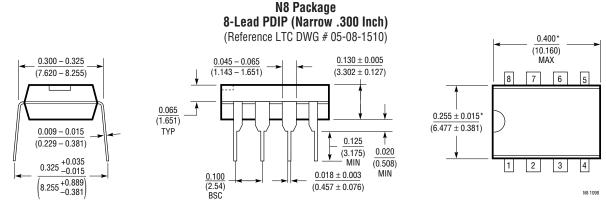

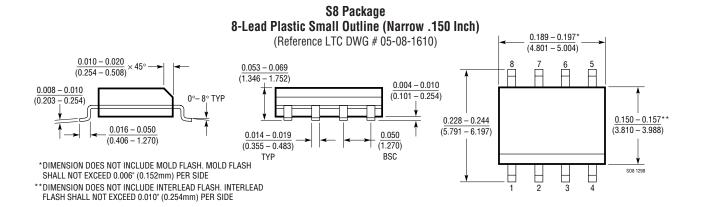

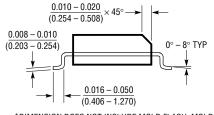

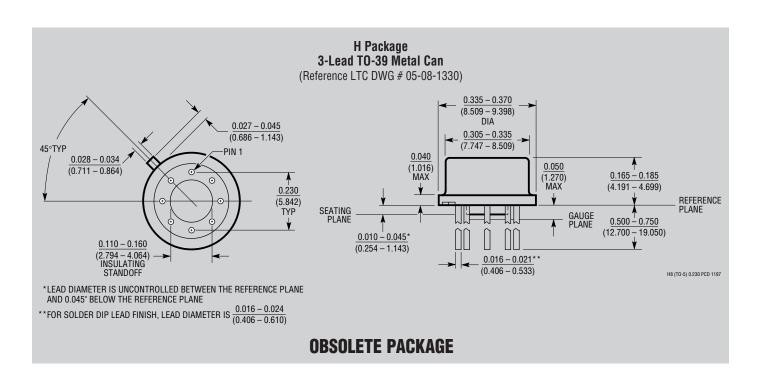

### PACKAGE DESCRIPTION

<sup>\*</sup>THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.010 INCH (0.254mm)

### PACKAGE DESCRIPTION

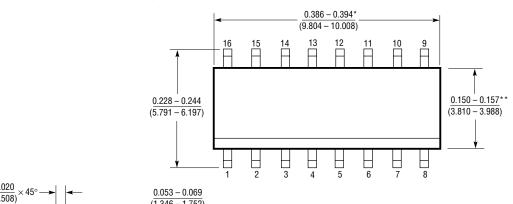

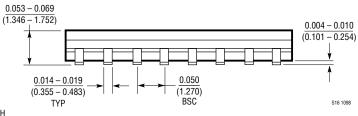

#### S Package 16-Lead Plastic Small Outline (Narrow .150 Inch)

(Reference LTC DWG # 05-08-1610)

- $^{\star}$  DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

- \*\*DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

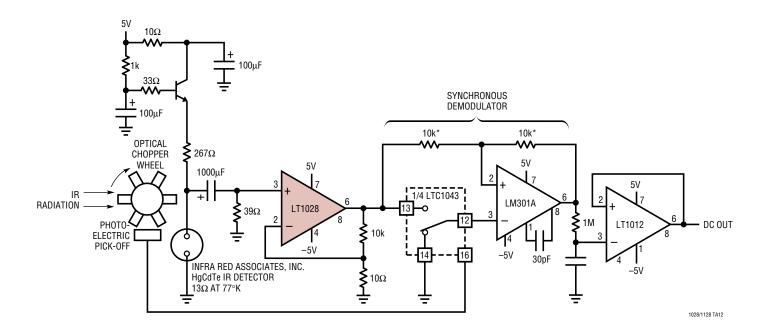

### TYPICAL APPLICATION

#### **Low Noise Infrared Detector**

# **RELATED PARTS**

| PART NUMBER   | DESCRIPTION                               | COMMENTS                                            |

|---------------|-------------------------------------------|-----------------------------------------------------|

| LT1806/LT1807 | 325MHz, 3.5nV/√Hz Single and Dual Op Amps | Slew Rate = 140V/µs, Low Distortion at 5MHz: -80dBc |