# LOW SKEW CLOCK DRIVER/ BUFFER FOR MOBILE PC WITH FOUR SO-DIMMS

## FEATURES:

- 1 to 10 output buffer/driver

- Tri-state pin for testing

- I<sup>2</sup>C programming capability

- Power Supply Voltage 3.3V ±5%

- Low Skew Outputs (<200ps)

- Multiple VDD and GND for noise reduction

- 28 Pin SSOP package

### DESCRIPTION

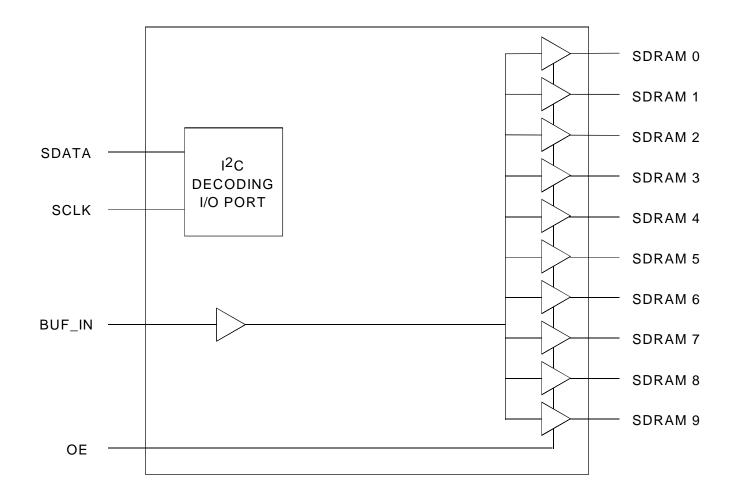

The QS5810 is a high speed, low noise 1-10 non-inverting buffer designed for SDRAM clock buffer applications. Out of the 10 outputs,8 could be used to drive up to four SDRAM SO-DIMMS, and the remaining can be used for external feedback to a PLL stage for synchronization to master clock.

The QS5810 also includes an I<sup>2</sup>C interface, which can enable or disable each output clock driver. By turning the outputs on and off, I<sup>2</sup>C will aid in reducing the Electro Magnetic Interference (EMI).

# **FUNCTIONAL BLOCK DIAGRAM**

1

### INDUSTRIAL TEMPERATURE RANGE

### **APRIL 2000**

#### INDUSTRIAL TEMPERATURE RANGE

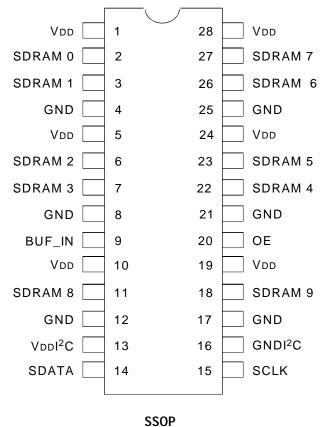

### **PIN CONFIGURATION**

TOP VIEW

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Symbol | Description                            | Max.            | Unit |

|--------|----------------------------------------|-----------------|------|

|        | Supply Voltage to Ground               | – 0.5 to 4.6V   | V    |

|        | DC Output Voltage Vout                 | – 0.5 to + 4.6V | V    |

|        | DC Output Voltage VIN                  | – 0.5 to + 4.6  | V    |

|        | DC Input Diode Current with VI < 0     | - 20            | mA   |

|        | Maximum Power Dissipation at TA = 85°C | 600             | mW   |

|        | TSTG Storage Temperature               | -65 to 150      | °C   |

#### NOTE:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **PIN DESCRIPTION**

| Pin Name            | Description                                                                                                                 |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SDRAM (0:3)         | SDRAM Byte 0 Clock Outputs.                                                                                                 |  |  |  |

| SDRAM (4:7)         | SDRAM Byte 1 Clock Outputs.                                                                                                 |  |  |  |

| SDRAM (8:9)         | SDRAM Byte 2 Clock Outputs.                                                                                                 |  |  |  |

| BUF_IN              | Input for Buffers.                                                                                                          |  |  |  |

| SDATA               | I <sup>2</sup> C Data Input. It has 100k $\Omega$ internal pull up to V <sub>DD</sub> .                                     |  |  |  |

| SCLK                | I <sup>2</sup> C Data Input. It has 100k $\Omega$ internal pull up to VDD.                                                  |  |  |  |

| OE                  | Tri-State Output Enable. When asserted LOW, clock outputs are high impedance. It has 100k $\Omega$ internal pull up to VDD. |  |  |  |

| Vdd                 | 3.3V power supply for output buffers.                                                                                       |  |  |  |

| GND                 | Ground for output buffers.                                                                                                  |  |  |  |

| GNDI <sup>2</sup> C | Ground for I <sup>2</sup> C circuitry.                                                                                      |  |  |  |

| Vddl <sup>2</sup> C | 3.3V Power Supply for I <sup>2</sup> C circuitry.                                                                           |  |  |  |

# DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified: Operating Condition:  $TA = -40^{\circ}C$  to  $+85^{\circ}C$

| Symbol              | Parameter                | Test Conditions                                                | Min.  | Typ. <sup>(1)</sup> | Max. | Unit |

|---------------------|--------------------------|----------------------------------------------------------------|-------|---------------------|------|------|

| Vih                 | Input HIGH Voltage Level | For all Inputs                                                 | 2     | -                   |      | V    |

| VIL                 | Input LOW Voltage Level  | For all inputs except I <sup>2</sup> C inputs (SDATA and SCLK) | -     | _                   | 0.8  | V    |

|                     |                          | I <sup>2</sup> C Inputs (SDATA and SCLK)                       | -     | _                   | 0.7  |      |

| Ін                  | Input High Current       | VIN = VDD                                                      | - 5   | _                   | 5    | μA   |

| lil                 | Input Low Current        | VIN = 0V: BUF_IN                                               | - 5   | _                   | 5    | μA   |

|                     |                          | VIN = 0V; OE, SDATA, SCLK                                      | - 100 | _                   | 0    |      |

|                     |                          | CL = 0pF; fin@66.66MHz <sup>(1)</sup>                          | _     | 50                  | 70   |      |

|                     |                          | CL = 0pF; fin@100MHz <sup>(1)</sup>                            | _     | 75                  | 105  | mA   |

| Idd                 | Supply Current           | CL = 30pF; fin@66.66MHz <sup>(1)</sup>                         | _     | 110                 | 130  |      |

|                     |                          | $C_L = 30pF; f_{IN}@100MHz^{(1)}$                              | _     | 165                 | 195  |      |

|                     |                          | BUF_IN 0 = GND or VDD, all other inputs to VDD                 | _     | _                   | 500  | μA   |

| Vон                 | Output High Voltage      | SDRAM (0:9) Іон = -36mA                                        | 2.4   | _                   | _    | V    |

| Vol                 | Output Low Voltage       | SDRAM (0:9) IOL = 25mA                                         | _     | _                   | 0.4  | V    |

| Voll <sup>2</sup> C | Output Low Voltage       | SDATA Ioli <sup>2</sup> C = 3mA                                | -     | -                   | 0.4  | V    |

#### NOTE:

1. Typical values are at Vcc = 3.3V, +25°C ambient.

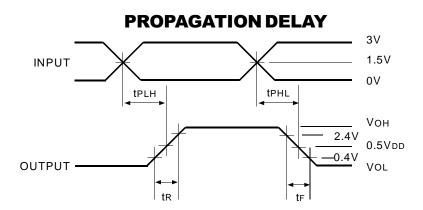

## AC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

| Symbol       | Parameter                           | Test Conditions                            | Min. | Typ. <sup>(1)</sup> | Max. | Unit |

|--------------|-------------------------------------|--------------------------------------------|------|---------------------|------|------|

| tR           | Rise Time <sup>(1)</sup>            | 0.4V to 2.4V; CL = 30pF                    |      | -                   | 2.2  | ns   |

| Tf           | Fall Time <sup>(1)</sup>            | 2.4V to 0.4V; CL = 30pF                    | _    | —                   | 2.2  | ns   |

| Dt           | Duty Cycle <sup>(1)</sup>           | VT = 1.5V; CL = 30pF, with 50% Input Clock | 45   | 50                  | 55   | %    |

| Тѕк          | Skew (output-output) <sup>(1)</sup> | VT = 1.5V; CL = 30pF for all outputs       | _    | —                   | 200  | ps   |

| TPHL or TPLH | Propagation Delay                   | VT = 1.5V                                  | _    | —                   | 6    | ns   |

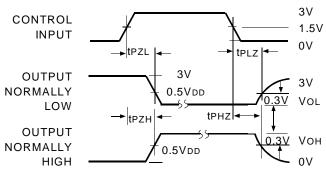

| TPZL or TPZH | Enable Delay, OE to SDRAM           | VT = 1.5V                                  | _    | —                   | 8    | ns   |

| TPLZ or TPHZ | Disable Delay, OE to SDRAM          | VT = 1.5V                                  | _    | —                   | 8    | ns   |

# **OPERATING CHARACTERISTICS**, TA = 25°C

| Symbol | Parameter             | Min.  | Тур. | Max.  | Unit |

|--------|-----------------------|-------|------|-------|------|

| Vdd    | Power Supply Voltage  | 3.135 | 3.3  | 3.465 | V    |

| TA     | Operating Temperature | -40   | 25   | 85    | °C   |

| CL     | Load Capacitance      | —     | —    | 30    | pF   |

| CIN    | Input Capacitance     | _     | _    | 15    | pF   |

## I<sup>2</sup>C SERIAL INTERFACE CONTROL

The I<sup>2</sup>C interface permits individual enable/disable of each clock output: any unused outputs may be disabled to reduce the EMI. The QS5810 is a slave receiver device. It can read back the data stored in the latches for verification.

The data transfer rate supported by the I<sup>2</sup>C interface is 100k bits/sec. Data is transferred in bytes (with the addition of start, stop, acknowledge bits) in sequential order from the lowest to highest byte with the ability to stop after any complete byte has been transferred. The first two bytes transferred must be a Command Code followed by a Byte Count. Both of these bytes are ignored by the device.

The I<sup>2</sup>C address of the QS5810 is:

| A7 | A6 | A5 | A4 | A3 | A2 | A1 |

|----|----|----|----|----|----|----|

| 1  | 1  | 0  | 1  | 0  | 0  | 1  |

Address A0 is the read/write bit and is set to 0 for writes and 1 for reads. During read back, the first byte read is a Byte Count representing the number of bytes following (fixed at 3).

## SERIAL CONFIGURATION COMMAND BITMAPS

Byte 0: SDRAM Active/Inactive Register (1 = Enable, 0 = Disable), Default = Enable

| Bit   | Pin # | Description               |  |

|-------|-------|---------------------------|--|

| Bit 7 | —     | Initialize to 0           |  |

| Bit 6 | _     | Initialize to 0           |  |

| Bit 5 | _     | Initialize to 0           |  |

| Bit 4 | _     | Initialize to 0           |  |

| Bit 3 | 7     | SDRAM 3 (Active/Inactive) |  |

| Bit 2 | 6     | SDRAM 2 (Active/Inactive) |  |

| Bit 1 | 3     | SDRAM 1 (Active/Inactive) |  |

| Bit 0 | 2     | SDRAM 0 (Active/Inactive) |  |

Byte 1: SDRAM Active/Inactive Register (1 = Enable, 0 = Disable), Default = Enable

| Pin # | Description               |  |

|-------|---------------------------|--|

| 27    | SDRAM 7 (Active/Inactive) |  |

| 26    | SDRAM 6 (Active/Inactive) |  |

| 23    | SDRAM 5 (Active/Inactive) |  |

| 22    | SDRAM 4 (Active/Inactive) |  |

| _     | Initialize to 0           |  |

| _     | Initialize to 0           |  |

| _     | Initialize to 0           |  |

|       | Initialize to 0           |  |

|       | 27<br>26<br>23            |  |

### Byte 2: SDRAM Active/Inactive Register

(1 = Enable, 0 = Disable), Default = Enable

| Bit   | Pin # | Description                       |

|-------|-------|-----------------------------------|

| Bit 7 | 18    | SDRAM 9 (Active/Inactive)         |

| Bit 6 | 11    | SDRAM 8 (Active/Inactive)         |

| Bit 5 | —     | Reserved, 1 at power up, set to 0 |

| Bit 4 | —     | Reserved, 1 at power up, set to 0 |

| Bit 3 | —     | Reserved, 1 at power up, set to 0 |

| Bit 2 | —     | Reserved, 1 at power up, set to 0 |

| Bit 1 | _     | Reserved, 1 at power up, set to 0 |

| Bit 0 |       | Reserved, 1 at power up, set to 0 |

INDUSTRIAL TEMPERATURE RANGE

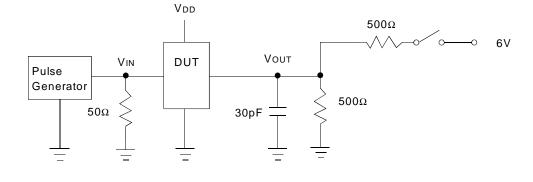

### **TEST CIRCUIT**

| Parameter<br>Tested | Switch<br>Position |

|---------------------|--------------------|

| tPLZ, tPZL          | Closed             |

| All Others          | Open               |

# **AC TEST CIRCUIT**

### **ENABLE AND DISABLE TIMES**

ENABLE

### **ORDERING INFORMATION**

*CORPORATE HEADQUARTERS* 2975 Stender Way Santa Clara, CA 95054 for SALES: 800-345-7015 or 408-727-6116 fax: 408-492-8674 www.idt.com\*

\*To search for sales office near you, please click the sales button found on our home page or dial the 800# above and press 2. The IDT logo is a registered trademark of Integrated Device Technology, Inc.