CMOS 4-Bit Microcontroller

# TMP47C222N, TMP47C422N TMP47C222F, TMP47C422F TMP47C222U, TMP47C422U

The TMP47C222/422 are high speed and high performance 4-bit single chip micro computers, integrating AD converter, pulse output, zero-cross detector and LCD driver based on the TLCS-470 series.

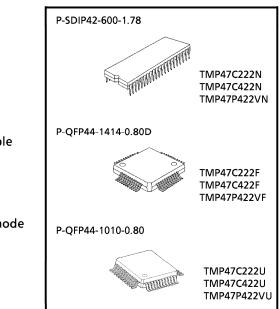

| Part No.   | ROM          | RAM         | Rackage            | OTP         |

|------------|--------------|-------------|--------------------|-------------|

| TMP47C222N |              |             | P-SDIP42-600-1.78  | TMP47P422VN |

| TMP47C222F | 2048 x 8-bit | 192 x 4-bit | P-QFP44-1414-0.80D | TMP47P422VF |

| TMP47C222U |              |             | P-QFP44-1010-0.80  | TMP47P422VU |

| TMP47C422N |              |             | P-SDIP42-600-1.78  | TMP47P422VN |

| TMP47C422F | 4096 x 8-bit | 256 x 4-bit | P-QFP44-1414-0.80D | TMP47P422VF |

| TMP47C422U |              |             | P-QFP44-1010-0.80  | TMP47P422VU |

#### Features

- ♦4-bit single chip microcomputer

- ♦Instruction execution time: 1.0 µs (at 8 MHz)

- Low voltage operation: 2.2 V (at 4.2 MHz)

- 92 basic instructions

- Table look-up instructions

- Subroutine nesting: 15 levels max

- ◆6 interrupt sources (External: 2, Internal: 4) All sources have independent latches each, and multiple interrupt control is available.

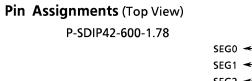

- ◆I/O port (SDIP: 20 pins, QFP: 22 pins)

- Interval Timer

- Two 12-bit Timer/Counters

- Timer, event counter, and pulse width measurement mode

- Watchdog Timer

- Serial Interface with 8-bit buffer

- Simultaneous transmission and reception capability

- 8/4-bit transfer, external/internal clock, and leading/trailing edge shift mode

000707EBA1

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Ouality and Reliability Assurance / Handling Precautions.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA

- making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.. The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments traffic signal instruments combustion control instruments medical instruments. transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others. The information contained herein is subject to change without notice.

- ♦ 8-bit successive approximate type AD converter

- With sample and hold

- 4 analog inputs

- Conversion time: 24  $\mu$ s (at 8 MHz)

- ♦Pulse output

- Buzzer drive/Remocon carrier

- ♦Zero-cross detector

- ♦LCD driver

- LCD direct drive capability (max 10-digit display at 1/4 duty LCD)

- 1/4, 1/3, 1/2 duties or static drive are programmably selectable.

- ◆Dual-clock operation

High-speed / Low-power-consumption operating mode

- ♦Hold function

- Battery/Capacitor back-up

- Emulation pod: BM47C422

# **Pin Function**

| Pin Name                                | Input / Output | Fun                                                                     | ction                                                   |  |  |  |

|-----------------------------------------|----------------|-------------------------------------------------------------------------|---------------------------------------------------------|--|--|--|

| R43 (AIN3/SEG19) to<br>R40 (AIN0/SEG16) | I/O<br>(I /O)  | 4-bit I/O ports with latch (P5 port has only                            | AD converter analog input<br>/ LCD segment drive output |  |  |  |

| P51, P50                                | Output         | 2-bit).                                                                 | (Note)                                                  |  |  |  |

| R63 (SEG15) to<br>R60 (SEG12)           | I/O (Output)   | These ports can be set, cleared and tested                              | LCD segment drive output                                |  |  |  |

| R73 (XTOUT)                             | I/O (Output)   | for each bit as specified by L-register                                 | Resonator connecting pins                               |  |  |  |

| R72 (XTIN)                              | I/O (Input)    | indirect addressing bit manipulation                                    | (Low-frequency).                                        |  |  |  |

| R71 (PULSE)                             | I/O (Output)   | instruction.                                                            | Pulse output                                            |  |  |  |

| R70                                     | I/O            |                                                                         |                                                         |  |  |  |

| R83 (T1)                                |                | 4-bit I/O ports with latch                                              | Timer / Counter1 external input                         |  |  |  |

| R82 (INT1/ZIN)                          | 1/0            | When used as input port, external interrupt input pin, or timer/counter | External interrupt1 and zero-cross input                |  |  |  |

| R81 (T2)                                | (Input)        | external input pin, the latch must be set to                            | Timer / Counter2 external input                         |  |  |  |

| R80 (INT2)                              |                | "1".                                                                    | External interrupt2 input                               |  |  |  |

| R92 (SCK)                               | I/O (I/O)      | 3-bit I/O ports with latch                                              | Serial clock I/O                                        |  |  |  |

| R91 (SO)                                | I/O (Output)   | When used as input port or serial port, the                             | Serial data output                                      |  |  |  |

| R90 (SI)                                | l/O (Input)    | latch must be set to "1".                                               | Serial data input                                       |  |  |  |

| SEG11 to SEG0                           |                | LCD segment drive output                                                |                                                         |  |  |  |

| COM4 to COM1                            | Output         | LCD Common drive output                                                 |                                                         |  |  |  |

| XIN                                     | Input          | Resonator connecting pins (High-frequency                               |                                                         |  |  |  |

| XOUT                                    | Output         | For inputting external clock, XIN is used and                           | I XOUT is opened                                        |  |  |  |

| RESET                                   | Input          | Reset signal input                                                      |                                                         |  |  |  |

| HOLD (KEO)                              | l/O (Input)    | HOLD request/release signal input                                       | sense input                                             |  |  |  |

| VDD (VAREF)                             |                | + 5 V                                                                   | AD converter analog reference voltage                   |  |  |  |

| VSS (VASS)                              | Power Supply   | 0 V (GND)                                                               | AD converter analog reference voltage<br>(GND)          |  |  |  |

| VLC                                     |                | LCD drive power supply                                                  |                                                         |  |  |  |

Note: TMP47C222/422N (SDIP) do not have port P5.

# TOSHIBA

## **Operational Description**

Concerning the TMP47C222/422 the configuration and functions of hardware are described. The basic instruction of configuration in the TMP47C222/422 is the same as those of TLCS-470 series.

1. System Configuration

- ♦Internal CPU Function

- 2.1 Program Counter (PC)

- 2.2 Program Memory (ROM)

- 2.3 H Register, L Register

- 2.4 Data Memory (RAM)

- a. Stack,

- b. Stack Pointer Word (SPW),

- c. Data Counter (DC)

- ALU, Accumulator

- 2.6 Flags

2.5

- 2.7 System Clock Controller

- 2.8 Interrupt Controller

- 2.9 Reset Controller

- Watchdog Timer

- Peripheral Hardware Function 3.1 I/O Ports

- 3.2 Interval Timer

- 3.3 Timer/Counters (TC1, TC2)

- 3.4 Pulse output

- 3.5 Zero-cross detector

- 3.6 AD converter

- 3.7 Serial Interface

- 3.8 LCD Driver

# 2. Internal CPU Function

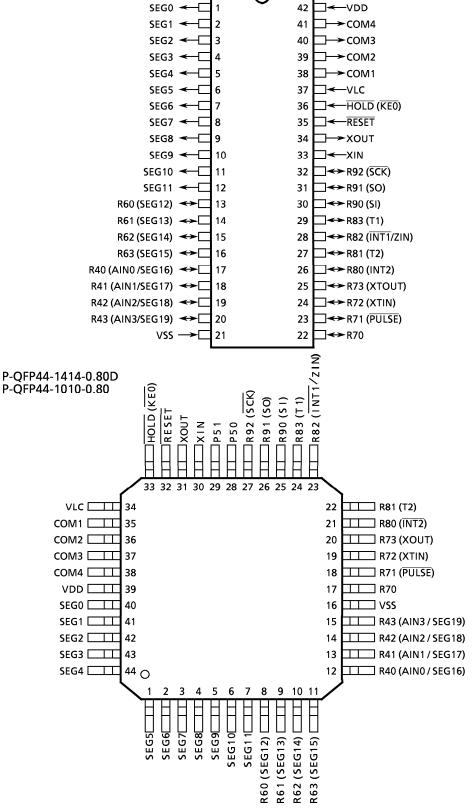

# 2.1 Program Counter (PC)

The program counter is a 12-bit binary counter which indicates the address of the program memory storing the next instruction to be executed. Normally, the PC is incremented by the number of bytes of the instruction every time it is fetched. When a branch instruction or a subroutine instruction has been executed or an interrupt has been accepted, the specified values listed in Table 2-1 are set to the PC. The PC is initialized to "0" during reset. In the TMP47C222/422, the long franch instruction [BSL a] should not be used.

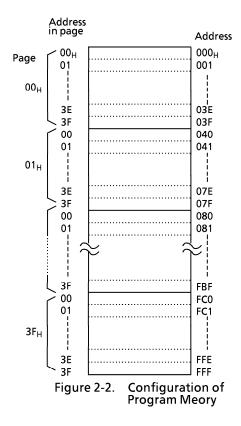

Figure 2-1. Configuration of Program Counter

The PC can directly address a 4096-byte address space. However, with the short branch and subroutine call instructions, the following points must be considered In the TMP47C222/422, the long branch instruction [BSL a] should not be used.

(1) Short branch instruction [BSS a]

In [BSS a] instruction execution, when the branch condition is satisfied, the value specified in the instruction is set to the lower 6 bits of the PC. That is, [BSS a] becomes the in-page branch instruction. When [BSS a] is stored at the last address of the page, the upper 6 bits of the PC point the next page, so that branch is made to the next page.

(2) Subroutine call instruction [CALL a]

In [CALL a] instruction execution, the contents of the PC are saved to the stack then the value specified in the instruction is set to the PC. The address which can be specified by the instruction consists of 11 bits and the most significant bit of the PC is always "0". Therefore, the entry address of the subroutine should be within an address range of  $000_{\rm H}$  through 7FF<sub>H</sub>.

| In                    | structi<br>or   | on |                   | Condition                                                 |                                                       |                  |                 |                 |                 | gram Co                 |                 |                 |                 |                 | <b>_</b> |        |

|-----------------------|-----------------|----|-------------------|-----------------------------------------------------------|-------------------------------------------------------|------------------|-----------------|-----------------|-----------------|-------------------------|-----------------|-----------------|-----------------|-----------------|----------|--------|

| 0                     | perati          | on |                   |                                                           | PC <sub>11</sub>                                      | PC <sub>10</sub> | PC <sub>9</sub> | PC <sub>8</sub> | PC <sub>7</sub> | PC <sub>6</sub>         | PC <sub>5</sub> | PC <sub>4</sub> | PC <sub>3</sub> | PC <sub>2</sub> | PC1      | PC0    |

| u o                   | BS              | а  | SF = 1<br>(Brancl | h condition is satisfied)                                 |                                                       |                  | I               | mmedi           | ate dat         | a specif                | fied by         | the ins         | truction        | า               |          |        |

| t i                   |                 | -  | SF = 0            | SF = 0 (Branch condition is not satisfied)                |                                                       | + 2              |                 |                 |                 |                         |                 |                 |                 |                 |          |        |

| - L                   |                 |    | SF = 1            | Lower 6-bit address $\neq$ 111111                         |                                                       |                  | Hold            |                 |                 | Imr                     | nediate         | e data s        | specifie        | d by th         | e instru | uction |

| l n s t               | BSS             | Sa | 5r = 1            | Lower 6-bit address<br>= 111111<br>(last address in page) |                                                       |                  | + 1             |                 |                 | lmr                     | nediat          | e data s        | specifie        | d by th         | e instru | uction |

| <b> </b> <del>-</del> |                 |    | SF = 0            |                                                           |                                                       |                  |                 |                 |                 | +                       | 1               |                 |                 |                 |          |        |

| °                     | CALL            | а  |                   |                                                           | 0                                                     |                  |                 | Imm             | ediate          | data sp                 | ecified         | by the          | instruc         | tion            |          |        |

| и<br>0<br>            | CALL            | Sa |                   |                                                           | 0                                                     | 0                | 0               | 0               |                 | ta genera<br>becified b |                 |                 | diate           | 1               | 1        | 0      |

| t<br>C                | RET             |    |                   |                                                           |                                                       |                  |                 | The r           | eturn a         | ddress i                | restore         | d from          | stack           |                 |          |        |

| e<br>Xe               | RETI            |    |                   |                                                           |                                                       |                  |                 | The r           | eturn a         | ddress                  | restore         | d from          | stack           |                 |          |        |

| l û                   | Othe            | rs |                   |                                                           | Incremented by the number of bytes in the instruction |                  |                 |                 |                 |                         |                 |                 |                 |                 |          |        |

|                       | errupt<br>eptan | ce |                   |                                                           | 0                                                     | 0                | 0               | 0               | 0               | 0                       | 0               | 0               | Inte            | rrupt v         | ector    | 0      |

|                       | Reset           |    |                   |                                                           | 0                                                     | 0                | 0               | 0               | 0               | 0                       | 0               | 0               | 0               | 0               | 0        | 0      |

Table 2-1. Status Change of Program Counter

### 2.2 Program Memory (ROM)

Programs and fixed data are stored in the program memory. The instruction to be executed next is read from the address indicated by the contents of the PC.

The fixed data can be read by using the table look-up instructions.

• Table look-up instructions

[LDL A, @DC], [LDH A, @DC +]

The table look-up instructions read the lower and upper 4 bits of the fixed data stored at the address specified in the data counter (DC) to place them into the accumulator. [LDL A, @DC] instruction reads the lower 4 bits of fixed data, and [LDH A, @DC+] instruction reads the upper 4 bits.

The DC is a 12-bit register, allowing it to address the entire program memory space.

#### 2.2.1 Program Memory Capacity

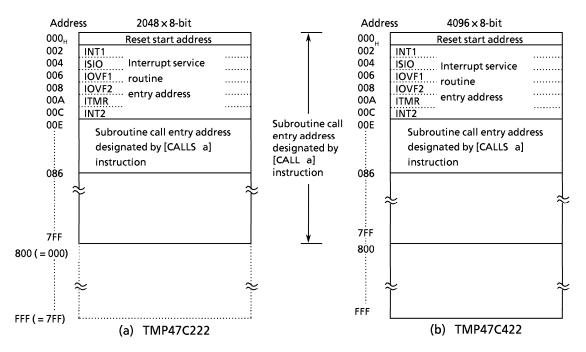

Figure 2-3 shows the program memory map. Address  $000_H$  to  $086_H$  of the program memory are also used for special purposes.

#### 2.2.2 Program Memory Map

The TMP47C222 has 2048  $\times$  8 bits (addresses 000<sub>H</sub> to 7FF<sub>H</sub>) of program memory (mask ROM), the TMP47C422 has 4096  $\times$  8 bits (addresses 000<sub>H</sub> to FFF<sub>H</sub>).

On the TMP47C222, no physical program memory exists in the address range  $800_H$  to FFF<sub>H</sub>. However, if this space is accessed by program, the most significant bit of each address is always regarded as "0" and the contents of the program memory corresponding to the address  $000_H$  to  $7FF_H$  are read.

Figure 2-3. Program Memory Map

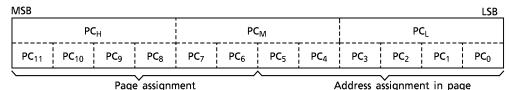

#### 2.3 H Register and L Register

The H register and the L register are 4-bit general registers. They are also used as a register pair (HL) for the data memory (RAM) addressing pointer. The RAM consists of pages, each page being 16 words long (1 word = 4 bits). The H register specifies a page and the L register specifies an address in the page.

The L register has the auto-post-increment/decrement capability, implementing the execution of composite instructions. For example, [ST A, @HL +] instruction automatically increments the contents of the L register after data transfer.

During the execution of [SET @L], [CLR @L], or [TEST @L] instructions, the L register is also used to specify the bits corresponding to I/O port pins R73 through R40 (the indirect addressing of port bits by the L register).

|                 | H Reg           | gister          |                 |                                                                 | L Reg | gister |  |

|-----------------|-----------------|-----------------|-----------------|-----------------------------------------------------------------|-------|--------|--|

| HR <sub>3</sub> | HR <sub>2</sub> | HR <sub>1</sub> | HR <sub>0</sub> | LR <sub>3</sub> LR <sub>2</sub> LR <sub>1</sub> LR <sub>0</sub> |       |        |  |

| ·               |                 |                 |                 | <b>^</b>                                                        |       | v      |  |

Page specification Address specification in page

Figure 2-4. Configuration of H and L Registers

#### **Electrical Characteristics**

Absolute Maximum Ratings

| Parameter                       | Symbol             | Pins                | Ratings                        | Unit |

|---------------------------------|--------------------|---------------------|--------------------------------|------|

| Supply Voltage                  | V <sub>DD</sub>    |                     | – 0.3 to 6.5                   | V    |

| Input Voltage                   | V <sub>IN</sub>    |                     | – 0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output Voltage                  | V <sub>OUT</sub>   |                     | – 0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output Current (Der 1 nin)      | I <sub>OUT1</sub>  | Port R4, R7         | 30                             |      |

| Output Current (Per 1 pin)      | I <sub>OUT2</sub>  | Port R5, R6, R8, R9 | 3.2                            | mA   |

|                                 | ZI <sub>OUT1</sub> | Port R4, R7         | 120                            |      |

| Power Dissipation [Topr = 70°C] | PD                 |                     | 400                            | mW   |

| Soldering Temperature (time)    | Tsld               |                     | 260 (10 s)                     | °C   |

| Storage Temperature             | Tstg               |                     | – 55 to 125                    | °C   |

| Operating Temperature           | Topr               |                     | – 30 to 70                     | °C   |

Note: The absolute maximum ratings are rated values which must not be exceeded during operation, even for an instant. Any one of the ratings must not be exceeded. If any absolute maximum rating is exceeded, a device may break down or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user. Thus, when designing products which include this device, ensure that no absolute maximum rating value will ever be exceeded.

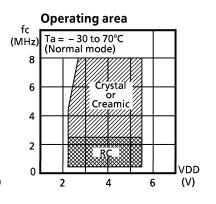

| Parameter          | Symbol           | Pins                    | Pins Conditions                |                        | Max                    | Unit |

|--------------------|------------------|-------------------------|--------------------------------|------------------------|------------------------|------|

|                    |                  |                         | fc = 8.0 MHz                   | 2.7                    |                        |      |

| Supply Voltage     |                  |                         | fc = 4.2 MHz                   | 2.2                    | ]                      |      |

|                    | V <sub>DD</sub>  |                         | In the SLOW mode               | 2.2                    | 5.5                    | V    |

|                    |                  |                         | In the HOLD mode               | 2.0                    | ]                      |      |

|                    | V <sub>IH1</sub> | Except Hysteresis Input | In the normal                  | V <sub>DD</sub> × 0.7  |                        |      |

| Input High Voltage | V <sub>IH2</sub> | Hysteresis Input        | operating area                 | V <sub>DD</sub> × 0.75 | V <sub>DD</sub>        | V    |

|                    | V <sub>IH3</sub> |                         | In the HOLD mode               | V <sub>DD</sub> × 0.9  |                        |      |

|                    | V <sub>IL1</sub> | Except Hysteresis Input | In the normal                  |                        | $V_{DD} \times 0.3$    |      |

| Input Low Voltage  | V <sub>IL2</sub> | Hysteresis Input        | operating area                 | 0                      | V <sub>DD</sub> × 0.25 | V    |

|                    | V <sub>IL3</sub> |                         | In the HOLD mode               |                        | V <sub>DD</sub> × 0.1  |      |

|                    |                  |                         | V <sub>DD</sub> = 2.7 to 5.5 V |                        | 8.0                    |      |

| Clock Frequency    | fc               | XIN, XOUT               | V <sub>DD</sub> = 2.2 to 5.5 V | 0.4                    | 4.2                    | ]    |

|                    |                  |                         | In the RC oscillation          | 7                      | 2.5                    | MHz  |

|                    | fs               | XTIN, XTOUT             | V <sub>DD</sub> = 2.2 to 5.5 V | 30                     | 34                     |      |

Recommended Operating Conditions  $(V_{SS} = 0 V, Topr = -30 to 70^{\circ}C)$

$(V_{SS} = 0 V)$

Note: The recommended operating conditions for a device are operating conditions under which it can be guaranteed that the device will operate as specified. If the device is used under operating conditions other than the recommended operating conditions (supply voltage, operating temperature range, specified AC/DC values etc.), malfunction may occur. Thus, when designing products which include this device, ensure that the recommended operating conditions for the device are always adhered to.

| DC Characteristics |

|--------------------|

|--------------------|

$(V_{SS} = 0 V, Topr = -30 to 70^{\circ}C)$

| Parameter                              | Symbol            | Pins                    | Conditions                                             | Min | Тур.     | Max | Unit |

|----------------------------------------|-------------------|-------------------------|--------------------------------------------------------|-----|----------|-----|------|

| Hysteresis Voltage                     | V <sub>HS</sub>   | Hysteresis Input        |                                                        | -   | 0.7      | -   | ×    |

|                                        | I <sub>IN1</sub>  | RESET, HOLD             |                                                        |     |          |     |      |

| Input Current                          | I <sub>IN2</sub>  | Open drain output ports | $V_{DD} = 5.5 V, V_{IN} = 5.5 V / 0V$                  | -   | _        | ± 2 | μA   |

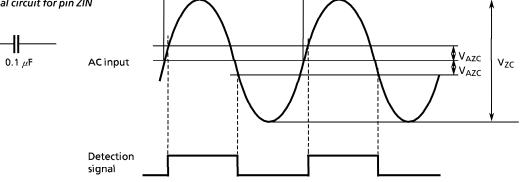

| Input Resistance                       | R <sub>IN</sub>   | RESET                   |                                                        | 100 | 220      | 450 | kΩ   |

| Output Leakage<br>Current              | I <sub>LO</sub>   | Open drain output ports | V <sub>DD</sub> = 5.5 V, V <sub>OUT</sub> = 5.5 V      | -   | _        | 2   | μΑ   |

| Output Low<br>Current                  | I <sub>OL</sub>   | Port R4, R7             | $V_{DD} = 4.5 V, V_{OL} = 1.0 V$                       | 7   | 10       | -   | mA   |

| Output Low                             |                   |                         | $V_{DD} = 4.5 V, I_{OL} = 1.6 mA$                      | _   | -        | 0.4 |      |

| Voltage V                              |                   | Port P5, R6, R8, R9     | $V_{DD} = 2.2 \text{ V}, \ I_{OL} = 20 \ \mu \text{A}$ | -   | _        | 0.1 | V    |

| Segment Output Low<br>Resistance       | R <sub>OS1</sub>  | SEG pin                 |                                                        |     | 10<br>or | _   | kΩ   |

| Common Output Low<br>Resistance        | R <sub>OC1</sub>  | COM pin                 |                                                        |     | 20       |     | K77  |

| Segment Output High<br>Resistance      | R <sub>OS2</sub>  | SEG pin                 |                                                        | _   | 70<br>or | _   | kΩ   |

| Common Output High<br>Resistance       | R <sub>OC2</sub>  | COM pin                 | $V_{DD} = 5 V, V_{DD} - V_{LC} = 3 V$                  |     | 200      |     | K32  |

|                                        | V <sub>O2/3</sub> |                         |                                                        | 3.8 | 4.0      | 4.2 |      |

| Segment/Common<br>Output Registance    | V <sub>01/2</sub> | SEG / COM pin           |                                                        | 3.3 | 3.5      | 3.7 | v    |

|                                        | V <sub>01/3</sub> |                         |                                                        | 2.8 | 3.0      | 3.2 |      |

|                                        |                   |                         | $V_{DD} = 5.5 V$ , fc = 4 MHz                          | -   | 2        | 4   |      |

| Supply Current<br>(in the Normal mode) | I <sub>DD</sub>   |                         | $V_{DD} = 3.0 V, fc = 4 MHz$                           | -   | 1        | 2   | mA   |

|                                        |                   |                         | $V_{DD} = 3.0 V$ , fc = 400 kHz                        | -   | 0.5      | 1   |      |

| Supply Current<br>(in the SLOW mode)   | I <sub>DDS</sub>  |                         | V <sub>DD</sub> = 3.0 V, fs = 32.768 kHz               | -   | 20       | 40  | μΑ   |

| Supply Current<br>(in the HOLD mode)   | I <sub>DDH</sub>  |                         | V <sub>DD</sub> = 5.5 V                                | -   | 0.5      | 10  | μΑ   |

Note 1: Typ. values show those at Topr =  $25^{\circ}$ C,  $V_{DD}$  = 5 V.

Note 2: Input Current  $I_{IN1}$ : The current through resistor is not included.

Note 3: Output Resistance R<sub>os</sub>, R<sub>oc</sub>; Shows on-resistance at the level switching.

Note 4:  $V_{O2/3}$ ; Shows 2/3 level output voltage, when the 1/4 or 1/3 duty LCD is used.

$V_{O1/2}$ ; Shows 1/2 level output voltage, when the 1/2 duty or static LCD is used.

$V_{O1/3}$ ; Shows 1/3 level output voltage, when the 1/4 or 1/3 duty LCD is used.

Note 5:

Supply Current  $I_{DD}$ ,  $I_{DDH}$ :  $V_{IN} = 5.3 V / 0.2 V (V_{DD} = 5.5 V)$ , 2.8 V / 0.2 V ( $V_{DD} = 3.0 V$ )

Supply Current  $I_{DDS}$  ;

$V_{IN} = 2.8 V / 0.2 V$ . Low frequency clock is only osillated.

Note 6: When using LCD, it is necessary to consider values of Ros 1/2 and Roc 1/2.

Note 7: Times fou SEG/COM output switching on ; Ros1, Roc1:2/fc (s)

Ros2, Roc2:  $1/(n \cdot f_F)$  (1/n; duty,  $f_F$ : frame frequency)

#### **AD Conversion Characteristics**

$(Topr = -30 \text{ to } 70^{\circ}\text{C})$

| Parameter                      | Symbol               | Conditions                        | Min             | Тур. | Max             | Unit |

|--------------------------------|----------------------|-----------------------------------|-----------------|------|-----------------|------|

| Analog Reference Voltage Range | $\triangle V_{AREF}$ | V <sub>DD</sub> – V <sub>SS</sub> | 2.7             | _    | —               | v    |

| Analog Input Voltage           | V <sub>AIN</sub>     |                                   | V <sub>SS</sub> | _    | V <sub>DD</sub> | v    |

| Analog Supply current          | I <sub>REF</sub>     |                                   | _               | 0.5  | 1.0             | mA   |

| Nonlinearity Error             |                      |                                   | _               | -    | ± 1             |      |

| Zero Point Error               |                      | V <sub>DD</sub> = 2.7 V to 5.5 V  | _               | _    | ± 1             |      |

| Full Scale Error               |                      | V <sub>SS</sub> = ± 0.000 V       | _               | -    | ± 1             | LSB  |

| Total Error                    |                      | ]                                 | _               | _    | ± 2             |      |

| AC Characteristics                         | (V <sub>SS</sub> = 0 | $(V_{SS} = 0 V, Topr = -30 to 70^{\circ}C)$ |                               |               |        |     |      |

|--------------------------------------------|----------------------|---------------------------------------------|-------------------------------|---------------|--------|-----|------|

| Parameter                                  | Symbol               | Con                                         | ditions                       | Min           | Тур.   | Max | Unit |

|                                            |                      |                                             | V <sub>DD</sub> = 2.7 to 5.5V | 1.0           |        |     |      |

| Instruction Cycle Time                     |                      | In the normal mode                          | $V_{DD}$ = 2.2 to 5.5V        | 1.9           |        | 20  |      |

|                                            | tcy                  |                                             | <b>RC</b> oscillation         | 3.2           | -      |     | μs   |

|                                            |                      | In the SLOW mode                            |                               | 235           |        | 267 |      |

|                                            |                      | <b>F</b>                                    | $V_{DD} \ge 2.7 V$            | 60            |        |     |      |

| High level clock pulse width               | t <sub>WCH</sub>     | For external                                | V <sub>DD</sub> <2.7 V        | 120           |        | -   |      |

| the state of the state of the state of the |                      |                                             | $V_{DD} \ge 2.7 V$            | 60            | _      |     | ns   |

| Low level clock pulse width                | t <sub>WCL</sub>     | (XIN input)                                 | V <sub>DD</sub> <2.7 V        | 120           |        |     |      |

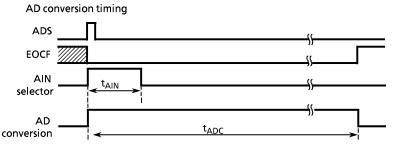

| AD Conversion Time                         | t <sub>ADC</sub>     |                                             |                               | _             | 24 tcy | _   |      |

| AD Sampling Time                           | t <sub>AIN</sub>     |                                             |                               | _             | 2 tcy  | _   | μs   |

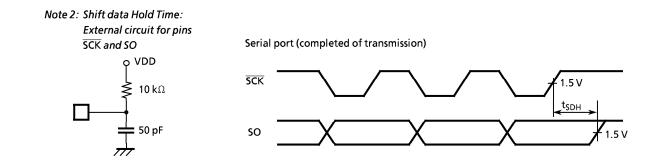

| Shift data Hold Time                       | t <sub>SDH</sub>     |                                             |                               | 0.5 tcy – 0.3 | -      | _   | μs   |

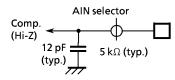

Note 1: AD conversion timing: Internal circuit for pins AIN0 to 7

\* Electrical change inust be loaded into the buit-in condensen during t<sub>AIN</sub> for normal AD conversion.

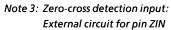

| Zero-Cross Detection       | (Vss = 0V, T     | opr = - 30                      | to 70℃)         |     |      |       |                  |

|----------------------------|------------------|---------------------------------|-----------------|-----|------|-------|------------------|

| Parameter                  | Symbol           | Conditions                      |                 | Min | Тур. | Max   | Unit             |

| Zero-cross Input Voltage   | V <sub>zc</sub>  | AC coupling (C = 0              | 0.1 μF <b>)</b> | 1.0 | _    | 3.0   | V <sub>P-P</sub> |

| Zero-cross Accuracy        | V <sub>AZC</sub> | f <sub>ZC</sub> = 50 to 60 Hz ( | sine curve)     | -   | —    | ± 135 | mV               |

| Zero-cross input frequensy | f <sub>ZC</sub>  |                                 |                 | 40  | _    | 1000  | Hz               |

1/f<sub>ZC</sub>

| Recommended Oscillating Conditions                  | $(V_{SS} = 0 V, V_{DD} = 2.2 \text{ to } 5.5 V, \text{ Topr} = -30 \text{ to } 70^{\circ}\text{C})$ |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| (1) 6 MHz<br>Ceramic Resonator                      | ХIN ХОИТ<br>С 6 MHz                                                                                 |

| CSA6.00MGU (MURATA)                                 | $C_{VIN} = C_{VOUT} = 30 \text{ pE}$                                                                |

| KBR-6.00MS (KYOCERA)                                | C <sub>XIN</sub> = C <sub>XOUT</sub> = 30 pF                                                        |

| EFOEC6004A4 (NATIONAL)                              | $C_{XIN} = C_{XOUT} = 30 \text{ pF}$ $C_{XIN} \stackrel{!}{=} \stackrel{I \sqcup I}{=} c_{XOUT}$    |

| (2) 4 MHz                                           |                                                                                                     |

| Ceramic Resonator                                   |                                                                                                     |

| CSA4.00MG (MURATA)                                  | C <sub>XIN</sub> = C <sub>XOUT</sub> = 30 pF                                                        |

| KBR-4.00MS (KYOCERA)                                | $C_{XIN} = C_{XOUT} = 30 \text{ pF}$ L                                                              |

| EFOEC4004A4 (NATIONAL)                              | $C_{XIN} = C_{XOUT} = 30 \text{ pF}$ $400 \text{ kHz} \stackrel{\checkmark}{\leq} R_{XOUT}$         |

| Crystal Oscillator                                  | ┝──┤□├───                                                                                           |

| 204B-6F 4.0000 (TOYOCOM)                            | $C_{XIN} = C_{XOUT} = 20 \text{ pF}$ $C_{XIN} + C_{XOUT}$                                           |

|                                                     | <i>117 111</i>                                                                                      |

| (3) 400 kHz                                         | XTIN XTOUT                                                                                          |

| Ceramic Resonator                                   |                                                                                                     |

| CSB400B (MURATA)                                    | $C_{XIN} = C_{XOUT} = 220 \text{ pF}, R_{XOUT} = 6.8 \text{ k}\Omega$                               |

| KBR-400B (KYOCERA)                                  | $C_{X N} = C_{XO  T} = 100 \text{ pr}, \text{ R}_{XO  T} = 10 \text{ R}_{XD}$                       |

| EFOA400K04B (NATIONAL)                              | $C_{XIN} = C_{XOUT} = 470 \text{ pF}, R_{XOUT} = 0 \Omega$                                          |

| (4) 32.768 kHz                                      | XIN XOUT                                                                                            |

| Crystal Oscillator C <sub>XTIN</sub>                | , C <sub>XTOUT</sub> ; 10 to 33 pF (Note)                                                           |

| (5) RC Oscillation ( $V_{SS} = 0 V, V_{DD} = 5.0 V$ | $T_{opr} = 25^{\circ}C$                                                                             |

| 2 MHz (Typ.)                                        |                                                                                                     |

| 400 kHz (Typ.)                                      | $C_{XIN} = 100 \text{ pF, } R_X = 30 \text{ k}\Omega$                                               |

| Nate: In ander to not the commete costille          |                                                                                                     |

Note: In order to get the accurate oscillation frequency, the adjustment of capacitors must be required.

## **Typical Characteristics**

fc