TOSHIBA Bipolar Linear IC Silicon Monolithic

# **TA84005F/FG**

#### Three-Phase Wave Motor Driver IC

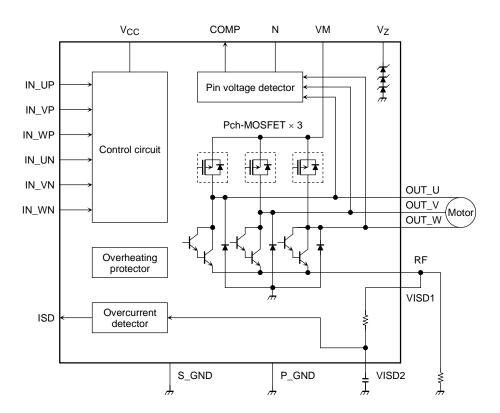

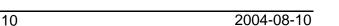

The TA84005F/FG is a three-phase wave motor driver IC. Used with a three-phase sensorless controller (TB6548F/FG), the TA84005F/FG can provide PWM sensorless

drive for three-phase brushless motors.

### **Features**

- Built-in voltage detector

- Overcurrent detector incorporated

- Overheating protector incorporated

- Multichip (MCH) structure

Uses Pch-MOS for the upper output power transistor

- Rated at 25 V/1.0 A

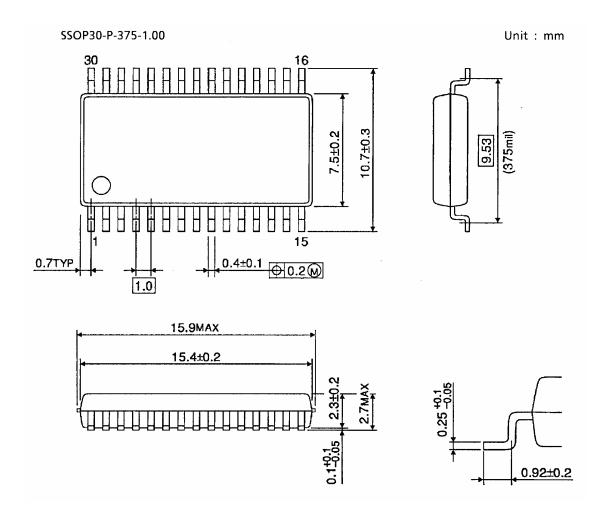

- Package: SSOP30-P-375-1.00

Weight: 0.63 g (typ.)

Note 1: This product has a multichip (MCP) structure utilizing Pch-MOS technology. The Pch-MOS structure is sensitive to electrostatic discharge and should therefore be handled with care.

### TA84005FG:

The TA84005FG is Pb-free product.

The following conditions apply to solderability:

\*Solderability

- 1. Use of Sn-63Pb solder bath

- \*solder bath temperature = 230°C

- \*dipping time = 5 seconds

- \*number of times = once

- \*use of R-type flux

- 2. Use of Sn-3.0Ag-0.5Cu solder bath

- \*solder bath temperature =  $245^{\circ}$ C

- \*dipping time = 5 seconds

- \*number of times = once

- \*use of R-type flux

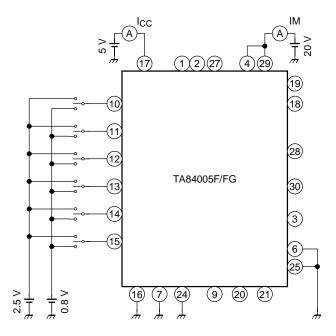

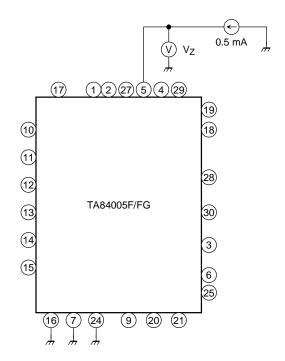

# **Block Diagram**

2 2004-08-10

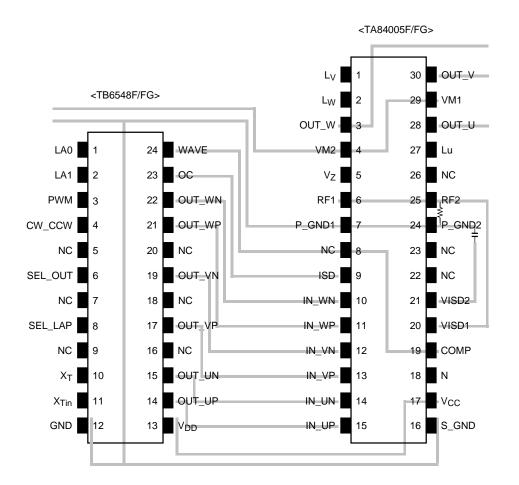

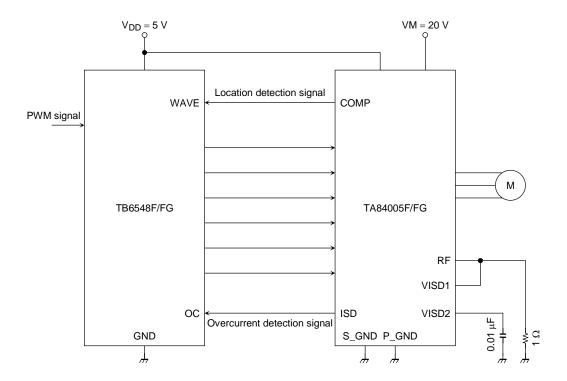

# **Pin Assignment**

3 2004-08-10

# **Pin Description**

| Pin<br>No. | Pin<br>Symbol  | Pin Function                         | Remarks                                                                                                          |  |  |

|------------|----------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|

| 1          | L <sub>V</sub> | V-phase output upper Pch gate pin    | Leave open.                                                                                                      |  |  |

| 2          | L <sub>W</sub> | W-phase output upper Pch gate pin    | Leave open.                                                                                                      |  |  |

| 3          | OUT_W          | W-phase output pin                   | Connects motor.                                                                                                  |  |  |

| 4          | VM2            | Motor drive power supply pin         | Externally connects to VM1.                                                                                      |  |  |

| 5          | VZ             | Reference voltage pin                | Used for the VM drop circuit reference voltage when VM (max) $\geqq$ 22 V. Left open when VM (max) $\leqq$ 22 V. |  |  |

| 6          | RF1            | Output current detection pin         | Externally connected to RF2. (Connect a detection resistor between this pin and GND.)                            |  |  |

| 7          | P_GND1         | Power GND pin                        | Externally connects to P_GND2.                                                                                   |  |  |

| 8          | NC             | Not connected                        | _                                                                                                                |  |  |

| 9          | ISD            | Overcurrent detection output pin     | Connects to the OC pin of the TB6548F/FG.                                                                        |  |  |

| 10         | IN_WN          | W-phase upper drive input pin        | Connects to the OUT_WN pin of the TB6548F/FG; incorporates pull-down resistor.                                   |  |  |

| 11         | IN_WP          | W-phase lower drive input pin        | Connects to the OUT_WP pin of the TB6548F/FG; incorporates pull-up resistor.                                     |  |  |

| 12         | IN_VN          | V-phase upper drive input pin        | Connects to the OUT_VN pin of the TB6548F/FG; incorporates pull-down resistor.                                   |  |  |

| 13         | IN_VP          | V-phase lower drive input pin        | Connects to the OUT_VP pin of the TB6548F/FG; incorporates pull-up resistor.                                     |  |  |

| 14         | IN_UN          | U-phase upper drive input pin        | Connects to the OUT_UN pin of the TB6548F/FG; incorporates pull-down resistor.                                   |  |  |

| 15         | IN_UP          | U-phase lower drive input pin        | Connects to the OUT_UP pin of the TB6548F/FG; incorporates pull-up resistor.                                     |  |  |

| 16         | S_GND          | Signal GND pin                       | _                                                                                                                |  |  |

| 17         | Vcc            | Control power supply pin             | V <sub>CC</sub> (opr) = 4.5 to 5.5 V                                                                             |  |  |

| 18         | Ν              | Mid-point pin                        | Mid-point potential confirmation pin; left open                                                                  |  |  |

| 19         | COMP           | Location detection signal output pin | Connects to the WAVE pin of the TB6548F/FG.                                                                      |  |  |

| 20         | VISD1          | Overcurrent detection input pin 1    | Externally connects to the RF2 pin.                                                                              |  |  |

| 21         | VISD2          | Overcurrent detection input pin 2    | Connect a capacitor between this pin and GND. Internal resistor and capacitor used to reduce noise.              |  |  |

| 22         | NC             | Not connected                        | _                                                                                                                |  |  |

| 23         | NC             | Not connected                        | _                                                                                                                |  |  |

| 24         | P_GND2         | Power GND pin                        | Externally connects to the P_GND1 pin.                                                                           |  |  |

| 25         | RF2            | Output current detection pin         | Externally connects to the RF1 pin. Connect a detection resistor between this pin and GND.                       |  |  |

| 26         | NC             | Not connected                        | _                                                                                                                |  |  |

| 27         | Lu             | U-phase upper output Pch gate pin    | Leave open.                                                                                                      |  |  |

| 28         | OUT_U          | U-phase output pin                   | Connects motor.                                                                                                  |  |  |

| 29         | VM1            | Motor drive power supply pin         | Externally connects to the VM2 pin.                                                                              |  |  |

| 30         | OUT_V          | V-phase output pin                   | Connects the motor.                                                                                              |  |  |

# **Maximum Ratings (Ta = 25°C)**

| Characteristic               | Symbol           | Rating                                | Unit    |  |

|------------------------------|------------------|---------------------------------------|---------|--|

| Motor power supply voltage   | VM               | 25                                    | V       |  |

| Control power supply voltage | V <sub>CC</sub>  | 7                                     | V       |  |

| Output current               | IO               | 1.0                                   | A/phase |  |

| Input voltage                | V <sub>IN</sub>  | GND - 0.3<br>~V <sub>CC</sub> + 0.3 V | V       |  |

| Power dissipation            | Pd               | 1.1 (Note 2)                          | W       |  |

| Fower dissipation            | Pu               | 1.4 (Note 3)                          |         |  |

| Operating temperature        | T <sub>opr</sub> | -30~85                                | °C      |  |

| Storage temperature          | T <sub>stg</sub> | -55~150                               | °C      |  |

Note 2: Standalone

Note 3: When mounted on a PCB (50  $\times$  50  $\times$  1.6 mm; Cu area, 30%)

# Recommended Operating Conditions (Ta = -30-85°C)

| Characteristic               | Symbol          | Test<br>Circuit | Test Conditions | Min | Тур. | Max             | Unit |

|------------------------------|-----------------|-----------------|-----------------|-----|------|-----------------|------|

| Control power supply voltage | V <sub>CC</sub> | _               | _               | 4.5 | 5.0  | 5.5             | V    |

| Motor power supply voltage   | VM              | _               | _               | 10  | 20   | 22              | V    |

| Output current               | lo              | _               | _               | _   | _    | 0.5             | Α    |

| Input voltage                | V <sub>IN</sub> | _               | _               | GND | _    | V <sub>CC</sub> | V    |

| Chopping frequency           | fchop           | _               | _               | 15  | 20   | 50              | kHz  |

| Vz current                   | IZ              | _               | _               | _   | _    | 1.0             | mA   |

# Electrical Characteristics (Ta = 25°C, $V_{CC}$ = 5 V, VM = 20 V)

| Characteristic Symbol Test Circuit Test Col |                      | Test Conditions | Min                                                                | Тур.        | Max  | Unit  |    |  |

|---------------------------------------------|----------------------|-----------------|--------------------------------------------------------------------|-------------|------|-------|----|--|

| Input voltage                               | V <sub>IN</sub> (H)  | 1               | IN_UP, IN_VP, IV_WP IN_UN, IN_VN, IN_WN                            | 2.5 _ 5     |      | 5.0   | V  |  |

|                                             | V <sub>IN</sub> (L)  | 1               | _                                                                  | GND         | _    | 0.8   |    |  |

|                                             | I <sub>IN1</sub> (H) | 2               | V <sub>IN</sub> = 5 V,<br>IN_UP, IN_VP, IN_WP                      |             | _    | 20    |    |  |

| land owner                                  | I <sub>IN2</sub> (H) | 2               | V <sub>IN</sub> = 5 V,<br>IN_UN, IN_VN, IN_WN                      | 300         | 450  | 600   |    |  |

| Input current                               | I <sub>IN1</sub> (L) | 2               | 2 V <sub>IN</sub> = GND,<br>IN_UN, IN_VN, IN_WN                    |             | _    | 1     | μА |  |

|                                             | I <sub>IN2</sub> (L) | 2               | $V_{IN} = GND,$ $IN\_UP, IN\_VP, IN\_WP$                           | 300         | 450  | 600   |    |  |

|                                             | I <sub>CC</sub> 1    | 3               | Upper phase 1 ON,<br>lower phase 1 ON, output open                 | _           | 8.0  | 13.0  |    |  |

|                                             | I <sub>CC</sub> 2    | 3               | Upper phase 2 ON,<br>synchronous regeneration<br>mode, output open | _           | 7.0  | 12.0  |    |  |

| Daniel and the same of                      | I <sub>CC</sub> 3    | 3               | All phases OFF, output open — 6.0                                  |             | 11   | A     |    |  |

| Power supply current                        |                      |                 | Upper phase 1 ON, lower phase 1 ON, output open                    | _           | 2.0  | 3.5   | mA |  |

|                                             | IM2                  | 3               | Upper phase 2 ON,<br>synchronous regeneration<br>mode, output open | _           | 2.0  | 3.5   |    |  |

|                                             | IM3                  | 3               | All phases OFF, output open                                        | n — 1.8 3.2 |      | 3.2   |    |  |

| Lower output saturation voltage             | VSAT                 | 4               | I <sub>O</sub> = 0.5 A                                             | _           | 1.0  | 1.5   | V  |  |

| Upper output ON-resistance                  | Ron                  | 5               | $I_O = \pm 0.5 \text{ A, bi-directional}$                          | _           | 0.65 | 1.0   | Ω  |  |

| Lower diode forward voltage                 | V <sub>F</sub> (L)   | 6               | I <sub>F</sub> = 0.5 A                                             |             | 1.2  | 1.6   | V  |  |

| Upper diode forward voltage                 | V <sub>F</sub> (H)   | 7               | I <sub>F</sub> = 0.5 A                                             | _           | 0.9  | 1.4   | V  |  |

| Mid-point voltage                           | VN                   | 8               | VM = 20 V<br>VRF = 0 V                                             | 9.88        | 10.4 | 10.92 | V  |  |

| Pin voltage detection level                 | VCMP                 | 9               | VM = 20 V<br>VRF = 0 V                                             | 9.88        | 10.4 | 10.92 | V  |  |

| Dis voltage detection output voltage        | VOL (CMP)            | 9               | I <sub>OL</sub> = 1 mA                                             | GND         | _    | 0.5   | V  |  |

| Pin voltage detection output voltage        | ROH (CMP)            | 9               | _                                                                  | 7           | 10   | 13    | kΩ |  |

| Overcurrent detection level                 | VRF                  | 10              | _                                                                  | 0.45        | 0.5  | 0.55  | V  |  |

| Oversurrent detection subsubjects           | VOH (ISD)            | 10              | I <sub>OH</sub> = 0.1 mA                                           | 4.5         | _    | 5.0   | V  |  |

| Overcurrent detection output voltage        | ROL (ISD)            | 10              | _                                                                  | 14          | 20   | 26    | kΩ |  |

| Reference voltage                           | VZ                   | 11              | $I_Z = 0.5 \text{ mA}, T_j = 25^{\circ}\text{C}$                   | 20.9        | 22.0 | 23.1  | V  |  |

| TSD temperature                             | TSD                  | _               | Tj                                                                 | _           | 180  | _     | °C |  |

| TSD hysteresis width                        |                      |                 | _                                                                  | 30          | _    | °C    |    |  |

| Output lookogo ourrent                      | I <sub>L</sub> (H)   | 12              | Pch-MOS                                                            | _ 0         |      | 100   | ^  |  |

| Output leakage current                      | I <sub>L</sub> (L)   | 13              | _                                                                  | 1 - 1       | 0    | 50    | μΑ |  |

6 2004-08-10

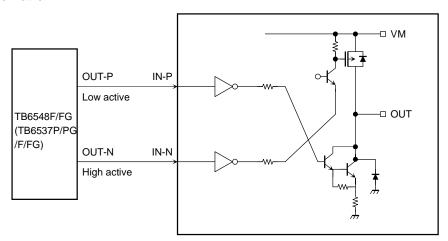

### **Functions**

| Inj  | put  |                           |                           |                        |

|------|------|---------------------------|---------------------------|------------------------|

| IN-P | IN-N | Upper Power<br>Transistor | Lower Power<br>Transistor |                        |

| High | High | ON                        | OFF                       | High                   |

| Low  | High | ON                        | ON                        | Prohibit mode (Note 4) |

| High | Low  | OFF                       | OFF                       | High impedance         |

| Low  | Low  | OFF                       | ON                        | Low                    |

Connecting the TB6548F/FG (or TB6537P/PG/F/FG) to the TA84005F/FG allows electric motors to be controlled by PWM.

Note 4: In Prohibit Mode, the output power transistor goes into vertical ON mode and through current may damage the circuit. Do not use the TA84005F/FG in this mode.

This mode is not actuated when the TA84005F/FG is connected to the TB6548F/FG or TB6537P/PG/F/FG, but can be triggered by input noise during standalone testing.

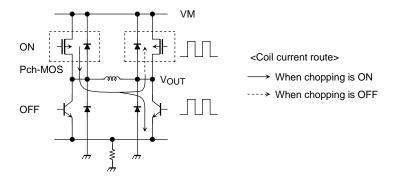

### <Schematic>

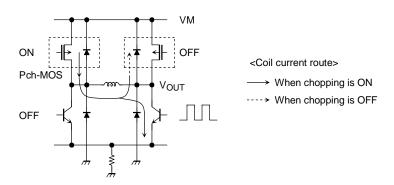

## <Lower PWM>

Connecting the TA84005F/FG to the TB6537P/PG/F/FG controls the lower PWM.

At chopping ON, the diagonally output power transistors are ON.

At chopping OFF, the lower transistor is OFF, regenerating the motor current via the upper diode (incorporating the Pch-MOS).

7

## <Synchronous rectification PWM>

Connecting the TA84005F/FG to the TB6548F/FG controls the synchronous rectification PWM.

At chopping OFF, power dissipation is reduced by operating the Pch-MOS in reverse and regenerating the motor's current.

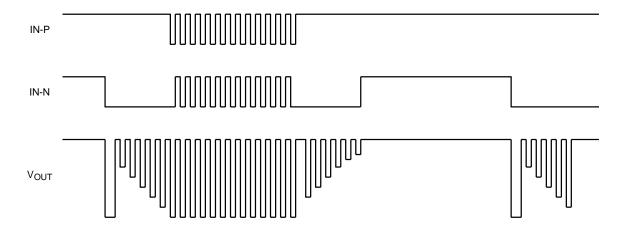

## <Timing Chart>

When controlling synchronous rectification PWM

## **Equivalent Circuit**

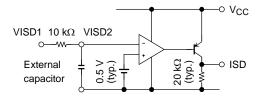

### <Overcurrent detector (RF, VISD, ISD) >

- Input to the VISD1 pin the voltage generated at the overcurrent detection resistor RF connected to the RF pin.

- At chopping ON, voltage spikes at the RF pin as a result of the Pch-MOS output capacitance. To cancel the spike, externally connect a capacitor to the VISD2 pin (10 kΩ resistor built-in).

- If the VISD2 pin voltage exceeds the internal reference voltage (VRF = 0.5 V), the overcurrent detection output ISD pin goes High.

Inputting the ISD pin output to the TB6537P/PG/F/FG or TB6548F/FG OC pin limits the PWM ON time and the current at the ISD output rising edge.

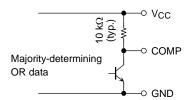

## <Pin voltage detector (COMP) >

The pin voltage detector outputs the result of OR-ing the output pin voltages and the virtual mid-point N voltage to determine the majority.

(If at least two phases of the three-phase output are greater than the mid-point potential, the detector outputs "Low". Conversely, if at least two phases are smaller than the mid-point potential, the circuit outputs "High".)

• With the virtual mid-point potential VN used as the reference for the pin voltage detection circuit considered as half the voltage applied to the motor, then

```

\begin{split} VN &= [ \text{ (VM - Ron (upper) *I_O)} - (V_{sat} \text{ (lower)} + VRF) ]/2 + V_{sat} + VRF \\ &= [VM - VRF + V_{sat} \text{ (lower)} - Ron \text{ (upper) *I_O}/2 + VRF. \\ \text{Here, assuming that } V_{sat} \text{ (lower)} - Ron \text{ (upper) *I_O} \simeq V_F, \\ \text{we have set the following: } VN &= [VM - VRF + VF]/2 + VRF \end{split}

```

### <Overheating protector>

• Automatic restoration TSD (ON) = 180°C TSD (OFF) = 150°C

• Temperature hysteresis supported TSD (HYS) = 30°C

## <Example of 24 V support>

• Incorporate a Zener diode and make the external connections shown in the diagram below. Design the device so that the voltage applied to the VM is clamped at 22 V below the maximum operating power supply voltage.

• A capacitor is needed to control the effect of the counter-electromotive force.

Verification is particularly necessary when the motor current is large at startup or at shutdown (output OFF).

$V_{\rm z}$  pin fluctuation width

$20.9~\mathrm{V}$  to  $23.1~\mathrm{V}$

Due to the temperature characteristics (3.5  $\times$  3 mV/°C),

the following applies at an ambient temperature of  $85^{\circ}\mathrm{C}$ :

$$V_z \text{ (max)} = 23.1 + (85 - 25) \times 3.5 \times 3 \text{ mV}$$

$$= 23.73 \text{ V}$$

By taking the measures shown in the diagram on the right to bring the voltage down to  $22~\rm V$ , the following becomes the case:

$$V_z \text{ (max)} = 23.73 - (0.7 - 2 \text{ mV} \times (85 - 25)) \times 3$$

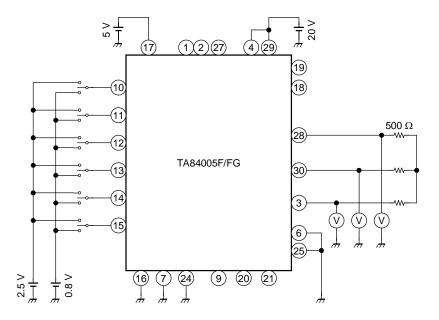

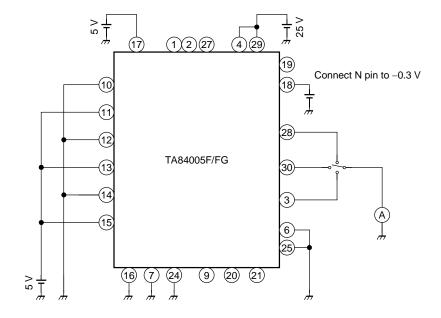

# **Example of Application Circuit**

Note 5: A short circuit between the outputs, or between output and supply or ground may damage the device. Design the output,  $V_{CC}$ ,  $V_{S}$ , and GND lines so that short circuits do not occur.

Test Circuit 1: V<sub>IN</sub> (H), V<sub>IN</sub> (L)

Input  $V_{\mbox{IN}}$  = 0.8 V/2.5 V, measure the output voltage, and test the function.

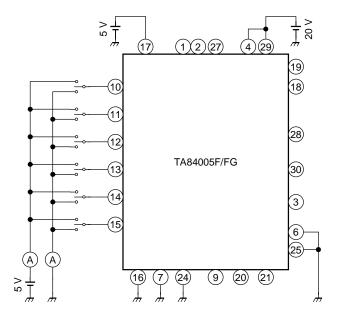

# Test Circuit 2: I<sub>IN</sub> (H), I<sub>IN</sub> (L)

12

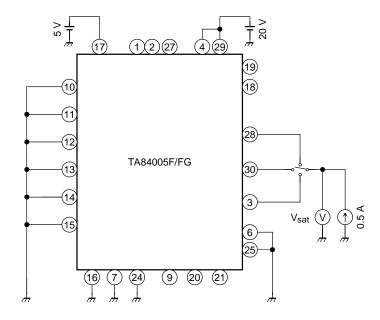

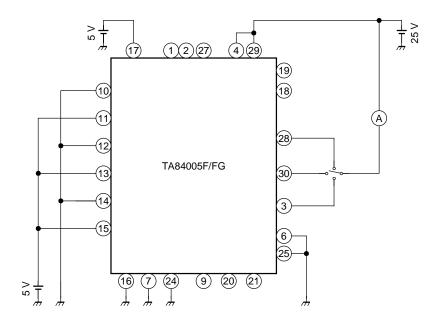

# Test Circuit 3: $I_{CC}1$ , $I_{CC}2$ , $I_{CC}3$ , IM1, IM2, IM3

ICC1, IM1: upper phase 1 ON, lower phase 1 ON (e.g., U-phase: H; V-phase: L; W-phase: Z)

ICC2, IM2: upper phase 1 ON, synchronous regeneration mode (e.g., U-phase: H; V-phase: H; W-phase: Z)

ICC3, IM3: all phases OFF

# Test Circuit 4: V<sub>sat</sub>

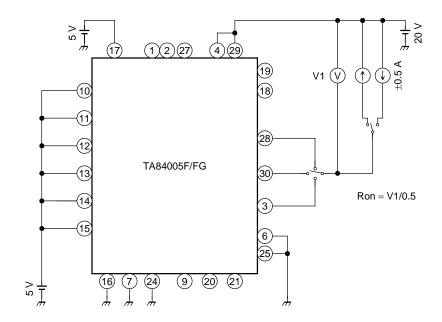

**Test Circuit 5: Ron**

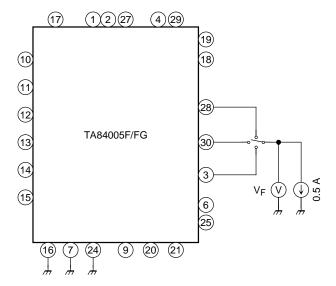

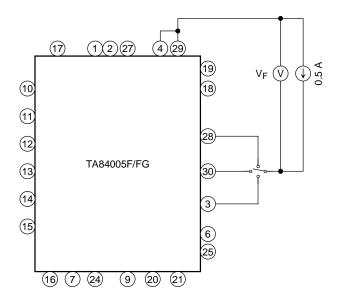

# Test Circuit 6: V<sub>F</sub> (L)

Test Circuit 7: V<sub>F</sub> (H)

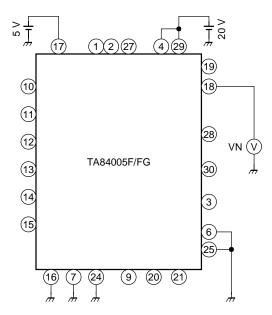

**Test Circuit 8: VN**

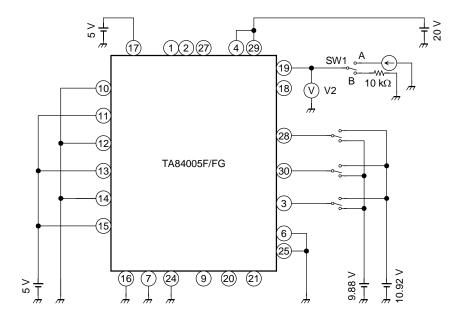

## Test Circuit 9: VCMP, VOL (CMP), ROH (CMP)

- (1) Where output phase 2 is High (10.92 V) and phase 1 is Low (= 9.88 V), set SW1 = A and measure V2 = VOL (CMP).

- (2) Where output phase 1 is High (10.92 V) and phase 2 is Low (9.88 V), set SW1 = B and confirm that  $5 \text{ V} \times 10 \text{ k}\Omega/(10 \text{ k}\Omega + 13 \text{ k}\Omega) < \text{V2} < 5 \text{ V} \times 10 \text{ k}\Omega/(10 \text{ k}\Omega + 7 \text{ k}\Omega)$ .

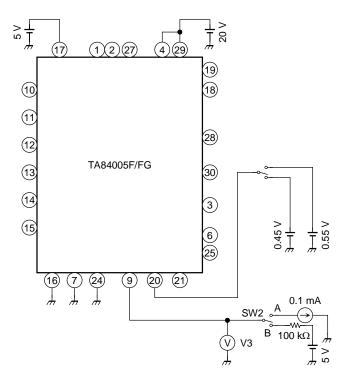

## Test Circuit 10: VRF, VOH (ISD), ROL (ISD)

- (1) Where VISD = 0.55 V, set SW2 = A and measure V3 = VOH (ISD).

- (2) Where VISD = 0.45 V, set SW2 = B and confirm that  $5 \text{ V} \times 14 \text{ k}\Omega/(100 \text{ k}\Omega + 14 \text{ k}\Omega) < \text{V3} < 5 \text{ V} \times 26 \text{ k}\Omega/(26 \text{ k}\Omega + 100 \text{ k}\Omega)$ .

Test Circuit 11: V<sub>Z</sub>

# Test Circuit 12: I<sub>L</sub> (H)

# Test Circuit Test Circuit 13: I<sub>L</sub> (L)

# **Package Dimensions**

Weight: 0.63 g (typ.)

### **Notes on Contents**

### 1. Block Diagrams

Some functional blocks, circuits, or constants may be omitted or simplified in the block diagram for explanatory purposes.

### 2. Equivalent Circuits

The equivalent circuit diagrams may be simplified or some parts of them may be omitted for explanatory purposes.

### 3. Timing Charts

Timing charts may be simplified for explanatory purposes.

### 4. Maximum Ratings

The absolute maximum ratings of a semiconductor device are a set of specified parameter values that must not be exceeded during operation, even for an instant.

If any of these ratings are exceeded during operation, the electrical characteristics of the device may be irreparably altered and the reliability and lifetime of the device can no longer be guaranteed.

Moreover, any exceeding of the ratings during operation may cause breakdown, damage and/or degradation in other equipment. Applications using the device should be designed so that no maximum rating will ever be exceeded under any operating conditions.

Before using, creating and/or producing designs, refer to and comply with the precautions and conditions set forth in this document.

## 5. Application Circuits

The application circuits shown in this document are provided for reference purposes only. Thorough evaluation is required, especially in the phase of mass production design.

In furnishing these examples of application circuits, Toshiba does not grant the use of any industrial property rights.

#### 6. Test Circuits

Components in test circuits are used only to obtain and confirm device characteristics. These components and circuits are not guaranteed to prevent malfunction or failure in application equipment.

### Handling of the IC

Ensure that the product is installed correctly to prevent breakdown, damage and/or degradation in the product or equipment.

## **Overcurrent Protection and Heat Protection Circuits**

These protection functions are intended only as a temporary means of preventing output short circuits or other abnormal conditions and are not guaranteed to prevent damage to the IC.

If the guaranteed operating ranges of this product are exceeded, these protection features may not operate and some output short circuits may result in the IC being damaged.

The overcurrent protection feature is intended to protect the IC from temporary short circuits only. Short circuits persisting over longer periods may cause excessive stress and damage the IC. Systems should be configured so that any overcurrent condition will be eliminated as soon as possible.

#### Counter-electromotive Force

When the motor reverses or stops, the effect of counter-electromotive force may cause the current to flow to the power source.

If the power supply is not equipped with sink capability, the power and output pins may exceed the maximum rating.

The counter-electromotive force of the motor will vary depending on the conditions of use and the features of the motor. Therefore make sure there will be no damage to or operational problem in the IC, and no damage to or operational errors in peripheral circuits caused by counter-electromotive force.

## **RESTRICTIONS ON PRODUCT USE**

030619EBA

- The information contained herein is subject to change without notice.

- The information contained herein is presented only as a guide for the applications of our products. No

responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which

may result from its use. No license is granted by implication or otherwise under any patent or patent rights of

TOSHIBA or others.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor

devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical

stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of

safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of

such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as

- In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- TOSHIBA products should not be embedded to the downstream products which are prohibited to be produced and sold, under any law and regulations.