TOSHIBA BI-CMOS INTEGRATED CIRCUIT SILICON MONOLITHIC

# TB62709NG,TB62709FG

# 7-SEGMENT DRIVERS WITH BUILT-IN DECODERS (COMMON ANODE CAPABILITY, MAXIMUM 4-DIGIT CONTROL)

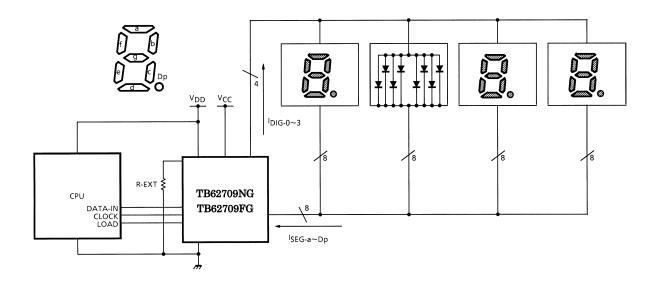

The TB62709NG and TB62709FG are multifunctional, compact, 7-segment LED display drivers.

These ICs can directly drive 7-segment displays and individual LEDs, and can control either a 4-digit display with decimal points, or 32 individual LEDs.

These ICs can also be used with common-anode displays. Their outputs are constant current, the ampere levels at which are set using an external resistor.

A synchronous serial port connects the IC to the CPU.

The different modes of control provided by this device including Duty Control Register Set, Digit Set, Decode Set and Standby Set, are all based on every 16-bit of serial data.

This devices are a product for the Pb free(Sn-Ag).

## FEATURES

- Control circuit power supply voltage

- : V<sub>DD</sub> = 4.5 to 5.5 V

- Digit output rating

- : 17 V / –400 mA

- Decoder output rating

- : 17 V / 50 mA

- Built-in decoder

- : Decodes the numerals 0 to 9, certain alphabetic

- characters, and of course blanks code.

- Digit control function

: Can scan digit outputs DIG-0 to DIG-3 when connected to the common anode pins of a 7-segment display.

- Maximum transmission frequency

- :  $f_{CLK} = 15 \text{ MHz}$

- Decoder outputs (OUT-A to OUT-Dp)

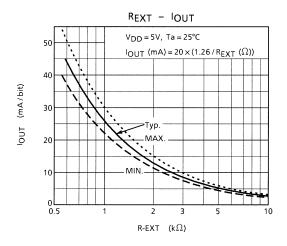

- Output current can be set up to a 40mA maximum using an external resistor.

- Constant current tolerance (Ta =  $25^{\circ}$ C, V<sub>DD</sub> = 5.0 V)

- : Variation between bits =  $\pm 7\%$ , variation between devices

- (including variation between bits) =  $\pm 15\%$  at VCE  $\geq 0.7$  V

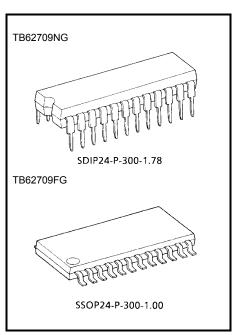

- Package

- : 24-pin SDIP (SDIP24-P-300-1.78)

- 24-pin SSOP (SSOP24-P-300-1.00)

Company Headquarters 3 Northway Lane North Latham, New York 12110 Toll Free: 800.984.5337 Fax: 518.785.4725

Web: www.marktechopto.com | Email: info@marktechopto.com

Weight SDIP24-P-300-1.78 :1.62 g (typ.) SSOP24-P-300-1.00:0.32 g (typ.)

> California Sales Office: 950 South Coast Drive, Suite 225 Costa Mesa, California 92626 Toll Free: 800.984.5337 Fax: 714.850.9314

# **PIN ASSIGNMENT (Top view)**

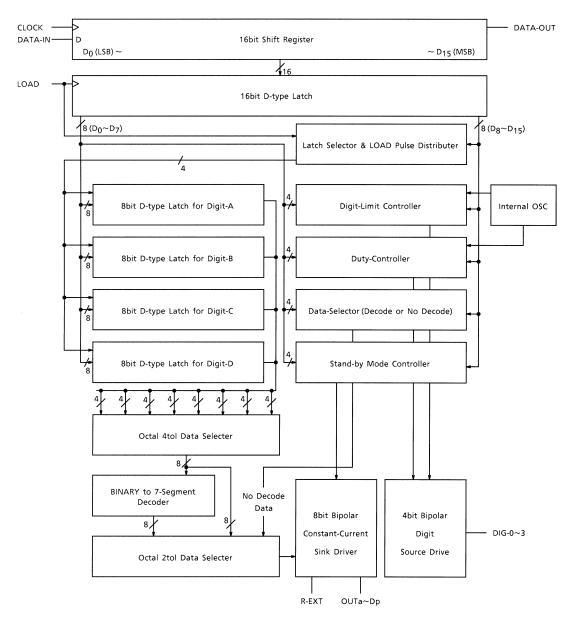

#### **BLOCK DIAGRAM**

# **PIN FUNCTIONS**

| PIN NUMBER     | PIN NAME           | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | V <sub>DD</sub>    | 5 V power pin.                                                                                                                                                                                                                                                                                                                                                                                  |

| 2              | DATA-IN (DI)       | Serial data input pin.                                                                                                                                                                                                                                                                                                                                                                          |

| 3              | CLOCK (CK)         | Clock input pin. The shift register shifts data on the clock's rising edge.                                                                                                                                                                                                                                                                                                                     |

| 4              | LOAD (LD)          | Load signal input pin. The data in the $D_8$ to $D_{15}$ are read on the rising edge and the current load register the is selected from among the Duty Register, the Decode & Digit Register, or Data Registers 0 to 3. The $D_0$ to $D_7$ bits of the 16-bit shift register contain data corresponding to the same registers just described, which are read on the load signal's falling edge. |

| 5~12           | OUT-A to<br>OUT-Dp | Segment drive output pins. The A to Dp outputs correspond to the seven segments. These pins output constant sink current. Connect each of these pins to the corresponding LED's cathode.                                                                                                                                                                                                        |

| 13, 21         | P-GND              | Ground pins, There are two which can be used to ground the output OUT-A to OUT-Dp pins.                                                                                                                                                                                                                                                                                                         |

| 14             | TEST-IN2           | Product test pin. In normal use, be sure to connect to ground.                                                                                                                                                                                                                                                                                                                                  |

| 15             | TEST-IN1           | Product test pin. In normal use, be sure to connect to ground.                                                                                                                                                                                                                                                                                                                                  |

| 16, 17, 19, 20 | DIG-0 to DIG-3     | Digit output pins. Each of these pins can control one of the four seven-segment digits in a display.<br>These pins output the V <sub>CC</sub> pin voltage as a source current output. Connect these pins to the LED anodes.                                                                                                                                                                     |

| 18             | V <sub>CC</sub>    | Power pin for digit output.                                                                                                                                                                                                                                                                                                                                                                     |

| 22             | R-EXT              | Current setting pin for the OUT-A to OUT-Dp pins. Connect a resistor between this pin and ground when setting the current.                                                                                                                                                                                                                                                                      |

| 23             | DATA-OUT (DO)      | Serial data output pin. Use when TB62709N or TB62709F devices are used in cascade connections.                                                                                                                                                                                                                                                                                                  |

| 24             | L-GND              | Ground pin for logic and analog circuits.                                                                                                                                                                                                                                                                                                                                                       |

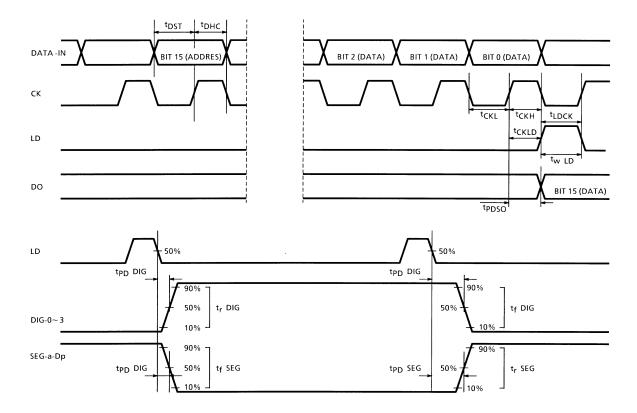

#### TIMING DIAGRAM

#### **DATA INPUT**

- Transfer data to the DATA-IN pin on every 16-bit combining address (8bits) and data (8bits). After the 16<sup>th</sup> clock signal input following this data transfer input a load signal from the LD pin.

- Input the load signal using an Active High pulse. The register address is set on the rising edge of the load pulse. On the subsequent falling edge, the data are read as data of the mode of the register.

# **DESCRIPTION OF OPERATION**

• Data input (SERIAL-IN, CLOCK, LOAD)

The data are input serially using the SERIAL–IN pin. The data input interface consists of a total of three inputs : SERIAL–IN, LOAD, and CLOCK.

Binary code stored in the 16-bit shift register offers control modes including duty Control Register Set, Digitset, Decode Set, and Standby Set,

The data are shifted on the rising edge of the clock, starting from the MSB. Cascade–connecting TB62709NG or TB62709FG devices provides capability for controlling a larger number of digits.

The serial data in the 16-bit shift register are used as follows : the four bits  $D_{15}$  (MSB) to  $D_{12}$  select the IC operating mode (Table 1), while D11 to D8 select the register corresponding to the operating mode (Table 2). Bits D7 to D0 (LSB) of the 16-bit shift register are used for detail settings, such as number of digits in use, character settings in each digit, and light intensity.

The internal registers are loaded on the rising edge of the LOAD signal, which causes loading of data from an external source into the D<sub>15</sub> (MSB) to D8 bits of the shift register, operating mode and the corresponding register selection data. On the subsequent falling edge, the detail setting data of D7 to D0 (LSB) are loaded. Normally LOAD is Low. After a serial transfer of 16bits, the input of a High–level pulse loads the data. Note the following caution : Use the D<sub>15</sub> to D8 setting and the D7 to D0 detail data setting as a pair. If only the D7 to D0 data are input without setting D<sub>15</sub> to D8 an error condition may result, in which the device will not operate normally. If the current mode is set again by a new signal, the data for D<sub>15</sub> to D8 must also be re–input.

#### • Operating precautions

At power-on or after operation in Clear mode (in initial state), set the IC to Normal mode again. Otherwise, the IC will not drive the LED.

Operating the IC in Blank mode (all lights off) or in All On mode (all lights lit) does not affect the internal data. Setting the IC to Normal mode again continues the LED lighting in the state governed by the settings made immediately before mode change.

Normal mode (not Shut Down, Clear, Blank, or All On mode) continues the operations set in Load Register mode. In Normal mode, operations are governed by any new settings made in the Load Register, as soon as the changed setting values are loaded.

| Operating modes (Ta  | ible 1.)                                                                                                                                                                                                                                                                                                       |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| These ICs support th | ne following five operating modes :                                                                                                                                                                                                                                                                            |

| 1. Blank             | Forcibly turns OFF the constant-current output both for data and for digit setting. This mode is not affected by the values in bits $D_{11}$ to $D_0$ .                                                                                                                                                        |

| 2. Normal Operate    | Used for display operations after the settings of the digits are complete. Note that setting this mode without making any other settings will cause display of the numeral 0.                                                                                                                                  |

| 3. Load Register     | Used for the detail settings of the Duty Control Register, for setting Decode / No Decode, for inputting display data, and for setting the number of digits to drive. D <sub>11</sub> to D <sub>0</sub> of the shift register are used for the detail settings of the digits currently being driven (Table 2). |

| 4. All On            | Forcibly turns ON the data-side constant-current output. This mode is not affected by D <sub>11</sub> to D <sub>0</sub> .<br>The initial setting is four digits. When the digits must be changed, use Load Register mode to set the number of digits to drive.                                                 |

| 5. Standby           | Used to set Standby state (in which internal data are not cleared) and to clear data (initialization). The settings in $D_3$ to $D_0$ of the shift register determine the choice between standby state or initialization.                                                                                      |

|                                               |                 |                 |                 | RE              | GISTER DAT                      | ΓA    |                                |          | INITIAL |

|-----------------------------------------------|-----------------|-----------------|-----------------|-----------------|---------------------------------|-------|--------------------------------|----------|---------|

|                                               | D <sub>15</sub> | D <sub>14</sub> | D <sub>13</sub> | D <sub>12</sub> | D <sub>11</sub> ~D <sub>8</sub> | D7~D4 | D <sub>3</sub> ~D <sub>0</sub> | HEX CODE | SETTING |

| BLANK (OUT-n &<br>DIG-0~3 ALL-OFF)            | 0               | 0               | 0               | 0               |                                 |       |                                | 0H       | •       |

| NORMAL (OPERATION)                            | 0               | 0               | 0               | 1               | -                               | -     | -                              | 1H       |         |

| LOAD REGISTER (DUTY,<br>DECODE, DIGIT & DATA) | 0               | 0               | 1               | 0               | х                               | х     | х                              | 2XXXH    |         |

| ALL ON (OUTn ALL-ON)                          | 0               | 0               | 1               | 1               | -                               | _     | -                              | 3Н       |         |

| STAND-BY                                      | 0               | 1               | 0               | 0               | _                               | _     | Х                              | 4XH      |         |

# Table 1 Operating mode settings

X = Input H or L. "-" = Are not affected by the truth table.

• Load Register Selection modes (Table 2)

These modes select the register to provide the data to control the IC operation. The Load Register selection mode is determined by the settings of  $D_{15}$  to  $D_{12}$  and  $D_{11}$  to  $D_8$  of the shift register.

| 1. Duty Register :           | The data in D <sub>7</sub> to D <sub>0</sub> of this register set the digit output duty cycle.<br>Duty settings can be made in 16 steps from $0 / 16$ to $15 / 16$ .<br>(See Table 3)                                             |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2. Decode & Digit Register : | Sets Decode / No Decode and the number of digits to drive. Decode can be set using D7 to D4.<br>The number of digits driven can be set using D3 to D0. Decode / No Decode and the number of digits driven are set simultaneously. |

| 3. Data registers 0 to 3 3   | Set the display data corresponding to DIG0 to DIG3 respectively. D7 to D0 of the shift register are used to set the display data.                                                                                                 |

|                              |                                  |                 |                 | REGISTER       | R DATA         |                                |                                |             |

|------------------------------|----------------------------------|-----------------|-----------------|----------------|----------------|--------------------------------|--------------------------------|-------------|

|                              | D <sub>15</sub> ~D <sub>12</sub> | D <sub>11</sub> | D <sub>10</sub> | D <sub>9</sub> | D <sub>8</sub> | D <sub>7</sub> ~D <sub>4</sub> | D <sub>3</sub> ~D <sub>0</sub> | HEX<br>CODE |

| LOAD DUTY REGISTER           | 2H                               | 0               | 0               | 0              | 0              | Х                              | Х                              | 20XXH       |

| LOAD DECODE & DIGIT REGISTER | 2H                               | 0               | 0               | 0              | 1              | Х                              | Х                              | 21XXH       |

| LOAD DATA REGISTER 0         | 2H                               | 0               | 0               | 1              | 0              | Х                              | Х                              | 22XXH       |

| LOAD DATA REGISTER 1         | 2H                               | 0               | 0               | 1              | 1              | х                              | х                              | 23XXH       |

| LOAD DATA REGISTER 2         | 2H                               | 0               | 1               | 0              | 0              | Х                              | Х                              | 24XXH       |

| LOAD DATA REGISTER 3         | 2H                               | 0               | 1               | 0              | 1              | Х                              | Х                              | 25XXH       |

# Table 2 Load register selection

X = Input H or L.

# **DUTY CONTROL REGISTER SETTINGS**

• Duty Control Register detail settings and operation (Table 3)

Writing 20H to  $D_{15}$ ~ $D_8$  and writing 0~FH to  $D_3$ ~ $D_0$  sets the duty cycle shown in the following table for the digit-side source driver output. The duty cycle can be set in 16 steps.

The initial setting is 15 / 16. After Data Clear, the setting is also 15 / 16.

The current settings continue until changed (by reset execution, or to the initial state, Data Clear state, or standby state).

|            |                                 |       | REGIS          | TER DAT        | Ą              |                |          | INITIAL SETTING |

|------------|---------------------------------|-------|----------------|----------------|----------------|----------------|----------|-----------------|

| DUTY CYCLE | D <sub>15</sub> ~D <sub>8</sub> | D7~D4 | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | HEX CODE | INITIAL SETTING |

| 0 / 16     | 20H                             | —     | 0              | 0              | 0              | 0              | 20X0H    |                 |

| 1 / 16     | 20H                             | —     | 0              | 0              | 0              | 1              | 20X1H    |                 |

| 2 / 16     | 20H                             | _     | 0              | 0              | 1              | 0              | 20X2H    |                 |

| 3 / 16     | 20H                             | _     | 0              | 0              | 1              | 1              | 20X3H    |                 |

| 4 / 16     | 20H                             | _     | 0              | 1              | 0              | 0              | 20X4H    |                 |

| 5 / 16     | 20H                             | _     | 0              | 1              | 0              | 1              | 20X5H    |                 |

| 6 / 16     | 20H                             | _     | 0              | 1              | 1              | 0              | 20X6H    |                 |

| 7 / 16     | 20H                             | _     | 0              | 1              | 1              | 1              | 20X7H    |                 |

| 8 / 16     | 20H                             | _     | 1              | 0              | 0              | 0              | 20X8H    |                 |

| 9 / 16     | 20H                             | _     | 1              | 0              | 0              | 1              | 20X9H    |                 |

| 10 / 16    | 20H                             | _     | 1              | 0              | 1              | 0              | 20XAH    |                 |

| 11 / 16    | 20H                             | _     | 1              | 0              | 1              | 1              | 20XBH    |                 |

| 12 / 16    | 20H                             | _     | 1              | 1              | 0              | 0              | 20XCH    |                 |

| 13 / 16    | 20H                             | _     | 1              | 1              | 0              | 1              | 20XDH    |                 |

| 14 / 16    | 20H                             | _     | 1              | 1              | 1              | 0              | 20XEH    |                 |

| 15 / 16    | 20H                             | _     | 1              | 1              | 1              | 1              | 20XFH    | •               |

Table 3

Duty control register settings

X = Input H or L. "-" = Are not affected by the truth table.

## **DIGIT SETTINGS**

• Setting the number of digits (Table 4)

Writing 21H to D<sub>15</sub>~D<sub>8</sub> and at the same step writing 0H~3H to D<sub>3</sub>~D<sub>0</sub> sets the number of digits to a maximum of four the display. The initial setting is four digits, and four will also be set by a Data Clear.

The current settings continue until changed (by reset execution, or to the initial state, Data Clear state, or standby state).

When changing the number of digits, also set D7 to D4.

|                     |                                 |       | F              | REGISTER DATA  |                |                |          |         |  |  |  |

|---------------------|---------------------------------|-------|----------------|----------------|----------------|----------------|----------|---------|--|--|--|

|                     | D <sub>15</sub> ~D <sub>8</sub> | D7~D4 | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | HEX CODE | SETTING |  |  |  |

| ACTIVATED DIG0 ONLY | 21H                             | Х     | 0              | 0              | 0              | 0              | 21X0H    |         |  |  |  |

| ACTIVATED DIG0~1    | 21H                             | Х     | 0              | 0              | 0              | 1              | 21X1H    |         |  |  |  |

| ACTIVATED DIG0~2    | 21H                             | Х     | 0              | 0              | 1              | 0              | 21X2H    |         |  |  |  |

| ACTIVATED DIG0~3    | 21H                             | х     | 0              | 0              | 1              | 1              | 21X3H    | •       |  |  |  |

#### Table 4 Digit settings

X = Input H or L.

## **DECODE SETTINGS**

• Decode settings (Table 5)

The settings for Decode are the same as the settings for the number of digits, described under setting, above. Writing 21H to  $D_{15}$ ~ $D_8$  and writing 0~1H to  $D_7$ ~ $D_4$  set Decode mode.

When using this IC for controlling the lighting on individual LEDs used for a dot matrix rather than a 7-segment display, set to No Decode.

As Table 6 shows,  $D_0$  in the data register is used to turn OUT-a ON and OFF;  $D_1$  turns OUT-b ON and OFF. The initial setting is Decode mode, and Decode mode will also be set by a Data Clear.

The current settings continue until changed (by reset execution, or to the initial state, Data Clear state, or standby state).

Since  $D_3$  to  $D_0$  are also used for setting the number of digits, when changing the Decode setting, also set  $D_3$  to  $D_0$ .

|                          |                                 | REGISTER DATA  |                |                |                |                                |          |         |  |  |

|--------------------------|---------------------------------|----------------|----------------|----------------|----------------|--------------------------------|----------|---------|--|--|

|                          | D <sub>15</sub> ~D <sub>8</sub> | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> ~D <sub>0</sub> | HEX CODE | SETTING |  |  |

| PASS DECODER (NO DECODE) | 21H                             | 0              | 0              | 0              | 0              | х                              | 210XH    |         |  |  |

| DECODE                   | 21H                             | 0              | 0              | 0              | 1              | Х                              | 211XH    | •       |  |  |

Table 5Decode settings

X = Input H or L.

# THE FOLLOWING TABLE SHOWS THE CORRESPONDENCE BETWEEN THE SERIAL DATA AND THE OUTPUT PINS WHEN NO DECODE IS SET

| REGISTER DATA  | OUTPUT | INITIAL STATE | NOTE                                            |  |  |

|----------------|--------|---------------|-------------------------------------------------|--|--|

| D <sub>0</sub> | OUT-a  | L             |                                                 |  |  |

| D <sub>1</sub> | OUT-b  | L             |                                                 |  |  |

| D <sub>2</sub> | OUT-c  | L             |                                                 |  |  |

| D <sub>3</sub> | OUT-d  | L             | Output is ON when data<br>= H and OFF when data |  |  |

| D <sub>4</sub> | OUT-e  | L             | = L.                                            |  |  |

| D <sub>5</sub> | OUT-f  | L             |                                                 |  |  |

| D <sub>6</sub> | OUT-g  | L             |                                                 |  |  |

| D <sub>7</sub> | OUT-Dp | L             |                                                 |  |  |

#### Table 6 Correspondence between serial data and output pins in no decode mode

#### **STANDBY SETTINGS**

• Standby mode settings and operation (Table 7)

Writing 4H to  $D_{15}$ ~ $D_{12}$  and writing 0H to  $D_3$ ~ $D_0$  sets Standby mode. Writing 4H to  $D_{15}$ ~ $D_{12}$  and writing 1H to  $D_3$ ~ $D_0$  sets All Data Clear mode.

Standby mode maintains the settings made immediately before this mode came in force, turns the output current OFF, and controls the bias current flowing in the internal circuits. All Data Clear resets all settings to their initial states.

|                         |                                 | REGISTER DATA |                |                |                |                |          |  |  |

|-------------------------|---------------------------------|---------------|----------------|----------------|----------------|----------------|----------|--|--|

|                         | D <sub>15</sub> ~D <sub>8</sub> | D7~D4         | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | HEX CODE |  |  |

| STANDBY (NO DATA CLEAR) | 4-H                             | —             | 0              | 0              | 0              | 0              | 4XX0H    |  |  |

| ALL DATA CLEAR          | 4-H                             | —             | 0              | 0              | 0              | 1              | 4XX1H    |  |  |

#### Table 7 Standby settings

X = Input H or L. "-" Are not affected by the truth table.

### LIST OF CHARACTER GENERATOR DECODING DATA

• Character generator decoding (Table 8)

As the following table shows, the characters are decoded using combinations of the data in  $D_0$  to  $D_3$  and  $D_5$  to  $D_4$ . In decoding,  $D_6$  is used exclusively for setting decimal points.

Spaces where  $(D_0, D_1, D_2, D_3) = (0000)$  and  $(D_5, D_4) = (01)$  are regarded as blank.

|    |                | D <sub>0</sub> | 0 | 1   | 0  | 1 | 0 | 1          | 0  | 1  | 0 | 1  | 0 | 1 | 0 | 1 | 0 | 1 |

|----|----------------|----------------|---|-----|----|---|---|------------|----|----|---|----|---|---|---|---|---|---|

|    |                | D <sub>1</sub> | 0 | 0   | 1  | 1 | 0 | 0          | 1  | 1  | 0 | 0  | 1 | 1 | 0 | 0 | 1 | 1 |

|    |                | D <sub>2</sub> | 0 | 0   | 0  | 0 | 1 | 1          | 1  | 1  | 0 | 0  | 0 | 0 | 1 | 1 | 1 | 1 |

|    |                | D <sub>3</sub> | 0 | 0   | 0  | 0 | 0 | 0          | 0  | 0  | 1 | 1  | 1 | 1 | 1 | 1 | 1 | 1 |

| D5 | D <sub>4</sub> | HEX            | 0 | 1   | 2  | 3 | 4 | 5          | 6  | 7  | 8 | 9  | А | В | С | D | Е | F |

| 0  | 0              | 0              | 0 | :   | ÷. | 3 | × | 5          | 8  | ÷. | 8 | 9  | 8 | ÷ | ÷ | đ | 8 | Ģ |

| 0  | 1              | 1              |   | :-: | сi | ' | ÷ | <u>е</u> ; | 1. | ψĥ | 0 | y. | - | ÷ | ė | 3 | ÷ | Э |

#### Table 8 List of character generator decoding data

| D <sub>7</sub> | D <sub>6</sub> |        |

|----------------|----------------|--------|

| Х              | 0              | Dp OFF |

| Х              | 1              | Dp ON  |

## DATA INPUT

(Example 1: Displays and blinks characters a, b, c and d in digits 0, 1, 2 and 3 respectively. Period after "d" part of it, or a sentence-end marker?)

| STEP | D15~<br>D12 | D11~<br>D8 | D7~<br>D4 | D3~<br>D0 | DIG<br>-0~3 | SEG<br>−a, b, c, d, e, f, g | SEG<br>-Dp | MODE                           | DISPLAY<br>INDICATE |

|------|-------------|------------|-----------|-----------|-------------|-----------------------------|------------|--------------------------------|---------------------|

| 0    | _           | _          | _         | _         | OFF         | OFF                         | OFF        | At power-on<br>( = CLEAR MODE) | ALL BLANK           |

| 1    | 0010        | 0000       | XXXX      | 1111      | OFF         | OFF                         | OFF        | DUTY = 15 / 16                 | ALL BLANK           |

| 2    | 0010        | 0001       | 0001      | 0011      | OFF         | OFF                         | OFF        | DECODE, 4DIG                   | ALL BLANK           |

| 3    | 0010        | 0010       | X000      | 1010      | OFF         | OFF                         | OFF        | DIG−0 = a                      | ALL BLANK           |

| 4    | 0010        | 0011       | X000      | 1011      | OFF         | OFF                         | OFF        | DIG-1 = b                      | ALL BLANK           |

| 5    | 0010        | 0100       | X000      | 1100      | OFF         | OFF                         | OFF        | DIG-2 = c                      | ALL BLANK           |

| 6    | 0010        | 0101       | X000      | 1101      | OFF         | OFF                         | OFF        | DIG-3 = d                      | ALL BLANK           |

| 7    | 0001        | XXXX       | XXXX      | XXXX      | ON          | ON                          | OFF        | NORMAL                         | a-b-c-d             |

| 8    | 0010        | 0000       | XXXX      | 1000      | ON          | ON                          | OFF        | DUTY = 8 / 16                  | a-b-c-d             |

| 9    | 0000        | XXXX       | XXXX      | XXXX      | OFF         | OFF                         | OFF        | BLANK                          | ALL BLANK           |

| 10   | 0001        | XXXX       | XXXX      | XXXX      | ON          | ON                          | OFF        | NORMAL                         | a-b-c-d             |

| 11   | 0000        | XXXX       | XXXX      | XXXX      | OFF         | OFF                         | OFF        | BLANK                          | ALL BLANK           |

| 12   | 0001        | XXXX       | XXXX      | XXXX      | ON          | ON                          | OFF        | NORMAL                         | a-b-c-d             |

| 13   | 0000        | XXXX       | XXXX      | XXXX      | OFF         | OFF                         | OFF        | BLANK                          | ALL BLANK           |

| 14   | 0001        | XXXX       | XXXX      | XXXX      | ON          | ON                          | OFF        | NORMAL                         | a-b-c-d             |

| 15   | 0100        | XXXX       | XXXX      | 0000      | OFF         | OFF                         | OFF        | STAND-BY<br>(SHUT DOWN)        | ALL BLANK           |

#### **DATA INPUT**

(Example 2: Scroll-lights digits 0, 1, 2, 3 = a., -b., -c., -d. ?SEQ; and please explain the data on rhs? digit by digit (with decimal points))

| STEP | D15~<br>D12 | D11~D<br>8 | D7~<br>D4 | D3~<br>D0 | DIG<br>-0~3 | SEG<br>−a, b, c, d, e, f, g | SEG<br>-Dp | MODE                           | DISPLAY<br>INDICATE |

|------|-------------|------------|-----------|-----------|-------------|-----------------------------|------------|--------------------------------|---------------------|

| 0    | _           | _          | _         | _         | OFF         | OFF                         | OFF        | At power-on<br>( = CLEAR MODE) | ALL BLANK           |

| 1    | 0010        | 0000       | XXXX      | 1111      | OFF         | OFF                         | OFF        | DUTY = 15 / 16                 | ALL BLANK           |

| 2    | 0010        | 0001       | 0001      | 0011      | OFF         | OFF                         | OFF        | DECODE, 4DIG                   | ALL BLANK           |

| 3    | 0010        | 0010       | X100      | 1010      | OFF         | OFF                         | OFF        | DIG-0 = a.                     | ALL BLANK           |

| 4    | 0010        | 0011       | X001      | 0000      | OFF         | OFF                         | OFF        | DIG-1 = blank                  | ALL BLANK           |

| 5    | 0010        | 0100       | X001      | 0000      | OFF         | OFF                         | OFF        | DIG−2 = blank                  | ALL BLANK           |

| 6    | 0010        | 0101       | X001      | 0000      | OFF         | OFF                         | OFF        | DIG-3 = blank                  | ALL BLANK           |

| 7    | 0001        | XXXX       | XXXX      | XXXX      | ON          | ON                          | ON         | NORMAL                         | a                   |

| 8    | 0010        | 0010       | X001      | 0000      | OFF         | ON                          | OFF        | DIG-0 = blank                  | ALL BLANK           |

| 9    | 0010        | 0011       | X100      | 1011      | ON          | ON                          | ON         | DIG-1 = b.                     | -b                  |

| 10   | 0010        | 0011       | X001      | 0000      | OFF         | ON                          | OFF        | DIG−1 = blank                  | ALL BLANK           |

| 11   | 0010        | 0100       | X100      | 1100      | ON          | ON                          | ON         | DIG−2 = c.                     | c                   |

| 12   | 0010        | 0100       | X001      | 0000      | OFF         | ON                          | OFF        | DIG−2 = blank                  | ALL BLANK           |

| 13   | 0010        | 0101       | X100      | 1101      | ON          | ON                          | ON         | DIG-3 = d.                     | d.                  |

| 14   | 0100        | XXXX       | XXXX      | 0000      | OFF         | OFF                         | OFF        | STAND-BY<br>(SHUT DOWN)        | ALL BLANK           |

## STATE TRANSITION DIAGRAM

# MAXIMUM RATINGS (Ta = 25°C)

| CHARACTERISTIC                       |           | SYMBOL                            | RATING         | UNIT |

|--------------------------------------|-----------|-----------------------------------|----------------|------|

| Supply Voltage for Logic<br>Circuits |           | V <sub>DD</sub>                   | 7.0            | V    |

| Supply Voltage                       |           | V <sub>CC</sub>                   | 17             | V    |

| DIG-0 to DIG-3 Output<br>Current     |           | I <sub>DIG</sub>                  | -400           | mA   |

| OUT-a to Dp Output Current           |           | IOUT                              | 50             | mA   |

| Output Current for Logic Block       |           | I <sub>OH</sub> / I <sub>OL</sub> | ±5             | mA   |

| Input Voltage                        |           | V <sub>IN</sub>                   | -0.3~VDD + 0.3 | V    |

| Operating Frequ                      | ency      | fск                               | 15.0           | MHz  |

| Total Supply Cu                      | rrent     | I <sub>VDD</sub>                  | 400            | mA   |

| Power                                | TB62709NG | D-                                | 1.78           | W    |

| Dissipation                          | TB62709FG | PD                                | 0.62           | vv   |

| Operating Temp                       | erature   | T <sub>opr</sub>                  | -40~85         | °C   |

| Storage Temperature                  |           | T <sub>stg</sub>                  | -55~150        | °C   |

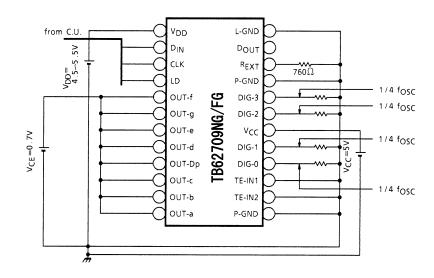

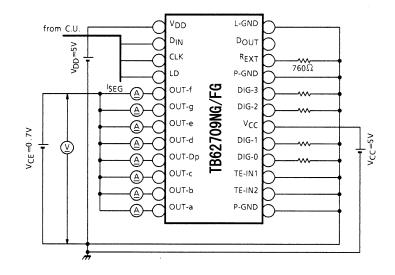

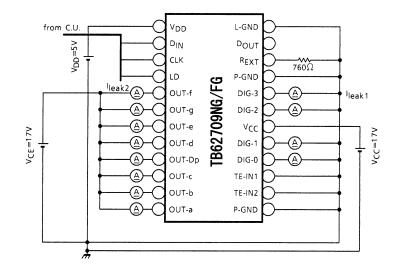

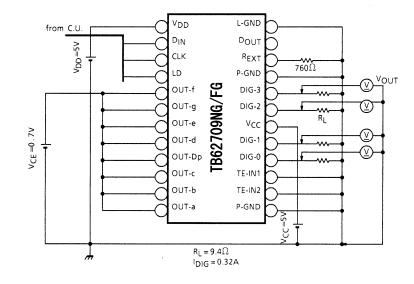

#### ELECTRICAL CHARACTERISTICS (Unless otherwise stated, $V_{DD}$ = 5.0 V, $V_{CC}$ = 5.0 V, $R_{EXT}$ = 760 $\Omega$ , Ta = -40~85°C)

| CHARACTERISTIC                                     | SYMBOL             | TEST<br>CIR-<br>CUIT | TEST CONDITION                                                                                     | MIN | TYP. | MAX | UNIT |

|----------------------------------------------------|--------------------|----------------------|----------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Operating Power Supply<br>Current for Output Block | I <sub>CC1</sub>   | 1                    | SET NORMAL OPE. MODE, REXT<br>= 760 Ω @OUT-a~Dp ALL ON, Ta<br>= 25°C                               | _   | 300  | _   | mA   |

|                                                    | I <sub>CC2</sub>   | 1                    | SET NORMAL OPE. MODE, REXT<br>= 760 $\Omega$ @OUT-a~Dp ALL ON V <sub>CC</sub><br>= 12 V, Ta = 25°C | _   | 320  | _   | IIIA |

| DIG-0 to DIG-3 Scan<br>Frequency                   | fosc               | 2                    | NORMAL OPE. MODE,<br>V <sub>DD</sub> = 4.5~5.5 V                                                   | 240 | 480  | 960 | Hz   |

| OUT-a to Dp Output Sink<br>Current                 | I <sub>SEG</sub>   | 3                    | NORMAL OPE. MODE,<br>V <sub>CE</sub> = 0.7 V, R <sub>EXT</sub> = 760 $\Omega$                      | 29  | 34   | 40  | mA   |

| DIG-0 to 3 Output Leakage<br>Current               | I <sub>leak1</sub> | 4                    | ALL OFF MODE, V <sub>CC</sub> = 17 V                                                               | _   | _    | -20 | μA   |

| OUT-a to Dp Output Leakage<br>Current              | I <sub>leak2</sub> | 4                    | ALL OFF MODE, V <sub>CC</sub> = 17 V                                                               | _   | _    | 20  | μA   |

| DIG-0 to 3 Output Voltage                          | V <sub>OUT</sub>   | 5                    | NORMAL OPE. MODE,<br>I <sub>DIG</sub> = -320 mA                                                    | 3.0 | _    | _   | V    |

# Logic block

| CHARACTERISTIC                                       | SYMBOL           | TEST<br>CIR-<br>CUIT | TEST CONDITION                                                                          | MIN | TYP.            | MAX  | UNIT |

|------------------------------------------------------|------------------|----------------------|-----------------------------------------------------------------------------------------|-----|-----------------|------|------|

| Static Power Supply Current for                      | I <sub>DD1</sub> | 6                    | STANDBY MODE, Ta = 25°C                                                                 | —   | —               | 200  | μA   |

| Logic Circuits                                       | I <sub>DD2</sub> | 6                    | BLANK MODE, Ta = 25°C                                                                   | —   | —               | 12.5 | mA   |

| Operating Power Supply<br>Current for Logic Circuits | I <sub>DD3</sub> | 6                    | NORMAL OPE. MODE,<br>f <sub>CLK</sub> = 10MHz,<br>DATA-IN : OUT-a~Dp = ON,<br>Ta = 25°C | _   | _               | 20.5 | mA   |

| High Input Current for Logic<br>Circuits             | IIH              | _                    | DATA-IN, LOAD & CLOCK :<br>V <sub>IN</sub> = 5 V                                        | _   | _               | 1    | μA   |

| Low Input Current for Logic<br>Circuits              | IIL              | _                    | DATA-IN, LOAD & CLOCK :<br>V <sub>IN</sub> = 0 V                                        | _   | _               | -1   | μA   |

| High Output Voltage for Logic                        | V <sub>OH1</sub> | 6                    | DATA-OUT, I <sub>OH</sub> = -1.0 mA                                                     | 4.6 | _               | _    | V    |

| Circuits                                             | V <sub>OH2</sub> | 6                    | DATA−OUT, I <sub>OH</sub> = −1.0 µA                                                     | _   | V <sub>DD</sub> | _    | v    |

| Low Output Voltage for Logic                         | V <sub>OL1</sub> | 6                    | DATA-OUT, I <sub>OL</sub> = 1.0 mA                                                      | _   | _               | 0.4  | v    |

| Circuits                                             | V <sub>OL2</sub> | 6                    | DATA-OUT, I <sub>OH</sub> = 1.0 μA                                                      | _   | 0.1             | _    | v    |

| Clock Frequency                                      | fclk             | 6                    | CASCADE CONNECTED,<br>Ta = −40~85°C                                                     | 10  | _               | _    | MHz  |

# SWITCHING CHARACTERISTICS (Unless otherwise stated, $V_{DD}$ = 5.0 V, $V_{CC}$ = 5.0 V, Ta = 25°C)

| CHARACTERISTIC                         | SYMBOL                | TEST<br>CIR-<br>CUIT | TEST CONDITION         | MIN | TYP. | MAX  | UNIT |

|----------------------------------------|-----------------------|----------------------|------------------------|-----|------|------|------|

| Data Hold Time<br>(D-IN-CLOCK)         | tDHO                  | _                    | _                      | _   | 10   | _    | ns   |

| Data Setup Time<br>(D-IN-CLOCK)        | t <sub>DST</sub>      | _                    | —                      | _   | 20   | _    | ns   |

| Serial Output Delay Time               | t <sub>pHL</sub> -SO  |                      | C <sub>L</sub> = 10 pF |     | 25   | —    | ns   |

| (CLOCK-D-OUT)                          | t <sub>pLH</sub> -SO  |                      | C <sub>L</sub> = 10 pF | -   | 25   | _    | 115  |

| High Clock Pulse Width                 | <sup>t</sup> скн      | -                    | —                      |     | 30   | -    | ns   |

| Low Clock Pulse Width                  | t <sub>CKL</sub>      | -                    | —                      | —   | 30   | —    | ns   |

| Load Pulse Width                       | t <sub>wLD</sub>      | -                    | —                      | _   | 100  | _    | ns   |

| Load Clock Time<br>(CLOCK-LOAD)        | <sup>t</sup> CLK-LD   | _                    | -                      | _   | 50   | _    | ns   |

| Clock Load Time<br>(LOAD-CLOCK)        | <sup>t</sup> LD-CLK   | _                    | _                      | _   | 50   | _    | ns   |

| OUT-a to Dp Output Delay               | t <sub>pHL</sub> -SEG |                      | C <sub>L</sub> = 10 pF | _   | _    | 5.0  | μs   |

| Time (LOAD-OUTn)                       | t <sub>pLH</sub> -SEG |                      | C <sub>L</sub> = 10 pF | _   | _    | 5.0  | μs   |

| OUT-a to Dp Output Rise Time<br>(OUTn) | t <sub>r</sub> SEG    | _                    | C <sub>L</sub> = 10 pF | 0.2 | 1.0  | _    | μs   |

| OUT-a to Dp Output Fall Time<br>(OUTn) | t <sub>f</sub> SEG    | _                    | C <sub>L</sub> = 10 pF | 0.2 | 1.0  | _    | μs   |

| DIG-0~DIG-3 Output Delay               | t <sub>pHL</sub> -DIG |                      | C <sub>L</sub> = 10 pF | _   | _    | 10.0 | 110  |

| Time (LOAD-DIGn)                       | t <sub>pLH</sub> -DIG |                      | C <sub>L</sub> = 10 pF | _   | _    | 10.0 | μs   |

| DIG-0~DIG-3 Output Rise<br>Time (DIGn) | t <sub>r</sub> DIG    | _                    | C <sub>L</sub> = 10 pF | 0.4 | 2.0  | _    | μs   |

| DIG-0~DIG-3 Output Fall Time<br>(DIGn) | t <sub>f</sub> DIG    |                      | C <sub>L</sub> = 10 pF | 0.4 | 2.0  | —    | μs   |

# RECOMMENDED OPERATING CONDITIONS

# (Unless otherwise stated, $V_{DD}$ = 5.0 V, $V_{CC}$ = 5.0 V, Ta = -40~85°C)

| CHARACTERISTIC                          | SYMBOL           | TEST<br>CIR-<br>CUIT | TEST CONDITION           | MIN | TYP. | MAX  | UNIT |

|-----------------------------------------|------------------|----------------------|--------------------------|-----|------|------|------|

| Supply Voltage for Output Block         | V <sub>CC</sub>  | -                    | —                        | 4.0 | _    | 6.0  | V    |

| DIG-0 to DIG-3 Output Source<br>Current | I <sub>DIG</sub> | _                    | V <sub>OUT</sub> = 3.0 V | _   | _    | -320 | mA   |

| OUT-a to OUT-Dp Output Sink<br>Current  | I <sub>SEG</sub> | _                    | V <sub>CE</sub> = 0.7 V  | _   | _    | 40   | mA   |

#### Logic block

| CHARACTERISTIC                           | SYMBOL          | TEST<br>CIR-<br>CUIT | TEST CONDITION                                              | MIN                    | TYP. | MAX                    | UNIT |

|------------------------------------------|-----------------|----------------------|-------------------------------------------------------------|------------------------|------|------------------------|------|

| Supply Voltage for Logic Block           | V <sub>DD</sub> | _                    | —                                                           | 4.5                    | _    | 5.5                    | V    |

| High Input Current for Logic<br>Circuits | IIН             | -                    | DATA-IN, LOAD & CLOCK,<br>V <sub>IN</sub> = V <sub>DD</sub> |                        | _    | 1                      | μA   |

| Low Input Current for Logic<br>Circuits  | Ι <sub>ΙL</sub> | _                    | DATA-IN, LOAD & CLOCK,<br>V <sub>IN</sub> = 0V              |                        | _    | -1                     | μA   |

| High Input Voltage for Logic<br>Circuits | V <sub>IH</sub> | _                    | —                                                           | 0.7<br>V <sub>DD</sub> | _    | _                      | V    |

| Low Input Voltage for Logic<br>Circuits  | VIL             | _                    | _                                                           | _                      | _    | 0.3<br>V <sub>DD</sub> | V    |

# SWITCHING CONDITIONS

| CHARACTERISTIC                            | SYMBOL             | TEST<br>CIR-<br>CUIT | TEST CONDITION         | MIN | TYP. | MAX | UNIT |

|-------------------------------------------|--------------------|----------------------|------------------------|-----|------|-----|------|

| Data Hold Time<br>(D-IN-CLOCK)            | tDHO               | _                    | —                      | 30  | _    | _   | ns   |

| Data Setup Time<br>(D-IN-CLOCK)           | t <sub>DST</sub>   | _                    | —                      | 50  | _    |     | ns   |

| Serial Output Delay Time<br>(CLOCK-D-OUT) | t <sub>PDSO</sub>  | _                    | C <sub>L</sub> = 10 pF | 50  | _    | -   | ns   |

| High Clock Pulse Width                    | tскн               | —                    | _                      | 30  | _    | _   | ns   |

| Low Clock Pulse Width                     | t <sub>CKL</sub>   | _                    | _                      | 30  | _    | _   | ns   |

| Load Pulse Width                          | t <sub>wLD</sub>   | —                    | —                      | 150 | _    | —   | ns   |

| Load Clock Time<br>(CLOCK-LOAD)           | <sup>t</sup> CLKLD | _                    | _                      | 100 | _    | _   | ns   |

| Clock Load Time<br>(LOAD-CLOCK)           | <sup>t</sup> ldclk | _                    | _                      | 100 | _    | _   | ns   |

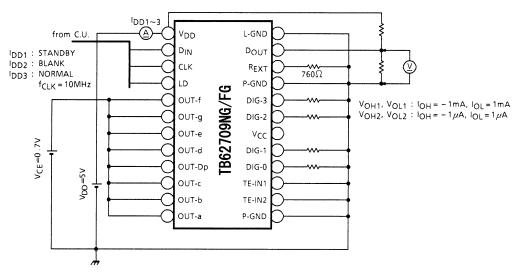

# **TEST CIRCUITS**

(1) Icc1, Icc2

(2) f<sub>OSC</sub>

# (3) I<sub>SEG</sub>

# (4) I<sub>leak1</sub>, I<sub>leak2</sub>

(5) V<sub>OUT</sub>

# (6) $I_{DD1}$ , $I_{DD2}$ , $I_{DD3}$ , $V_{OH1}$ , $V_{OH2}$ , $V_{OL1}$ , $V_{OL2}$ , $f_{CLK}$

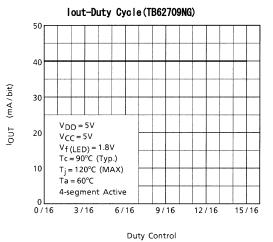

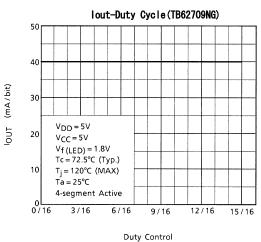

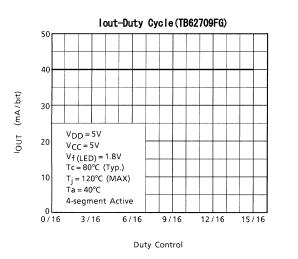

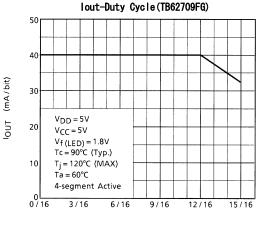

# DUTY CYCLE SETTINGS AND OUTPUT CURRENT VALUES

Duty Control

# EXTERNAL RESISTANCE AND OUTPUT CURRENT VALUES

TOSHIBA

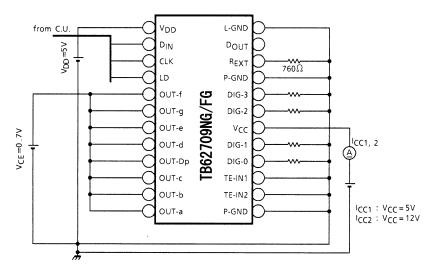

The following diagram shows application circuits.

Because operation may be unstable due to influences such as the electromagnetic induction of the wiring, the IC should be located as close as possible to the LED.

The L–GND and P–GND of the IC are connected to the substrate in the IC.

Take care to avoid a potential difference exceeding 0.4V at two pins.

When executing the pattern layout, Toshiba recommends not including inductance components in the GND or output pin lines, and not inserting capacitance components exceeding 50pF between the REXT and GND.

# **APPLICATION CIRCUIT EXAMPLE** (Connection example)

#### **PRECAUTIONS for USING**

Utmost care is necessary in the design of the output line,  $V_{CC}$  ( $V_{DD}$ ) and (L-GND, P-GND) line since IC may be destroyed due to short-circuit between outputs, air contamination fault, or fault by improper grounding.

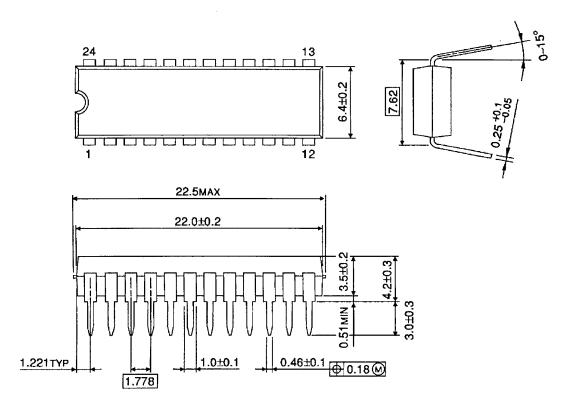

# Package Dimensions

SDIP24-P-300-1.78

Unit : mm

Weight: 1.62 g (typ.)

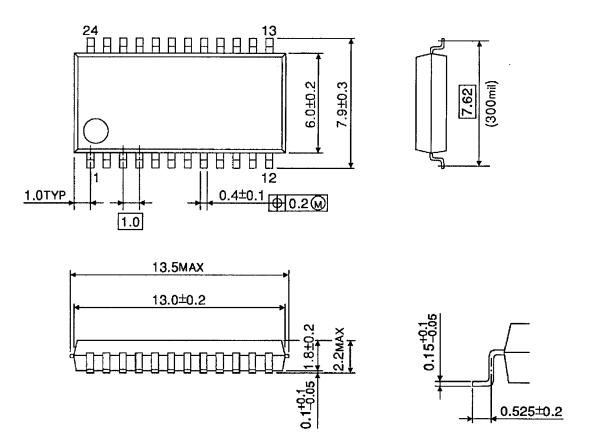

# Package Dimensions

SSOP24-P-300-1.00

Unit : mm

Weight: 0.32 g (typ.)

About solderability, following conditions were confirmed

#### Solderability

- (1) Use of Sn-63Pb solder Bath

- solder bath temperature = 230°C

- · dipping time = 5 seconds

- $\cdot$  the number of times = once

- use of R-type flux

- (2) Use of Sn-3.0Ag-0.5Cu solder Bath

- solder bath temperature = 245°C

- · dipping time = 5 seconds

- $\cdot$  the number of times = once

- · use of R-type flux

#### **RESTRICTIONS ON PRODUCT USE**

030619EBA

- The information contained herein is subject to change without notice.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor

devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical

stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety

in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such

TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- TOSHIBA products should not be embedded to the downstream products which are prohibited to be produced and sold, under any law and regulations.