# (QU\)U) ABIHZOT

## 1. GENERAL

The T6668 is a single chip CMOS LSI for voice recording and reproducing using the ADM (Adaptive Delta Modulation) system. When a dynamic RAM is used as a voice data memory and an audio circuit including a microphone, speaker, amplifier, etc. is externally connected, a voice recording/reproducing system can be composed.

## 2. FEATURES

| A single chip LSI for voice recording / reproducing.                                                           |

|----------------------------------------------------------------------------------------------------------------|

| D - RAM (Dynamic RAM) used as a voice data memory with the capacity up to 4pcs. of 64Kbit or 4pcs. of 256Kbit. |

| Built - in counter to refresh D - RAMs.                                                                        |

| Easy connection with CPU. Control by 9 kinds of commands.                                                      |

| Capable of recording / reproducing of max. 16 phrases.                                                         |

| Selectable 4 kinds of bit rates (32k, 16k, 11k, 8kbps).                                                        |

| Recording tone of each phrase is variable (MAX. 128 sec. at 256KD - RAM×4, bit rate 8kbps).                    |

| Built in microphone amplifier for sound recording and band path filter for sound reproducing.                  |

| Built in 10 bit D - A converter, voltage follower output.                                                      |

| Built in oscillation circuit for ceramic resonator.                                                            |

| Single 5V power supply Low power consumption by CMOS structure.                                                |

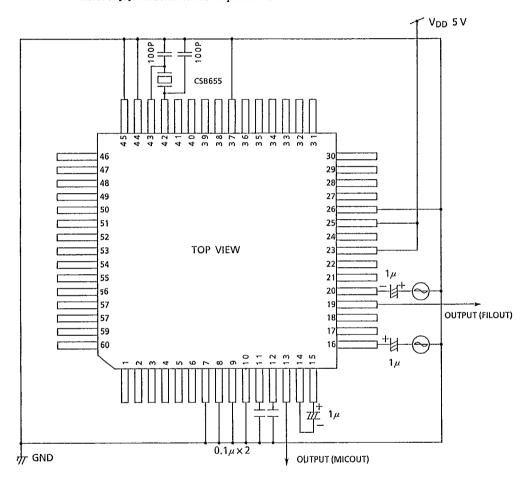

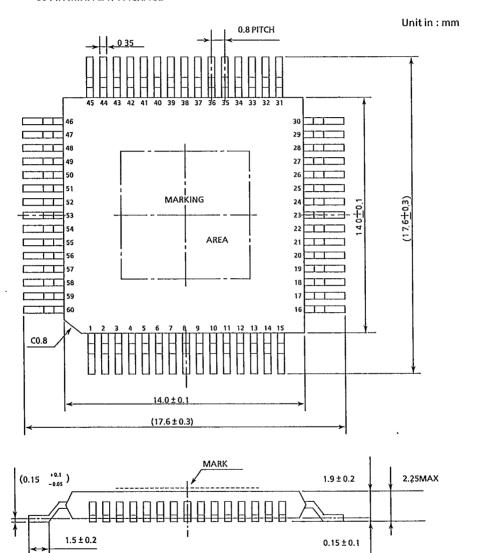

| 60 pin mini flat package.                                                                                      |

# (qu/Ju) ABIHZOT

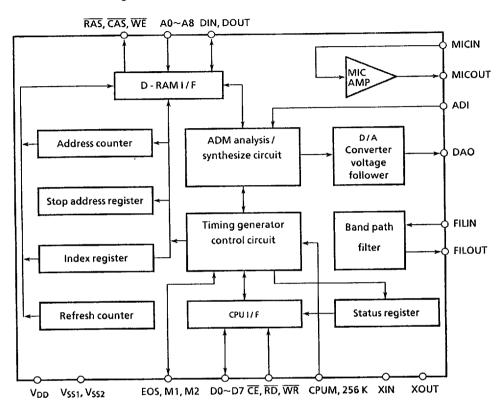

## 3. BLOCK DIAGRAM

#### 3.1 T6668 Block Diagram

#### 3.2 Block Diagram Description

#### (1) Address Counter

The 20 bit counter to show addresses of the external D - RAMs. Values can be set or read out by commands under CPU control. (Note 1)

#### (2) Stop Address Register

The 20 bit register to show addresses to stop recording / reproducing. Values can be set by commands, but values can not read out by commands under CPU control.

#### (3) Index Register

The register to show addresses of the index area on D - RAMs in the label index mode (refer to 5.5). User cannot directly operate this register.

#### (4) Refresh Counter

The 8 bit counter to refresh the external D - RAMs.

#### (5) Status Register

The 8 bit register to show the status of T6668. The status outputs by setting  $\overline{RD}$  to L level.

#### (6) CPU I/F

The interface circuit for the external microprocessor, etc. This circuit has also the chattering preventing circuit in the manual control. (Note 1)

This chattering preventing circuit acts on D4 and D5 terminals (start and stop inputs), and chattering time is approx. 16 ms.

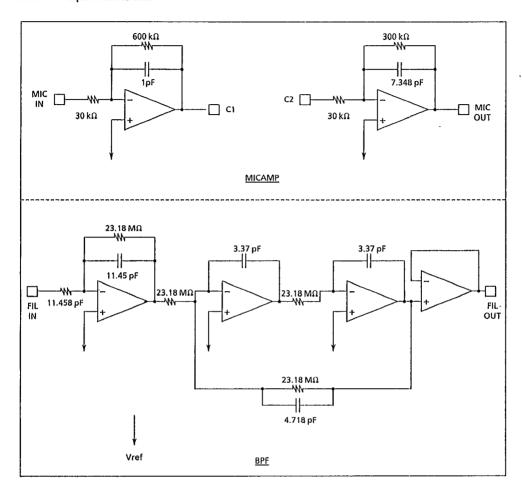

#### (7) Microphone Amplifier

The microphone amplifier for sound recording. Output of MICOUT terminal can be connected directly with the ADI pins.

#### (8) Band - pass Filter

The band pass filter for sound reproducing. The 1st stage high pass filter and the 2nd stage low pass filter are built in.

Note 1. There are two controls available for the T6668; CPU control using a microcomputer, etc. and the manual control using SW, etc.

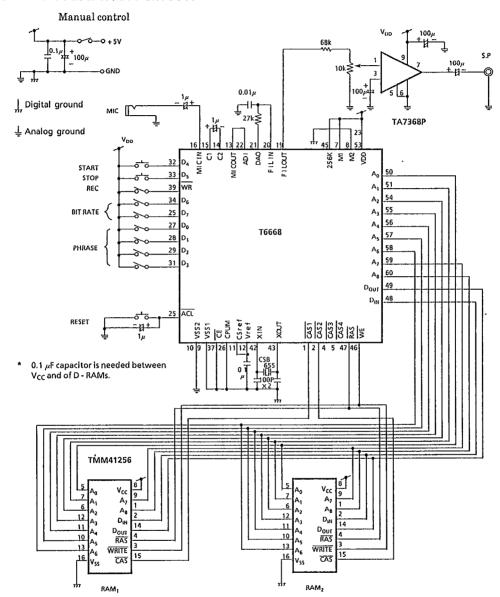

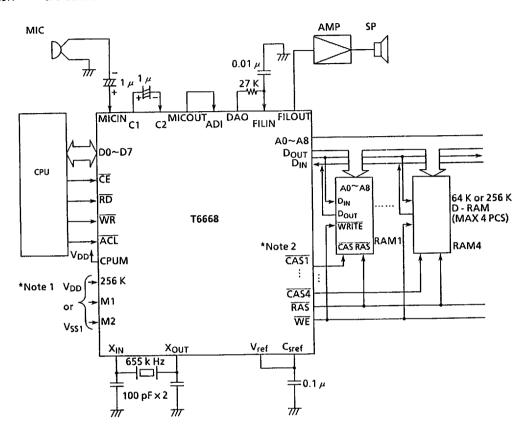

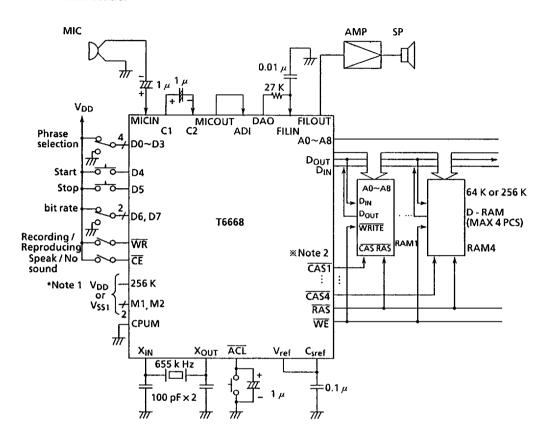

# 3.3 Example of Voice Recording / Reproducing LSI System Configuration

#### 3.3.1 CPU Control

\* Note 1, Note 2: For connections of 256K, M1 M2 and CAS1~CAS4, refer to 5.10 Connection to D - RAMs.

64E D

#### 3.3.2 Manual Control

Note1 , Note2 : For connections of 256 k, M1 M2 and  $\overline{CAS1} \sim \overline{CAS4}$ , refer to 5.10 Connection to D - RAMs .

64E D

#### 4. PIN DESCRIPTION

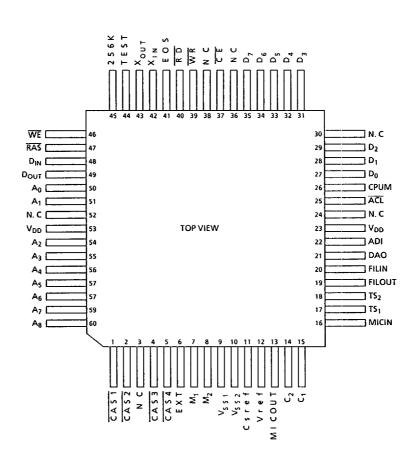

#### 4.1 Pin Assignments

**\*\*** NC: NON - CONNECTION

# 4.2 Pin Description

|          |         |                              | Stru        | cture  | · · · · · · · · · · · · · · · · · · · |                                                                                                                    |  |  |  |  |  |

|----------|---------|------------------------------|-------------|--------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin name | Pin no. | Man                          | ual control | СР     | U control                             | Functional explanation                                                                                             |  |  |  |  |  |

|          |         | I/O Pull - up Pull -<br>down |             | 1/0    | Pull - up Pull -<br>down              | Control Capitalion                                                                                                 |  |  |  |  |  |

| CAS1     | 1       | Out                          | _           | Out    | -                                     | Column address strobe output Used from CAST to that                                                                |  |  |  |  |  |

| CAS2     | 2       |                              |             |        |                                       | required corresponding to the number of D - RAMs.                                                                  |  |  |  |  |  |

| CAS3     | 4       | •                            |             |        |                                       |                                                                                                                    |  |  |  |  |  |

| CAS4     | 5       | _                            |             | ļ      |                                       | 191                                                                                                                |  |  |  |  |  |

| EXT      | 6       | Out                          | -           | Out    | <u> </u>                              | Output pins for test circuit.                                                                                      |  |  |  |  |  |

| M1       | 7       | In                           | None        | In     | None                                  | Input pins for programming of the number of D - RAMs.                                                              |  |  |  |  |  |

| M2       | 8       |                              |             |        |                                       | M2 M1                                                                                                              |  |  |  |  |  |

|          |         |                              |             |        |                                       | 1 pcs 0 0                                                                                                          |  |  |  |  |  |

|          |         |                              |             |        | <u> </u>                              | 2 pcs 0 1                                                                                                          |  |  |  |  |  |

|          |         |                              |             |        |                                       | 3 pcs 1 0 0 = L level                                                                                              |  |  |  |  |  |

|          |         |                              |             |        |                                       | 4 pcs 1 1 1 = H level                                                                                              |  |  |  |  |  |

| VSS1     | 9       | Power                        | _           | Power  | -                                     | Power supply pin to be connected to minus. V <sub>SS1</sub> is for                                                 |  |  |  |  |  |

| VSS2     | 10      | Supply                       |             | Supply |                                       | digital circuit and V <sub>SS2</sub> is for analog one.                                                            |  |  |  |  |  |

| Csref    | 11      | 1/0                          | ~           | 1/0    | -                                     | Pins for connecting the decoupling capacitor to the                                                                |  |  |  |  |  |

| Vref     | 12      |                              |             |        |                                       | reference voltage circuit of the built - in OP - AMP.                                                              |  |  |  |  |  |

| MICOUT   | 13      | Out                          | -           | Out    | _                                     | Output pin of built - in MIC. AMP. Output signal must be oscillating signal centering around 1/2 V <sub>DD</sub> . |  |  |  |  |  |

| C2       | 14      | in                           | None        | In     | None                                  | Pins for connecting the coupling capacitor of built - in MIC.                                                      |  |  |  |  |  |

| C1       | 15      | Out                          | -           | Out    | _                                     | AMP.                                                                                                               |  |  |  |  |  |

| MICIN    | 16      | in                           | None        | In     | None                                  | Input pin for built - in MIC. AMP.                                                                                 |  |  |  |  |  |

|          |         |                              |             |        |                                       | MIC must be connected to this pin through capacitor.                                                               |  |  |  |  |  |

| TS1      | 17      | In                           | Pull - down | in     | Pull - down                           | Pins for test circuit.                                                                                             |  |  |  |  |  |

| TS2      | 18      | Out                          |             | Out    |                                       | Must be open.                                                                                                      |  |  |  |  |  |

| FILOUT   | 19      | Out                          | -           | Out    | _                                     | Output and input pins of built - in band pass filter (for                                                          |  |  |  |  |  |

| FILIN    | 20      | ln                           | None        | In     | None                                  | reproducing)                                                                                                       |  |  |  |  |  |

| DAO      | 21      | Out                          | -           | Out    |                                       | Voice Output pin of voice synthesizing circuit. Voltage                                                            |  |  |  |  |  |

|          |         |                              |             |        |                                       | follower output. Monitor output for input voice is                                                                 |  |  |  |  |  |

|          |         |                              |             |        |                                       | obtained during recording. Output signal must be                                                                   |  |  |  |  |  |

|          |         |                              |             |        | L                                     | oscillating signal centering around 1 /2 V <sub>DD</sub>                                                           |  |  |  |  |  |

# 6201 ■ 97249 0024949 970 ■ C 344

# TOSHIBA (UC/UP)

|                                              |                                              |                             | Struc       | ture            |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|----------------------------------------------|----------------------------------------------|-----------------------------|-------------|-----------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin name                                     | Pin no.                                      | Man                         | ual control | СР              | U control                | Functional explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                                              |                                              | I/O Pull - up Pull-<br>down |             | 1/0             | Pull - up Pull -<br>down |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| ADI                                          | 22                                           | In                          | None        | In              | None                     | Voice input pin of voice analyzing circuit. Input signal must be oscillating signal centering around 1 / 2 $V_{DD}$ and MAX. 1.6 $V_{P-P}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| V <sub>DD</sub>                              | 23/53                                        | Power<br>Supply             | -           | Power<br>Supply | _                        | Power supply pins ··· + 5 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| ACL                                          | 25                                           | ln                          | Pull - up   | In              | Pull - up                | Input pin for reset signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| СРИМ                                         | 26                                           | In                          | None        | In              | None                     | Mode change pin. Must be fixed to low level under manual control mode, fixed to high level under CPU control mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| D0<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6<br>D7 | 27<br>28<br>29<br>31<br>32<br>33<br>34<br>35 | In                          | Pull-down   | 1/0             | None                     | In the CPU control mode, these are bidirectional data bus for commands or data between CPU and T6668. In the manual control mode, these are used in such a way as shown below.  (1) D0 ~ D3 inputs for phrase selection. MAX. 16 phrases can be selected by these 4-bit codes.  (2) D4 START input Recording or reproducing starts by setting this pin at high level.  (3) D5 STOP input Recording or reproducing starts by setting this pin at high level.  (4) D6, D7 Inputs for bit rate selection Usable bit rates are as follows  D7 D6  8 Kbps 0 0  11 Kbps 0 1  16 Kbps 1 0  32 Kbps 1 1  1 = H level |  |  |  |  |

| Œ                                            | 37                                           | In                          | Pull - down | In              | None                     | Chip enable input pin under the CPU control mode. This pin is used for inputting voice / no voice in the MANUAL control mode. When the pin is set at high level under reproducing, DAO output becomes no voice condition. The pin must be put low level during recording.                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|                  |         |                              | Struc       | ture                      |             |                                                                                                                                                                                                            |  |  |

|------------------|---------|------------------------------|-------------|---------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin name         | Pin no. | Man                          | ual control | СР                        | U control   | Functional explanation                                                                                                                                                                                     |  |  |

|                  |         | I/O Pull - up Pull -<br>down |             | I/O Pull-up Pull-<br>down |             | Torktonar explanation                                                                                                                                                                                      |  |  |

| WR               | 39      | In                           | Pull - down | In                        | None        | Write pulse input pin under the CPU control mode. Under<br>the manual control mode, this pin is for selection of<br>recording / reproducing. High level to this pin makes<br>recording mode, respectively. |  |  |

| RD               | 40      | ln                           | Puli - down | In                        | None        | Read pulse input pin under the CPU control mode.                                                                                                                                                           |  |  |

| EOS              | 41      | Out                          | -           | Out                       | -           | Output of "End of Speech."  It becomes low level after the start of recording or reproducing, and returns to high level after the stop of those.                                                           |  |  |

| X <sub>IN</sub>  | 42      | In                           | None        | In                        | None        | Input and output pins of oscillator circuit. 655 kHz ceramic                                                                                                                                               |  |  |

| X <sub>OUT</sub> | 43      | Out                          |             | Out                       | _           | oscillator and capacitors are connected.                                                                                                                                                                   |  |  |

| TEST             | 44      | In                           | Pull - down | In                        | Pull - down | Pin for test circuit. Must be open.                                                                                                                                                                        |  |  |

| 256K             | 45      | ln                           | None        | in                        | None        | Input pin for the selection of the type of D-RAMs.  It must be set at low level for 64Kbit D - RAM and high level for 256Kbit D - RAM.                                                                     |  |  |

| WE               | 46      | Out                          | -           | Out                       | -           | Write pulse output pin. Connect this to WRITE pins of D - RAMs.                                                                                                                                            |  |  |

| RAS              | 47      | Out                          | -           | Out                       | _           | Low address strobe output. Connect this to $\overline{\text{RAS}}$ input pins of D - RAMs.                                                                                                                 |  |  |

| D <sub>IN</sub>  | 48      | In                           | Pull - up   | <b>l</b> n                | Pull - up   | Data input pin. Connect this to data input pins of D - RAMs.                                                                                                                                               |  |  |

| D <sub>OUT</sub> | 49      | Out                          | _           | Out                       | _           | Data output pin. Connect this to data input pins of D - RAMs.                                                                                                                                              |  |  |

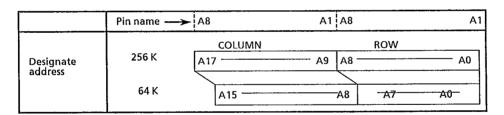

| A0               | 50      | Out                          | _           | Out                       |             | Address output.                                                                                                                                                                                            |  |  |

| A1               | 51      |                              |             |                           |             | Connect this to address input pins of D - RAMs. Only A8 is                                                                                                                                                 |  |  |

| A2               | 54      |                              | }           |                           |             | not needed when 64Kbit D - RAMs are used.                                                                                                                                                                  |  |  |

| A3               | 55      |                              |             |                           |             |                                                                                                                                                                                                            |  |  |

| A4               | 56      |                              |             |                           |             |                                                                                                                                                                                                            |  |  |

| A5               | 57      | l                            |             |                           |             |                                                                                                                                                                                                            |  |  |

| A6               | 58      |                              |             |                           |             |                                                                                                                                                                                                            |  |  |

| A7               | 59      |                              |             |                           |             |                                                                                                                                                                                                            |  |  |

| A8               | 60      |                              |             |                           |             |                                                                                                                                                                                                            |  |  |

# 5. SPECIFICATION

# 5.1 Recording / Reproducing

| System             | ADM System                                                                   |                                                        |

|--------------------|------------------------------------------------------------------------------|--------------------------------------------------------|

| D / A Converter    | 10bit voltage type                                                           |                                                        |

| Bit rate           | 32K/16K/11K/8Kbps                                                            |                                                        |

| Max. phrase number | In manual control Label Index mode in CPU control Direct mode in CPU control | ··· 16 phrases<br>··· 16 phrases<br>··· No restriction |

| Address counter    | Built in counter to refresh D - RAMs                                         | 3                                                      |

### 5.2 Others

| Input Microphone amplifier | Two - stage, gain TYP = 46 dB                            |  |  |  |  |

|----------------------------|----------------------------------------------------------|--|--|--|--|

| Output filter              | Built in 2nd stage low pass + 1st stage high pass filter |  |  |  |  |

| RAM for storing voice data | 64K or 256K D - RAM, maximum 4 pcs each                  |  |  |  |  |

| Oscillation frequency      | 655kHz (TYP. )                                           |  |  |  |  |

#### 5.3 Operational Description

When composing a voice recording / reproducing system by the T6668, there are CPU control using a microcomputer, etc. and the manual control using external SW, etc.

#### 5.4 Manual Control

#### 5.4.1 Selection of Phrase

Using 4 input pins of D0~D3, the sound recording / reproducing of maximum 16 phrases can be performed. Before starting the sound recording / reproducing, phrase No. shall be specified in 4-bit code.

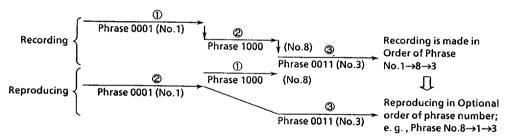

Phrase numbers are as follows, and can be selected at random. (Fig. 5.1)

Table 5.1 Phrase no.

| Pin name<br>Phrase No. | MSB D3 | D2 | D1       | LSB D0 |

|------------------------|--------|----|----------|--------|

| No.0                   | 0      | 0  | 0        | 0      |

| No.1                   | 0      | 0  | 0        | 1      |

| No.15                  | 1      | 1  | ↓<br>  1 | ↓<br>1 |

0 = L level 1 = H level

Fig.5.1 Example of phrase selection

#### 5.4.2 Selection of Bit Rate

The T6668 can use 4 kinds of bit rates as shown in Table 5.2; 8k, 11k, 16k and 32kbps, which are selected by D6 and D7. Since a bit rate is independently specified for sound recording/reproducing, it is possible to change reproduced voice to slow/fast speaking. However, the phrases are reproduced at low tone when slowly spoken and at high tone when rapidly spoken. Bit rate should be specified prior to recording/reproducing.

64E D

Table 5.2 Bit rate selection

|          | D <sub>7</sub> | D6 |   |

|----------|----------------|----|---|

| 8 K bps  | 0              | 0  |   |

| 11 K bps | 0              | 1  |   |

| 16 K bps | 1              | 0  | 0 |

| 32 K bps | 1              | 1  | 1 |

0 = L level 1 = H level

(Caution) Selection of phrase and bit rate is decided when D4 pin is set at "H" level (start input).

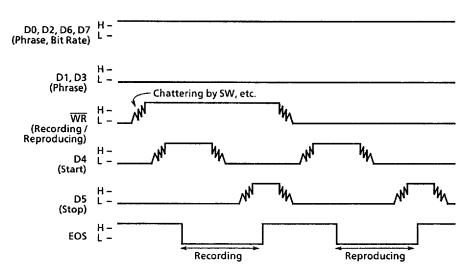

Switching of Recording / Reproducing Mode

Switching of recording / reproducing of the T6668 is made by the  $\overline{WR}$  pin.

"H" level is ready to accept the recording and "L" level is ready to accept the reproducing.

#### 5.4.3 Recording Mode

The T6668 has the 20 bit address counter, and voice data is written into RAM from the address designated by that value. When making the sound recording newly, first, reset the address counter by the  $\overline{ACL}$  input. Setting of the  $\overline{WR}$  pin to "H" level results in the recording waiting state.

When the D4 pin is set to "H" level (start input), the recording starts and the address counter is added successively. When the D5 pin is set at "H" level (stop input) or when the value on the address counter reaches the maximum address (see 5.7) of RAM, the sound recording is stopped.

Since this maximum address is changed when the 256K, M1 and M2 pins are set, the full capacity of RAM can be effectively used. However, when the RAM's capacity is fully used, subsequent recording is not allowed. Therefore, to make the recording newly, reset the address counter again of the  $\overline{ACL}$  input.

In T6668, when the sound recording starts, a value of the address counter at time of the start (start address) and when the sound recording ends, that at time of the stop (stop address) are automatically written into a part of RAM, respectively. Further, it is possible to monitor synthesized voices from input voices through analysis and synthesis during the recording.

#### 5.4.4 Reproducing Mode

When the  $\overline{WR}$  pin is set at "L" level, the T6668 is placed in the sound reproducing waiting state. When the D4 pin is set at "H" level at this times the T6668 starts the sound reproducing after loading the start address and stop address, which have been written at time of the sound recording, into the address counter and stop address register, respectively. The sound reproducing is terminated when the D5 pin is set at "H" level or when the value of the address counter agrees with the stop address.

Fig.5.2 Recording / reproducing at phrase No.5, bit rate 32 kbps

\* Refer to 5.6 Recording/Reproducing via Index Area for details of recording/reproducing, addition of phrases and change of phrase contents when many phrases are involved, and refer to 5.9 Operation of Address Counter for the address counter operation.

#### 5.4.5 Start, Stop Input and Internal Status

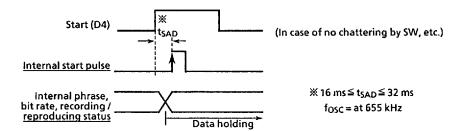

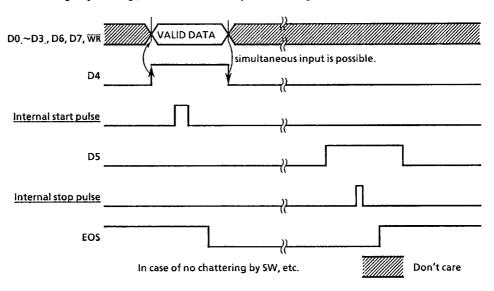

Phrase No., bit rate and recording / reproducing status are all held at the leading edge of internal start pulse. Further, external start input and internal start pulses are at the timings shown in Fig. 5.3.

Fig.5.3 Start input and internal status

From Fig. 5.3, it is possible to input externally given D0~D3 (Phrase), D6~D7 (bit rate), WR (recording/reproducing), D4 (start) and D5 (stop) as shown Fig. 5.4.

Fig.5.4 How to give start input and stop input

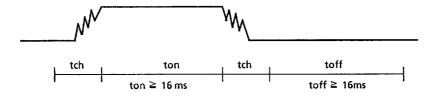

#### 5.4.6 Chattering Preventing Circuit

In the manual control mode, the chattering preventing circuit is actuated to prevent malfunction by chattering of the switches connected to the D4 pin (start input) and D5 pin (stop input).

Fig.5.5 Chattering preventing circuit

In case of operating in manual mode, start and stop inputs should be set to min. 16ms.

64E D

#### 5.5 CPU Control

In the CPU control, the operation of T6668 is controlled by 9 kinds of commands. In addition, the T6668 has a 8 bit status register and the external CPU is able to read the status of T6668 at any time.

In addition, the T6668 has the address overflow detector (Note 1) and the address comparator flip-flop (Note 2), which control the sound recording and reproducing operations.

(Note 1) Address overflow detector ...... (Refer to 5.5.5)

(Note 2) Address comparator flip-flop ....... (Refer to 5.5.6)

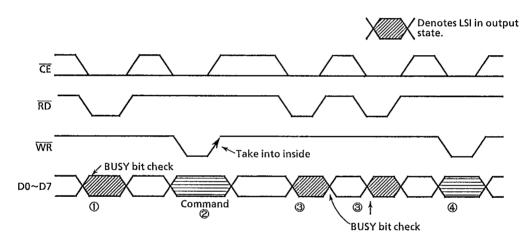

#### 5.5.1 How to Write CPU Command

As shown Fig. 5.6, using D Pulse, read data from LSI and check BUSY bit. If not in D BUSY state, after setting up command data in D0~D7, write a command using  $\overrightarrow{WR}$  pulse. In case of such 3 byte commands as ADLD1, ADLD2, etc., after rechecking BUSY bit by D Pulse, write the D 2nd and 3rd byte bits. After the 1st and 2nd byte bits of a 3 byte command, other command bits cannot be written.

Fig.5.6 How to write command

2

6668-16

64E

TOSHIBA (UC/UP)

5.5.2 Commands of T6668

| (1) NOP             | MSB   |     |   |   |   | LSE | 3 |

|---------------------|-------|-----|---|---|---|-----|---|

| (1) NOF<br>(1 hvte) | 0,0,0 | 0 0 | х | Х | X | X   | l |

0 = L level 1 = H level X = Don't Care

No operation. In the sound recording mode, this command is set in the sound reproducing mode. In addition, this command is used to reset ERR and OVR (refer to 5.2.3) in the status register.

This command is used to start the sound recording or reproducing in the direct mode from the RAM address shown by the contents of the address counter.

This command is used to stop the sound recording or reproducing. If this command is given during the sound recording by the LABEL command, the contents of the address counter at time of stop are written into the index area of RAM.

This command is used to set address in the address counter together with 2 bytes following that address. When the 64Kbit RAM is specified, A19 and A18 are made to "00" by force.

This command is used to set address in the stop address register together with 2 bytes following that address. When the 64Kbit RAM is specified, A19 and A18 are made to "00" by force.

This command specifies a bit rate and silent state. When the silent state is specified, the DAO pin is forced to become 1/2. VDD level. The silent state should not be specified at time of sound recording.

64E D>

(7) LABEL (1 byte) MSB LSB (For LB3,LB2, LB1, and LB0, refer to the command list)

This command specifies phase No.  $(0\sim15)$  and starts the sound recording / reproducing. When this command is given in the sound recording mode, the contents of the address counter is written into the index area of RAM and then, the sound recording is started. In case of the sound reproducing mode, start address, stop address, and bit rate are read from the index area and then, the sound reproducing is started.

(8) ADRD MSB LS (1 byte) 0 1 1 1 X X X X

This command is used to read out the contents of the address counter. By successive 3 times of read access, high order 4bits, middle order 8 bits, and low order 8bits are output to  $D0\sim D7$  in that order. If next command is given without performing 3 times of read access, the ADRD code interrupted and the next command process is started, enabling read out of the status register.

(9) REC MSB LS

(1 byte) 1 0 0 0 X X X X

This command is used to set the T6668 to the sound recording mode when it is in the sound reproducing mode. The T6668 is returned to the sound reproducing mode by NOP command.

(Caution) During the sound recording / reproducing (that is, when the EOS pin or EOS bit of the status register is 0), do not give any command other than STOP.

#

# TOSHIBA (UC/UP)

Table 5.3 Command list

| Command           |         | 1st        | byte          | )    |        |             | 2ne   | d byte      | •        |       |          |       | 3nc   | l byte       |       |

|-------------------|---------|------------|---------------|------|--------|-------------|-------|-------------|----------|-------|----------|-------|-------|--------------|-------|

| Input Pin         | D7 -    |            |               |      | D0     | D7 —        |       |             |          | D0    | D7       |       |       | -            | D0    |

| NOP               | 0000    | Χ          | Х             | Х    | Х      |             |       | _           |          |       |          |       |       | _            |       |

| START             | 0001    | Χ          | Х             | Х    | Х      |             |       | _           |          |       |          |       |       | _            |       |

| STOP              | 0010    | Х          | Х             | Х    | Х      |             |       | _           |          |       |          |       |       | _            |       |

| ADLD <sub>1</sub> | 0 0 1 1 | A19        | A18           | A17  | A16    | A15 A14     | A13 A | 12 A11      | A10 A    | \9 A8 |          | 47 A6 | A5 A4 | 4 A3 A2      | A1 A0 |

| ADLD <sub>2</sub> | 0100    | A19        | A18           | A17  | A16    | A15 A14     | A13 A | 12 A 1 1    | A10 A    | \9 A8 | ,        | 47 A6 | A5 A4 | 4 A3 A2      | A1 A0 |

|                   | 0101    | х <u>s</u> |               |      | BR0    |             |       | -           |          |       |          |       |       | _            |       |

|                   |         |            |               |      |        | SL          | 7     |             |          | Bit R | ate      | В     | R1    | BRO          |       |

|                   |         |            |               |      | ound   |             |       | L           | <b>→</b> | 8 1   | <        |       | 0     | 0            |       |

|                   |         |            | $\rightarrow$ |      | ilent  | 1           |       |             |          | 11    | K        |       | 0     | 1            |       |

|                   |         |            | L             |      | iiciit | <del></del> | 16 K  |             |          | K     | 1 0      |       |       |              |       |

|                   |         |            |               |      |        |             |       |             | L        | 32    | K        |       | 1     | 1            |       |

| LABEL             | 0110    | LB3        | LB2           | LB 1 | LB0    |             |       | <del></del> |          |       | <u> </u> |       |       | =            |       |

|                   |         | MSB        | 3             |      |        | 1           | SB    |             |          |       |          |       |       |              |       |

|                   |         |            |               |      |        | LBO = Phr   |       | lo. (0-     | ~15)     |       |          |       |       |              |       |

| ADRD              | 0111    | X          | X             | X    | Х      |             |       | <del></del> |          |       | 1        |       |       | <del>-</del> |       |

|                   |         |            |               |      |        | Read        | D7    |             |          | Outpu | ut Dat   | ia    |       | D0           | ]     |

|                   |         |            |               |      |        | 1st         | 0     | 0           | 0        | 0     | A19      | A18   | A17   | A16          | 1     |

|                   |         |            |               |      | 1      | 2nd         | A15   | A14         | A13      | A12   | A11      | A10   | Α9    | A8           | ]     |

|                   |         |            |               |      |        | 3rd         | Α7    | Α6          | Α5       | Α4    | А3       | A2    | Α1    | Α0           | ]     |

|                   | 1000    | X          | X             | Х    | X      |             |       | _           |          |       | T        |       |       |              |       |

64E D :

#### 5.5.3 Status Register

The status register consists of 8 bits. When the  $\overline{\rm RD}$  pin is set to L level (read access) under CPU control, data of the status register is output to D0~D7 and the internal operating status of the T6668 can be checked. Each bit of the status register is explained in the following. (Table 5.4)

#### (1) BUSY

When this bit is 1, it indicates that the T6668 is in reset state or processing a command internally. Do not give any command from CPU. If the command is given, the internal status may possible becomes uncertainty.

#### (2) EOS

This bit becomes 1 during the not sound recording / reproducing and 0 when the sound recording / reproducing is started. This value is the same as the value that is output at the EOS pin.

#### (3) ERR

Command error. This bit becomes 1 when any undefined is given to the T6668. This bit is reset by NOP command.

#### (4) OVR

Address over. It is indicated that the sound recording ends as the address counter exceeded max. address (refer to 5.3) of RAM during the sound recording by LEBEL command. This status bit is reset by NOP command.

#### (5) M2, M1

values of these bits are the same as those set at pin M2 and M1.

Table 5.4 Status register

| Terminal Name   | D7   | D6  | D5  | D4  | D3             | D2             | D1 | D0 |

|-----------------|------|-----|-----|-----|----------------|----------------|----|----|

| Status Register | BUSY | EOS | ERR | OVR | M <sub>2</sub> | M <sub>1</sub> | 0  | 0  |

0 = L Level 1 = H Level

#### 5.5.4 Busy Bit

Conditions for setting BUSY bit of the status register to 1 are broadly classified into the following 3 conditions. That is, BUSY bit is set to 1 during the reset period of T6668, during the process of command given externally, and during the process after stop of the sound recording due to address overflow. (Table 5.5)

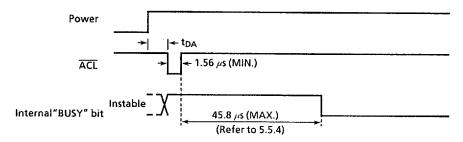

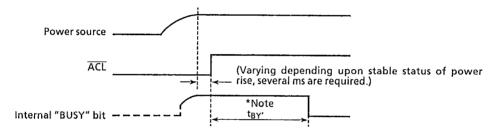

#### (1) Reset Process

When the  $\overline{ACL}$  pin becomes L level, BUSY bit becomes 1. When the  $\overline{ACL}$  pin returns to H level again, the internal state of T6668 is initialized and after all are completed, BUSY bit becomes 0.

64E D~

#### (2) Command Process

When it is detected that both of the  $\overline{CE}$  and  $\overline{WR}$  pins have become L level in the CPU control, BUSY bit become 1. When the process of all command is completed, BUSY bit returns to 0 again. The command process is actually started after return of the least either one of the  $\overline{CE}$  or  $\overline{WR}$  pin to H level has been detected. (The table shown below also indicates times for BUSY bit to become 0 after the  $\overline{CE}$  or  $\overline{WR}$  pin returned to "H" level.)

#### (3) Address overflow process

When the address counter is overflow during the sound recording in the label index mode, the T6668 automatically stops the sound recording. During this period, BUSY bit also becomes 1.

Table 5.5 BUSY generating length

|                    | BUSY Generating Conditions |                                  |        |  |  |  |

|--------------------|----------------------------|----------------------------------|--------|--|--|--|

| Reset process (aft | er <del>ACL</del> ↑)       |                                  | 3 t ø  |  |  |  |

| NOP, START, CND    | T, REC Con                 | nmand                            | 3 t ø  |  |  |  |

| 40104 401026       |                            | 1st byte                         | 4 t ø  |  |  |  |

| ADLD1, ADLD2 Co    | mmand                      | 2nd, 3rd byte                    | 3 t ø  |  |  |  |

| ADRD Command       |                            |                                  | 4 t ø  |  |  |  |

| 4D104 4D1D3 G      |                            | Sound recording mode             | 35 t ø |  |  |  |

| ADLD1, ADLD2 Co    | mmana                      | Sound reproducing mode           | 67 t ø |  |  |  |

| crop c             | During sou                 | ind recording in label indexmode | 40 t ø |  |  |  |

| STOP Command       | 3 t ø                      |                                  |        |  |  |  |

| Address Overflow   | Address Overflow Process   |                                  |        |  |  |  |

ts 15.3 μs

@ fCLK = 655 kHz

#### 5.5.5 Address Overflow Detector

When the address counter exceeds maximum address that is determined by the pin 256K, M2 and M1, it is detected by this detector. When the LABEL command is given in the sound recording mode, it becomes valid and is kept until the NOP command is given. When the address overflow is detected, the sound recording is stopped, a value of the maximum address is written into the index area as the stop address and then, the address counter is preset at address 00400H. In addition, the OVR bit of status register is set.

During this period of processing, BUSY bit of the status register also become 1.

64E D ~

#### 5.5.6 Address Comparator Flip - Flop

The sound recording / reproducing is stopped if the contents of the address counter agrees with those of the stop address register when this flip - flop has been set. When it has been reset, the sound recording / reproducing is not stopped until the STOP command is given. (Exception: Address overflow in the preceding item)

This flip - flop is set when the ADLD2 command is given or when the LABEL command is given in the sound reproducing mode, and is reset when the ADLD1 command is given or when the LABEL command is given in the sound recording mode.

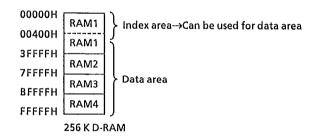

#### 5.5.7 Modes in CPU Control

There are two ways about both recording and reproducing of T6668 when it is under CPU control. That is, one is the Direct mode and another is Label / Index mode. The former is the way to write start address, stop address and bit rate of each phrase by command, and the latter is to designate phrase number so that T6668 write the above mentioned parameters into the certain part of RAM.

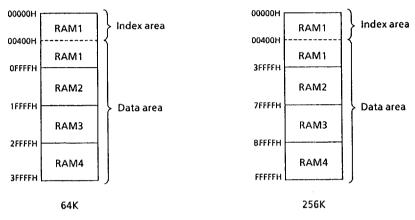

So, at the Label / Index mode, the certain part of RAM (s) is used for Index area. On the contrary at the direct mode, such a part can used for data area (Fig. 5-7).

Fig.5.7 Memory map at direct mode

\* Refer to 5.6 RECORDING VIA INDEX AREA for details of recording / reproducing, addition of phrases and change of phrase contents many phrases are involved, and 5.9 OPERATION OF ADDRESS COUNTER for address counter operation.

64E D

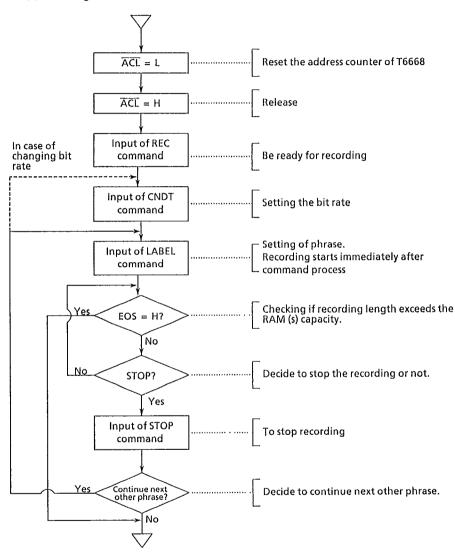

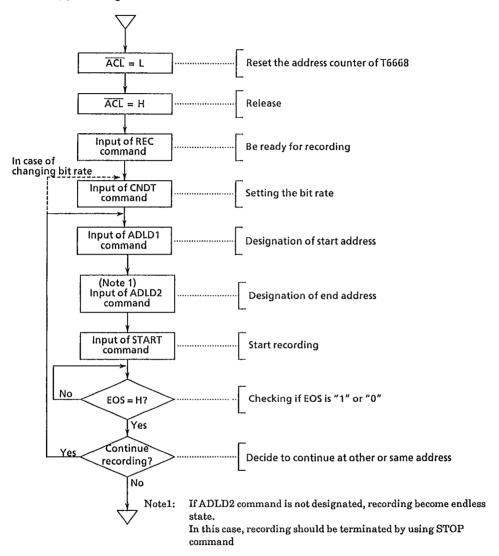

#### 5.5.8 The Flowchart of Recording / Reproducing in Label Index Mode

(1) Recording

Fig.5.8 Recording in label / index mode

#### (2) Reproducing

Note: In CPU control mode, bit rate is that settled previously at the recording and fast / slow speaking cannot be specified as in manual control mode.

Fig.5.9 Reproducing in label / index mode

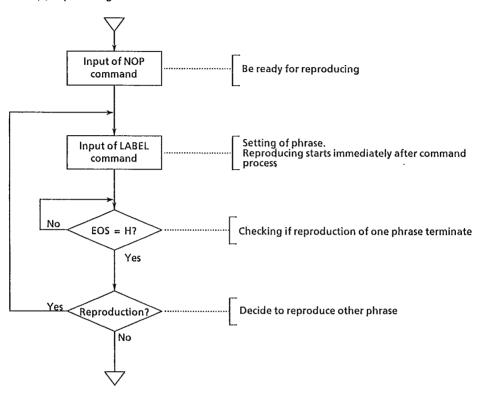

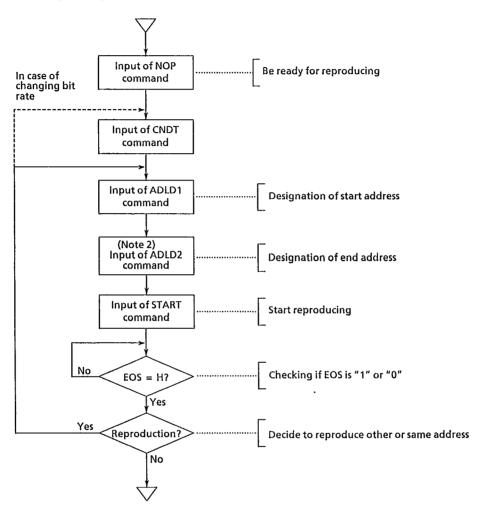

#### 5.5.9 The Flowchart of Recording / Reproducing AT "DIRECT MODE"

#### (1) Recording

Fig.5.10 Recording in direct mode

(2) Reproducing

Note 2: When ADLD2 is used as the maximum address of RAM during recording and omitted during reproducing, endless speaking becomes possible. STOP command is used to terminate it.

Fig.5.11 Reproducing in direct mode

**64E**

#### 5.6 Recording / Reproducing Via Index Area

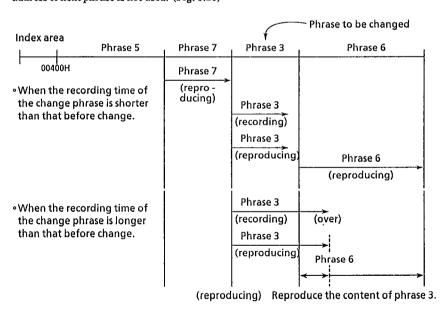

The recording / reproducing methods by the manual control of the T6668 and the label index mode in CPU control are described here. In the manual control (LABEL command under CPU control), the recording / reproducing is indirectly performed as the T6668 writes start addresses, stop address and bit rate of each phrase into a part of RAM and selects phrase number. The memory maps of RAMs in the label index mode are as follows.

Fig.5.12 Memory map in level index mode

Maximum number of addresses that can be used varies depending upon type and number of externally connected D - RAM. In may case, addresses 00000H~003FFII are used as the index area, and the succeeding address 00400H and up become the voice data area.

Start address, stop address, and bit rate are recorded in the index area by the T6668 at time of sound recording, and data read out from this area are loaded on the address counter, etc. at time of sound reproducing.

#### 5.6.1 Recording of Phrase

In performing the recording newly, first reset the T6668 by the  $\overline{ACL}$  input. The internal address counter is preset to 004000H at this time.

Then, when the start signal is input by specifying a bit rate and phrase No., the recording starts. After the contents of the address counter at this time; that is, start address is written into the index area of RAM, actual recording is started. During the recording, the contents of the address counter are added successively.

When the stop signal is input during the recording, the recording ends. The contents of the address counter at the time; that is, the end address and bit rate are written into the index area of RAM. Thereafter, the contents of the address counter are added with one (+1) and preparation for next recording is performed.

To perform the recording with other phrase successively, Phrase No. is newly designated and the start signal is input (Fig. 5.19).

Fig.5.13 In case of recording phrase 2

#### 5.6.2 Reproducing of Phrase

If any already recorded phrase No. is selected and start input is give, voice corresponding to that phrase No. is reproduced. Phrase No. at this time can be designated irrespective of sequence of the recording. Further, it is also possible to stop speaking by giving the stop input in the middle of the reproducing. Thereafter, when the start input is given again using the same phrase No., the reproducing is performed from the beginning of that phrase. If the reproducing is started by designating phrase No. that was not used for the recording, what sound is reproduced is uncertain. However, it is possible to stop the sound reproducing by giving stop input. The reproducing is started after the start address, end address and bit rate are set in the T6668 from the index area. When the start input signal is given by specifying next phrase No. during the reproducing in the manual control mode, this next phrase is spoken successively after end of the preceding phrase generation, because T6668 has a buffer for phrase No. When the start input signal is given several times during speaking of one phrase, the last phrase specification remains in the buffer. As the bit rate has no buffer, however, the bit rate of a phrase during the reproducing becomes the bit rate of next phrase in change the phrases with different bit rates.

#### 5.6.3 Addition of Phrase

First, reproduce the last phrase at the recording to the last in the reproducing mode. At this time, the address counter stops while indicating address next to the end address of the last phrase. Change the reproducing mode to the recording mode. Do not reset the T6668 at this time. When the recording is made by designating any unrecorded phrase No., phrase can be added.

2

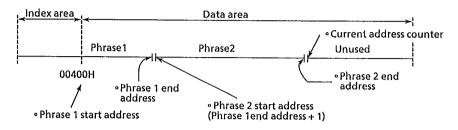

#### 5.6.4 Change of Phrase Contents

To change the contents of phrases that have been once recorded, reproduce a phrase preceding the phrase that is to be changed to have the address counter indicate the start address of the phrase to be changed. (For example, when Phrase No. has been recorded in order of 5-7-3-6 and the contents of phrase No. 3 are to be changed, reproduce phrase No. 7 to the last.) Do not reset the T6668 at this stage. When the recording is made by designating phrase No. that is to be changed successively, the contents of that phrase are changed to the new contents. At this time, if the recording time of the changed phrase is longer than that of the phrase before changed, the first part of next phrase may be changed. When the changed phrase is reproduced under this state, the new contents are spoken properly but when it is tried to reproduce next phrase, the reproducing is started at the middle of the changed phrase and when the reproducing ends, sound is produced successively from the middle of next phrase. This is phenomenon that is taken place as the start address of next phrase written in the index area remains unchanged from the previous address. On the contrary, when the recording time of the changed phrase is shorter than that before change, the latter part data of the phrase before change is left. When this part is reproduced, the last speaking of the changed phrase stops. Needless to say, next phase is also properly reproduced.

Under this state, a RAM for the part between the end address of the changed phrase and the start address of next phrase is not used. (Fig. 5.20)

Fig.5.14 Change of phrase contents

(40\JD) ABIHZOT

64E D <

#### 5.6.5 Address and Data in Label Index Mode

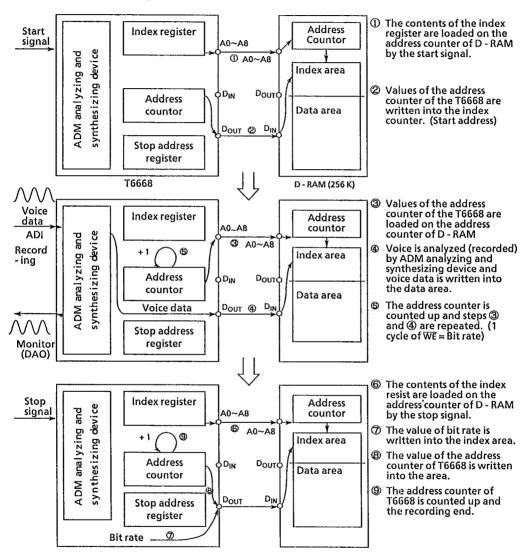

The operations of the T6668 and  ${\bf D}$  - RAM in the label index mode are described in the following.

(1) At time recording

Fig.5.15 Access to memory in recording

#### (2) At time of reproducing

Fig. 5.16 Access to memory in reproducing

64E D 3

#### 5.7 Maximum Address of RAM

When the contents of the address counter reach the maximum address during the recording in the label index mode at the manual and CPU controls, the T6668 stops the recording automatically. In this case, the maximum address is stored as the the end address of a phrase at that time. Further, the address counter is preset at 00400H address and stops there.

Therefore, in the recording / reproducing of the one phrase only, the stop switch (D5) becomes unnecessary. In other words, when a certain time has passed after starting the recording (when the recording is made to the last of RAM), the recording ends and also, the reproducing stops after the contents of RAM were spoken to the last.

This maximum address changes according to the settings of the pin 256 K, M1 and M2 of the T6668. These pins shall be set according to kind and quantity of externally connected RAM. (Table 5.6)

Table 5.6 External RAMs and maximum addresses

| External RAM        | 256 K  | M2 | M1 | Maximum Address |                   |

|---------------------|--------|----|----|-----------------|-------------------|

| 64K D - RAM 1 pc.   | * Note | 0  | 0  | FFFFH \         |                   |

| 64K D - RAM 2 pcs.  | 0      | 0  | 1  | 1FFFFH          |                   |

| 64K D - RAM 3 pcs.  | 0      | 1  | 0  | 2FFFFH          |                   |

| 64K D - RAM 4 pcs.  | 0      | 1  | 1  | 3FFFFH          | Address  HEX CODE |

| 256K D - RAM 1 pc.  | 1      | 0  | 0  | 3FFFFH          |                   |

| 256K D - RAM 2 pcs. | 1      | 0  | 1  | 7FFFFH          |                   |

| 256K D - RAM 3 pcs. | 1      | 1  | 0  | BFFFFH          |                   |

| 256K D - RAM 4 pcs. | 1      | 1  | 1  | FFFFFH /        |                   |

Note 0 = L level 1 = H level

#### 5.8 Reset Operation

#### 5.8.1 The Status during Reset Operation

Low level to  $\overline{ACL}$  pin causes the reset to T6668 in both of the manual control and CPU control, and all operations such as recording/reproducing stop. However, the refresh counter continues to operate and therefore, the data stored in D - RAM(s) remain unchanged. Further, BUSY bit of status register becomes 1 during this period and therefore, recording/reproducing start inputs under the manual control mode and command input under CPU control mode should not be given.

#### 5.8.2 The Status after Reset Operation

When  $\overline{ACL}$  pin becomes from L to H level, the internal state of T6668 is initialized as shown below.

- (1) In CPU control mode, it becomes reproducing mode.

- (2) Address counter and stop address register are preset to 00400H.

- (3) Address overflow detector and address comparator flip flop are reset.

- (4) In CPU control mode, bit rate becomes 8Kbps, and "Silence Status" is released.

- (5) ERR and OVR bits in status register are reset.

After terminating the above completely, BUSY bit in status register is set to "0".

#### 5.8.3 Reset Processing after Power ON

After Power ON, the following items become instable;

- (1) Change over of recording / reproducing modes

- (2) Address counter

- (3) ADM arithmetic system

- (4) Other processing registers such as start and stop processing

Therefore, to initialize this instable condition and assure proper operations, apply ACL signal. (System reset)

64E D

ACL signal to be given after power ON and its pulse width are shown in Fig.5.13.

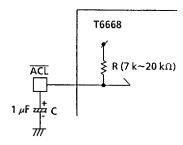

Fig.5.17 ACL pulse width

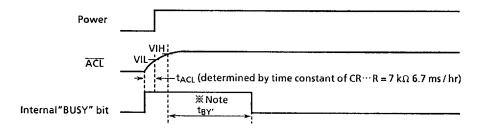

However, if width of tDA after power ON is long, the instable status lasts and causes malfunction (start of recording / reproducing, etc.) in Fig.5.18. So, in [10] Application Circuit in the manual control mode, an automatic clear circuit is configured to input integral waveform by time constant of a pull-up resistor (7 k~20 k $\Omega$ ) housed in the  $\overline{ACL}$  pin by attaching a 1 $\mu$ F capacitor to the  $\overline{ACL}$  pin, making the system initialization possible immediately after power ON as illustrated in Fig.5.18.

Fig.5.18 Circuit for power on reset

Fig.5.19 ACL input at power on reset

T6668-34

64F

9097249 0024975 T62 **=** T0S:

# TOZHIBA (UC/UP)

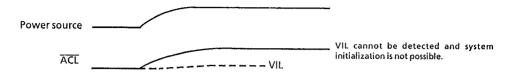

However, the power on reset is effective only for a step power rise and when power rise is gentle, no system initialization is performed. (Fig. 5.20)

Fig.5.20 In case power rise is gentle

Further, if the  $\overline{ACL}$  pin can be controlled under CPU control mode regardless of power ON / OFF at T6668 side, the system initialization can be applied as shown in Fig.5.21.

Fig.5.21 System initialization by CPU control

\* Note tBY is a time from power ON till oscillation is stabilized and varies depending on an external oscillator. (Several ms in case if CSB655)

### 5.9 Operation of Address Counter

The operation of address counter of the T6668 and the memory map of the index area are described here.

Fig.5.22 Address output

# (qu/)U) ABIHZOT

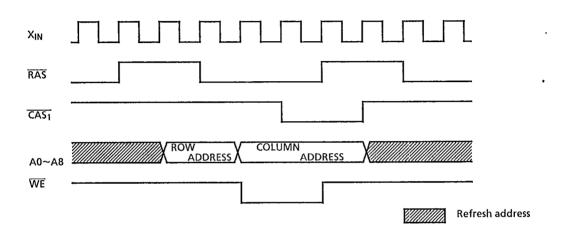

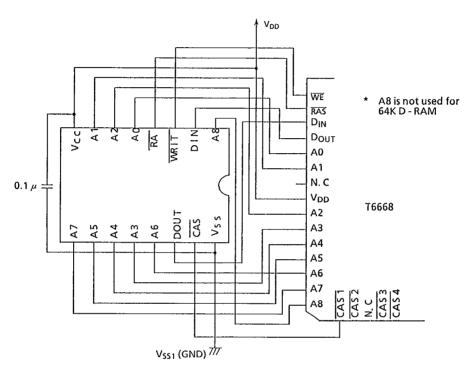

# .5.10 Connection to D - RAMS

The T6668 needs outer D - RAMs (dynamic RAMs) for the storage of recorded voice data.

Maximum four 64K D - RAMs or four 256K D - RAMs are directly connected to the T6668. But is impossible to connect 64K D - RAMs and 256K D - RAMs at the same time.

Fig.5.23 Connection with D - RAM

Fig. 5.23 shows the connection with D - RAM. In case of two or more D - RAMs,  $\overline{\text{CAS1}}$  pin T6668 must be connected to the  $\overline{\text{CAS}}$  pin of 1st D - RAM, the  $\overline{\text{CAS2}}$  pin of T6668 to the  $\overline{\text{CAS}}$  pin of 2nd D - RAM and so on. That is,  $\overline{\text{CAS1}} \sim \overline{\text{CAS4}}$  pins must be connected to the  $\overline{\text{CAS}}$  pin of D - RAMs, respectively. Other pins about D - RAM of T6668 may be connected in parallel to every D - RAMs. (See 3.3 "Example of Voice Recording / Reproducing LST System Configuration".) Some pins of T6668 must be settled high or low according to the type and number of outer D - RAMs. Table 5.7 shows the setting conditions. These conditions shown in Table must not be changed during recording or reproducing operation.

Table 5.7 Pin setting according to type and number of D - RAMs

| Pin name<br>Type<br>of D - RAM | 256K |

|--------------------------------|------|

| 256K                           | 1    |

| 64K                            | 0    |

| Pin name<br>Number<br>of D - RAM | M2 | М1 |

|----------------------------------|----|----|

| 1 pc                             | 0  | 0  |

| 2 pcs                            | 0  | 1  |

| 3 pcs                            | 1  | 0  |

| 4 pcs                            | 1  | 1  |

0 = L level 1 = H level

#### 5.11 Analog Function

The T6668 has built in microphone amplifier and 2nd stage low pass + 1st stage high pass filter. Therefore, voice recording / reproducing system is easily available by connecting input to MIC and output to audio Amplifier circuit.

#### 5.11.1 Microphone Amplifier

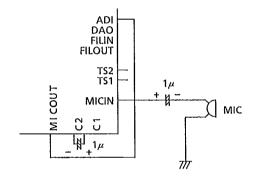

Fig.5.24 Connection of MIC

Note: Be careful for wiring. The signal from microphone is so small that noise from surroundings tends to have influence.

There are two MIC, AMP, s.

- ① between MICIN and C1 ...... Gain is about 26 dB

- ② between C2 and MICOUT ...... Gain is about 20 dB

So, there are three ways ①, ② and ① +②. One is selected by the type of MIC. C1 or MICOUT pin must be connected to ADI pin at the case of ① or ② and ① +②, respectively.

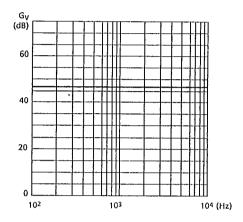

Fig.5.25 Frequency characteristics of MIC. AMP.

This characteristics is between MICIN and MICOUT with couplings C1 and C2. Further, when MIC Amp is not used, it is possible to input voice directly input ADI. In this case, however, the input level should be max. 1.6 Vp-p, centering around 1/2 Vpp.

#### 5.11.2 Filter

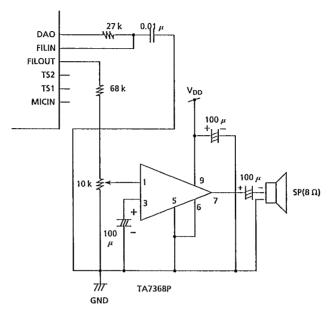

Fig.5.26 Connection of audio amp.

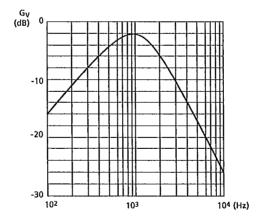

Fig. 5.27 Frequency characteristics of band pass filter This characteristic is between FILIN and FILOUT.

#### 5.11.3 Equivalent Circuits

Fig.5.28 Equivalent circuits of analog circuits

#### 5.12 Precautions

#### (1) Under manual and CPU control mode

- During recording or reproducing operation, pins of M1, M2 and 256K must not be changed.

- During the reset, the address counter, flag, etc. only are reset and oscillation does not stop; that

is, the refresh of D RAM is performed.

#### (2) Under manual control mode

- o The conditions of phrase, bit rate and recording / reproducing are kept held by START input and not changed until next START input is given. That is, T6668 does not care those conditions after START operation has done.

- During recording, START input is not accepted. This is to protect RAM data in the index area from being destructed when phrase number etc. are changed by START input during recording.

- Ouring reproducing, START input is accepted as the buffer function is available. In this case, the operation must not be started with WR placed in H level (recording mode). RAM data change and the reproducing is not properly performed.

- The START input during the recording is inhibited at address over condition (when the maximum RAM capacity is already used.). Resets address by ACL for recording.

#### (3) Under CPU control mode

Ouring recording / reproducing, do not give any other commands other than STOP command. When other commands are input to the T6668, the operation becomes unstable. 2

## 6. ELECTRICAL CHARACTERISTICS

## 6.1 Absolute Maximum Rating

| SYMBOL           | ITEM RATING         |                          | UNIT |

|------------------|---------------------|--------------------------|------|

| V <sub>DD</sub>  | Supply Voltage      | - 0.3 ~ 6.0              | V    |

| V <sub>IN</sub>  | Input Voltage       | $-0.3 \sim V_{DD} + 0.3$ | V    |

| V <sub>OUT</sub> | Output Voltage      | $-0.3 \sim V_{DD} + 0.3$ | V    |

| TsTG             | Storage Temperature | - 55 ~ 125               | °C   |

## 6.2 Recommended Operating Condition

| ITEM                  | SYMBOL           | RATING              | UNIT |

|-----------------------|------------------|---------------------|------|

| Supply Voltage        | $V_{DD}$         | 4.5 ~ 5.5           | V    |

| Input Voltage         | VIN              | 0 ~ V <sub>DD</sub> | V    |

| Output Voltage        | V <sub>OUT</sub> | 0 ~ V <sub>DD</sub> | V    |

| Oscillation Frequency | f <sub>CLK</sub> | 640 ~ 1000          | KHz  |

| Operating Temperature | Topr             | - 10 ~ 70           | °C   |

# (QU/JU) ABIHZOT

## 6.3 DC Characteristics ( $V_{DD} = 5 \text{ V} \pm 10 \text{ %}$ , Ta = 25 °C)

| SYMBOL            | ITEM                                                              | CONDITION                                    | MIN. | TYP. | MAX. | UNIT |

|-------------------|-------------------------------------------------------------------|----------------------------------------------|------|------|------|------|

| l <sub>IH</sub>   | Input Current (D <sub>0</sub> ~D <sub>7</sub> , TEST, CE, RD, WR) | V <sub>IN</sub> = V <sub>DD</sub> , CPUM = L | 20   | 100  | 500  |      |

| l <sub>IL1</sub>  | Input Current 1 D <sub>IN</sub> )                                 | V <sub>IN</sub> = 0                          | 50   | 100  | 350  | μΑ   |

| l <sub>lL2</sub>  | Input Current 2 (ACL)                                             | V <sub>IN</sub> = 0                          | 250  | 500  | 700  | μ.,  |

| ILK               | Input Leak Current                                                | $V_{IN} = 0 \sim V_{DD}$ , CPUM = H          | _    | -    | ± 10 |      |

| V <sub>IHI1</sub> | High Level Input Voltage1                                         | D0~D7, Œ, RD, WR, DIN                        | 2.4  | _    | -    |      |

| V <sub>IHI2</sub> | High Level Input Voltage2                                         | Except above                                 | 4.1  | _    | _    | V    |

| V <sub>IL1</sub>  | Low Level Input Voltage1                                          | D0~D7, CE, RD, WR, DIN                       | -    | -    | 0.8  |      |

| V <sub>IL2</sub>  | Low Level Input Voltage2                                          | Except above                                 | _    | -    | 0.4  |      |

| loH               | High Level Output Current                                         | V <sub>OUT</sub> = 2.4 V                     | 0.5  | -    | -    |      |

| loL               | Low Level Output Current                                          | V <sub>OUT</sub> = 0.8 V                     | 0.5  | -    | -    | mA   |

| I <sub>SS1</sub>  | Supply Current 1 (V <sub>SS1</sub> )                              | Under no signal, IOUT = 0 mA                 | _    | 1.0  | 3.0  |      |

| l <sub>SS2</sub>  | Supply Current 2 (V <sub>SS2</sub> )                              | Under no signal, IOUT = 0 mA                 | -    | 1.0  | 3.0  |      |

Note: Each TYP. value is under  $V_{DD}$ =5.0 V, Ta=25 °C MIN. and MAX. values are defined by their absolute values.

T6668-44

## EZOT ■ 4097249 0024985 901 ■ TOS3

## TOSHIBA (UC/UP)

# AC Characteristics ( $V_{DD} = 5 \text{ V} \pm 10\%$ , $T_a = 25 \,^{\circ}\text{C}$ , $f_{CLK} = 655 \,\text{kHz}$ , $C_L = 50 \,\text{pF}$ )

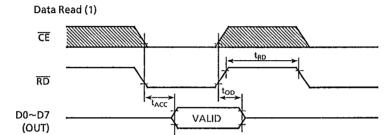

### 6.4.1 For Data Read (Status Reading)

| SYMBOL           | ITEM                             | MIN. | TYP. | MAX. | UNIT |

|------------------|----------------------------------|------|------|------|------|

| t <sub>RD</sub>  | Read Disable Time (ADRD Command) | 21   | -    | _    | μς   |

| t <sub>ACC</sub> | Read Access Time                 |      | -    | 300  |      |

| t <sub>QD</sub>  | Output Disable Time              | -    | -    | 150  | ns   |

TOSHIBA (UC/UP)

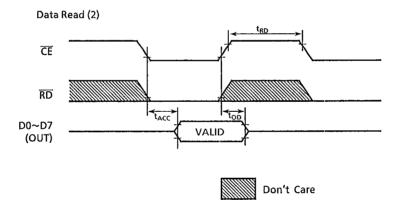

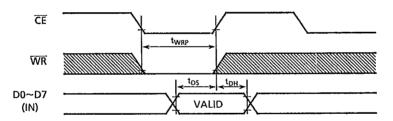

#### 6.4.2 For Data Write (Command Write)

| SYMBOL           | ITEM             | MIN. | TYP. | MAX. | UNIT |

|------------------|------------------|------|------|------|------|

| t <sub>DS</sub>  | Data Set Up Time | 500  | -    | -    | ns   |

| t <sub>DH</sub>  | Data Hold Time   | 0    | -    |      | ns   |

| t <sub>WRP</sub> | WR Pulse Width   | 300  | -    | -    | ns   |

#### Data Write (1)

#### Data Write (2)

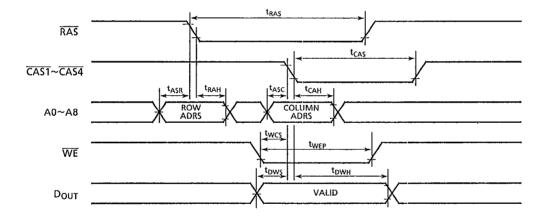

### 6.4.3 For Voice Analysis (At Recording)

| SYMBOL           | ITEM                         | MIN. | TYP. | MAX. | UNIT |

|------------------|------------------------------|------|------|------|------|

| t <sub>ASR</sub> | Low Address Set - up Time    | 150  | -    | -    |      |

| t <sub>RAH</sub> | Low Address Hold Time        | 500  | -    | _    | ns   |

| t <sub>RAS</sub> | RAS Pulse Width              | _    | 4.58 | _    | μs   |

| tASC             | Column Address Set - up Time | 150  | -    | _    |      |

| tcah             | Column Address Hold Time     | 500  | -    | -    | ns   |

| t <sub>CAS</sub> | CAS Pulse Width              | -    | 3.05 | -    | μS   |

| twcs             | Write Command Set - up Time  | -    | 1.53 | _    |      |

| twep             | WE Pulse Width               | _    | 3.05 | _    | μ\$  |

| tows             | Data Output Set - up Time    | 500  | -    | -    |      |

| t <sub>DWH</sub> | DWH Data Output Hold Time    |      | -    | -    | ns   |

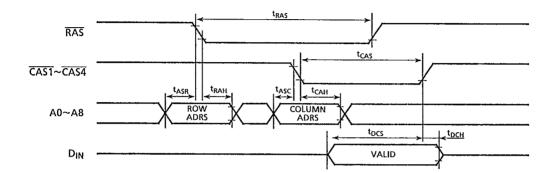

## 6.4.4 For Voice Synthesis (At Reproducing)

| SYMBOL           | ITEM MIN.                |     | TYP. | MAX | UNIT |  |

|------------------|--------------------------|-----|------|-----|------|--|

| t <sub>DCS</sub> | Data Input Set - up Time | 500 | -    | -   | ns   |  |

| t <sub>DCH</sub> | Data Input Hold Time     | 0   | -    | _   | ns   |  |

### 6.5 Characteristics of Analog Function

## 6.5.1 Micamp. ( $V_{SS1} = V_{SS2} = OV$ , $V_{DD} = 5$ V, $T_0 = 25$ °C, $f_{in} = 1$ kHz, UNLESS OTHERWISE SPECIFIED)

| SYMBOL            | ITEM                               | PIN NAME         | CONDITION                                                                            | MIN. | TYP. | MAX. | UNIT  |

|-------------------|------------------------------------|------------------|--------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>IN1</sub>  |                                    | MICIN            | MICAMP (1) + (2)                                                                     | -    | 6    | 8    |       |

| V <sub>IN2</sub>  | Allowable Input                    | MICIN            | MICAMP (1) only                                                                      | _    | 60   | 80   | mVp-p |

| V <sub>IN3</sub>  | Voltage Range                      | C2               | MICAMP (2) only                                                                      | -    | 120  | 160  |       |

| G <sub>V1</sub>   | Pass Band Gain  C2  -MICON -C1  C2 | MICIN<br>-MICOUT |                                                                                      | _    | 46   | -    |       |

| G <sub>V2</sub>   |                                    | MICIN<br>-C1     | $V_{IN} = 6 \text{ mVp} - \text{p}$ $f_{IN} = 100 \text{ Hz} \sim 10 \text{ kHz}$    | -    | 26   |      | d8    |

| G <sub>V3</sub>   |                                    | C2<br>-MICOUT    |                                                                                      | -    | 20   | -    |       |

| THD               | Total Harmonic<br>Distortion       | MICIN<br>-MICOUT | $V_{IN} = 6 \text{ mVp} - \text{p}$<br>$f_{IN} = 100 \text{ Hz} \sim 10 \text{ kHz}$ | -    | _    | 2    | %     |

| R <sub>IN1</sub>  | Land Baristan                      | MICIN            |                                                                                      | 20   | 30   | 40   |       |

| R <sub>IN2</sub>  | Input Resistance                   | C2               | _                                                                                    | 20   | 30   | 40   | kΩ    |

| R <sub>OUT1</sub> | Outnut Posistones                  | C1               | _                                                                                    |      | 1    | -    | 1.0   |

| R <sub>OUT2</sub> | Output Resistance                  | MICOUT           |                                                                                      | -    | 1    | -    | kΩ    |

#### 6.5.2 Band Pass Filter (DITTO)

| SYMBOL           | ITEM                             | PIN NAME         | CONDITION                                                                             | MIN. | TYP. | MAX. | UNIT |

|------------------|----------------------------------|------------------|---------------------------------------------------------------------------------------|------|------|------|------|

| VIN              | Allowable Input<br>Voltage Range | FILIN            | -                                                                                     | -    | 2.4  | 2.6  | Vp-p |

| G <sub>V</sub>   | Pass Band Gain                   | FILIN<br>-FILOUT | $V_{IN} = 1.0 \text{ Vp} - \text{p}$<br>$f_{IN} = 100 \text{ Hz} \sim 10 \text{ kHz}$ | - 27 | _    | -1   | dB   |

| THD              | Total Harmonic<br>Distortion     | FILIN<br>-FILOUT | $V_{IN} = 1.0 \text{ Vp} - \text{p}$<br>$f_{IN} = 100 \text{ Hz} \sim 10 \text{ kHz}$ | -    | _    | 4    | %    |

| R <sub>IN</sub>  | Input Resistance                 | FILIN            | _                                                                                     | 5    | 14   | 20   | MΩ   |

| R <sub>OUT</sub> | Output Resistance                | FILOUT           | -                                                                                     | _    | 1    |      | kΩ   |

# (QU\)U) ABIHZOT

### 6.5.3 Audio In (DITTO)

| SYMBOL. | ITEM                             | PIN NAME | CONDITION    | MIN. | TYP. | MAX. | UNIT |

|---------|----------------------------------|----------|--------------|------|------|------|------|

|         | Allowable Input<br>Voltage Range | ADI      | <del>-</del> | -    | 1.2  | 1.6  | Vp-p |

| RIN     | Input Resistance                 | ADI      | -            | 1    | -    | -    | MΩ   |

#### 6.5.4 Audio Out (DITTO)

| SYMBOL | ITEM              | PIN NAME | CONDITION | MIN. | TYP. | MAX. | UNIT |

|--------|-------------------|----------|-----------|------|------|------|------|

| Rout   | Output Resistance | DAO      | _         | -    | 5    | -    | kΩ   |

Note: Values centering around 1/2 VDD are used in allowable input voltage range.

## (QU\JU) ABIHZOT

#### 6.5.5 Measuring Circuit

(VIN, Gy, THD)

Refer to [4] Pin Connections for pin name.

## 7. OUTLINE DRAWINGS

**60 PIN MINI FLAT PACKAGE**

## 8. APPLICATION CIRCUIT