**TENTATIVE**

TOSHIBA CMOS DIGITAL INTEGRATED CIRCUITS SILICON MONOLITHIC

# TC90A35N, TC90A35F

# NICAM/IGR AUDIO SIGNAL PROCESSORS

These LSIs are designed to decode PCM and FM aural signals in UK sound multiplex broadcasts (NICAM728). In addition, they also can decode IGR sound multiplex

The QPSK modulating signal in UK sound multiplex broadcasts are capable of doing digital QPSK demodulation and PCM decoding, and also can demodulate 1-channel FM sound signal. (Simultaneous NICAM and FM outputs are not supported.) Using a digital PLL for QPSK demodulation and a digital OSC for FM demodulation, these can modulate I, B/G and any carrier used, with a single crystal. In addition, they allow for significant reduction in external part counts and materialize adjustment-free operation.

### **FEATURES**

- Decodes NICAM sound.

- Decodes FM sound.

- Decodes 2-carrier FM (IGR) sound.

- Uses digital PLL and digital OSC for multicarrier capability.

- Uses digital BPF to provide BPF characteristics matched to each system.

- Contains digital emphasis circuit for FM and PCM.

- Interfaces with a microcomputer via the I<sup>2</sup>C bus.

- Uses AGC circuit to stabilize input signal levels.

- Operates with a single crystal (18.432 MHz).

- Greatly reduces part counts thanks to digital processing.

- Operates with a single 5V power supply.

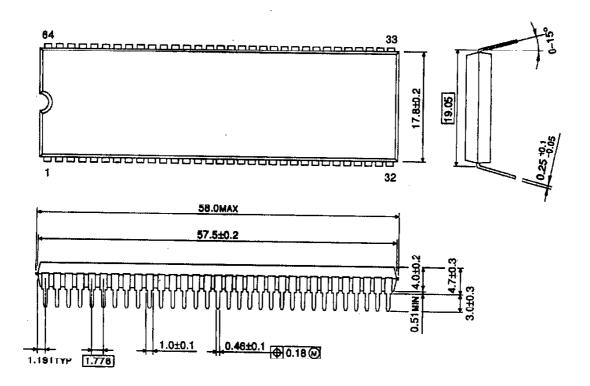

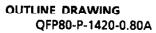

- Package: QFP80 or SDIP64

Weight

SDIP64-P-750-1.78 : 8.85 g (Typ.) QFP80-P-1420-0.80A : 1.6 g (Typ.)

(\*) These products are under development. Specifications are subject to change without notice.

980910EBA1 TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor DOMBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in the FOSHIBA semiconductor reliability Handbook.

The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information costained begin is subject to change without notice.

The information contained herein is subject to change without notice.

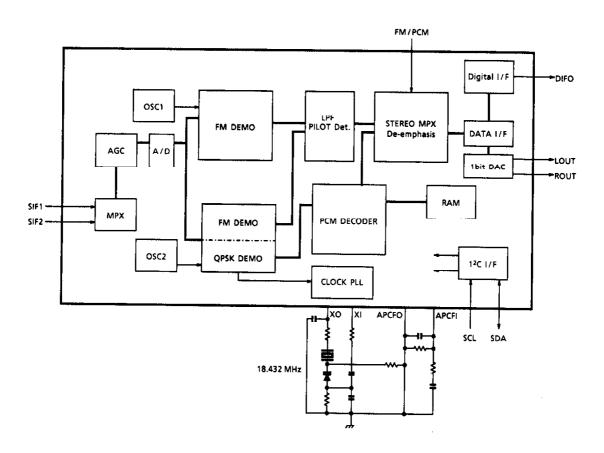

# **BLOCK DIAGRAM**

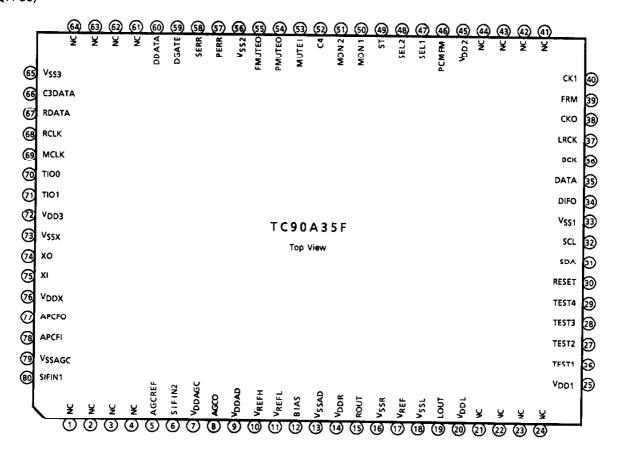

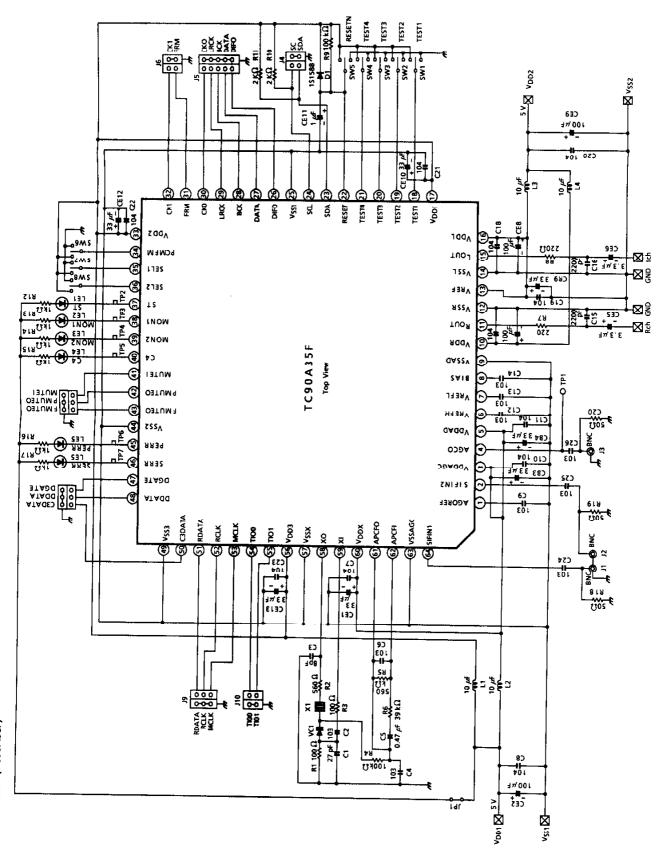

# PIN CONNECTION (QFP80)

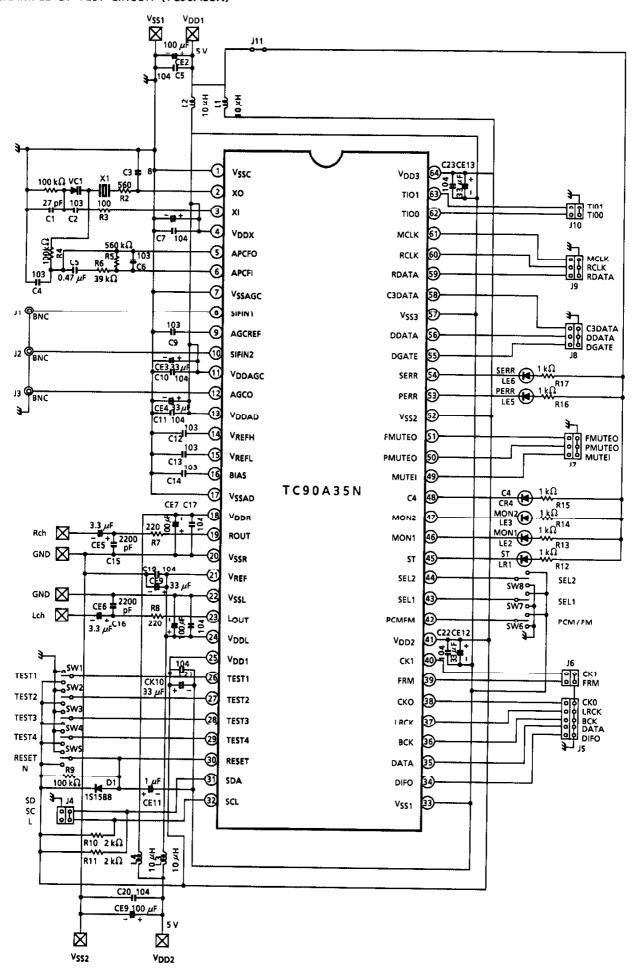

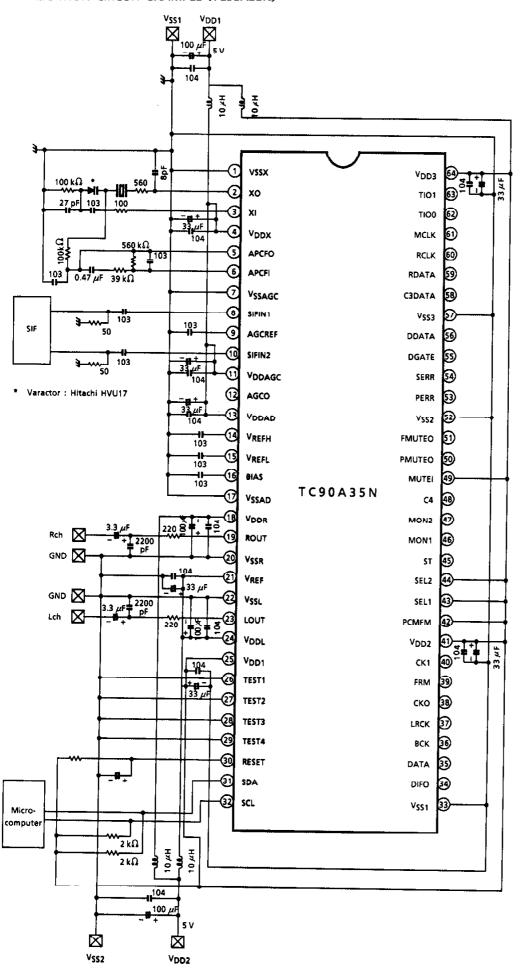

# (SDIP64)

# PIN CONNECTION (QFP80)

| PIN No. | PIN NAME           | 1/0      | FUNCTION                                       |

|---------|--------------------|----------|------------------------------------------------|

| 1       | NC                 | _        |                                                |

| 2       | NC                 | _        | _                                              |

| 3       | NC                 | T        |                                                |

| 4       | NC                 |          |                                                |

| 5       | AGCREF             |          | AGC reference                                  |

| 6       | SIF <sub>IN2</sub> | Ī        | SIF IN2                                        |

| 7       | VDDAGC             |          | AGC-V <sub>DD</sub>                            |

| 8       | AGCO               | 1/0      | AGC test I/O                                   |

| 9       | V <sub>DDAD</sub>  |          | ADC-V <sub>DD</sub>                            |

| 10      | VREFH              |          | ADC bias pin H                                 |

| 11      | VREFL              |          | ADC bias pin L                                 |

| 12      | BIAS               |          | ADC bias pin                                   |

| 13      | VSSAD              |          | ADC-V <sub>SS</sub>                            |

| 14      | V <sub>DDR</sub>   |          | Power supply for R-channel sound output filter |

| 15      | ROUT               | 0        | R-channel sound output                         |

| 16      | VSSR               | _        | GND for R-channel sound output filter          |

| 17      | VREF               |          | 1-bit DAC reference power supply               |

| 18      | V <sub>SSL</sub>   |          | GND for L-channel sound output filter          |

| 19      | LOUT               | 0        | L-channel sound output                         |

| 20      | VDDL               |          | Power supply for L-channel sound output filter |

| 21      | NC                 | <u> </u> | -                                              |

| 22      | NC                 |          |                                                |

| 23      | NC                 |          | -                                              |

| 24      | NC                 | _        |                                                |

| 25      | V <sub>DD1</sub>   |          | Digital power supply 1                         |

| 26      | TEST1              | 1        | Test pin 1                                     |

| 27      | TEST2              | l        | Test pin 2                                     |

| 28      | TEST3              | <u> </u> | Test pin 3                                     |

| 29      | TEST4              | 1        | Test pin 4                                     |

| 30      | RESET              | ı        | Reset pin                                      |

| 31      | SDA                | 1/0      | I <sup>2</sup> C bus data pin                  |

| 32      | SCL                | 1        | I <sup>2</sup> C bus clock pin                 |

| 33      | V <sub>SS1</sub>   |          | Digital GND                                    |

| 34      | DIFO               | 0        | Digital I/F output                             |

| 35      | DATA               | 0        | External DAC data output                       |

| 36      | BCK                | 0        | External DAC shift clock output                |

| 37      | LRCK               | 0        | External DAC L/R clock output                  |

| 38      | ско                | 0        | External DAC clock output                      |

| 39      | FRM                | 0        | Frame sync signal output                       |

| 40      | CK1                | 0        | Carrier output                                 |

| 41      | NC                 |          |                                                |

| 42      | NC                 |          |                                                |

| PIN No. | PIN NAME          | 1/0            | FUNCTION                         |

|---------|-------------------|----------------|----------------------------------|

| 43      | NC                | <del>  _</del> |                                  |

| 44      | NC                | <del>  _</del> |                                  |

| 45      | V <sub>DD2</sub>  |                | Digital power supply 2           |

| 46      | PCMFM             | <del>†</del> i | Analog sound PCM / FM switch     |

| 47      | SEL1              | ı              | Digital sound select input 1     |

| 48      | SEL2              | <del> -</del>  | Digital sound select input 2     |

| 49      | ST                | 0              | Stereo mode sound output         |

| 50      | MON1              | 0              | Monaural mode sound output 1     |

| 51      | MON2              | 0              | Monaural mode sound output 2     |

| 52      | C4                | 0              | C4 mode display output           |

| 53      | MUTEI             |                | Sound mute input                 |

| 54      | PMUTEO            | !              | PCM mute signal output           |

| 55      | FMUTEO            | 1              | FM mute signal output            |

| 56      | V <sub>SS2</sub>  |                | Digital GND                      |

| 57      | PERR              | 0              | Parity error output              |

| 58      | SERR              | 0              | Sync error output                |

| 59      | DGATE             | 0              | Data GATE signal output          |

| 60      | DDATA             | 0              | Data output                      |

| 61      | NC                |                |                                  |

| 62      | NC                |                |                                  |

| 63      | NC                | _              |                                  |

| 64      | NC                | _              |                                  |

| 65      | V\$\$3            |                | Digital GND                      |

| 66      | C3DATA            | 0              | C3 data output                   |

| 67      | RDATA             | 0              | QPSK demodulation signal output  |

| 68      | RCLK              | 0              | Clock output (728 kHz)           |

| 69      | MCLK              | Ö              | Clock output (carrier frequency) |

| 70      | TIOO              | 1/0            | Test I/O                         |

| 71      | TIO1              | 1/0            | Test I/O                         |

| 72      | $V_{DD3}$         | _              | Digital power supply 3           |

| 73      | Vssx              | _              | VCXO-GND                         |

| 74      | XO                | 0              | Crystal oscillation output       |

| 75      | ΧI                | Ī              | Crystal oscillation input        |

| 76      | V <sub>DD</sub> X | _              | VCXO-V <sub>DD</sub>             |

| 77      | APCFO             | 0              | APC filter output                |

| 78      | APCFI             | ī              | APC filter input                 |

| 79      | Vssagc            |                | V <sub>SS</sub> -AGC             |

| 80      | SIFIN1            | 1              | SIF IN1                          |

# PIN CONNECTION (SDIP64)

| PIN No.  | PIN NAME           | 1/0            | FUNCTION                                       |

|----------|--------------------|----------------|------------------------------------------------|

| 1        | Vssx               | <del>  _</del> | VCXO-GND                                       |

| 2        | хо                 | 0              | Crystal oscillation output                     |

| 3        | ΧI                 | 1              | Crystal oscillation input                      |

| 4        | V <sub>DD</sub> X  |                | VCXO-V <sub>DD</sub>                           |

| 5        | APCFO              | 0              | APC filter output                              |

| 6        | APCFI              | 1              | APC filter input                               |

| 7        | Vssagc             |                | V <sub>SS</sub> -AGC                           |

| 8        | SIF <sub>IN1</sub> | Ī              | SIF IN1                                        |

| 9        | AGCREF             |                | AGC reference                                  |

| 10       | SIF <sub>IN2</sub> | 1              | SIF IN2                                        |

| 11       | VDDAGC             |                | AGC-V <sub>DD</sub>                            |

| 12       | AGCO               | 1/0            | AGC test I/O                                   |

| 13       | VDDAD              |                | ADC-V <sub>DD</sub>                            |

| 14       | V <sub>REFH</sub>  | <u> </u>       | ADC bias pin H                                 |

| 15       | VREFL              | <u> </u>       | ADC bias pin L                                 |

| 16       | BIAS               | <u> </u>       | ADC bias pin                                   |

| 17       | VSSAD              |                | ADC-V <sub>SS</sub>                            |

| 18       | V <sub>DDR</sub>   |                | Power supply for R-channel sound output filter |

| 19       | ROUT               | 0              | R-channel sound output                         |

| 20       | VSSR               | <del> </del> _ | GND for R-channel sound output filter          |

| 21       | VREF               |                | 1-bit DAC reference power supply               |

| 22       | V <sub>SSL</sub>   |                | GND for L-channel sound output filter          |

| 23       | LOUT               | <u> </u>       | L-channel sound output                         |

| 24       | VDDL               |                | Power supply for L-channel sound output filter |

| 25       | V <sub>DD1</sub>   | <u> </u>       | Digital power supply 1                         |

| 26<br>27 | TEST1              |                | Test pin 1                                     |

| 28       | TEST2              |                | Test pin 2                                     |

| 29       | TEST3              | !              | Test pin 3                                     |

| 30       | TEST4<br>RESET     |                | Test pin 4                                     |

| 31       | SDA                | 1/0            | Reset pin                                      |

| 32       | SCL                | 1/0            | I <sup>2</sup> C bus data pin                  |

| 33       | V <sub>SS1</sub>   |                | I <sup>2</sup> C bus clock pin Digital GND     |

| 34       | DIFO               | <del>-</del>   |                                                |

| 35       | DATA               | 0              | Digital I/F output                             |

| 36       | BCK                | 0              | External DAC data output                       |

| 37       | LRCK               | 0              | External DAC shift clock output                |

| 38       | CKO                |                | External DAC L/R clock output                  |

| 39       | FRM                | 0              | External DAC clock output                      |

| 40       | CK1                | 0              | Frame sync signal output                       |

|          |                    | 0              | Carrier output                                 |

| 41       | V <sub>DD2</sub>   |                | Digital power supply 2                         |

| 42       | RCMFM              | 1              | Analog sound PCM/FM switch                     |

| PIN No. | PIN NAME         | 1/0 | FUNCTION                         |

|---------|------------------|-----|----------------------------------|

| 43      | SEL1             | 1   | Digital sound select input 1     |

| 44      | SEL2             | 1   | Digital sound sciect input 2     |

| 45      | ST               | 0   | Stereo mode sound output         |

| 46      | MON1             | 0   | Monaural mode sound output 1     |

| 47      | MON2             | 0   | Monaural mode sound output 2     |

| 48      | C4               | 0   | C4 mode display output           |

| 49      | MUTEI            | ı   | Sound mute input                 |

| 50      | PMUTEO           | 1   | PCM mute signal output           |

| 51      | FMUTEO           | 1   | FM mute signal output            |

| 52      | V <sub>SS2</sub> |     | Digital GND                      |

| 53      | PERR             | 0   | Parity error output              |

| 54      | SERR             | 0   | Sync error output                |

| 55      | DGATE            | 0   | Data GATE signal output          |

| 56      | DDATA            | 0   | Data output                      |

| 57      | V5S3             | _   | Digital GND                      |

| 58      | C3DATA           | 0   | C3 data output                   |

| 59      | RDATA            | 0   | QPSK demodulation signal output  |

| 60      | RCLK             | 0   | Clock output (728 kHz)           |

| 61      | MCLK             | 0   | Clock output (carrier frequency) |

| 62      | TIOO             | 1/0 | Test I/O                         |

| 63      | TIO1             | 1/0 | Test I/O                         |

| 64      | V <sub>DD3</sub> | _   | Digital power supply 3           |

# MAXIMUM RATINGS (Ta = 25°C)

| CHARACTERISTIC      | SYMBOL           | RATING                     | UNIT |

|---------------------|------------------|----------------------------|------|

| Supply Voltage      | VDD              | Vss~Vss + 7.0              | V    |

| Input Voltage       | VIN              | -0.3~V <sub>DD</sub> + 0.3 | V    |

| Power Dissipation   | PD               |                            | mW   |

| Storage Temperature | T <sub>sta</sub> | - 55~125                   | °C   |

# RECOMMENDED OPERATING CONDITIONS

| CHARACTERISTIC        | SYMBOL          | TEST CONDITION | MIN. | TYP. | MAX.            | UNIT |

|-----------------------|-----------------|----------------|------|------|-----------------|------|

| Supply Voltage        | V <sub>DD</sub> | <del>_</del>   | 4.75 | 5    | 5.25            | V    |

| Input Voltage         | VIN             | _              | 0    |      | V <sub>DD</sub> | v    |

| Operating Temperature | Topr            |                | - 20 |      | 75              | °C   |

# **ELECTRICAL CHARACTERISTICS**

DC characteristics (Unless otherwise specified, Ta = 25°C, V<sub>DD</sub> = 5 V)

| CHARACTERISTIC            | SYMBOL           | TEST CONDITION | MIN.                                               | TYP.     | MAX.        | UNIT          |

|---------------------------|------------------|----------------|----------------------------------------------------|----------|-------------|---------------|

| Current Dissipation       | lcc              |                |                                                    |          |             | mA            |

| Current Dissipation       | 1DD              | 4444           |                                                    |          |             | mA            |

| Power Dissipation         | PD               |                |                                                    |          | <del></del> | mW            |

| High-level Input Voltage  | VIH              |                | 4.0                                                |          |             | V             |

| Low-level Input Voltage   | VIL              |                | <del>-   -   -   -   -   -   -   -   -   -  </del> |          | 1.0         | V             |

| Hysteresis Width          | V <sub>H</sub>   | _              | <del> </del>                                       |          | 1.0         | V             |

| High-level Input Current  | lін              |                |                                                    | <u> </u> | 10          | μA            |

| Low-level Input Current   | IL               |                | - 10                                               |          |             | <del></del>   |

| High-level Output Voltage | V <sub>QH1</sub> | <del>_</del>   |                                                    |          |             | μA<br>V       |

| Low-level Output Voltage  | V <sub>OL1</sub> | <del></del>    |                                                    |          | -           | V             |

| High-level Output Voltage | V <sub>OH2</sub> |                | <del>  _</del> -                                   |          |             |               |

| Low level Output Voltage  | V <sub>OL2</sub> | <del>-</del>   | <del>   </del>                                     |          |             | $\overline{}$ |

# AC characteristics (Unless otherwise specified, $Ta = 25^{\circ}C$ , $V_{DD} = 5 V$ )

| CHARACTERISTIC                        | SYMBOL           | TEST CONDITION            | MIN.         | TYP.     | MAX.                                             | UNIT     |

|---------------------------------------|------------------|---------------------------|--------------|----------|--------------------------------------------------|----------|

| SCL Clock Frequency                   | fSCL             | f <sub>SCL</sub> = 1/TSCL | 0            |          | 100                                              | kHz      |

| SCL High-level Duration               | tsH              | $C_1 = 400  pF$           | 4.0          |          | <del> </del>                                     | μs       |

| SCL Low-level Duration                | tsL              | C <sub>L</sub> = 400 pF   | 4.7          |          | <del>                                     </del> |          |

| Data Setup Time                       | tDS              | C <sub>1</sub> = 400 pF   | 250          | <u> </u> | <del>                                     </del> | μs<br>ns |

| Data Hold Time                        | <sup>t</sup> DH  | C <sub>L</sub> = 400 pF   | 5.0          |          | <del>                                     </del> |          |

| Transfer Start Condition Hold<br>Time | t <sub>SCH</sub> | C <sub>L</sub> = 400 pF   | 4.0          |          | _                                                | μs       |

| Transfer End Condition Setup Time     | tECS             | C <sub>L</sub> = 400 pF   | 4.7          |          |                                                  | μ5       |

| Data Transfer Cycle                   | t <sub>BUF</sub> | C <sub>L</sub> = 400 pF   | 4.7          |          |                                                  | 445      |

| I <sup>2</sup> C Rise Time            | tir              | C <sub>L</sub> = 400 pF   | <del> </del> |          | 1.0                                              | μ5       |

| I <sup>2</sup> C Fall Time            | tif              | C <sub>L</sub> = 400 pF   | _            |          | 300                                              | ns ns    |

| DA converter output level | DAC | _ |      | 3.4 V.              |   |

|---------------------------|-----|---|------|---------------------|---|

|                           |     |   | <br> | 3.4 V <sub>p-</sub> | р |

# AUDIO OUTPUT CHARACTERISTICS

| DAC Output level   |   | _        | 3.4 | V <sub>p-p</sub> |

|--------------------|---|----------|-----|------------------|

| S/N (NICAM)        |   | _        |     | dB               |

| S/N (FM)           | _ | _        |     | dB               |

| THD (NICAM)        | — |          | ·   | dB               |

| THD (FM)           | _ | _        |     | dB               |

| Crosstalk          | _ | <u> </u> |     | dB               |

| Channel Separation |   |          |     | dB               |

# SIF INPUT WAVEFORM

| SIF Maximum Input Level  |   |                  |             | V <sub>p-p</sub>                                 | 7        |

|--------------------------|---|------------------|-------------|--------------------------------------------------|----------|

| SIF Minimum Input Level  |   | 1 = 1            |             | V <sub>p-p</sub>                                 | -        |

| AGC Range                |   | <del>  _  </del> |             | dB                                               | -        |

| Input Frequency Range    | _ | <del></del> 1    | <del></del> | MHz                                              | 7        |

| Input Capacitance        | _ |                  |             | pF                                               | ┪        |

| Input Impedance          | _ |                  |             | Ω                                                | 7        |

| RM / NICAM Level Ratio   | _ | -7               |             | dB                                               | B/G      |

|                          |   | - 10             |             | dB                                               | 1        |

| FM1/FM2 Level Ratio      |   | 7                |             | dB                                               | D/K      |

| FM / visual Signal Ratio | _ |                  | <del></del> | dB                                               |          |

| Maximum FM Deviation     | _ |                  |             | <del>                                     </del> | THD < 1% |

# PILOT SIGNAL

| Pilot Signal Modulation Ratio |   | _ | _ | %  |

|-------------------------------|---|---|---|----|

| Pilot Signal Level            | _ | - |   |    |

| C/N                           | _ |   |   | dB |

# DIGITAL DEEMPHASIS

| Chanastaristic F     |   |   |            |

|----------------------|---|---|------------|

| Characteristic Error | 1 | 1 | l ın '''1  |

| and determined and   |   |   | <br>i ar i |

|                      |   |   | <br>       |

# DIGITAL FILTER

| Passband Ripple | _ | _ |   | dB  |

|-----------------|---|---|---|-----|

| Passband        | _ |   |   | kHz |

| Attenuation     |   |   | _ | dB  |

# Specifications of crystal and varactor

Crystal

Dai-Shinku AT-49

Frequency

18.432 MHz

Frequency deviation

$\pm 20 \times 10^{-6}$  at 25°C  $\pm 3$ °C

Equivalent resistance

40  $\Omega$  (max.)

Storage temperature range Operating temperature range -40~85°C -10~70°C

Temperature characteristic

$\pm 20 \times 10^{-6} (-10 \sim 70 ^{\circ}\text{C})$

Load capacitance

$10.0 pF \pm 0.5 pF$

Drive Level

$10 \,\mu W \pm 2 \,\mu W$

Shunt Capacitance

7.0 pF (max.)

Insulation resistance

500 Ω (min.) / 100 V DC

Vibration type

Basic wave

Varactor

Hitachi HVU17

#### **FUNCTIONS**

#### (1) Outline

### 1. Input block

Incorporates an MPX circuit which selects one of the two input signals, an AGC circuit, and an 8-bit AD converter.

#### 2. Digital QP\$K demodulation block

Demodulates AD-converted QPSK modulation signal to PCM data. Multi-support system that modulates any carrier, in addition to I and B/G by digital PLL. Operates differentials and converts between parallel and serial. Use an 18.432 MHz crystal.

At the same time as QPSK demodulation, can perform FM demodulation for a channel. Output from the DA converter is one of the following: (1) NICAM (two channels), (2) IGR (two channels), and (3) FM monaural (one channel). Simultaneous output of NICAM and FM monaural is not possible.

#### 3. PCM decoder block

Generates digital sound data which are passed to the DA converter from the QPSK demodulation digital data. Also, decodes sound data and selects sound output.

## 4. Digital FM demodulation block

Demodulates AD-converted FM modulated signal using a digital oscillator and generates digital sound data which are passed to the DA converter. With an FM demodulator which uses a digital oscillator, demodulates any carrier, such as two-carrier FM multiplex broadcasting.

#### 5. SW and matrix block

Incorporates a switch for PCM/FM and a matrix for two-carrier FM multiplex broadcasting.

# 6. Digital deemphasis block

Incorporates a digital deemphasis circuit for FM and PCM. The circuit processes signals in binaseband form.

#### 7. Digital output block

Outputs digital data conforming to IEC958. Output sound data are those after digital deemphasis.

## (2) Description by Block

#### 1. SIF selector circuit

Switches between two inputs, SIFIN1 and SIFIN2. I<sup>2</sup>C bus is used for switching.

#### 2. AGC circuit

Absorbs level fluctuations in the input signal selected by the SIF selector circuit. Can automatically control gain of signals whose input level is \*\*\* to \*\*\*  $mV_{p-p}$ .

#### 3. ADC circuit

AD-converts the input signal selected by the SIF selector circuit in units of 8 bits.

#### 4. OSC circuit

Generates a carrier frequency corresponding to that used by broadcasters in various countries. I<sup>2</sup>C bus is used to set the carrier frequency.

### 5. Data playback circuit

Calculates data differentials, converts between parallel and serial, plays back data, and generates 5.824 MHz and 728 kHz clocks in sync with data.

#### 6. Sync circuit

Detects an 8-bit sync pattern (Frame Alignment Word, FAW) from the QPSK demodulation signal output by the data playback circuit. Checks the sync patterns are consecutive using the fact that one frame consists of 728 bits. Sync protection starts after two consecutive frames are in sync, when sync status is entered, and lasts until after six consecutive frames are out of sync, when async status is entered. Once FAW sync is established, perform sync on 16 frames using the CO bit in the control bits. CO sync protection starts after two consecutive CO frames are in sync, when sync status is entered, and lasts until after four consecutive CO frames are out of sync, when async status is entered. During async, Low level is output to SERR (TC90A35F: pin 58, TC90A35N: pin 54)

#### 7. Descramble circuit

Operates the built-in PN code generator in sync with the frame using the frame sync pulse from the sync circuit and eliminates the PN code in the QPSK demodulation signal. For PN scramble broadcasting, switch the display pin to the decode pin. Switch using DPSL at I<sup>2</sup>C bus address B4HEX, subaddress 04HEX. For scramble broadcasting, set the FAW initial value using the I<sup>2</sup>C bus.

# 8. Timing generator circuit

Outputs timing signals which are in sync using the frame sync pulse from the sync signal.

#### 9. Control bit detector circuit

Performs majority decision on the playback signal from the descramble circuit in units of 16 frames and outputs the control bits. Thus, data are updated every 16 frames. The detected control bits are decoded and output to C4 (TC90A35F: pin 52, TC90A35N: pin 48), MONO2 (TC90A35F: pin 51, TC90A35N: pin 47), MONO1 (TC90A35F: pin 50, TC90A35N: pin 46), and ST (TC90A35F: pin 49, TC90A35N: pin 45).

# 10.Range bit detector circuit

Detects by multiple decisions the range bit and the control information bit multiplexed with the parity bit.

#### 11. Parity detector circuit

Using the range bit and the control information bit detected by the range bit detector circuit, eliminates the range bit and the control information bit multiplexed with the parity bit and checks the parity.

#### 12.10 → 14-bit stretch circuit

According to the range bit detected by the range bit detector circuit, stretches the 10-bit data to 14-bit. Adds "00" in the lower two bits and treats the data as 16-bit.

# 13. Error interpolation circuit

If an error is detected by the parity detector circuit, performs data interpolation. For a single error, performs mean interpolation; for consecutive errors, holds the previous value.

#### 14.NICAM output selector circuit

If a received signal is monaural, two-channel, output to the digital filter can be selected using SEL1 and SEL2 at I<sup>2</sup>C bus address B4HEX and subaddress 00HEX, or external pin SEL1 (TC90A35F: 47, TC90A35N: pin 35) and external pin SEL2 (TC90A35F: 48, TC90A35N: pin 36). Because the control signals are OR-ed internally, when the I<sup>2</sup>C bus is used, connecting external pins SEL1 and SEL2 to DGND selects output to the digital filter. When external pins are used, connecting SCL (TC90A35F: pin 32, TC90A35N: pin 32) and SDA (TC90A35F: pin 31, TC90A35N: pin 31) to DVDD makes the selection.

If both control signals are set to High level, display output disappears, muting the digital sound output.

#### 15. Muting circuit

### (1) PCM muting circuit

The muting circuit outputs High level to PMUTE (TC90A35FN; pin 54, TC90A35N; pin 50).

- When a sync error occurs.

- When parity errors occur more than the specified number of times during the specified decision duration (approx. 0.5 s).

At this time, it takes seven frames until a sync error occurs. If digital mute is not in use, fix MUTEI to Low level. Switch the mute threshold value using THL0 to THL7 at I<sup>2</sup>C bus address B4HEX and subaddress 01HEX. Set the mute duration using CYLCE0 to CYLCE4 at I<sup>2</sup>C bus address B4HEX and subaddress 02HEX.

When mute is on, High level is output to PMUTEO (TC90A35F: pin 54, TC90A35N: pin 50). In the muting circuit, PMUTEO (TC90A35F: pin 54, TC90A35N: pin 50), FMUTEO (TC90A35F: pin 55, TC90A35N: pin 51), and MUTEI (TC90A35F: pin 53, TC90A35N: pin 49) are OR-ed. Setting the MUTEI pin to High level triggers mute regardless of errors. If the MUTEI pin is not used, connect it to digital GND.

## (2) FM muting circuit

When the circuit is in the following condition, the muting circuit mutes the sound output. During muting, High level is output to FMUTEO (TC90A35F: pin 55, TC90A35N: 51).

• When the FM carrier cannot be detected.

#### 16.12C Bus Control Circuit

Extracting control bits, selecting output, or setting the operating mode is performed via the I<sup>2</sup>C bus, which is an asynchronous serial interface. A register is selected using an 8-bit address and an 8-bit subaddress which data are sent to or received from. Data are transferred from SDA in sync with the SCL clock.

The contents of a register are initialized to 00HEX by inputting Low level to RESET (TC90A35F: pin 30, TC90A35N: pin 30). Data written to a register are retained until the next data are written.

(Note) After power on, set the RESET pin to Low level, then initialize before use.

# 17. Digital Deemphasis Circuit

# (1) NICAM deemphasis circuit

Digitally deemphasizes digital sound signals which are digitally demodulated according to ITU-T Recommendation J.17 characteristics. The gain error is (0.25 dB or below. This circuit can be turned on or off. Switching is done using NIEMP1 and NIEMP2 at I<sup>2</sup>C bus address B4HEX and subaddress 42HEX.

# (2) FM deemphasis circuit

Deemphasizes digitally demodulated FM sound signals. This circuit can be turned on or off. Switching is done using FMEMP1 and FMEMP2 at I<sup>2</sup>C bus address B4HEX and subaddress 41HEX.

# I<sup>2</sup>C REGISTERS

| SUBADDRESS | NAME         |                                                   |

|------------|--------------|---------------------------------------------------|

|            | DIFO         | Digital interface output switch                   |

|            | FMSEL        | FM/NICAM auto select switch                       |

| 00HEX      | <b>FMPCM</b> | FM / PCM (NICAM) output select                    |

| OOTTEX     | ERM          | Muting circuit control                            |

|            | SEL1         | Sound output main sound/sub sound switch 1        |

|            | SEL2         | Sound output main sound/sub sound switch 2        |

|            | THL7         | Mute level threshold value switch 7               |

|            | THL6         | Mute level threshold value switch 6               |

|            | THL5         | Mute level threshold value switch 5               |

| 01HEX      | THL4         | Mute level threshold value switch 4               |

| OTTEX      | THL3         | Mute level threshold value switch 3               |

|            | THL2         | Mute level threshold value switch 2               |

|            | THL1         | Mute level threshold value switch 1               |

|            | THLO         | Mute level threshold value switch 0               |

|            | CYCLE4       | Error detection duration setting 4                |

|            | CYCLE3       | Error detection duration setting 3                |

| 02HEX      | CYCLE2       | Error detection duration setting 2                |

|            | CYCLE1       | Error detection duration setting 1                |

|            | CYCLE0       | Error detection duration setting 0                |

|            | IISBUS       | Data timing 1-bit shift                           |

| 03HEX      | LRCLCREV     | Inverts LRCLC polarity.                           |

|            | PNDIN        | Supports PN scramble.                             |

|            | FAW7         | FAW scramble broadcasting initial value setting 7 |

|            | FAW6         | FAW scramble broadcasting initial value setting 6 |

|            | FAW5         | FAW scramble broadcasting initial value setting 6 |

| 08HEX      | FAW4         | FAW scramble broadcasting initial value setting 4 |

| SOITEX     | FAW3         | FAW scramble broadcasting initial value setting 3 |

|            | FAW2         | FAW scramble broadcasting initial value setting 2 |

|            | FAW1         | FAW scramble broadcasting initial value setting 1 |

|            | FAW0         | FAW scramble broadcasting initial value setting 0 |

| 9HEX       | DSPMUTE      | Sound mute                                        |

|            | SIFSEL       | SIFIN1/SIFIN2 select                              |

|            | PILOT7       | Pilot detection threshold vale setting 7          |

|            | PILOT6       | Pilot detection threshold vale setting 6          |

|            | PILOT5       | Pilot detection threshold vale setting 5          |

| AHEX       | PILOT4       | Pilot detection threshold vale setting 4          |

| MILEN      | PILOT3       | Pilot detection threshold vale setting 3          |

|            | PILOT2       | Pilot detection threshold vale setting 2          |

|            | PILOT1       | Pilot detection threshold vale setting 2          |

|            | PILOTO       | Pilot detection threshold vale setting 1          |

# <sup>2</sup>C REGISTERS

| SUBADDRESS | NAME    |                                        |

|------------|---------|----------------------------------------|

|            | LVLO    | Pilot level setting data 0             |

|            | LVL1    | Pilot level setting data 1             |

|            | LVL2    | Pilot level setting data 2             |

| 0CHEX      | LVL3    | Pilot level setting data 3             |

| CHEX       | LVL4    | Pilot level setting data 4             |

|            | LVL5    | Pilot level setting data 5             |

|            | LVL6    | Pilot level setting data 6             |

|            | LVL7    | Pilot level setting data 7             |

|            | LVL8    | FM1 level setting data 8               |

|            | LVL9    | FM1 level setting data 9               |

|            | LVL10   | FM1 level setting data 10              |

| 0DHEX      | LVL11   | FM1 level setting data 11              |

|            | LVL12   | FM1 level setting data 12              |

|            | LVL13   | FM1 level setting data 13              |

|            | LVL14   | FM1 level setting data 14              |

|            | LVL15   | FM1 level setting data 15              |

|            | LVL16   | FM2 level setting data 16              |

|            | LVL17   | FM2 level setting data 17              |

|            | LVL18   | FM2 level setting data 18              |

| DEHEX      | LVL19   | FM2 level setting data 19              |

|            | LVL20   | FM2 level setting data 20              |

|            | LVL21   | FM2 level setting data 21              |

|            | LVL22   | FM2 level setting data 22              |

|            | LVL23   | FM2 level setting data 23              |

|            | LVL24   | NICAM level data setting data 24       |

|            | LVL25   | NICAM level data setting data 25       |

|            | LVL26   | NICAM level data setting data 26       |

| FHEX       | LVL27   | NICAM level data setting data 27       |

|            | LVL28   | NICAM level data setting data 28       |

|            | LVL29   | NICAM level data setting data 29       |

|            | LVL30   | NICAM level data setting data 30       |

|            | LVL31   | NICAM level data setting data 31       |

|            | OSC23   | OSC2 oscillation frequency switch 3    |

|            | OSC22   | OSC2 oscillation frequency switch 2    |

|            | OSC21   | OSC2 oscillation frequency switch 1    |

| OHEX       | OSC13   | OSC1 oscillation frequency switch 3    |

|            | OSC12   | OSC1 oscillation frequency switch 2    |

|            | OSC11   | OSC1 oscillation frequency switch 1    |

|            | DEMMOD2 | Demodulator circuit operation select 2 |

|            | DEMMOD1 | Demodulator circuit operation select 1 |

# I<sup>2</sup>C REGISTERS

| SUBADDRESS | NAME    |                                        |

|------------|---------|----------------------------------------|

|            | FMST2   | FM stereo matrix select 2              |

|            | FMST1   | FM stereo matrix select 1              |

|            | FMEMP2  | FM emphasis setting 2                  |

| 41HEX      | FMEMP1  | FM emphasis setting 1                  |

| THEX       | PILOT2  | Pilot carrier frequency setting 2      |

|            | PILOT1  | Pilot carrier frequency setting 1      |

|            | FMDEV2  | FM deviation setting 2                 |

|            | FMDEV1  | FM deviation setting 1                 |

|            | ROLOF1  | Rolloff filter characteristic switch 1 |

| 42HEX      | ROLOF2  | Rolloff filter characteristic switch 2 |

| THE ITEM   | NIEMP1  | NICAM emphasis characteristic switch 1 |

|            | NIEMP2  | NICAM emphasis characteristic switch 2 |

|            | SYSSEL4 | Receive mode select 4                  |

| 14HEX      | SYSSEL3 | Receive mode select 3                  |

| ,          | SYSSEL2 | Receive mode select 2                  |

|            | SYSSEL1 | Receive mode select 1                  |

Description of I<sup>2</sup>C bus registers

After power on, the values of the I<sup>2</sup>C bus registers are undefined. Thus, perform reset after power on. The initial value after reset is NICAM-1 mode.

Write register (B4HEX) Subaddress 00HEX

| MSB |      |   |       |       |     |      | LSB  |

|-----|------|---|-------|-------|-----|------|------|

| 0   | DIFO | 0 | FMSEL | PCMFM | ERM | SEL2 | SEL1 |

DIFO: Digital interface output switch

0 : Digital output off1 : Digital output on

Setting DIFO to 1 and setting SIGONO and SIGON1 at subaddress 0BHEX output digital signal from DIFO (TC90A35F: pin 34, TC90A35N: pin 34).

FMSEL: C4 auto select switch

0 : Auto select

1 : PCM/FM selected by FMPCM register

Among control bits transmitted by NICAM, C4 is set to 1 when the contents of NICAM sound are the same as those transferred by FM sound. When C4 = 1, switches between automatic NICAM output (auto select) or selection (PCM/FM) by the FMPCM register.

FMPCM: FM/PCM (NICAM) output select

0 : FM

1: PCM (NICAM)

(Note) FMPCM of the I<sup>2</sup>C bus register and external pin PCMFM (TC90A35F: pin 46, TC90A35N: pin 34) are OR-ed internally. Thus, when external pin PCMFM is not used, connect to digital GND.

ERM: Muting circuit control

0: Uses muting circuit.

1 : Does not use muting circuit.

TC90A35N and TC90A35N incorporate a muting circuit, which uses error frequency detection. This bit selects whether the muting circuit is used or not. For how to set the muting circuit, see subaddresses 01HEX and 02HEX.

SEL1, SEL2: Sound select

Determines the sound mode. Depending on the type of broadcast being received (FM or NICAM) and the broadcast mode (stereo, monaural, two-channel monaural), the following sound is selected. External pins SEL1 (TC90A35F: pin 47, TC90A35N: pin 48) and SEL2 (TC90A35F: pin 48, TC90A35N: pin 47) can also control the sound selection.

(Note) SEL1 and SEL2 of the I<sup>2</sup>C bus and external pins SEL1 and SEL2 are internally OR-ed. Therefore, if the external pins are not used, connect these pins to digital GND.

### FM mode

FM stereo mode

00 : Stereo 01 : Stereo 10 : Stereo

11: Not selected (no sound output)

| MODE   | SOUND SELECTED |      | SOUND OUTPUT |      |

|--------|----------------|------|--------------|------|

|        | SEL1           | SEL2 | L            | R    |

|        | 0              | 0    | Ĺ            | R    |

| Stereo | 0              | 1    | L            | R    |

|        | 1              | 0    | L            | R    |

|        | 1              | 1    | Mute         | Mute |

### Two-channel monaural mode

00: Main sound 01: Sub sound

10: Main sound/sub sound

11: Not selected (no sound output)

| MODE        | SOUND SELECTED |      | SOUND | OUTPUT |  |

|-------------|----------------|------|-------|--------|--|

|             | SEL1           | SEL2 | L     | R      |  |

| Monaural    | 0              | 0    | M1    | M1     |  |

| Two-channel | 0              | 1    | M1    | M2     |  |

| THE CHAINIC | 1              | 0    | M2    | M2     |  |

|             | 1              | 1    | Mute  | Mute   |  |

# FM monaural mode

00 : Monaural 01 : Monaural 10 : Monaural

11: Not selected (no sound output)

| MODE                                    | SOUND SELECTED |      | SOUND | OUTPUT |

|-----------------------------------------|----------------|------|-------|--------|

|                                         | SEL1           | SEL2 | L     | R      |

|                                         | 0              | 0    | М     | М      |

| Monaural                                | 0              | 1    | М     | М      |

|                                         | 1              | 0    | М     | М      |

| *************************************** | 1              | 1    | Mute  | Mute   |

# NICAM stereo mode

The control bits in the table below are bits sent together with sound data in NICAM broadcasting. The decoder determines the mode by detecting the control bit.

|       | МС          | DE        |     | SOUND SELECTED |     | SOUND | OUTPUT |

|-------|-------------|-----------|-----|----------------|-----|-------|--------|

| Stere | ereo        |           |     | SEL1 SEL2 L    |     | L     | R      |

| 31010 |             |           | _ [ | 0              | 0   | L     | R      |

| Cont  | Control Bit |           |     | 0              | 0 1 | L     | R      |

| C1    | C2          | <b>C3</b> | C4  | 1              | 0   | L     | R      |

| 0     | 0           | 0         | 0/1 | 1              | 1   | Mute  | Mute   |

| MODE        |       |                    |     | SOUND SELECTED |    | SOUND | OUTPUT |  |

|-------------|-------|--------------------|-----|----------------|----|-------|--------|--|

| Monaurai    |       | Monaural SEL1 SEL2 |     | SEL2           | L  | R     |        |  |

|             | chang |                    |     | 0              | 0  | M1    | M1     |  |

| Control Bit |       | 0 1                | 1   | M2             | M2 |       |        |  |

| C1          | C2    | C3                 | C4  | 1              | 0  | M1    | M2     |  |

| 0           | 1     | 0                  | 0/1 | 1              | 1  | Mute  | Mute   |  |

|           | MC     | DDE   |     | SOUND SELECTED |      | SOUND | OUTPUT |

|-----------|--------|-------|-----|----------------|------|-------|--------|

| Mon       | aural  | + Dat | +a  | SEL1           | SEL2 | L     | R      |

|           |        |       |     | 0              | 0    | Mute  | Mute   |

| Cont      | rol Bi | t     |     | 0              | 1    | Mute  | Mute   |

| <u>C1</u> | C2     | C3    | C4  | 1              | 0    | Mute  | Mute   |

| 1         | 0      | 0     | 0/1 | 1              | 1    | M     | М      |

|        | МО     | DE |     | SOUND | SELECTED | SOUND | OUTPUT |

|--------|--------|----|-----|-------|----------|-------|--------|

| Data   |        |    |     | SEL1  | SEL2     | L     | R      |

|        |        |    |     | 0     | 0        | FM    | FM     |

| Contro | ol Bit |    |     | 0     | 1        | FΜ    | FM     |

| C1     | C2     | C3 | C4  | 1     | 0        | FM    | FM     |

| 1      | _1     | 0  | 0/1 | 1     | 1        | FM    | FM     |

|      | MC     | DE |     | SOUND SELECTED |      | SOUND | OUTPUT |

|------|--------|----|-----|----------------|------|-------|--------|

| Othe | rc     |    |     | SEL1           | SEL2 | L     | R      |

|      |        |    |     | 0              | 0    | FM    | FM     |

| Cont | rol Bi | t  |     | 0              | 1    | FM    | FM     |

| C1   | C2     | C3 | C4  | 1              | 0    | FM    | FM     |

| Х    | Х      | 0  | 0/1 | 1              | 1    | FM    | FM     |

# Subaddress 01HEX

| MSB  |      |      |      |      |      |      | LSB  |

|------|------|------|------|------|------|------|------|

| THL7 | THL6 | THL5 | THL4 | THL3 | THL2 | THL1 | THLO |

THL7 to THL0: Mute level threshold value

Set values: 00 to FF (1 to 256 samples)

This register is used to set level where mute is applied.

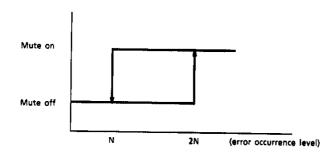

Combining the set mute threshold value and the set mute duration at subaddress 02HEX can set muteon status to any error detection duration and error frequency.

The muting circuit has ON/OFF hysteresis as shown below. When a parity error occurs to (set value  $\times$  2) samples, mute turns on.

When errors return to (set value  $\times$  1), mute turns off.

\* 1 frame = 64 samples = 1/728 s

#### Subaddress 02HEX

| MSB |   |   |        |        |        |        | LSB |

|-----|---|---|--------|--------|--------|--------|-----|

| 0   | 0 | 0 | CYCLE4 | CYCLE3 | CYCLE2 | CYCLE1 |     |

|     |   |   |        |        |        |        |     |

CYCLE4 to CYCLE0 : Set error detection duration.

Set values: 00 to 1F (0 to 31 super frames\*)

\* 1 super frame = 10 frames =  $16 \times (1/728)$  s

This register is used to set the error detection duration for mute. If a parity error at the level set at subaddress 01HEX is detected during the set duration, mute turns on.

#### Subaddress 03HEX

| MSB    |          |       |   |   |   |   | LSB |

|--------|----------|-------|---|---|---|---|-----|

| IISBUS | LRCLKREV | PNDIN | 0 | 0 | 0 | 0 | 0   |

IISBUS: Data timing 1-bit shift

LRCLKREV: Inverts polarity of LRCLK.

PNDIN: Supports PN scramble.

Set the functions of external pins TIO0 (TC90A35F: pin 70, TC90A35N: pin 58) and TIO1 (TC90A35F:

pin 71, TC90A35N: pin 59) as follows:

TIO0 = CWCLOCK

TIO1 = CWDATA

#### Subaddress 08HEX

| MSB  |      |      |      |      |      |      | LSB  |

|------|------|------|------|------|------|------|------|

| FAW7 | FAW6 | FAW5 | FAW4 | FAW3 | FAW2 | FAW1 | FAW0 |

FAW7 to FAW0 : Set the FAW scramble broadcasting initial value.

When receiving FAW scramble broadcasting, set the initial value in this register.

(Note) After the IC is reset "01001110" which is the NICAM broadcasting specification, is set as the initial value. Note that if the register is accessed, the value is altered and remains altered unless "01001110" is set again (decoding becomes impossible). Do not access the register unless necessary.

#### Subaddress 09HEX

| MSB      |   |   |   |   |   |        | LSB |

|----------|---|---|---|---|---|--------|-----|

| DSPCMUTE | 0 | 0 | 0 | 0 | 0 | SIFSEL | 0   |

**DSPCMUTE:** Sound mute

0 : Normal 1 : Mute

Applies mute to sound output. Valid for both NICAM and FM sounds. For mute when an NICAM or FM error occurs, see subaddresses 01 and 02HEX.

SIFSEL: Selects SIFIN1 or SIFIN2.

0 : SIFIN11 : SIFIN2

Selects Input to SIFIN1 (TC90A35F: pin 80, TC90A35N: pin 8) or SIFIN2 (TC90A35F: pin 6, TC90A35N: pin 10).

#### Subaddress OA HEX

| MSB     |         |         |         |         |         |         | LSB     |

|---------|---------|---------|---------|---------|---------|---------|---------|

| PILOTH7 | PILOTH6 | PILOTH5 | PILOTH4 | PILOTH3 | PILOTH2 | PILOTH1 | PILOTH0 |

PILOTH7 to PILOTH0 : Set pilot detection threshold value.

# Subaddress OB HEX

| MSB    |        |  |  | <br>LSB |

|--------|--------|--|--|---------|

| SIGON0 | SIGON1 |  |  |         |

SIGON0: External DAC signal output 0

0: Does not use digital interface.

1: Uses digital interface.

SIGON1: External DAC signal output 1

0: Does not use digital interface.

1: Uses digital interface.

When using a digital interface, set both SIGONO and SIGON1 to 1 and DIRO at subaddress 00HEX to 1.

# Subaddress OC HEX

| MSB  |      |      |      |      |      |      | LSB  |

|------|------|------|------|------|------|------|------|

| LVLO | LVL1 | LVL2 | LVL3 | LVL4 | LVL5 | LVL6 | LVL7 |

LVL0 to LVL7 : Set pilot level data 1

### Subaddress OD HEX

| MSB  |      |       |       |       |       |       | LSB   |

|------|------|-------|-------|-------|-------|-------|-------|

| LVL8 | LVL9 | LVL10 | LVL11 | LVL12 | LVL13 | LVL14 | LVL15 |

LVL8 to LVL15 : Set FM1 level data.

Set an FM1 detection threshold value.

### Subaddress OE HEX

| MSB   |       |       |       |       |       | ***************** | LSB   |

|-------|-------|-------|-------|-------|-------|-------------------|-------|

| LVL16 | LVL17 | LVL18 | LVL19 | LVL20 | LVL21 | LVL22             | LVL23 |

LVL16 to LVL23 : Set FM2 level data.

Set an FM2 detection threshold value.

#### Subaddress OF HEX

| MSB   |       |       |       |       |       |       | LSB   |

|-------|-------|-------|-------|-------|-------|-------|-------|

| LVL24 | LVL25 | LVL26 | LVL27 | LVL28 | LVL29 | LVL30 | LVL31 |

LVL24 to LVL31 : Set NICAM level data.

Set a NICAM detection threshold value.

# Subaddress 40 HEX

| MSB   |       |       |       |       |       |         | LSB     |

|-------|-------|-------|-------|-------|-------|---------|---------|

| OSC23 | OSC22 | OSC21 | OSC13 | OSC12 | OSC11 | DEMMOD2 | DEMMOD1 |

OSC23 to OSC21 : Set the oscillation frequency of internal oscillator 2.

000 6.552 MHz

100 5.85 MHz

010 5.74 MH≥

110 6.74 MHz

001 4.74 MHz

OSC13 to OSC11: Set the oscillation frequency of internal oscillator 1.

000 6.0 MHz

100 5.5 MHz

010 6.5 MHz

110 4.5 MHz

DEMMOD : Selects the demodulator circuit operation.

00 : NICAM + FM

10 : FM + FM (two-carrier FM)

01, 11 : FM (monaural)

(Note) When NICAM + FM mode is selected by setting DEMMOD to 00, FM and NICAM are decoded internally but cannot be output simultaneously.

# Subaddress 41HEX FM decoder setting switch

| MSB   |       |        |        |        |        | <u> </u> | LSB |

|-------|-------|--------|--------|--------|--------|----------|-----|

| FMST2 | FMST1 | FMEMP1 | FMEMP1 | PILOT2 | PILOT1 | FMDEV2   |     |

FMST2, FMST1 : Set FM stereo matrix.

00 : L/R

10 : L+R/2R

01 : L+R/L-R

FMEMP2, FMEMP1: Set FM emphasis.

00 : 50 μs

10 :  $75 \mu s$

01: Bypasses the emphasis circuit.

PILOT2, PILOT1: Set pilot carrier in two-carrier FM mode.

00 : IGR

FMDEV1, FMDEV2 : Set FM deviation.

FMDEV2, FMDEV1

00 : 50 kHz

10 : 30 kHz

01 : 25 kHz

Subaddress 42HEX NICAM decoder setting switch

| MSB    |        |        |        |   |   |   | LSB |

|--------|--------|--------|--------|---|---|---|-----|

| ROLOF1 | ROLOF2 | NIEMP1 | NIEMP2 | 0 | 0 | 0 | 0   |

The TC90A35F and TC90A35N incorporate a NICAM rolloff filter and deemphasis circuit.

ROLOF1, 2: Switch rolloff filter characteristics.

00 : 100% (1)

10 : 40% (B/G)

NIEMP1, 2:

00 : J. 17 (+6 dB)

01 : J. 17

10 : Bypasses the deemphasis circuit

#### Subaddress 44HEX

| MSB     |         |         |         |   |          |          | LSB |

|---------|---------|---------|---------|---|----------|----------|-----|

| SYSSEL4 | SYSSEL3 | SYSSEL2 | SYSSEL1 | 0 | SCANPRD2 | SCANPRD1 | 0   |

SYSEL4 to SYSEL1 : Select receive mode

0000 : NICAM I

0001 : NICAM B/G

0010 : IGR (two-carrier FM)

0100 : NICAM D/K

0101 : FM B/G

0110 : FM I

0111 : FM D/K

1000 : External setting mode

— Manual setting mode

To support different broadcasting modes, the TC90A35F/N contains in internal ROM parameters such as oscillation frequencies, pilot carrier frequencies, FM emphasis characteristics, FM deviations, and NICAM emphasis characteristics.

Setting SYSSEL determines the combination of parameters used to read data. Combinations of parameters are as shown in the table below. The initial value after reset is SYSSEL = 0000.

Preset mode

| SYSSEL | CONTENTS  | MODE       | OSC1 OSCILLATION FREQUENCY | OSC2<br>OSCILLATION<br>FREQUENCY | FM<br>DEVI-<br>ATIONS | PILOT<br>SIGNAL | FM<br>EMPHASIS | ROLLOFF<br>RATIO | FM<br>MATRIX<br>MODE |

|--------|-----------|------------|----------------------------|----------------------------------|-----------------------|-----------------|----------------|------------------|----------------------|

| 0000   | NICAM-I   | FM + NICAM | 6.0 MHz                    | 6.552 MHz                        | 50 kHz                | _               | 50 μs          | 100%             |                      |

| 0001   | NICAM-B/G | FM + NICAM | 5.5 MHz                    | 5.85 MHz                         | 50 kHz                | _               | 50 μs          | 40%              |                      |

| 0010   | IGR       | FM + FM    | 5.5 MHz                    | 5.7421875 MHz                    | 30 kHz                | 54.6875 kHz     | 50 μs          |                  | L+R/2R               |

| 0100   | NICAM-D/K | FM + NICAM | 6.5 MHz                    | 5.85 MHz                         | 50 kHz                | _               | 50 μs          |                  | ET 11 / EN           |

| 0101   | FM-B/G    | FM         | 5.5 MHz                    |                                  | 50 kHz                | _               | 50 μs          |                  |                      |

| 0110   | FM-I      | FM         | 6.0 MHz                    | <del></del>                      | 50 kHz                |                 | 50 μs          |                  | — <del>-</del>       |

| 0111   | FM-D/K    | FM         | 6.5 MHz                    |                                  | 50 kHz                |                 | 50 μs          |                  | <del></del>          |

# Setting of actual receive modes

1. Preset mode (mode which can be set by SYSSEL)

Parameters can be determined at subaddresses 40HEX to 42HEX. However, normally, all the parameters can be set using SYSSEL at subaddress 44HEX only.

After the IC is reset, set the desired receive mode in SYSSEL.

2. Manual setting mode (mode which cannot be set by SYSSEL)

To change some SYSSEL parameters, overwrite using the I<sup>2</sup>C bus after the mode is set in SYSSEL.

- (1) Set SYSSEL at 44HEX.

- (2) Set the parameters to be changed at 40HEX to 42HEX.

- (3) Set 1000 in SYSSEL and transmit the coefficients.

(Note) When the parameters at 40HEX to 42HEX are changed, TYSSEL = 10000 must be set. Otherwise, coefficients will not be transmitted to their destinations.

TC90A35F, TC90A35N address B5HEX (read register)

| RFAD<br>ORDER | SIGNAL<br>NAME | FUNCTION                  | DESCRIPTION                                                                                                                                                                       |  |  |  |  |  |

|---------------|----------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1             | C1             |                           |                                                                                                                                                                                   |  |  |  |  |  |

| 2             | C2             | Control bits              | Indicate the control bits to be transmitted in NICAM broadcast mode.                                                                                                              |  |  |  |  |  |

| 3             | C3             | Control bits              |                                                                                                                                                                                   |  |  |  |  |  |

| 4             | C4             | 7                         |                                                                                                                                                                                   |  |  |  |  |  |

| 5             | SERR           | Sync error                | Set to 1 when a sync error occurs.                                                                                                                                                |  |  |  |  |  |

| 6             | PMUTEO         | NICAM mute signal         | Set to 1 when mute is applied to NICAM.                                                                                                                                           |  |  |  |  |  |

| 7             | CIB1           | Information bit           |                                                                                                                                                                                   |  |  |  |  |  |

| 8             | CIB2           | Information bit           |                                                                                                                                                                                   |  |  |  |  |  |

| 9             | LDET           | Level detection result    | Indicates the detection result for the mode specified by subaddress 44HEX (SYSSEL). For example, when SYSSEL = 0000 (NICAM-1) is set, detecting FM and NICAM results in LDET = 1. |  |  |  |  |  |

| 10            | <b>FMMUTEO</b> | FM mute signal            | Set to 1 when mute is applied to FM.                                                                                                                                              |  |  |  |  |  |

| 11            | PLT2           | Pilot signal 2            | Indicate IGR mode detection result. PLT2: PLT1 = 0:0 = MONO                                                                                                                       |  |  |  |  |  |

| 12            | PLT1           | Pilot signal 1            | PLT2 : PLT1 = 1 : 0 = 2ch MONO<br>PLT2 : PLT1 = 0 : 1 = STEREO                                                                                                                    |  |  |  |  |  |

| 13            | SYSSEL3        |                           | Indicate FM + NICAM or FM receive mode.  SYSSEL3: SYSSEL2: SYSSEL1: SYSSEL0 =  0000 = NICAM I, 0001 = NICAM B/G, 0010 = IGR,  0100 = NICAM D/K, 0101 = FM B/G, 0110 = FM I,       |  |  |  |  |  |

| 14            | SYSSEL2        | ]                         |                                                                                                                                                                                   |  |  |  |  |  |

| 15            | SYSSEL1        | Receive mode              |                                                                                                                                                                                   |  |  |  |  |  |

| 16            | SYSSELO        |                           | 0111 = FM D/K                                                                                                                                                                     |  |  |  |  |  |

| 17            | LVLDT0         |                           |                                                                                                                                                                                   |  |  |  |  |  |

| 18            | LVLDT1         | ļ                         |                                                                                                                                                                                   |  |  |  |  |  |

| 19            | LVLDT2         | 4                         | Indicate FM1 detection result.                                                                                                                                                    |  |  |  |  |  |

| 20            | LVLDT3         | FM 1 level detection data |                                                                                                                                                                                   |  |  |  |  |  |

| 21            | LVLDT4         | - Control delication dela |                                                                                                                                                                                   |  |  |  |  |  |

| 22            | LVLDT5         | 1                         |                                                                                                                                                                                   |  |  |  |  |  |

| 23            | LVLDT6         | 1                         |                                                                                                                                                                                   |  |  |  |  |  |

| 24            | LVLDT7         |                           |                                                                                                                                                                                   |  |  |  |  |  |

| 25            | LVLDT9         | •                         |                                                                                                                                                                                   |  |  |  |  |  |

| 27            | LVLDT9         | 1                         |                                                                                                                                                                                   |  |  |  |  |  |

| 28            | LVLDT10        |                           |                                                                                                                                                                                   |  |  |  |  |  |

| 29            | LVLDT12        | FM 2 level detection data | Indicate FM2 detection result.                                                                                                                                                    |  |  |  |  |  |

| 30            | LVLDT13        |                           |                                                                                                                                                                                   |  |  |  |  |  |

| 31            | LVLDT14        |                           |                                                                                                                                                                                   |  |  |  |  |  |

| 32            | LVLDT15        |                           |                                                                                                                                                                                   |  |  |  |  |  |

| 33            | LVLDT16        |                           |                                                                                                                                                                                   |  |  |  |  |  |

| 34            | LVLDT17        |                           | İ                                                                                                                                                                                 |  |  |  |  |  |

| 35            | LVLDT18        |                           |                                                                                                                                                                                   |  |  |  |  |  |

| 36            | LVLDT19        | NICAM level detection     |                                                                                                                                                                                   |  |  |  |  |  |

| 37            | LVLDT20        | data                      | Indicate NICAM detection result.                                                                                                                                                  |  |  |  |  |  |

| 38            | LVLDT21        |                           |                                                                                                                                                                                   |  |  |  |  |  |

| 39            | LVLDT22        |                           |                                                                                                                                                                                   |  |  |  |  |  |

| 40            | LVLDT23        |                           |                                                                                                                                                                                   |  |  |  |  |  |

# Description of I<sup>2</sup>C bus functions

The TC90A35F/N uses I<sup>2</sup>C bus specifications (Philips bus specifications) as the interface for controlling operation. The I<sup>2</sup>C bus specifications are designed to transfer data between ICs using a common serial bus. Both TC90A35F and TC90A35N are designed so that they can operate on an I<sup>2</sup>C bus.

#### 1. Outline

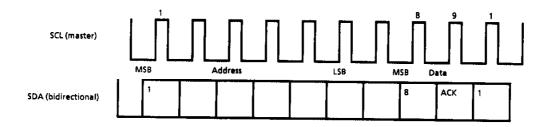

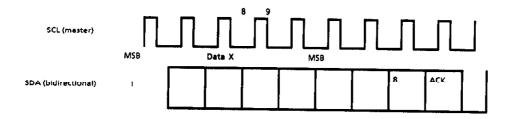

The I<sup>2</sup>C bus consists of two lines, SCL and SDA.

Data are transferred on the SDA line in units of 8 bits in sync with the clock of the SCL line. Transfer start and end are controlled by changing SDA when the SCL line is High level. Acknowledge is defined in units of bytes, thus a 1-bit acknowledge is sent after 8-bit data are transferred.

The I<sup>2</sup>C bus assumes multimasters but the TC90A35F/N supports only a slave function. Therefore, data are transferred at a point between the master and the slave (in this case, TC90A35F/N). Transfer start, end, slave selection, and operating mode are all controlled by the then master. Therefore, the SCL line is always controlled by the master and the slave (TC90A35F/N) is set to input. The SDA line is bidirectional. Input/output is switched by a register of the slave (TC90A35F/N). The SCL is driven by the master. The SDA line is driven by an open drain from the master or TC90A35F/N and pulled up by a pull-up resistor.

The master must control transfer (eg, switch input/output of SDA line) by the operating mode (read/write) of the slave address (TC90A35F/N).

#### 2. Address

The I<sup>2</sup>C bus allocates two 8-bit addresses to a slave. As the list of I<sup>2</sup>C bus registers shows, B4HEX is assigned as the write address, B5HEX as the read address. An 8-bit subaddress is also set. To control TC90A35F/N, data are sent/received by specifying an address and a subaddress.

#### 3. Data Block

The I<sup>2</sup>C bus can transfer any number of bytes in units of 8 bits. With the TC90A35F/N, as the list of I<sup>2</sup>C bus registers shows, 8 bits are transferred for B4HEX or B5HEX.

All the TC90A35F/N registers are static, so the previous values are retained until the next update. The slave registers are undefined after power on. Always input Low level to the RESET pin (TC90A35N: pin 30, TC90A35F: pin 30) and initialize to 00HEX.

# 4. Transfer Sequence

# 4.1 Transfer Start and End

Data are transferred in sync with the SCL line. In standby mode, both SDL and SDA lines are left at high impedance. Because both lines are pulled up, they are High level. Data transfer starts when the SDA line changes from High to Low while the SCL line is at High level and ends when the SDA line changes from Low to High while the SCL line is at High level. There are no such sequences during data transfer duration (see sequences 1 and 2).

# 4.2 SCL Line and SDA Line Timing

The SDA line data must be valid between the SCL line rising and falling. To make sure data are valid, the transmitting side should output data to the SDA line after checking that the SCL line changes from High to Low level. Due to this restriction, there are no start and end sequences during data transfer.

#### 4.3 Acknowledge

When 8-bit data are correctly received in the write register, the TC90A35F/N sets the SDA line to Low level. When the master detects this, it knows that data are received correctly. If acknowledge remains at High level, data are not received correctly. Then, the master must retransmit the data.

#### 4.4 Data Transfer Order

The polarity of the SDA line is positive. Data are transferred from the MSB to the LSB of the address, then the MSB to the LSB of the data.

# 4.5 Data Transmit/Receive Switch Timing

To receive acknowledge after transfer of 8 bits, the master sets the SDA line to high impedance after the SCL line falls after outputting an 8-bit address. The TC90A35F/N outputs acknowledge to the SDA line in sync with the fall of the SCL line. The SDA line returns to high impedance after the SCL line falls after outputting acknowledge.

#### I<sup>2</sup>C bus control example

After power on, the master sets the SCL and SDA lines to high impedance.

Then, the TC90A35F/N inputs Low level to RESET to initialize the IC. Low level can be input to RESET using an external RC or by a pulse from the microcomputer.

At this time, the TC90A35F/N can be controlled externally and the write register at address B4HEX is initialized to 00HEX.

Here, for slave registers whose initial settings you want to change, send the initial data. For example, to select NICAM-B/G at automatic system setting, send data 01HEX to subaddress 44HEX. Using this as an example, transfer is described in more detail.

First, output High level to the SCL and SDA lines. Then, to start transfer, set the SDA line to Low level, then the SCL line to Low level.

Next, send the address. Transfer starts from the MSB. As a data string for address B4HEX, send 10110100 (transfer starting from the MSB). For the first bit transfer, set the SDA line to High level, the SCL line to High level, then return to Low level. Then, in sync with the SCL line, change the SDA line to Low level, High level, Low level, High level, Low level, then Low level, transfer the 8-bit address, change the SCL line to High level and confirm that acknowledge is Low level. After confirmation, change the SCL line to Low level then proceed from transfer of the address to transfer of the subaddress.

To transfer the subaddress, start from the MSB. As a data string for subaddress B4HEX, send 01000100 (transfer starting from the MSB). For the first bit transfer, set the SDA line to Low level, the SCL line to High level, then return to Low level. Then, in sync with the SCL line, change the SDA line to High level, Low level, Low level, High level, Low level, then Low level, transfer the 8-bit subaddress, change the SCL line to High level and confirm that acknowledge is Low level. After confirmation, change the SCL line to Low level then proceed from transfer of the subaddress to transfer of data.

The data string at 01HEX is 00000001. In sync with the SCL line, change the SDA line to Low level, Low level, Low level, Low level, Low level, Low level, then High level, transfer the 8-bit data.