# Dual-Channel Isolators with Integrated DC/DC Converter, 50 mW

# **Preliminary Technical Data**

# ADuM5240/ADuM5241/ADuM5242

#### **FEATURES**

Integrated isolated DC/DC converter

Regulated 5V/10 mA output

Dual dc-to-10 Mbps (NRZ) signal isolation channels

Narrow body SOIC 8-lead package

High temperature operation: 105°C

Precise timing characteristics:

3 ns maximum pulse-width distortion

3 ns maximum channel-to-channel matching

70 ns maximum propagation delay

High common-mode transient immunity: > 25 kV/ $\mu$ s Safety and regulatory approvals (pending)

**UL** recognition

2500 V rms for 1 minute per UL 1577

CSA component acceptance notice #5A

VDE certificate of conformity

DIN EN 60747-5-2 (VDE 0884 Part 2): 2003-01

DIN EN 60950 (VDE 0805): 2001-12; DIN EN 60950: 2000

V<sub>IORM</sub> = 425 V peak

#### **GENERAL DESCRIPTION**

The ADuM524x¹ are dual-channel digital isolators having an integrated DC/DC converter. Based on Analog Devices' *i*Coupler® technology, the DC/DC converter provides up to 50 mW of regulated, isolated power at +5V. This eliminates the need for a separate isolated DC/DC converter in low-power isolated designs. Analog Devices' chip-scale transformer *i*Coupler® technology is used both for the isolation of the logic signals as well as for the DC/DC converter. The result is a small form-factor total-isolation solution.

ADuM524x units may be used in combination or with other *i*Coupler products to achieve greater channel counts.

The ADuM524x isolators provide two independent isolation channels in a variety of channel configurations and data rates (see Ordering Guide) operating off a 5V input supply.

#### **FUNCTIONAL BLOCK DIAGRAM**

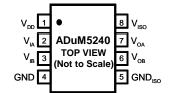

Figure 1. ADuM5240 Functional Block Diagram

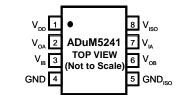

Figure 2. ADuM5241 Functional Block Diagram

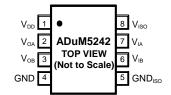

Figure 3. ADuM5242 Functional Block Diagram

<sup>&</sup>lt;sup>1</sup> Protected by U.S. Patents 5,952,849 6,873,065 and 7,075,329 Other patents pending.

# **SPECIFICATIONS**

#### **ELECTRICAL CHARACTERISTICS<sup>1</sup>**

All voltages are relative to their respective ground. All min/max specifications apply over the entire recommended operating range, unless otherwise noted. All typical specifications are at  $T_A = 25$ °C,  $V_{DD} = 5.0$  V,  $V_{ISO} = 5.0$  V.

Table 1.

| Parameter                                           | Symbol                              | Min                     | Тур   | Max          | Unit  | <b>Test Conditions</b>                                 |

|-----------------------------------------------------|-------------------------------------|-------------------------|-------|--------------|-------|--------------------------------------------------------|

| With DC/DC Converter Enabled:                       |                                     |                         |       |              |       |                                                        |

| DC to 2 Mbps Data Rate:                             |                                     |                         |       |              |       | Logic signal freq. ≤ 1 MHz                             |

| Setpoint                                            | V <sub>ISO</sub>                    | 5.0                     |       | 5.5          | V     |                                                        |

| Maximum Output Current                              | I <sub>ISO(max)</sub>               | 10                      |       |              | mA    |                                                        |

| Input Supply Current <sup>2</sup>                   |                                     |                         |       |              |       |                                                        |

| At Maximum Output Current                           | I <sub>DD(max)</sub>                |                         |       | 125          | mA    | I <sub>ISO</sub> = 10 mA, Logic signal freq. ≤ 1 MHz   |

| With No Output Current                              | I <sub>DD(0)</sub>                  |                         |       | 95           | mA    | I <sub>ISO</sub> = 0                                   |

| 10 Mbps Data Rate:                                  |                                     |                         |       |              |       | Logic signal freq. = 5 MHz                             |

| Setpoint                                            | V <sub>ISO</sub>                    | 4.5                     |       | 5.5          | V     |                                                        |

| Maximum Output Current                              | I <sub>ISO(max, 10)</sub>           |                         |       |              |       |                                                        |

| ADuM5240                                            |                                     | 8.5                     |       |              | mA    |                                                        |

| ADuM5241                                            |                                     | 7.0                     |       |              | mA    |                                                        |

| ADum5242                                            |                                     | 5.7                     |       |              | mA    |                                                        |

| Input Supply Current <sup>3</sup>                   |                                     |                         |       |              |       |                                                        |

| At Maximum Output Current                           | I <sub>DD(max)</sub>                |                         |       | 125          | mA    | I <sub>ISO(max, 10)</sub> , Logic signal freq. = 5 MHz |

| With No Output Current                              | I <sub>DD(0)</sub>                  |                         |       | 100          | mA    | I <sub>ISO</sub> = 0, Logic signal freq. = 5 MHz       |

| With DC/DC Converter Disabled:                      | 100(0)                              |                         |       |              |       | 1.55 - 1, == 3.1 - 1.51 - 1.11 - 1.11                  |

| DC to 2 Mbps                                        | I <sub>DD(2)</sub>                  |                         |       |              |       | Logic signal freq.≤1 MHz                               |

| Input Supply Current, V <sub>DD</sub> <sup>2</sup>  | 100(2)                              |                         |       |              |       | Logic signal freq 1 Will iz                            |

| ADuM5240                                            |                                     |                         |       | 3.3          | mA    |                                                        |

| ADuM5241                                            |                                     |                         |       | 2.7          | mA    |                                                        |

| ADuM5241<br>ADuM5242                                |                                     |                         |       | 2.7          | mA    |                                                        |

| Input Supply Current, V <sub>ISO</sub> <sup>2</sup> |                                     |                         |       | 2.2          | 111/4 |                                                        |

|                                                     |                                     |                         |       | 1.6          | m 1   |                                                        |

| ADuM5240                                            |                                     |                         |       | 1.6          | mA    |                                                        |

| ADuM5241                                            |                                     |                         |       | 3.1          | mA    |                                                        |

| ADum5242                                            |                                     |                         |       | 2.5          | mA    | L Olaminaionalformation                                |

| 10 Mbps                                             | I <sub>DD(10)</sub>                 |                         |       |              |       | I <sub>ISO</sub> =0, Logic signal freq.≤5 MHz          |

| Input Supply Current, V <sub>DD</sub> <sup>2</sup>  |                                     |                         |       | - 4          |       |                                                        |

| ADuM5240                                            |                                     |                         |       | 6.1          | mA    |                                                        |

| ADuM5241                                            |                                     |                         |       | 5.0          | mA    |                                                        |

| ADum5242                                            |                                     |                         |       | 4.0          | mA    |                                                        |

| Input Supply Current, V <sub>ISO</sub> <sup>2</sup> |                                     |                         |       |              |       |                                                        |

| ADuM5240                                            |                                     |                         |       | 3.8          | mA    |                                                        |

| ADuM5241                                            |                                     |                         |       | 5.0          | mA    |                                                        |

| ADuM5242                                            |                                     |                         |       | 6.2          | mA    |                                                        |

| Enable Threshold <sup>4</sup>                       | V <sub>ENABLE</sub>                 |                         |       | 4.5          | V     |                                                        |

| Disable Threshold⁴                                  | $V_{DISABLE}$                       | 4.0                     |       | 4.5          | V     |                                                        |

| Input Currents                                      | I <sub>IA</sub> , I <sub>IB</sub>   | -10                     | +0.01 | +10          | μΑ    |                                                        |

| Logic High Input Threshold                          | V <sub>IH</sub>                     |                         |       | $0.7V_{ISO}$ | V     |                                                        |

| Logic Low Input Threshold                           | VIL                                 | 0.3 V <sub>ISO</sub>    |       |              | V     |                                                        |

| Logic High Output Voltages                          | V <sub>OAH</sub> , V <sub>OBH</sub> | $V_{DD}$ , $-0.1$       | 5.0   |              | V     | $I_{Ox} = -20 \mu A, V_{Ix} = V_{IxH}$                 |

|                                                     | ,                                   | V <sub>DD</sub> , – 0.5 | 4.8   |              | V     | $I_{0x} = -4 \text{ mA}, V_{lx} = V_{lxH}$             |

| Logic Low Output Voltages                           | V <sub>OAL</sub> , V <sub>OBL</sub> |                         | 0.0   | 0.1          | V     | $I_{Ox} = 20 \mu A$ , $V_{Ix} = V_{IxL}$               |

|                                                     | - OAL) • OBL                        |                         | 0.0   | 0.4          | v     | 1                                                      |

|                                                     |                                     |                         | ()()  | 0.4          | 1 V   | $I_{Ox} = 4 \text{ mA}, V_{Ix} = V_{IxL}$              |

# **Preliminary Technical Data**

# ADuM5240/ADuM5241/ADuM5242

| Parameter                                                                   | Symbol                              | Min | Тур | Max | Unit       | Test Conditions                                                                         |

|-----------------------------------------------------------------------------|-------------------------------------|-----|-----|-----|------------|-----------------------------------------------------------------------------------------|

| AC SPECIFICATIONS                                                           |                                     |     |     |     |            |                                                                                         |

| Minimum Pulse Width⁵                                                        | PW                                  |     |     | 100 | ns         | $C_L = 15 \text{ pF, CMOS signal levels}$                                               |

| Maximum Data Rate <sup>6</sup>                                              |                                     | 10  |     |     | Mbps       | $C_L = 15 \text{ pF, CMOS signal levels}$                                               |

| Propagation Delay <sup>7</sup>                                              | t <sub>PHL</sub> , t <sub>PLH</sub> | 25  |     | 70  | ns         | $C_L = 15 \text{ pF, CMOS signal levels}$                                               |

| Pulse-Width Distortion, $ t_{PLH} - t_{PHL} ^7$                             | PWD                                 |     |     | 3   | ns         | $C_L = 15 \text{ pF, CMOS signal levels}$                                               |

| Propagation Delay Skew <sup>8</sup>                                         | <b>t</b> <sub>PSK</sub>             |     |     | 45  | ns         | $C_L = 15 \text{ pF, CMOS signal levels}$                                               |

| Channel-to-Channel Matching,<br>Codirectional Channels <sup>9</sup>         | t <sub>PSKCD</sub>                  |     |     | 3   | ns         | C <sub>L</sub> = 15 pF, CMOS signal levels                                              |

| Channel-to-Channel Matching,<br>Opposing-Directional Channels <sup>10</sup> | <b>t</b> PSKCD                      |     |     | 15  | ns         | C <sub>L</sub> = 15 pF, CMOS signal levels                                              |

| Ripple <sup>11</sup>                                                        |                                     |     | 200 |     | $mV_{P-P}$ |                                                                                         |

| Enable Time <sup>12</sup>                                                   | T <sub>ENABLE</sub>                 |     | 50  |     | ns         |                                                                                         |

| Disable Time <sup>12</sup>                                                  | T <sub>DISABLE</sub>                |     | 50  |     | ns         |                                                                                         |

| Output Rise/Fall Time (10% to 90%)                                          | t <sub>R</sub> /t <sub>F</sub>      |     | 2.5 |     | ns         | $C_L = 15$ pF, CMOS signal levels                                                       |

| Common-Mode Transient Immunity<br>at Logic High Output                      | [СМн]                               | 25  | 35  |     | kV/μs      | $V_{Ix} = V_{DD}$ , $V_{ISO}$ , $V_{CM} = 1000 \text{ V}$ , transient magnitude = 800 V |

| Common-Mode Transient Immunity<br>at Logic Low Output                       | CM <sub>L</sub>                     | 25  | 35  |     | kV/μs      | $V_{lx} = 0 \text{ V}, V = 1000 \text{ V},$<br>transient magnitude = 800 V              |

| Refresh Frequency                                                           | f <sub>r</sub>                      |     | 1.0 |     | MHz        |                                                                                         |

#### **PACKAGE CHARACTERISTICS**

Table 2.

| Parameter                             | Symbol           | Min Typ          | Max | Unit | Test Conditions |

|---------------------------------------|------------------|------------------|-----|------|-----------------|

| Resistance (Input-Output)             | R <sub>I-O</sub> | 10 <sup>12</sup> |     | Ω    |                 |

| Capacitance (Input-Output)            | C <sub>I-O</sub> | 1.0              |     | рF   | f = 1 MHz       |

| Input Capacitance                     | Cı               | 4.0              |     | рF   |                 |

| IC Junction-to-Air Thermal Resistance | θја              | 150              |     | °C/W |                 |

<sup>&</sup>lt;sup>1</sup> All voltages are relative to their respective ground.

<sup>&</sup>lt;sup>2</sup> Supply current values are specified with no load present on the digital outputs.

<sup>&</sup>lt;sup>3</sup> Supply current values are specified with no load present on the digital outputs.

<sup>&</sup>lt;sup>4</sup> Enable/disable threshold is the voltage at which the internal DC/DC converter is enabled/disabled.

<sup>&</sup>lt;sup>5</sup> The minimum pulse width is the shortest pulse width at which the specified pulse-width distortion is guaranteed.

<sup>&</sup>lt;sup>6</sup> The maximum data rate is the fastest data rate at which the specified pulse-width distortion is guaranteed.

<sup>7</sup> t<sub>PHL</sub> propagation delay is measured from the 50% level of the falling edge of the V<sub>Ix</sub> signal to the 50% level of the falling edge of the V<sub>Ox</sub> signal. t<sub>PLH</sub> propagation delay is measured from the 50% level of the rising edge of the V<sub>Ix</sub> signal to the 50% level of the V<sub>Ox</sub> signal.

<sup>8</sup> t<sub>PSK</sub> is the magnitude of the worst-case difference in t<sub>PHL</sub> and/or t<sub>PLH</sub> that is measured between units at the same operating temperature, supply voltages, and output load within the recommended operating conditions.

<sup>&</sup>lt;sup>9</sup> Channel-to-channel matching is the absolute value of the difference in propagation delays between the two channels when operated with identical loads.

<sup>&</sup>lt;sup>10</sup> Channel-to-channel matching is the absolute value of the difference in propagation delays between the two channels when operated with identical loads.

<sup>&</sup>quot;Ripple occurs at frequency corresponding to the input signal data rate or the refresh frequency for data rates below 1Mbps.

<sup>&</sup>lt;sup>12</sup> Enable time is the duration from when input supply voltage rises above the enable threshold to when the internal DC/DC converter starts charging an external load.

Disable time is the duration from when the input supply voltage drops below the disable threshold to when the internal DC/DC converter stops charging an external load.

#### **REGULATORY INFORMATION**

The ADuM5240/5241/5242 will be approved by the following organizations upon product release:

| UL (pending)                                                                                                            | CSA (pending)                                                                                                                                                      | VDE (pending)                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Recognized under 1577 Component<br>Recognition Program <sup>1</sup><br>Basic insulation, 2500 V rms isolation<br>rating | Approved under CSA Component<br>Acceptance Notice #5A<br>Basic insulation per CSA 60950-1-03<br>and IEC 60950-1, 300 V rms (425 V<br>peak) maximum working voltage | Certified according to DIN EN 60747-5-2 (VDE 0884 Part 2):2003-01 <sup>2</sup> Basic insulation,300 V rms (425 V peak) maximum working voltage |

| File E214100                                                                                                            | File 205078                                                                                                                                                        | File 2471900-4880-0001                                                                                                                         |

$<sup>^{1}</sup>$  In accordance with UL1577, each ADuM524x is proof-tested by applying an insulation test voltage ≥ 3000 V rms for 1 second (current leakage detection limit = 5  $\mu$ A).  $^{2}$  In accordance with DIN EN 60747-5-2, each ADuM524x is proof-tested by applying an insulation test voltage ≥ 1050 V peak for 1 second (partial discharge detection

#### **INSULATION AND SAFETY-RELATED SPECIFICATIONS**

#### Table 4.

| Parameter                                        | Symbol | Value     | Unit  | Conditions                                                                           |

|--------------------------------------------------|--------|-----------|-------|--------------------------------------------------------------------------------------|

| Rated Dielectric Insulation Voltage              |        | 2500      | V rms | 1 minute duration                                                                    |

| Minimum External Air Gap (Clearance)             | L(I01) | 4.90 min  | mm    | Measured from input terminals to output terminals, shortest distance through air     |

| Minimum External Tracking (Creepage)             | L(102) | 4.01 min  | mm    | Measured from input terminals to output terminals, shortest distance path along body |

| Minimum Internal Gap (Internal<br>Clearance)     |        | 0.017 min | mm    | Insulation distance through insulation                                               |

| Tracking Resistance (Comparative Tracking Index) | СТІ    | >175      | V     | DIN IEC 112/VDE 0303 Part 1                                                          |

| Isolation Group                                  |        | Illa      |       | Material Group (DIN VDE 0110, 1/89, Table 1)                                         |

limit = 5 pC).

#### DIN EN 60747-5-2 (VDE 0884 PART 2) INSULATION CHARACTERISTICS

Table 5.

| Description                                                                                                             | Symbol          | Characteristic | Unit   |

|-------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|--------|

| Installation Classification per DIN VDE 0110                                                                            |                 |                |        |

| For Rated Mains Voltage ≤ 150 V rms                                                                                     |                 | I–IV           |        |

| For Rated Mains Voltage ≤ 300 V rms                                                                                     |                 | I–III          |        |

| Climatic Classification                                                                                                 |                 | 40/105/21      |        |

| Pollution Degree (DIN VDE 0110, Table 1)                                                                                |                 | 2              |        |

| Maximum Working Insulation Voltage                                                                                      | VIORM           | 425            | V peak |

| Input to Output Test Voltage, Method b1                                                                                 | $V_{PR}$        | 797            | V peak |

| $V_{IORM} \times 1.875 = V_{PR}$ , 100% Production Test, $t_m = 1$ sec, Partial Discharge $< 5$ pC                      |                 |                |        |

| Input to Output Test Voltage, Method a                                                                                  | $V_{PR}$        |                |        |

| After Environmental Tests Subgroup 1                                                                                    |                 |                |        |

| $V_{IORM} \times 1.6 = V_{PR}$ , $t_m = 60$ sec, Partial Discharge $< 5$ pC                                             |                 | 680            | V peak |

| After Input and/or Safety Test Subgroup 2/3                                                                             |                 |                |        |

| $V_{IORM} \times 1.2 = V_{PR}$ , $t_m = 60$ sec, Partial Discharge $< 5$ pC                                             |                 | 510            | V peak |

| Highest Allowable Overvoltage (Transient Overvoltage, t <sub>TR</sub> = 10 sec)                                         | $V_{TR}$        | 4000           | V peak |

| Safety-Limiting Values (maximum value allowed in the event of a failure; also see the thermal derating curve, Figure 4) |                 |                |        |

| Case Temperature                                                                                                        | Ts              | 150            | °C     |

| Side 1 Current                                                                                                          | I <sub>S1</sub> | 160            | mA     |

| Side 2 Current                                                                                                          | I <sub>S2</sub> | 170            | mA     |

| Insulation Resistance at $T_s$ , $V_{10} = 500 \text{ V}$                                                               | Rs              | >109           | Ω      |

Note that the "\*" marking on the package denotes DIN EN 60747-5-2 approval for a 425 V peak working voltage.

This isolator is suitable for basic isolation only within the safety limit data. Maintenance of the safety data is ensured by protective circuits.

#### [Figure to be added]

# Figure 4. Thermal Derating Curve, Dependence of Safety Limiting Values on Case Temperature, per DIN EN 60747-5-2

#### **RECOMMENDED OPERATING CONDITIONS**

Table 6.

| Parameter                               | Symbol           | Min | Max  | Unit |

|-----------------------------------------|------------------|-----|------|------|

| Operating Temperature                   | T <sub>A</sub>   | -40 | +105 | °C   |

| Supply Voltages <sup>1</sup>            |                  |     |      |      |

| V <sub>DD</sub> , DC/DC Conv. Enabled   | $V_{DD}$         | 4.5 | 5.5  | V    |

| V <sub>DD</sub> , DC/DC Conv. Disabled  | $V_{\text{DD}}$  | 2.7 | 4.0  | V    |

| V <sub>ISO</sub> , DC/DC Conv. Disabled | V <sub>ISO</sub> | 2.7 | 5.5  | V    |

| Input Signal Rise and Fall Times        |                  |     | 1.0  | ms   |

| Input Supply Slew Rate                  |                  |     | 10   | V/ms |

<sup>&</sup>lt;sup>1</sup> All voltages are relative to their respective ground.

## **ABSOLUTE MAXIMUM RATINGS**

Ambient temperature = 25°C, unless otherwise noted.

Table 7.

| Parameter                                    | Symbol                             | Min  | Max                       | Unit  |

|----------------------------------------------|------------------------------------|------|---------------------------|-------|

| Storage Temperature                          | T <sub>ST</sub>                    | -55  | 150                       | °C    |

| Ambient Operating Temperature                | T <sub>A</sub>                     | -40  | 105                       | °C    |

| Supply Voltages <sup>1</sup>                 | V <sub>DD</sub> , V <sub>ISO</sub> | -0.5 | 7.0                       | V     |

| Input Voltage <sup>1</sup>                   | V <sub>IA</sub> , V <sub>IB</sub>  | -0.5 | $V_{\text{DD/ISO}} + 0.5$ | V     |

| Output Voltage <sup>1</sup>                  | V <sub>OA</sub> , V <sub>OB</sub>  | -0.5 | $V_{\text{DD/ISO}} + 0.5$ | V     |

| Average Output Current, per Pin <sup>2</sup> | Io                                 |      |                           | mA    |

| Common-Mode Transients <sup>3</sup>          |                                    | -100 | +100                      | kV/μs |

<sup>&</sup>lt;sup>1</sup> All voltages are relative to their respective ground.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; Functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

Table 8. Truth Table, ADuM5240

| V <sub>DD</sub> State | DC/DC<br>Converter | V <sub>ISO</sub> State  | V <sub>IA</sub><br>Input | V <sub>IB</sub><br>Input | V <sub>OA</sub><br>Output | V <sub>OB</sub><br>Output |

|-----------------------|--------------------|-------------------------|--------------------------|--------------------------|---------------------------|---------------------------|

| Powered               | Enabled            | Powered<br>(Internally) | Н                        | Н                        | Н                         | Н                         |

| Powered               | Enabled            | Powered<br>(Internally) | L                        | L                        | L                         | L                         |

| Powered               | Enabled            | Powered<br>(Internally) | Н                        | L                        | Н                         | L                         |

| Powered               | Enabled            | Powered<br>(Internally) | L                        | Н                        | L                         | Н                         |

| Powered               | Disabled           | Powered<br>(Externally) | Н                        | Н                        | Н                         | Н                         |

| Powered               | Disabled           | Powered<br>(Externally) | L                        | L                        | L                         | L                         |

| Powered               | Disabled           | Powered<br>(Externally) | Н                        | L                        | Н                         | L                         |

| Powered               | Disabled           | Powered<br>(Externally) | L                        | Н                        | L                         | Н                         |

| Powered               | Disabled           | Unpowered               | Χ                        | Χ                        | Z                         | Z                         |

| Unpowered             | Disabled           | Powered<br>(Externally) | X                        | Х                        | L                         | L                         |

| Unpowered             | Disabled           | Unpowered               | Χ                        | Χ                        | Z                         | Z                         |

<sup>&</sup>lt;sup>2</sup> See Figure 4 for maximum rated current values for various temperatures.

<sup>&</sup>lt;sup>3</sup> Refers to common-mode transients across the insulation barrier. Common-mode transients exceeding the Absolute Maximum Rating may cause latch-up or permanent damage.

Table 9. Truth Table, ADuM5241

| V <sub>DD</sub> State | DC/DC<br>Converter | V <sub>ISO</sub> State  | V <sub>IA</sub><br>Input | V <sub>IB</sub> | V <sub>OA</sub><br>Output | V <sub>OB</sub><br>Output |

|-----------------------|--------------------|-------------------------|--------------------------|-----------------|---------------------------|---------------------------|

| Powered               | Enabled            | Powered<br>(Internally) | Н                        | Н               | Н                         | Н                         |

| Powered               | Enabled            | Powered<br>(Internally) | L                        | L               | L                         | L                         |

| Powered               | Enabled            | Powered<br>(Internally) | Н                        | L               | Н                         | L                         |

| Powered               | Enabled            | Powered<br>(Internally) | L                        | Н               | L                         | Н                         |

| Powered               | Disabled           | Powered<br>(Externally) | Н                        | Н               | Н                         | Н                         |

| Powered               | Disabled           | Powered<br>(Externally) | L                        | L               | L                         | L                         |

| Powered               | Disabled           | Powered<br>(Externally) | Н                        | L               | Н                         | L                         |

| Powered               | Disabled           | Powered<br>(Externally) | L                        | Н               | L                         | Н                         |

| Powered               | Disabled           | Unpowered               | Χ                        | Х               | L                         | Z                         |

| Unpowered             | Disabled           | Powered<br>(Externally) | X                        | Х               | Z                         | L                         |

| Unpowered             | Disabled           | Unpowered               | Χ                        | Х               | Z                         | Z                         |

Table 10. Truth Table, ADuM5242

| V <sub>DD</sub> State | DC/DC<br>Converter | V <sub>ISO</sub> State  | V <sub>IA</sub><br>Input | V <sub>IB</sub><br>Input | V <sub>OA</sub><br>Output | V <sub>OB</sub><br>Output |

|-----------------------|--------------------|-------------------------|--------------------------|--------------------------|---------------------------|---------------------------|

| Powered               | Enabled            | Powered<br>(Internally) | Н                        | Н                        | Н                         | Н                         |

| Powered               | Enabled            | Powered<br>(Internally) | L                        | L                        | L                         | L                         |

| Powered               | Enabled            | Powered<br>(Internally) | Н                        | L                        | Н                         | L                         |

| Powered               | Enabled            | Powered<br>(Internally) | L                        | Н                        | L                         | Н                         |

| Powered               | Disabled           | Powered<br>(Externally) | Н                        | Н                        | Н                         | Н                         |

| Powered               | Disabled           | Powered<br>(Externally) | L                        | L                        | L                         | L                         |

| Powered               | Disabled           | Powered<br>(Externally) | Н                        | L                        | Н                         | L                         |

| Powered               | Disabled           | Powered<br>(Externally) | L                        | Н                        | L                         | Н                         |

| Powered               | Disabled           | Unpowered               | Х                        | Χ                        | L                         | L                         |

| Unpowered             | Disabled           | Powered<br>(Externally) | Х                        | Х                        | Z                         | Z                         |

| Unpowered             | Disabled           | Unpowered               | Χ                        | Χ                        | Z                         | Z                         |

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 5. ADuM5240 Pin Configuration

Figure 6. ADuM5241 Pin Configuration

Figure 7. ADuM5242 Pin Configuration

Table 11. ADuM5240 Pin Function Descriptions

| Pin<br>No. | Mnemonic           | Function                                                                                                                  |

|------------|--------------------|---------------------------------------------------------------------------------------------------------------------------|

| 1          | V <sub>DD1</sub>   | Supply Voltage for Isolator Side 1,<br>4.5 V to 5.5 V (DC/DC Enabled), 2.7 V to 4.0<br>V (DC/DC Disabled)                 |

| 2          | VIA                | Logic Input A.                                                                                                            |

| 3          | V <sub>IB</sub>    | Logic Input B.                                                                                                            |

| 4          | GND                | Ground. Ground reference for Isolator<br>Side 1.                                                                          |

| 5          | GND <sub>ISO</sub> | Isolated Ground. Ground reference for Isolator Side 2.                                                                    |

| 6          | V <sub>OB</sub>    | Logic Output B.                                                                                                           |

| 7          | V <sub>OA</sub>    | Logic Output A.                                                                                                           |

| 8          | V <sub>ISO</sub>   | Isolated Supply Voltage for Isolator Side 2, 5.0 V to 5.5 V Output (DC/DC Enabled), 4.5 V to 5.5 V Input (DC/DC Disabled) |

Table 13. ADuM5242 Pin Function Descriptions

Pin

| Pin<br>No. | Mnemonic           | Function                                                                                                                  |

|------------|--------------------|---------------------------------------------------------------------------------------------------------------------------|

| 1          | V <sub>DD1</sub>   | Supply Voltage for Isolator Side 1,<br>4.5 V to 5.5 V (DC/DC Enabled), 2.7 V to 4.0<br>V (DC/DC Disabled)                 |

| 2          | V <sub>OA</sub>    | Logic Output A.                                                                                                           |

| 3          | V <sub>OB</sub>    | Logic Output B.                                                                                                           |

| 4          | GND                | Ground. Ground reference for Isolator Side 1.                                                                             |

| 5          | GND <sub>ISO</sub> | Isolated Ground. Ground reference for Isolator Side 2.                                                                    |

| 6          | V <sub>IB</sub>    | Logic Input B.                                                                                                            |

| 7          | VIA                | Logic Input A.                                                                                                            |

| 8          | V <sub>ISO</sub>   | Isolated Supply Voltage for Isolator Side 2, 5.0 V to 5.5 V Output (DC/DC Enabled), 4.5 V to 5.5 V Input (DC/DC Disabled) |

Table 12. ADuM5241 Pin Function Descriptions

| Pin<br>No. | Mnemonic           | Function                                                                                                                        |

|------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 1          | V <sub>DD1</sub>   | Supply Voltage for Isolator Side 1,<br>4.5 V to 5.5 V (DC/DC Enabled), 2.7 V to 4.0<br>V (DC/DC Disabled)                       |

| 2          | Voa                | Logic Output A.                                                                                                                 |

| 3          | V <sub>IB</sub>    | Logic Input B.                                                                                                                  |

| 4          | GND                | Ground. Ground reference for Isolator Side 1.                                                                                   |

| 5          | GND <sub>ISO</sub> | Isolated Ground. Ground reference for Isolator Side 2.                                                                          |

| 6          | V <sub>OB</sub>    | Logic Output B.                                                                                                                 |

| 7          | V <sub>IA</sub>    | Logic Input A.                                                                                                                  |

| 8          | V <sub>ISO</sub>   | Isolated Supply Voltage for Isolator Side 2,<br>5.0 V to 5.5 V Output (DC/DC Enabled), 4.5<br>V to 5.5 V Input (DC/DC Disabled) |

## APPLICATION INFORMATION

#### DC/DC CONVERTER

The ADuM524x can be operated with the internal DC/DC enabled or disabled. With the internal DC/DC converter enabled, the Pin 8 isolated supply provides output power as well as power to the part's isolated-side circuitry. Since the power consumed by the ADuM524x is a function of the input signals' data rate, the available isolated output power is determined by the data rate at which the part's data channels are operating.

The ADuM524x's internal DC/DC converter state is controlled by the input  $V_{\rm DD}$  voltage as defined in Table 6. In normal operating mode,  $V_{\rm DD}$  is set between 4.5 V and 5.5 V and the internal DC/DC converter is enabled. When/if it is desired to disable the DC/DC converter,  $V_{\rm DD}$  is lowered to a value between 2.7 V and 4.0 V. In this mode, the  $V_{\rm ISO}$  supply is supplied by the user and the ADuM524x's signal channels continue to operate normally.

#### **GUIDELINES FOR PRE-PRODUCTION SAMPLES**

Pre production samples meet all data sheet specifications; however, a limitation in the internal circuitry of the ADuM524x prevents proper start-up under all load conditions. This limitation will be corrected in the final product.

At certain temperature and load conditions the ADuM524x will not regulate its  $V_{\rm ISO}$  output to the 5.25V target voltage at converter start-up. The output stabilizes at just under 4V with no external load or as low as 3V with an external load. If the converter starts successfully, the output voltage will continue to regulate properly even as temperature and load conditions change.

The start-up issue is affected by several circuit and environmental conditions: slew rate applied to  $V_{\rm DD1}$ , ambient temperature, and  $V_{\rm ISO}$  capacitive load. The recommendations in the PC board layout section address the  $V_{\rm DD1}$  slew rate dependence in most cases. Good results have been obtained when the system power supply slews at  ${\sim}0.5 V/\mu S$ . Faster slew rates can be tolerated but should be verified over temperature. Table 14 contains guidelines for the maximum reliable start-up temperature for two common values of load capacitance.

The  $V_{\rm ISO}$  start-up issue is strongly temperature dependant. The ADuM542x dissipates between 40 and 63mW under normal operation, causing the internal temperature of the device to be higher than ambient during normal operation. A "warm start" after the device has reached its equilibrium temperature is the worst case condition and will give the highest probability of incorrect regulation of output voltage. The guidelines in Table 14 are based on "warm start" at full load. Cold start will be successful at higher ambient temperatures.

When these guidelines are followed, pre-production samples may be used for prototype and evaluation. As mentioned above this issue will be corrected in final silicon and the ADuM524x will operate at specified load and temperature conditions.

**Table 14. Special Usage Conditions for Pre-production Devices**

Max Temperature by Load Capacitance<sup>1</sup>

|          | 10nF  | 100nF           |

|----------|-------|-----------------|

| ADuM5240 | 105°C | Not Recommended |

| ADuM5241 | 105°C | 65°C            |

| ADuM5242 | 80°C  | 80°C            |

<sup>&</sup>lt;sup>1</sup> Value of load capacitor C3 in Figure 8

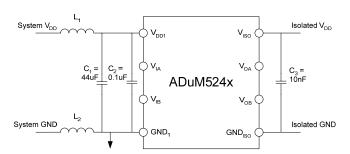

#### PC BOARD LAYOUT

The ADuM524x digital isolators require no external interface circuitry for the logic interfaces. Power supply bypassing is strongly recommended at the input and output supply pins as shown in Figure 8. For the ADuM5240 and ADuM5241, a bypass capacitance ( $C_1$ ) of 44  $\mu F$  is required at the  $V_{DD}$  input to ensure proper power-up. For all models bypass capacitance is recommended with  $C_2$ =0.1  $\mu F$  on the non-isolated side and  $C_3$ =10 nF on the isolated side. Due to high inductance associated with larger capacitors such as  $C_1$ , it is recommended that both  $C_1$  and  $C_2$  be used on the ADuM5240 and ADuM5241. The bypass capacitors should be placed as close as possible to the ADuM524x device.

In cases where EMI is a concern, inductance should be added between the system supply and ground and the ADuM524x supply and ground as shown in Figure 8. Inductance can be added in the form of discrete inductors or ferrite beads, and it's recommended the value correspond to an impedance between  $50\Omega$  and  $100\Omega$  at approximately  $300 \rm MHz$ .

Figure 8. Recommended Application Circuit.  $C_1$  may be omitted for ADuM5242, and  $L_1$  and  $L_2$  should be included where EMI is a concern.

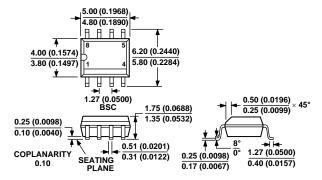

# **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MS-012AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

Figure 9. 8-Lead Standard Small Outline Package [SOIC]—Narrow Body (R-8)

Dimensions shown in millimeters (inches)

#### **ORDERING GUIDE**

| Model                       | Number<br>of Inputs,<br>V <sub>DD1</sub> Side | Number of Inputs, VDD2 Side | Maximum<br>Data Rate<br>(Mbps) | Temperature<br>Range (°C) | Package<br>Option <sup>1</sup> |

|-----------------------------|-----------------------------------------------|-----------------------------|--------------------------------|---------------------------|--------------------------------|

| ADuM5240BRZ <sup>2,3</sup>  | 2                                             | 0                           | 10                             | -40 to +105               | R-8                            |

| ADuM5241BRZ <sup>2,3</sup>  | 1                                             | 1                           | 10                             | -40 to +105               | R-8                            |

| ADuM5242BRZ <sup>2, 3</sup> | 0                                             | 2                           | 10                             | -40 to +105               | R-8                            |

<sup>&</sup>lt;sup>1</sup> R-8 = 8-lead narrow body SOIC.

<sup>&</sup>lt;sup>2</sup> Tape and reel are available. The addition of an "-RL7" suffix designates a 7" (1,000 units) tape and reel option.

$<sup>^{3}</sup>$  Z = Pb-free part.