# AC Vector Processor

AD2S100

#### **FEATURES**

Complete Vector Coordinate Transformation on Silicon Mixed Signal Data Acquisition Three-Phase 120° and Orthogonal 90° Signal Transformation Three-Phase Balance Diagnostic-Homopolar Output

## APPLICATIONS

APPLICATIONS AC Induction and DC Permanent Magnet Motor Control HVAC, Pump, Fan Control Material Handling Robotics Spindle Drives Gyroscopes Dryers Washing Machines Electric Cars Actuator Three-Phase Power Measurement Digital-to-Resolver & Synchro Conversion

### **GENERAL DESCRIPTION**

The AD2S100 performs the vector rotation of three-phase 120 degree or two-phase 90 degree sine and cosine signals by transferring these inputs into a new reference frame which is controlled by the digital input angle  $\phi$ . Two transforms are included in the AD2S100. The first is the Clarke transform which computes the sine and cosine orthogonal components of a three-phase input. These signals represent real and imaginary components which then form the input to the Park transform. The Park transform relates the angle of the input signals to a reference frame controlled by the digital input port. The digital input port is a 12-bit parallel binary representation.

If the input signals are represented by Vds and Vqs, respectively, where Vds and Vqs are the real and imaginary components, then the transformation can be described as follows:

Vds' = Vds Cos\u03c6 - Vqs Sin\u03c6 Vqs' = Vds Sin\u03c6 + Vqs Cos\u03c6

Where Vds' and Vqs' are the output of the Park transform and Sin $\phi$ , and Cos $\phi$  are the values internally derived by the AD2S100 from the binary digital data.

The input section of the device can be configured to accept either three-phase inputs, two-phase inputs of a three-phase system, or two 90 degree input signals. The homopolar output detects the imbalance of a three-phase input only. Under normal conditions, this output will be zero.

### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

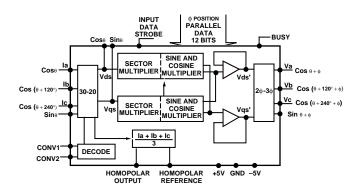

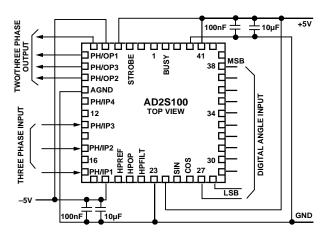

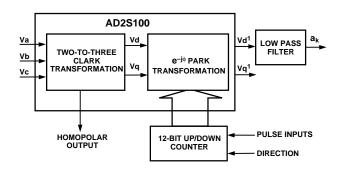

### FUNCTIONAL BLOCK DIAGRAM

The digital input section will accept a resolution of up to 12 bits (AD2S100). An input data strobe signal is required to synchronize the position data and load this information into the device counters. A busy output is provided to identify the conversion status of the AD2S100. The busy period represents the conversion time of the vector rotation.

Two analog output formats are available. A two-phase rotated output facilitates multiple rotation blocks. Three phase format signals are available for use with a PWM inverter.

## **PRODUCT HIGHLIGHTS**

## Hardware Peripheral for Standard Microcontrollers and DSP Systems

The AD2S100 removes the time consuming cartesian transformations from digital processors and benchmarks a speed improvement of 30:1 on standard 20 MHz processors. AD2S100 transformation time =  $2 \mu s$  (typ).

## Field Oriented Control of AC and DC Brushless Motors

The AD2S100 accommodates all the necessary functions to provide a hardware solution for ac vector control of induction motors and dc brushless motors.

#### **Three-Phase Imbalance Detection**

The AD2S100 can be used to sense overcurrent situations or imbalances in a three-phase system via the homopolar output.

#### **Resolver-to-Digital Converter Interface**

The AD2S100 provides general purpose interface for position sensors used in the application of dc brushless and ac induction motor control.

# **AD2S100—SPECIFICATIONS** ( $V_{DD} = +5 V \pm 5\%$ ; $V_{SS} = -5 V \pm 5\%$ AGND = DGND = 0 V; $T_A = -40^{\circ}$ C to +85°C, unless otherwise noted)

| Parameter                                                                                                                                | Min             | Тур                      | Max                  | Units                     | Conditions                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------|----------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIGNAL INPUTS<br>PH/IP1, 2, 3, 4 Voltage Level<br>PH/IPH1, 2, 3 Voltage Level<br>Input Impedance                                         |                 | ±2.8                     | <b>±3.3</b><br>±4.25 | V p-p<br>V p-p            | DC to 50 kHz<br>DC to 50 kHz                                                                                                                                                            |

| PH/IP1, 2, 3<br>PH/IPH1, 2, 3                                                                                                            | 7.5<br>13.5     | 10<br>18                 |                      | kΩ<br>kΩ                  |                                                                                                                                                                                         |

| PH/IP1, 4<br>Gain                                                                                                                        | 1               |                          |                      | ΜΩ                        | Mode 1 Only (2 Phase) Sin & Cos                                                                                                                                                         |

| PH/IP1, 2, 3, 4<br>PH/IPH1, 2, 3                                                                                                         | 0.98            | 1<br>0.56                | 1.02                 |                           |                                                                                                                                                                                         |

| VECTOR PERFORMANCE<br>3θ Input-Output<br>Radius Error (Any Phase)<br>Angular Error <sup>1, 2</sup> (PH/IP)<br>(PH/IPH)                   |                 | 0.35<br>9                | 0.7<br>18<br>24      | %<br>arc min<br>arc min   | DC to 600 Hz<br>DC to 600 Hz<br>DC to 600 Hz                                                                                                                                            |

| Monotonicity<br>Full Power Bandwidth<br>Small Signal Bandwidth                                                                           |                 | 50<br>200                |                      | kHz<br>kHz                | Guaranteed Monotonic                                                                                                                                                                    |

| ANALOG SIGNAL OUTPUTS<br>PH/OP1, 2, 3, 4<br>Output Voltage <sup>3</sup><br>Offset Voltage<br>Slew Rate<br>Small Signal Step Response     |                 | $^{\pm 2.8}_{2}_{2}_{1}$ | ±3.3<br>5            | V p-p<br>mV<br>V/μs<br>μs | PH/IP, PH/IPH INPUTS<br>DC to 50 kHz<br>Inputs = 0 V<br>$1^{\circ}$ Input to Settle to ±1 LSB                                                                                           |

| Output Resistance<br>Output Drive Current<br>Resistive Load                                                                              | <b>3.0</b><br>2 | 15<br>4.0                |                      | Ω<br>mA<br>kΩ             | (Input to Output)<br>Outputs to AGND                                                                                                                                                    |

| Capacitive Load<br>STROBE<br>Write                                                                                                       | 100             | 50                       |                      | pF<br>ns                  | Positive Pulse                                                                                                                                                                          |

| Max Update Rate                                                                                                                          |                 | 366                      |                      | kHz                       |                                                                                                                                                                                         |

| BUSY<br>Pulse Width<br>V <sub>OH</sub><br>V <sub>OL</sub>                                                                                | 4               | 1.7                      | 2.5<br>1             | μs<br>V dc<br>V dc        | Conversion in Process<br>$I_{OH} = 0.5 \text{ mA}$<br>$I_{OL} = 0.5 \text{ mA}$                                                                                                         |

| DIGITAL INPUTS<br>DB1–DB12<br>V <sub>IH</sub><br>V <sub>IL</sub><br>Input Current, I <sub>IN</sub><br>Input Capacitance, C <sub>IN</sub> | 3.5             | 10                       | 1.5<br>±10           | V dc<br>V dc<br>μΑ<br>pF  |                                                                                                                                                                                         |

| CONVERT MODE<br>(CONV1, CONV2)<br>V <sub>IH</sub><br>V <sub>IL</sub><br>Input Current<br>Input Capacitance                               | 3.5             | 10                       | 1.5<br>100           | V dc<br>V dc<br>μA<br>pF  | Internal 50 kΩ Pull-Up Resistor                                                                                                                                                         |

| CONVERT LOGIC<br><u>CONV1</u> CONV2<br>NO CONNECT DGND<br>DGND V <sub>DD</sub><br>V <sub>DD</sub> V <sub>DD</sub>                        |                 |                          |                      |                           | 2-Phase Orthogonal with 2 Inputs<br>Nominal Input Level<br>3-Phase (0°, 120°, 240°) with 3 Input<br>Nominal Input Level<br>3-Phase (0°, 120°, 240°) with 2 Input<br>Nominal Input Level |

| Parameter        | Min   | Тур | Max   | Units | Conditions                                             |

|------------------|-------|-----|-------|-------|--------------------------------------------------------|

| HOMOPOLAR OUTPUT |       |     |       |       |                                                        |

| HPOP–Output      |       |     |       |       |                                                        |

| V <sub>OH</sub>  | 4     |     |       | V dc  | $I_{OH} = 0.5 \text{ mA}$                              |

| V <sub>OL</sub>  |       |     | 1     | V dc  | $I_{OL} = 0.5 \text{ mA}$                              |

| HPREF-REFERENCE  |       | 0.5 |       | V dc  | Homopolar Output-Internal                              |

|                  |       |     |       |       | $I_{\text{SOURCE}} = 25 \mu\text{A}$ and 20 k $\Omega$ |

|                  |       |     |       |       | to AGND                                                |

| HPFILT-FILTER    |       | 100 |       | kΩ    | Internal Resistor with External                        |

|                  |       |     |       |       | Capacitor = 220 nF                                     |

| POWER SUPPLY     |       |     |       |       |                                                        |

| V <sub>DD</sub>  | 4.75  | 5   | 5.25  | V dc  |                                                        |

| V <sub>SS</sub>  | -5.25 | -5  | -4.75 | V dc  |                                                        |

| I <sub>DD</sub>  |       | 4   | 10    | mA    | Quiescent Current                                      |

| I <sub>SS</sub>  |       | 4   | 10    | mA    | Quiescent Current                                      |

NOTES

<sup>1</sup>Angular accuracy includes offset and gain errors. Stationary digital input and maximum analog frequency inputs.

<sup>2</sup>Included in the angular error is an allowance for the additional error caused by the phase delay as a function of input frequency. For example, if

$f_{INPUT}$  = 600 Hz, the contribution to the error due to phase delay is: 650 ns ×  $f_{INPUT}$  × 60 × 360 = 8.4 arc minutes.

<sup>3</sup>Output subject to input voltage and gain.

Specifications in **boldface** are production tested.

Specifications subject to change without notice.

## **RECOMMENDED OPERATING CONDITIONS**

| Power Supply Voltage $(+V_{DD}, -V_{SS})$ $\pm 5 \text{ V dc} \pm 5\%$ |

|------------------------------------------------------------------------|

| Analog Input Voltage (PH/IP1, 2, 3, 4) $\dots 2$ V rms $\pm 10\%$      |

| Analog Input Voltage (PH/IPH1, 2, 3) 3 V rms ± 10%                     |

| Ambient Operating Temperature Range                                    |

| Industrial (AP)40°C to +85°C                                           |

## **ORDERING GUIDE**

| Model Temperature Ra |                | Accuracy   | Option* |

|----------------------|----------------|------------|---------|

| AD2S100AP            | –40°C to +85°C | 18 arc min | P-44A   |

\*P = Plastic Leaded Chip Carrier.

## **ABSOLUTE MAXIMUM RATINGS** $(T_A = +25^{\circ}C)$

| $V = t_0 \Lambda CND$ 0.3 V to $\pm 7$ V do                                 |

|-----------------------------------------------------------------------------|

| $V_{DD}$ to AGND                                                            |

| $V_{SS}$ to AGND +0.3 V to -7 V dc                                          |

| AGND to DGND±0.3 V dc                                                       |

| Analog Input Voltage to AGND $\dots \dots V_{SS}$ to $V_{DD}$               |

| Digital Input Voltage to DGND $\dots -0.3$ V to V <sub>DD</sub> + 0.3 V dc  |

| Digital Output Voltage to DGND $\dots -0.3$ V to V <sub>DD</sub> + 0.3 V dc |

| Analog Output Voltage to AGND                                               |

| $\dots$ V <sub>SS</sub> – 0.3 V to V <sub>DD</sub> + 0.3 V dc               |

| Analog Output Load Condition (PH/OP1, 2, 3, 4                               |

| Sinθ, Cosθ) 2 kΩ                                                            |

| Power Dissipation                                                           |

| Operating Temperature                                                       |

| Industrial (AP)40°C to +85°C                                                |

| Storage Temperature65°C to +150°C                                           |

| Lead Temperature (Soldering, 10 sec) +300°C                                 |

#### CAUTION

- 1. Absolute Maximum Ratings are those values beyond which damage to the device may occur.

- 2. Correct polarity voltages must be maintained on the +V\_{DD} and -V\_{SS} pins.

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD2S100 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

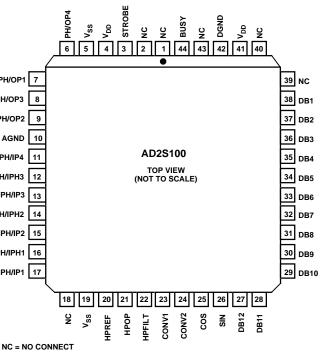

## PIN DESIGNATIONS<sup>1, 2, 3</sup>

| Pin | Mnemonic        | Description                                       |                                                    |

|-----|-----------------|---------------------------------------------------|----------------------------------------------------|

| 3   | STROBE          | Begin Conversion                                  | PH/OP4                                             |

| 4   | V <sub>DD</sub> | Positive Power Supply                             |                                                    |

| 5   | Vss             | Negative Power Supply                             | 6 5                                                |

| 6   | PH/OP4          | $\sin(\theta + \phi)$                             | <del></del>                                        |

| 7   | PH/OP1          | $\cos(\theta + \phi)$                             | PH/OP1 7                                           |

| 8   | PH/OP3          | $\cos(\theta + 240^\circ + \phi)$                 | PH/OP3 8                                           |

| 9   | PH/OP2          | $\cos(\theta + 120^\circ + \phi)$                 | PH/OP2 9                                           |

| 10  | AGND            | Analog Ground                                     |                                                    |

| 11  | PH/IP4          | Sin $\theta$ Input                                | AGND 10                                            |

| 12  | PH/IPH3         | High Level Cos ( $\theta$ + 240°) Input           | PH/IP4 11                                          |

| 13  | PH/IP3          | $\cos(\theta + 240^\circ)$ Input                  | PH/IPH3 12                                         |

| 14  | PH/IPH2         | High Level Cos ( $\theta$ + 120°) Input           |                                                    |

| 15  | PH/IP2          | $\cos(\theta + 120^\circ)$ Input                  | PH/IP3 13                                          |

| 16  | PH/IPH1         | High Level Cos $\theta$ Input                     | PH/IPH2 14                                         |

| 17  | PH/IP1          | Cos (θ) Input                                     | PH/IP2 15                                          |

| 19  | V <sub>SS</sub> | Negative Power Supply                             | PH/IPH1 16                                         |

| 20  | HPREF           | Homopolar Reference                               |                                                    |

| 21  | HPOP            | Homopolar Output                                  | PH/IP1 17                                          |

| 22  | HPFILT          | Homopolar Filter                                  |                                                    |

| 23  | CONV1           | Select Input Format (3 Phase/3 Wire, Sin $\theta$ | 18 19                                              |

| 24  | CONV2           | Cos θ/Input, 3 Phase/2 Wire)                      | <pre>C S S S S S S S S S S S S S S S S S S S</pre> |

| 25  | COS             | Cos Output                                        |                                                    |

| 26  | SIN             | Sin Output                                        | NC = NO CONNECT                                    |

| 27  | DB12            | (DB1 = MSB, DB12 = LSB                            |                                                    |

| 38  | DB1             | Parallel Input Data)                              |                                                    |

| 41  | V <sub>DD</sub> | Positive Power Supply                             |                                                    |

| 42  | DGND            | Digital Ground                                    |                                                    |

| 44  | BUSY            | Conversion in Progress                            |                                                    |

## PIN CONFIGURATION

#### NOTES

Signal Inputs Ph/IP and PH/IPH on Pin Nos 11 through 17.

<sup>1</sup>90° orthogonal signals = Sin  $\theta$ , Cos  $\theta$  (Resolver) = PH/IP4 and PH/IP1.

<sup>2</sup>Three phase, 120°, three-wire signals

=  $\cos \theta$ ,  $\cos (\theta + 120^\circ)$ ,  $\cos (\theta + 240^\circ)$ . = PH/IP1, PH/IP2, PH/IP3

High Level = PH/IPH1, PH/IPH2, PH/IPH3.

<sup>3</sup>Three Phase, 120°, two-wire signals = Cos ( $\theta$  + 120°), Cos ( $\theta$  + 240°) = PH/IP2, PH/IP3.

In all cases where any of the input Pins 11 through 17 are not used, they must be left unconnected.

## THEORY OF OPERATION

A fundamental requirement for high quality induction motor drives is that the magnitude and position of the rotating air-gap rotor flux be known. This is normally carried out by measuring the rotor position via a position sensor and establishing a rotor reference frame that can be related to stator current coordinates.

To generate a flux component in the rotor, stator current is applied. A build-up of rotor flux is concluded which must be maintained by controlling the stator current,  $i_{ds}$ , parallel to the rotor flux. The rotor flux current component is the magnetizing current,  $i_{mr}$ .

Torque is generated by applying a current component which is perpendicular to the magnetizing current. This current is normally called the torque generating current,  $i_{\alpha s}$ .

To orient and control both the torque and flux stator current vectors, a coordinate transformation is carried out to establish a new reference frame related to the rotor. This complex calculation is carried out by the AD2S100 vector processor.

To expand upon the vector operator a description of a single vector rotation is of assistance. If it is considered that the moduli of a vector is OP and that through the movement of rotor position by  $\phi$ , we require the new position of this vector it can be deduced as follows:

Let original vector OP = A (Cos  $\theta$  + jSIN  $\theta$ ) where *A* is a constant;

so if  $OQ = OP e^{i\phi}$  (1)

and:  $e^{j\phi} = \cos \phi + j\sin \phi$

$$OQ = A (Cos (\theta + \phi) + jSin (\theta + \phi))$$

$$= A \left[ Cos \ \theta \ Cos \ \phi - Sin \ \theta \ Sin \ \phi + jSin \ \theta \ Cos \ \phi + jCos \ \theta \ Sin \ \phi \right]$$

$$= A \left[ (Cos \ \theta + jSin \ \theta) \ (Cos \ \phi + jSin \ \phi) \right]$$

(2)

o

The complex stator current vector can be represented as  $i_s = i_{as}$ +  $ai_{bs} + a^2i_{cs}$  where  $a = e \frac{j2\pi}{3}$  and  $a^2 = e \frac{j4\pi}{3}$ . This can be replaced by rectangular coordinates as

$$i_s = i_{ds} + ji_{qs} \tag{3}$$

In this equation  $i_{ds}$  and  $i_{qs}$  represent the equivalent of a twophase stator winding which establishes the same magnitude of MMF in a three-phase system. These inputs can be seen after the three-phase to two-phase transformation in the AD2S100 block diagram. Equation (3) therefore represents a three-phase to two-phase conversion. To relate these stator current to the reference frame the rotor currents assume the same rectangular coordinates, but are now rotated by the operator  $e^{i\varphi}$ , where  $e^{i\varphi} = \cos \varphi + j\sin \varphi$ .

Here the term vector rotator comes into play where the stator current vector can be represented in rotor-based coordinates or vice versa.

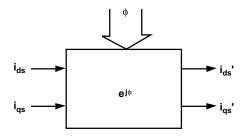

The AD2S100 uses  $e^{i\phi}$  as the core operator. Here  $\phi$  represents the digital position angle which rotates as the rotor moves. In terms of the mathematical function, it rotates the orthogonal  $i_{ds}$  and  $i_{qs}$  components as follows:

$$i_{ds}' + ji_{qs}' = (I_{ds} + jI_{qs}) e^{jc}$$

where  $i_{ds}$ ',  $i_{qs}$ ' = stator currents in the rotor reference frame. And

$$e^{j\phi} = Cos \phi + jSin \phi$$

$$= (I_{ds} + jI_{qs})(Cos \phi + jSin \phi)$$

The output from the AD2S100 takes the form of:

$$i_{ds'} = I_{ds} \cos \phi - I_{qs} \sin \phi$$

$i_{as'} = I_{ds} \sin \phi + I_{as} \cos \phi$

The matrix equation is:

$$\begin{bmatrix} i_{ds} \\ i_{as} \end{bmatrix} = \begin{bmatrix} \cos \phi & -\sin \phi \\ \sin \phi & \cos \phi \end{bmatrix} \begin{bmatrix} I_{ds} \\ I_{as} \end{bmatrix}$$

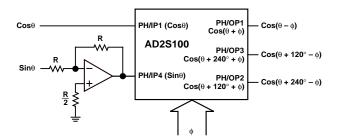

and it is shown in Figure 2.

Figure 2. AD2S100 Vector Rotation Operation

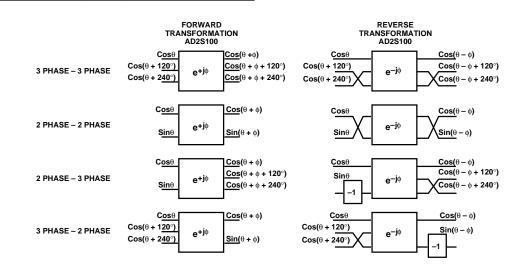

Figure 3. Converter Operation Diagram

## **CONVERTER OPERATION**

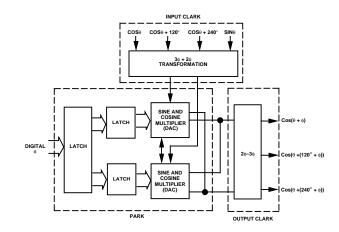

The architecture of the AD2S100 is illustrated in Figure 3. The AD2S100 is configured in the forward transformation which rotates the stator coordinates to the rotor reference frame.

### **Forward Rotation**

In this configuration the  $3\phi-2\phi$  Clark is bypassed, and inputs are fed directly into the quadrature (PH/IP4) and direct (PH/ IPI) inputs to the Park transform,  $e^{i\phi}$ , where  $\phi$  is defined by the AD2S100's digital input. Position data,  $\phi$ , is loaded into the input latch on the positive edge of the strobe pulse. (For detail on the timing, please refer to the "timing diagram.") The negative edge of the strobe signifies that conversion has commenced. A busy pulse is subsequently produced as data is passed from the input latches to the Sin and Cos multipliers. During the loading of the multiplier, the busy pulse remains high to ensure simultaneous setting of  $\phi$  in both the Sin and Cos registers.

The negative edge of the busy pulse signifies that the multipliers are set up and the orthogonal analog inputs are multiplied real time. The resultant two outputs are accessed via the PH/OPI (Pin 7) and PH/OP4 (Pin 6), alternatively they can be directly applied to the output Clark transform. The Clark output is the vector sum of the analog input vector (Cos $\theta$  (PH/OPI), Cos ( $\theta$  + 120°) (PH/OP2), Cos ( $\theta$  + 240°) (PH/OP3) and the digital input vector  $\phi$ .

For other configurations, please refer to "Forward and Reverse Transformation."

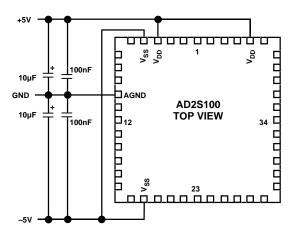

#### CONNECTING THE CONVERTER Power Supply Connection

The power supply voltages connected to  $V_{DD}$  and  $V_{SS}$  pins should be +5 V dc and -5 V dc and must not be reversed. Pin 4 ( $V_{DD}$ ) and Pin 41 ( $V_{DD}$ ) should both be connected to +5 V; similarly, Pin 5 ( $V_{SS}$ ) and Pin 19 ( $V_{SS}$ ) should both be connected to -5 V dc.

It is recommended that decoupling capacitors, 100 nF (ceramic) and 10  $\mu$ F (tantalum) or other high quality capacitors, are connected in parallel between the power line V<sub>DD</sub>, V<sub>SS</sub> and AGND adjacent to the converter. Separate decoupling capacitors should be used for each converter. The connections are shown in Figure 4.

Figure 4. AD2S100 Power Supply Connection

## ANALOG SIGNAL INPUT AND OUTPUT CONNECTIONS Input Analog Signals

All analog signal inputs to AD2S100 are voltages. There are two different voltage levels of three-phase (0°,  $120^{\circ}$ ,  $240^{\circ}$ ) signal inputs. One is the nominal level, which is ±2.8 V dc or 2 V rms and the corresponding input pins are PH/IP1 (Pin 17), PH/IP2 (Pin 15), PH/IP3 (Pin 13) and PH/IP4 (Pin 11).

The high level inputs can accommodate voltages from nominal up to a maximum of  $\pm V_{DD}/V_{SS}$ . The corresponding input pins are PH/IPH1 (Pin 16), PH/IPH2 (Pin 14) and PH/IPH3 (Pin 12). The homopolar output can only be used in the three-phase connection mode.

The converter can accept both two-phase format and threephase format input signals. For the two-phase format input, the two inputs must be orthogonal to each other. For the threephase format input, there is the choice of using all three inputs or using two of the three inputs. In the latter case, the third input signal will be generated internally by using the information of other two inputs. The high level input mode, however, can only be selected with three-phase/three-input format. All these different conversion modes, including nominal/high input level and two/three-phase input format can be selected using two select pins (Pin 23, Pin 24). The functions are summarized in Table I.

Table I. Conversion Mode Selection

| Mode  | Description                                                         | CONV1<br>(Pin 23) | CONV2<br>(Pin 24) |

|-------|---------------------------------------------------------------------|-------------------|-------------------|

| MODE1 | 2-Phase Orthogonal with 2 Inputs<br>Nominal Input Level             | NC                | DGND              |

| MODE2 | 3-Phase (0°, 120°, 240°) with 3 Inputs<br>Nominal/High Input Level* | DGND              | $V_{DD}$          |

| MODE3 | 3-Phase (0°, 120°, 240°) with 2 Inputs<br>Nominal Input Level       | $V_{DD}$          | V <sub>DD</sub>   |

\*The high level input mode can only be selected with MODE2.

**MODE1: 2-Phase/2 Inputs with Nominal Input Level** In this mode, PH/IP1 and PH/IP4 are the inputs and the Pins 12 through 16 must be left unconnected.

**MODE2:** 3-Phase/3 Inputs with Nominal/High Input Level In this mode, either nominal or high level inputs can be used. For nominal level input operation, PH/IP1, PH/IP2 and PH/IP3 are the inputs, and there should be no connections to PH/IPH1, PH/IPH2 and PH/IPH3; similarly, for high level input operation, the PH/IPH1, PH/IPH2 and PH/IPH3 are the inputs, and there should be no connections to PH/IP1, PH/IP2 and PH/IP3. In both cases, the PH/IP4 should be left unconnected. For high level signal input operation, select MODE2 only.

**MODE3: 3-Phase/2 Inputs with Nominal Input Level** In this mode, PH/IP2 and PH/IP3 are the inputs and the third signal will be generated internally by using the information of other two inputs. It is recommended that PH/IP1, PH/IPH1, PH/IPH2, PH/IP4 and PH/IPH3 should be left unconnected.

## **Output Analog Signals**

There are three forms of analog output from the AD2S100.

Sin/Cos orthogonal output signals are derived from the Clark/ three-to-two-phase conversion before the Park angle rotation. These signals are available on Pin 25 (Cos  $\theta$ ) and Pin 26 (Sin  $\theta$ ), and occur before Park angle rotation.

#### **Three-Phase Output Signals**

(Cos ( $\theta + \phi$ ), Cos ( $\phi + \theta + 120^{\circ}$ ), Cos ( $\phi + \theta + 240^{\circ}$ )), where  $\phi$  represents digital input angle. These signals are available on Pin 7 (PH/OP1), Pin 9 (PH/OP2) and Pin 8 (PH/OP3), respectively.

#### **Two-Phase (Sin** $(\theta + \phi)$ , Cos $(\theta + \phi)$ ) Signals

These represent the output of the coordinate transformation. These signals are available on Pin 6 (PH/OP4, Sin  $(\theta + \phi)$ ) and Pin 7 (PH/OP1, Cos  $(\theta + \phi)$ ).

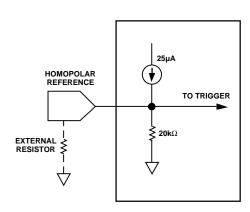

## HOMOPOLAR OUTPUT

## HOMOPOLAR Reference

In a three-phase ac system, the sum of the three inputs to the converter can be used to indicate whether or not the phases are balanced.

If  $V_{SUM} = PH/IP1 + PH/IP2 + PH/IP3$  (or PH/IPH1 + PH/IPH2 + PH/IPH3) this can be rewritten as  $V_{SUM} = [Cos\theta, + Cos(\theta + 120^\circ) + Cos(\theta + 240^\circ)] = 0$ . Any imbalances in the line will cause the sum  $V_{SUM} \neq 0$ . The AD2S100 homopolar output (HPOP) goes high when  $V_{SUM} > 3 \times V_{ts}$ . The voltage level at which the HPOP indicates an imbalance is determined by the HPREF threshold,  $V_{ts}$ . This is set internally at  $\pm 0.5$  V dc ( $\pm 0.1$  V dc). The HPOP goes high when

$$V_{ts} < \frac{(Cos\theta + Cos(\theta + 120^\circ) + Cos(\theta + 240^\circ))}{3} \times V$$

where V is the nominal input voltage.

With no external components  $V_{SUM}$  must exceed  $\pm 1.5$  V dc in order for HPOP to indicate an imbalance. The sensitivity of the threshold can be reduced by connecting an external resistor between HPOP and ground in Figure 5 where,

$$V_{ts} = \frac{0.5 R_{EXT}}{R_{EXT} + 20000}$$

$R_{EXT} = \Omega$  $V_{ts} = V dc.$

Figure 5. The Equivalent Homopolar Reference Input Circuitry

Example: From the equivalent circuit, it can be seen that the inclusion of a 20 k $\Omega$  resistor will reduce  $V_{ts}$  to  $\pm 0.25$  V dc. This corresponds to an imbalance of  $\pm 0.75$  V dc in the inputs.

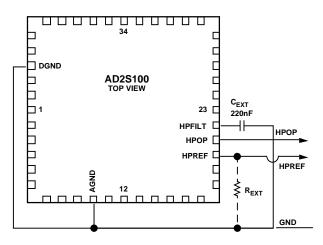

## **Homopolar Filtering**

The equation  $V_{SUM} = \cos\theta + \cos(\theta + 120^\circ) + \cos(\theta + 240^\circ)$ = 0 denotes an imbalance when  $V_{SUM} \neq 0$ . There are conditions, however, when an actual imbalance will occur and the conditions as defined by  $V_{SUM}$  will be valid. For example, if the first phase was open circuit when  $\theta = 90^\circ$  or  $270^\circ$ , the first phase is valid at 0 V dc.  $V_{SUM}$  is valid, therefore, when  $\cos\theta$  is close to 0. In order to detect an imbalance  $\theta$  has to move away from  $90^\circ$  or  $270^\circ$ , i.e., when on a balanced line  $\cos \theta \neq 0$ .

Line imbalance is detected as a function of HPREF, either set by the user or internally set at ±0.5 V dc. This corresponds to a dead zone when  $\phi = 90^{\circ}$  or  $270^{\circ} \pm 30^{\circ}$ , i.e.,  $V_{SUM} = 0$ , and, therefore, no indicated imbalance. If an external 20 k $\Omega$  resistor is added, this halves  $V_{ts}$  and reduces the zone to ±15°. Note this example only applies if the first phase is detached.

In order to prevent this false triggering an external capacitor needs to be placed from HPFILT to ground, as shown in Figure 5. This averages out the perceived imbalance over a complete cycle and will prevent the HPOP from alternatively indicating balance and imbalance over  $\theta = 0^{\circ}$  to  $360^{\circ}$ .

For

$$\frac{d\theta}{dt} = 1000 \ rpm \ C_{EXT} = 200 \ nF$$

$$\frac{d\theta}{dt} = 100 \ rpm \ C_{EXT} = 2.2 \ \mu F$$

Note: The slower the input rotational speed, the larger the time constant required over which to average the HPOP output. Use of the homopolar output at slow rotational speeds becomes impractical with respect to the increased value for  $C_{EXT}$ .

Figure 6. AD2S100 Homopolar Output Connections

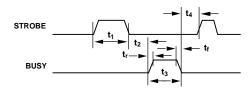

## TIMING DIAGRAMS

### **Busy Output**

The state of converter is indicated by the state of the BUSY output (Pin 44). The BUSY output will go HI at the negative edge of the STROBE input. This is used to synchronize digital input data and load the digital angular rotation information into the device counter. The BUSY output will remain HI for 2  $\mu$ s, and go LO until the next strobe negative edge occurs.

### Strobe Input

The width of the positive STROBE pulse should be at least 100 ns, in order to successfully start the conversion. The maximum frequency of STROBE input is 366 kHz, i.e., there should be at least 2.73  $\mu$ s from the negative edge of one STROBE pulse to the next rising edge. This is illustrated by the following timing diagram and table.

Figure 7. AD2S100 Timing Diagram

Note: Digital data should be stable 25 ns before and after positive strobe edge.

| Table  | II. | AD2S100  | Timing    | Tabl  | e |

|--------|-----|----------|-----------|-------|---|

| I GOIC |     | 11020100 | 1 1111119 | I GUI | - |

| Parameter      | Min    | Тур    | Max    | Condition                              |

|----------------|--------|--------|--------|----------------------------------------|

| t <sub>1</sub> | 100 ns |        |        | STROBE Pulse Width                     |

| t <sub>2</sub> |        | 30 ns  |        | STROBE $\downarrow$ to BUSY $\uparrow$ |

| t <sub>3</sub> | 1.7 μs |        | 2.5 µs | BUSY Pulse Width                       |

| t <sub>4</sub> |        | 100 ns |        | BUSY $\downarrow$ to STROBE $\uparrow$ |

| t <sub>r</sub> |        | 20 ns  |        | BUSY Pulse Rise Time                   |

|                |        |        |        | with No Load                           |

|                |        | 150 ns |        | BUSY Pulse Rise Time                   |

|                |        |        |        | with 68 pF Load                        |

| t <sub>f</sub> |        | 10 ns  |        | BUSY Pulse Fall Time                   |

|                |        |        |        | with No Load                           |

|                |        | 120 ns |        | BUSY Pulse Fall Time                   |

|                |        |        |        | with 68 pF Load                        |

#### **TYPICAL CIRCUIT CONFIGURATION**

Figure 8 shows a typical circuit configuration for the AD2S100 in a three phase, nominal level input mode (MODE2).

Figure 8. Typical Circuit Configuration

## APPLICATIONS

### Forward and ReverseTransformation

The AD2S100 can perform both forward and reverse transformations. The section "Theory of Operation" explains how the chip operates with the core operator  $e^{+j\phi}$ , which performs a forward transformation. The reverse transformation,  $e^{-j\phi}$ , is not mentioned in the above sections of the data sheet simply to avoid the confusion in the functionality and pinout. However, the reverse transformation is very useful in many different applications, and the AD2S100 can be easily configured in a reverse transformation configuration. Figure 9 shows four different phase input/output connections for AD2S100 reverse transformation operation.

Figure 9. Reverse Transformation Connections

$\sqrt{\text{In Figure 9, "-1" operator performs a 180° phase shift opera$ tion. It can be illustrated by a 2-phase-to-3-phase reverse transformation. An example is shown in Figure 10.

Figure 10. Two-Phase to Three-Phase Reverse Transformation

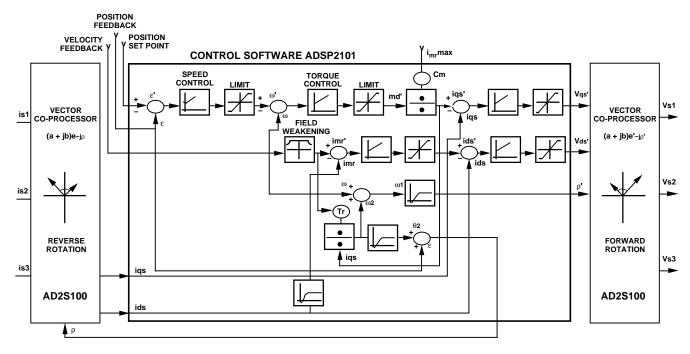

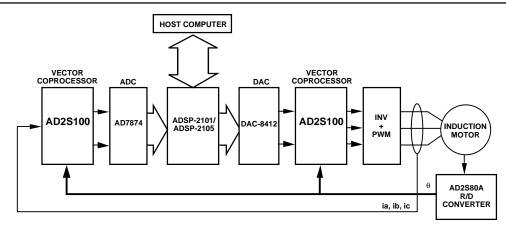

## Field Oriented Control of AC Induction Machine in a Rotor Flux Frame

The architecture shown in Figure 11 identifies a simplified scheme where the AD2S100 permits the DSP computing core to execute the motor control in what is normally termed the rotor reference frame. This reference frame actually operates in synchronism with the rotor of a motor. This has significant benefits regarding motor control efficiency and economics. The

calculating power required in the rotor reference frame is significantly reduced because the currents and flux are rotating at the slip frequency. This permits calculations to be carried out in time frames of, 100 µs, or under by a fixed-point DSP. Benchmark timing in this type of architecture can attain floating-point speed processing with a fixed-point processor. Perhaps the largest advantage is in the ease with which the rotor flux position can be obtained. A large amount of computation time is, therefore, removed by the AD2S100 vector processors due to the split architecture shown in Figure 11. Motor control systems employing one DSP to carry out the cartesian to polar transformations required for vector control are, therefore, tasked with additional duties due to the fact that they normally operate in the flux reference frame.

The robustness of the control system can also be increased by carrying out the control in the rotor reference frame. This is achieved through the ability to increase and improve both the algorithm quality in nonlinear calculations attributed to magnetizing inductance and rotor time constant for example. An increase in sampling time can also be concluded with this architecture by avoiding the additional computing associated with number truncation and rounding errors which reduce the signalto-noise rejection ratio.

Figure 11. Rotor Reference Frame Architecture

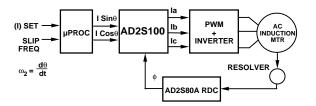

## SIMPLE SLIP CONTROL

In an adjustable-frequency drive, the control strategy must ensure that motor operation is restricted to low slip frequencies, resulting in stable operation with a high power factor and a high torque per stator ampere. Figure 12 shows the block diagram of simple slip control using the AD2S100. Here, the slip frequency command  $\omega_2$  and the current amplitude command are sent to the microprocessor to generate two orthogonal signals,  $|I| \sin \theta$ and  $|I| \cos \theta$  here ( $\theta = \omega_2$ .) With the actual shaft position angle,  $\phi$ , (resolver-to-digital converter) and the orthogonal signals from

## Figure 12. Slip Control of AC Induction Motor with AD2S100

the  $\mu$ P, the AD2S100 generates the inverter frequency and amplitude command into a three-phase format. The three-phase sine wave reference currents are reproduced in the stator phases. For general applications, both the steady-state and dynamic performance of this simple control scheme is satisfactory. For detailed information about this application, please refer to the bibliography at the end of the data sheet.

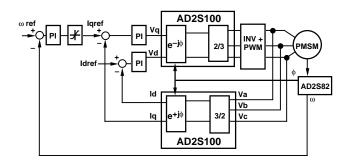

## ADVANCED PMSM SERVO CONTROL

Electronically commutated permanent magnet synchronous motors (PMSM) are used in high performance drives for machine tools and robotics. When a field orientated control scheme is deployed, the resulting brushless drive has all the properties required for servo applications in machine tool fed drives, industrial robots, and spindle drives. These properties include large torque/inertia ratio, a high peak torque capability for fast acceleration and deceleration with high torsional stiffness at standstill.

Figure 13 shows the AD2S100 configured for both forward and reverse transformations. This architecture concludes both flux and torque current components independently. The additional control of Vd (flux component) allows for the implementation of field weakening schemes and maintenance of power factor.

For more detailed information, please refer to the application note "Vector Control Using a Single Vector Rotation Semiconductor for Induction and Permanent Magnet Motors."

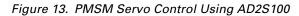

## MOTION CONTROL DSP COPROCESSOR

AC induction motors are superior to dc motors with respect to size/power ratio, weight, rotor inertia, maximum rotating velocity, efficiency and cost for motor ratings greater than 5 HP. However, because of nonlinear and the highly interactive multivariable control structure, ac induction motors have been considered difficult to control in applications demanding variable speed and torque.

Field orientated control theory and practice, under development since 1975, has offered the same level of control enjoyed by traditional dc machines. Practical implementation of these algorithms involves the use of DSP and microprocessor based architectures. The AD2S100 removes the needs for software implementation of the rotor-to-stator and stator-to-rotor transformations in the DSP or  $\mu$ P. The reduction in throughput times from typically 100  $\mu$ s ( $\mu$ P) and 40  $\mu$ s (DSP) to 2  $\mu$ s increases system bandwidths while also allowing additional features to be added to the CPU. The combination of the fixed point ADSP-2101 and the AD2S100, the "advanced motion control engine" shown in Figure 14, enables bandwidths previously attainable only through the use of floating point devices.

For more detailed information on the AD2S100 vector control application and on this advanced motion control engine, please refer to application notes "Vector Control Using a Single Vector Rotation Semiconductor for Induction and Permanent Magnet Motors."

## **MEASUREMENT OF HARMONICS**

Three-phase ac power systems are widely used in power generation, transmission and electric drive. The quality of the electricity supply is affected by harmonics injected into the power main. In inverter fed ac machines, fluxes and currents of various frequencies are produced. Predominantly in ac machines the 5th and 7th harmonics are the most damaging; their reaction with the fundamental flux component produces 6th harmonic torque pulsations. The subsequent pulsating torque output may result in uneven motion of the motor, especially at low speeds.

The AD2S100 can be used to monitor and detect the presence and magnitude of a particular harmonic on a three-phase line. Figure 15 shows the implementation of such a scheme using the AD2S100. Note, the actual line voltages will have to be scaled before applying to the three-phase input of the AD2S100.

Selecting a harmonic is achieved by synchronizing the rotational frequency of the park digital input,  $\phi$ , with the frequency of the fundamental flux component and the integer harmonic selected. The update rate, r, of the counters is determined by:

$$r = 4096 \ \frac{n \times \omega}{2 \ \pi}$$

Here, *r* = input clock pulse rate (pulses/second);

- n = the order of harmonics to be measured;

- $\omega$  = fundamental angular frequency of the ac signal.

Figure 14. Advanced Motion Control Engine

The magnitude of the n-th harmonic as well as the fundamental component in the power line is represented by the output of the low-pass filter,  $a_k$ . In concert with magnitude of the harmonic the AD2S100 homopolar output will indicate whether the three phases are balanced or not. For more details about this application, refer to the related application note listed in the bibliography.

Figure 15. Harmonics Measurement Using AD2S100

## **MULTIPLE POLE MOTORS**

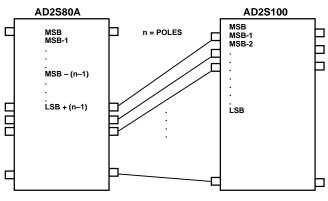

For multi-pole motor applications where a single speed resolver is used, the AD2S100 input has to be configured to match the electrical cycle of the resolver with the phasing of the motor windings. The input to the AD2S100 is the output of a resolverto-digital converter, e.g., AD2S80A series. The parallel output of the converter needs to be multiplied by  $2^{n-1}$ , where n = the number of pole parts of the motor. In practice this is implemented by shifting the parallel output of the converter left relative to the number of pole pairs.

Figure 16 shows the generic configuration of the AD2S80A with the AD2S100 for a motor with n pole pairs. The MSB of the AD2S100 is connected to MSB-(n-1) bit of the AD2S80A digital output, MSB-1 bit to MSB-(n-2) bit, . . ., LSB bit to LSB bit of AD2S80A, etc.

12,14 OR 16-BIT RESOLUTION MODE

### Figure 16. A General Consideration in Connecting R/D Converter and AD2S100 for Multiple Pole Motors

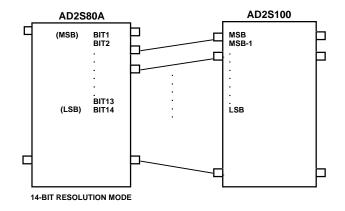

Figure 17 shows the AD2S80A configured for use with a four pole motor, where n = 2. Using the formula described the MSB is shifted left once

## DIGITAL-TO-RESOLVER AND SYNCHRO CONVERSION

The AD2S100 can be configured for use as a 12-bit digital-toresolver (DRC) or synchro converter (DSC). DRCs and DSCs are used to simulate the outputs of a resolver or a synchro. The simulated outputs are represented by the transforms outlined below.

## **Resolver Outputs**

Asinωt.cosφ Asinωt.sinφ

## Synchro Outputs

Asinωt.sinφ Asinωt.sin (φ + 120°) Asinωt.sin (φ + 240°)

where:  $Asin\omega t = fixed$  ac reference

$\phi$  = digital input angle, i.e., shaft position

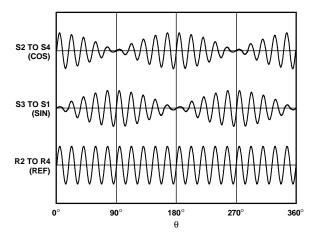

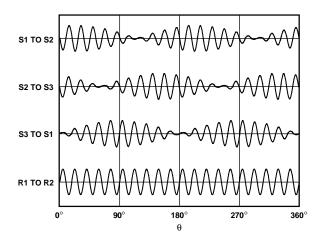

The waveforms are shown in Figures 18 and 19.

*Figure 18. Electrical Representation and Typical Resolver Signals*

Figure 19. Electrical Representation and Typical Synchro Signals

Configuring the AD2S100 for DRC and DSC operation is done by the following.

## DRC-Must Select Mode 1

| Inputs<br>Outputs      | PH/IP4<br>PH/IP1<br>PH/OP1<br>PH/OP4 | Pin 11<br>Pin 1<br>Pin 7<br>Pin 6 | AGND<br>Reference Asinωt<br>Asinωt Cosφ<br>Asinωt Sinφ |  |  |  |

|------------------------|--------------------------------------|-----------------------------------|--------------------------------------------------------|--|--|--|

| DSC—Must Select Mode 1 |                                      |                                   |                                                        |  |  |  |

| Inputs                 | PH/IP4                               | Pin 11                            | Reference Asinwt                                       |  |  |  |

|                        | PH/IP1                               | Pin 17                            | AGND                                                   |  |  |  |

| Outputs                | PH/OP1                               | Pin 7                             | –Asinωt Sinφ                                           |  |  |  |

|                        | PH/OP2                               | Pin 9                             | $-Asin\omega t Sin (\phi + 120^{\circ})$               |  |  |  |

|                        | PH/OP3                               | Pin 8                             | -Asin $\omega$ t Sin ( $\phi$ + 240°)                  |  |  |  |

NOTES

1. Valid information is only available after the strobe pulse and BUSY go low. For more information on DRCs see the AD2S65/AD2S66 data sheet.

2. To correct for inverse phasing of the DSC outputs the reference should be inverted, or the MSB can be inverted.

## **APPLICATION NOTES LIST**

- "Vector Control Using a Single Vector Rotation Semiconductor for Induction and Permanent Magnet Motors," by F. P. Flett, Analog Devices.

- "Gamana DSP Vector Coprocessor for Brushless Motor Control," by Analog Devices and Infosys Manufacturing System.

- 3. "Silicon Control Algorithms for Brushless Permanent Magnet Synchronous Machines," by F. P. Flett.

- 4. "Single Chip Vector Rotation Blocks and Induction Motor Field Oriented Control," by A. P. M. Van den Bossche and P. J. M. Coussens.

- 5. "Three Phase Measurements with Vector Rotation Blocks in Mains and Motion Control," P. J. M. Coussens, et al.

- 6. "Digital to Synchro and Resolver Conversion with the AC Vector Processor AD2S100," by Dennis Fu.

- 7. "Experiment with the AD2S100 Evaluation Board," by Dennis Fu.

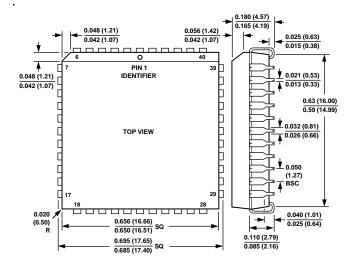

44-Lead Plastic Leaded Chip Carrier (P-44A)

PRINTED IN U.S.A.