## CMOS Complete DDS

AD9830

FEATURES +5 V Power Supply 50 MHz Speed On-Chip SINE Look-Up Table On-Chip 10-Bit DAC Parallel Loading Power-Down Option 72 dB SFDR 250 mW Power Consumption 48-Pin TQFP

APPLICATIONS DDS Tuning Digital Demodulation

### GENERAL DESCRIPTION

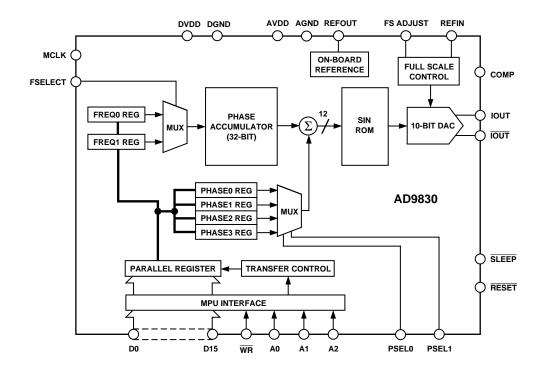

This DDS device is a numerically controlled oscillator employing a phase accumulator, a sine look-up table and a 10-bit D/A converter integrated on a single CMOS chip. Modulation capabilities are provided for phase modulation and frequency modulation.

Clock rates up to 50 MHz are supported. Frequency accuracy can be controlled to one part in 4 billion. Modulation is effected by loading registers through the parallel microprocessor interface.

A power-down pin allows external control of a power-down mode. The part is available in a 48-pin TQFP package.

### **FUNCTIONAL BLOCK DIAGRAM**

# $\label{eq:AD9830-SPECIFICATIONS} \begin{aligned} &\text{AD9830-SPECIFICATIONS}^1 \text{ ($V_{DD} = +5$ V$ $\pm 5\%$; AGND = DGND = 0 V$; $\underline{T_A = T_{MIN}$ to $T_{MAX}$}$; REFIN = REFOUT$; \\ &R_{SET} = 1 \text{ k} \Omega; R_{LOAD} = 51 \text{ }\Omega \text{ for IOUT and } \overline{\text{IOUT}} \text{ unless otherwise noted)} \end{aligned}$

| Parameter                                                                                                                                        | AD9830A                                           | Units                                                    | Test Conditions/Comments                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIGNAL DAC SPECIFICATIONS Resolution Update Rate (f <sub>MAX</sub> )                                                                             | 10<br>50                                          | Bits<br>MSPS max                                         |                                                                                                                                                                         |

| I <sub>OUT</sub> Full Scale<br>Output Compliance                                                                                                 | 20                                                | mA max<br>V max                                          |                                                                                                                                                                         |

| DC Accuracy<br>Integral Nonlinearity<br>Differential Nonlinearity                                                                                | ±1<br>±0.5                                        | LSB typ<br>LSB typ                                       |                                                                                                                                                                         |

| DDS SPECIFICATIONS <sup>2</sup> Dynamic Specifications                                                                                           |                                                   | 31                                                       |                                                                                                                                                                         |

| Signal-to-Noise Ratio<br>Total Harmonic Distortion<br>Spurious Free Dynamic Range (SFDR) <sup>3</sup><br>Narrow Band                             | 50<br>-53                                         | dB min<br>dBc max                                        | $ \begin{array}{l} f_{MCLK} = f_{MAX} \;,\; f_{OUT} = 2\;MHz \\ f_{MCLK} = f_{MAX} \;,\; f_{OUT} = 2\;MHz \\ f_{MCLK} = 6.25\;MHz ,\; f_{OUT} = 2.11\;MHz \end{array} $ |

| (±50 kHz)<br>(±200 kHz)<br>Wide Band (±2 MHz)                                                                                                    | -72<br>-68<br>-50                                 | dBc min<br>dBc min<br>dBc min                            |                                                                                                                                                                         |

| Clock Feedthrough<br>Wake Up Time<br>Power-Down Option                                                                                           | -55<br>1<br>Yes                                   | dBc typ<br>ms typ                                        |                                                                                                                                                                         |

| VOLTAGE REFERENCE Internal Reference @ +25°C     T <sub>MIN</sub> to T <sub>MAX</sub> REFIN Input Impedance Reference TC REFOUT Impedance        | 1.21<br>1.21 ± 7%<br>10<br>100<br>300             | Volts typ Volts min/max MΩ typ ppm/°C typ Ω typ          |                                                                                                                                                                         |

| LOGIC INPUTS $V_{\rm INH}$ , Input High Voltage $V_{\rm INL}$ , Input Low Voltage $I_{\rm INH}$ , Input Current $C_{\rm IN}$ , Input Capacitance | V <sub>DD</sub> -0.9<br>0.9<br>10<br>10           | V min<br>V max<br>μA max<br>pF max                       |                                                                                                                                                                         |

| POWER SUPPLIES AVDD DVDD $I_{AA}$ $I_{DD}$ $I_{AA} + I_{DD}^4$                                                                                   | 4.75/5.25<br>4.75/5.25<br>25<br>6 + 0.5/MHz<br>60 | V min/V max<br>V min/V max<br>mA max<br>mA typ<br>mA max | f <sub>OUT</sub> = 2 MHz                                                                                                                                                |

| Low Power Sleep Mode <sup>5</sup>                                                                                                                | 0.25                                              | mA typ<br>mA max                                         | 1 MΩ Resistor Tied Between REFOUT and AGND                                                                                                                              |

#### NOTES

The AD9830 is tested with a capacitive load of 50 pF. The part can be operated with higher capacitive loads, but the magnitude of the analog output will be attenuated. For example, a 10 MHz output signal will be attenuated by 3 dB when the load capacitance equals  $250 \, \mathrm{pF}$ .

Specifications subject to change without notice.

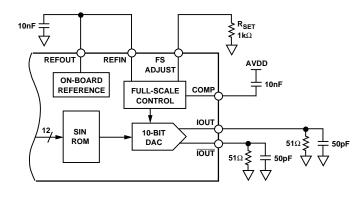

Figure 1. Test Circuit with Which Specifications Are Tested

-2- REV. A

$<sup>^1</sup> Operating \ temperature \ range \ is \ as follows: A Version: <math display="inline">-40\,^{\circ}C$  to  $\ +85\,^{\circ}C.$

<sup>&</sup>lt;sup>2</sup>All dynamic specifications are measured using IOUT. 100% production tested.

$<sup>^3</sup>f_{MCLK} = 6.25$  MHz, Frequency Word = 5671C71C HEX,  $f_{OUT} = 2.11$  MHz.

<sup>&</sup>lt;sup>4</sup>Measured with the digital inputs static and equal to 0 V or DVDD.

$<sup>^5</sup> The\ Low\ Power\ Sleep\ Mode\ current$  is 2 mA typically when a 1  $M\Omega$  resistor is not tied from REFOUT to AGND.

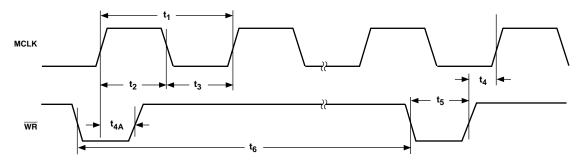

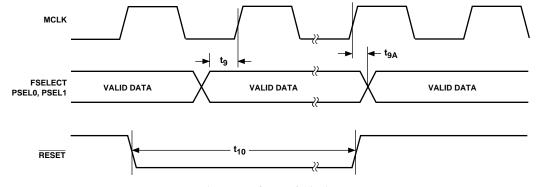

## TIMING CHARACTERISTICS ( $V_{DD} = +5 \text{ V} \pm 5\%$ ; AGND = DGND = 0 V, unless otherwise noted)

| Parameter        | Limit at<br>T <sub>MIN</sub> to T <sub>MAX</sub><br>(A Version) | Units  | Test Conditions/Comments                                 |

|------------------|-----------------------------------------------------------------|--------|----------------------------------------------------------|

| $\overline{t_1}$ | 20                                                              | ns min | MCLK Period                                              |

| $t_2$            | 8                                                               | ns min | MCLK High Duration                                       |

| $t_3$            | 8                                                               | ns min | MCLK Low Duration                                        |

| $t_4^1$          | 8                                                               | ns min | WR Rising Edge Before MCLK Rising Edge                   |

| $t_{4A}^1$       | 8                                                               | ns min | WR Rising Edge After MCLK Rising Edge                    |

| $t_5$            | 8                                                               | ns min | WR Pulse Width                                           |

| $t_6$            | $t_1$                                                           | ns min | Duration Between Consecutive WR Pulses                   |

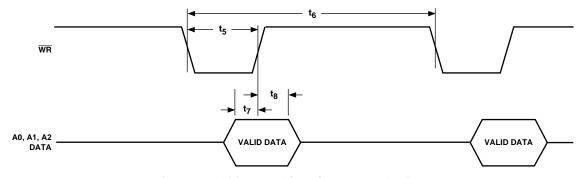

| $t_7$            | 5                                                               | ns min | Data/Address Setup Time                                  |

| t <sub>8</sub>   | 3                                                               | ns min | Data/Address Hold Time                                   |

| $t_9^1$          | 8                                                               | ns min | FSELECT, PSEL0, PSEL1 Setup Time Before MCLK Rising Edge |

| $t_{9A}^1$       | 8                                                               | ns min | FSELECT, PSEL0, PSEL1 Setup Time After MCLK Rising Edge  |

| $t_{10}$         | $t_1$                                                           | ns min | RESET Pulse Duration                                     |

Guaranteed by design, but not production tested.

Figure 2. WR-MCLK Relationship

Figure 3. Writing to a Phase/Frequency Register

Figure 4. Control Timing

NOTES

See Pin Description section.

###

| Maximum Junction Temperature         | +150°C |

|--------------------------------------|--------|

| TQFP $\theta_{JA}$ Thermal Impedance | 75°C/W |

| Lead Temperature, Soldering          |        |

| Vapor Phase (60 sec)                 | +215°C |

| Infrared (15 sec)                    | +220°C |

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### CAUTION.

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this device features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

### **ORDERING GUIDE**

| Model     | Temperature Range | Package Option* |  |

|-----------|-------------------|-----------------|--|

| AD9830AST | -40°C to +85°C    | ST-48           |  |

<sup>\*</sup>ST = Thin Quad Flatpack (TQFP).

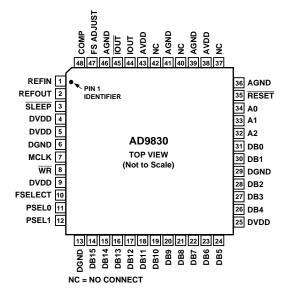

### PIN CONFIGURATION

### PIN DESCRIPTION

| Mnemonic     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER SUPI   | PLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AVDD         | Positive power supply for the analog section. A 0.1 $\mu F$ capacitor should be connected between AVDD and AGND. AVDD has a value of +5 V $\pm$ 5%.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AGND         | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DVDD         | Positive power supply for the digital section. A 0.1 $\mu F$ decoupling capacitor should be connected between DVDD and DGND. DVDD has a value of +5 V $\pm$ 5%.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DGND         | Digital Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ANALOG SIG   | NAL AND REFERENCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| IOUT, IOUT   | Current Output. This is a high impedance current source. A load resistor should be connected between IOUT and AGND. IOUT should be either tied directly to AGND or through an external load resistor to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| FS ADJUST    | Full-Scale Adjust Control. A resistor ( $R_{SET}$ ) is connected between this pin and AGND. This determines the magnitude of the full-scale DAC current. The relationship between $R_{SET}$ and the full-scale current is as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | $IOUT_{FULL\text{-}SCALE} = 16 \ V_{REFIN}/R_{SET} \ V_{REFIN} = 1.21 \ V \ nominal, \ R_{SET} = 1 \ \mathrm{k}\Omega \ typical$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| REFIN        | Voltage Reference Input. The AD9830 can be used with either the on-board reference, which is available from pin REFOUT, or an external reference. The reference to be used is connected to the REFIN pin. The AD9830 accepts a reference of 1.21 V nominal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| REFOUT       | Voltage Reference Output. The AD9830 has an on-board reference of value 1.21 V nominal. The reference is made available on the REFOUT pin. This reference is used as the reference to the DAC by connecting REFOUT to REFIN. REFOUT should be decoupled with a 10 nF capacitor to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| COMP         | Compensation pin. This is a compensation pin for the internal reference amplifier. A 10 nF decoupling ceramic capacitor should be connected between COMP and AVDD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DIGITAL INT  | ERFACE AND CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MCLK         | Digital Clock Input. DDS output frequencies are expressed as a binary fraction of the frequency of MCLK. The output frequency accuracy and phase noise are determined by this clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| FSELECT      | Frequency Select Input. FSELECT controls which frequency register, FREQ0 or FREQ1, is used in the phase accumulator. FSELECT is sampled on the rising MCLK edge. FSELECT needs to be in steady state when an MCLK rising edge occurs. If FSELECT changes value when an MCLK rising edge occurs, there is an uncertaint of one MCLK cycle as to when control is transferred to the other frequency register. To avoid any uncertainty, a change on FSELECT should not coincide with an MCLK rising edge.                                                                                                                                                                                                                                                                                                              |

| WR           | Write, Edge-Triggered Digital Input. The $\overline{WR}$ pin is used when writing data to the AD9830. The data is loaded into the AD9830 on the rising edge of the $\overline{WR}$ pulse. This data is then loaded into the destination register on the MCLK rising edge. The $\overline{WR}$ pulse rising edge should not coincide with the MCLK rising edge as there will be ar uncertainty of one MCLK cycle regarding the loading of the destination register with the new data. The $\overline{WR}$ rising edge should occur before an MCLK rising edge. The data will then be transferred into the destination register on the MCLK rising edge. Alternatively, the $\overline{WR}$ rising edge can occur after the MCLK rising edge and the destination register will be loaded on the next MCLK rising edge. |

| D0-D15       | Data Bus, Digital Inputs for destination registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| A0-A2        | Address Digital Inputs. These address bits are used to select the destination register to which the digital data is to be written.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PSEL0, PSEL1 | Phase Select Input. The AD9830 has four phase registers. These registers can be used to alter the value being input to the SIN ROM. The contents of the phase register can be added to the phase accumulator output, the input PSEL0 and PSEL1 selecting the phase register to be used. Like the FSELECT input, the AD9830 samples the PSEL0 and PSEL1 inputs on the MCLK rising edge. Therefore, these inputs should be in steady state at the MCLK rising edge or, there is an uncertainty of one MCLK cycle as to when control is transferred to the selected phase register.                                                                                                                                                                                                                                     |

| SLEEP        | Low Power Control, active low digital input. SLEEP puts the AD9830 into a low power mode. Internal clocks are disabled and the DAC's current sources and REFOUT are turned off. The AD9830 is re-enabled by taking SLEEP high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RESET        | Reset, active low digital input. RESET resets the phase accumulator to zero which corresponds to an analog output of midscale.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

REV. A -5-

### **TERMINOLOGY**

### **Integral Nonlinearity**

This is the maximum deviation of any code from a straight line passing through the endpoints of the transfer function. The endpoints of the transfer function are zero scale, a point 0.5 LSB below the first code transition  $(000 \dots 00 \text{ to } 000 \dots 01)$  and full scale, a point 0.5 LSB above the last code transition  $(111 \dots 10 \text{ to } 111 \dots 11)$ . The error is expressed in LSBs.

### **Differential Nonlinearity**

This is the difference between the measured and the ideal 1 LSB change between two adjacent codes in the DAC.

### Signal to (Noise + Distortion)

Signal to (Noise + Distortion) is measured signal to noise at the output of the DAC. The signal is the rms magnitude of the fundamental. Noise is the rms sum of all the nonfundamental signals up to half the sampling frequency ( $f_{MCLK}/2$ ) but excluding the dc component. Signal to (Noise + Distortion) is dependent on the number of quantization levels used in the digitization process; the more levels, the smaller the quantization noise. The theoretical Signal to (Noise + Distortion) ratio for a sine wave input is given by

Signal to (Noise + Distortion) =

$$(6.02 N + 1.76) dB$$

where N is the number of bits. Thus, for an ideal 10-bit converter, Signal to (Noise + Distortion) = 61.96 dB.

### **Total Harmonic Distortion**

Total Harmonic Distortion (THD) is the ratio of the rms sum of harmonics to the rms value of the fundamental. For the AD9830, THD is defined as

$$THD = 20\log \frac{\sqrt{(V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2)}}{V_1}$$

where  $V_1$  is the rms amplitude of the fundamental and  $V_2$ ,  $V_3$ ,  $V_4$ ,  $V_5$  and  $V_6$  are the rms amplitudes of the second through the sixth harmonic.

### **Output Compliance**

The output compliance refers to the maximum voltage which can be generated at the output of the DAC to meet the specifications. When voltages greater than that specified for the output compliance are generated, the AD9830 may not meet the specifications listed in the data sheet. For the AD9830, the maximum voltage which can be generated by the DAC is 1V.

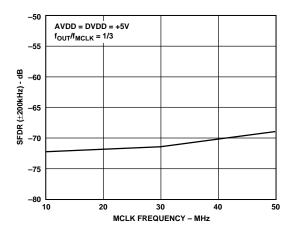

### **Spurious Free Dynamic Range**

Along with the frequency of interest, harmonics of the fundamental frequency and images of the MCLK frequency will be present at the output of a DDS device. The spurious free dynamic range (SFDR) refers to the largest spur or harmonic which is present in the band of interest. The wideband SFDR gives the magnitude of the largest harmonic or spur relative to the magnitude of the fundamental frequency in the bandwidth  $\pm 2$  MHz about the fundamental frequency. The narrowband SFDR gives the attenuation of the largest spur or harmonic in a bandwidth of  $\pm 200$  kHz and  $\pm 50$  kHz about the fundamental frequency.

### **Clock Feedthrough**

There will be feedthrough from the MCLK input to the analog output. The clock feedthrough refers to the magnitude of the MCLK signal relative to the fundamental frequency in the AD9830's output spectrum.

-6- REV. A

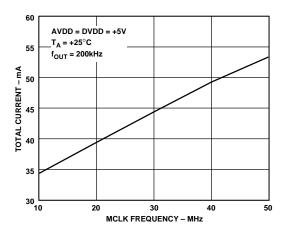

## Typical Performance Characteristics—AD9830

Figure 5. Typical Current Consumption vs. MCLK Frequency

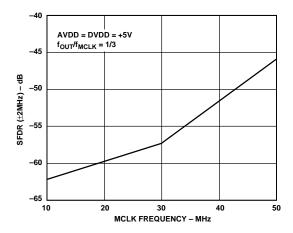

Figure 6. Narrow Band SFDR vs. MCLK Frequency

Figure 7. Wide Band SFDR vs. MCLK Frequency

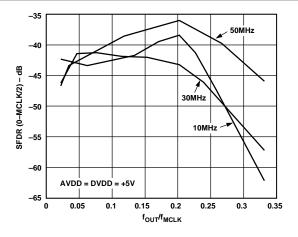

Figure 8. WB SFDR vs.  $f_{OUT}/f_{MCLK}$  for Various MCLK Frequencies

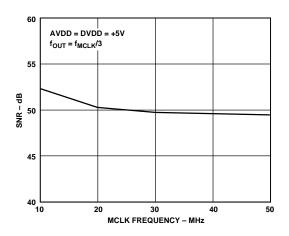

Figure 9. SNR vs. MCLK Frequency

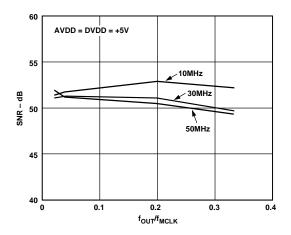

Figure 10. SNR vs.  $f_{OUT}/f_{MCLK}$  for Various MCLK Frequencies

REV. A -7-

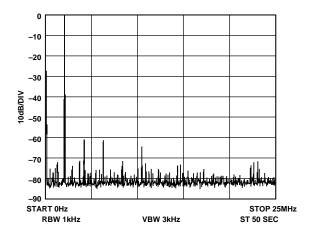

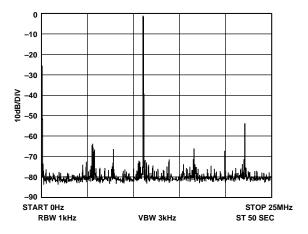

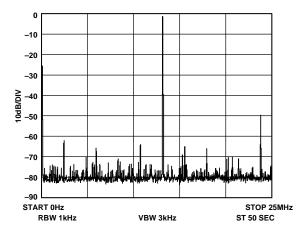

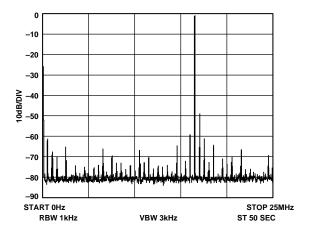

Figure 11.  $f_{MCLK} = 50$  MHz,  $f_{OUT} = 2.1$  MHz, Frequency Word = ACO8312

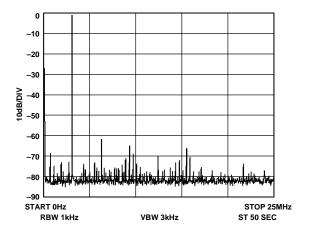

Figure 12.  $f_{MCLK}$  = 50 MHz,  $f_{OUT}$  = 3.1 MHz, Frequency Word = FDF3B64

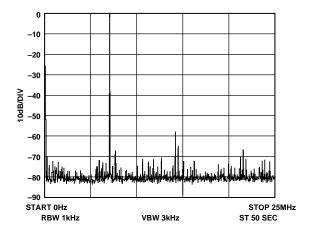

Figure 13.  $f_{MCLK}$  = 50 MHz,  $f_{OUT}$  = 7.1 MHz, Frequency Word = 245A1CAC

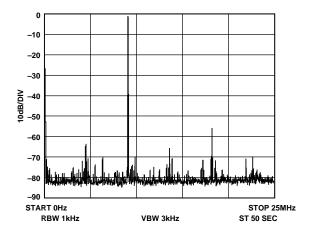

Figure 14.  $f_{MCLK} = 50$  MHz,  $f_{OUT} = 9.1$  MHz, Frequency Word = 2E978D50

Figure 15.  $f_{MCLK}$  = 50 MHz,  $f_{OUT}$  = 11.1 MHz, Frequency Word = 38D4FDF4

Figure 16.  $f_{MCLK}$  = 50 MHz,  $f_{OUT}$  = 13.1 MHz, Frequency Word = 43126E98

Figure 17.  $f_{MCLK}$  = 50 MHz,  $f_{OUT}$  = 16.5 MHz, Frequency Word = 547AE148

| - ·        | - C1    | - · · ·                                                                                                                                |

|------------|---------|----------------------------------------------------------------------------------------------------------------------------------------|

| Register   | Size    | Description                                                                                                                            |

| FREQ0 REG  | 32 Bits | Frequency Register 0. This defines the output frequency, when FSELECT = 0, as a fraction of the MCLK frequency.                        |

| FREQ1 REG  | 32 Bits | Frequency Register 1. This defines the output frequency, when FSELECT = 1, as a fraction of the MCLK frequency.                        |

| PHASE0 REG | 12 Bits | Phase Offset Register 0. When PSEL0 = PSEL1 = 0, the contents of this register are added to the output of the phase accumulator.       |

| PHASE1 REG | 12 Bits | Phase Offset Register 1. When PSEL0 = 1 and PSEL1 = 0, the contents of this register are added to the output of the phase accumulator. |

| PHASE2 REG | 12 Bits | Phase Offset Register 2. When PSEL0 = 0 and PSEL1 = 1, the contents of this register are added to the output of the phase accumulator. |

| PHASE3 REG | 12 Bits | Phase Offset Register 3. When PSEL0 = PSEL1 = 1, the contents of this register are added to the output of the phase accumulator.       |

Figure 18. AD9830 Control Registers

| A2 | A1 | A0 | Destination Register |

|----|----|----|----------------------|

| 0  | 0  | 0  | FREQ0 REG 16 LSBs    |

| 0  | 0  | 1  | FREQ0 REG 16 MSBs    |

| 0  | 1  | 0  | FREQ1 REG 16 LSBs    |

| 0  | 1  | 1  | FREQ1 REG 16 MSBs    |

| 1  | 0  | 0  | PHASE0 REG           |

| 1  | 0  | 1  | PHASE1 REG           |

| 1  | 1  | 0  | PHASE2 REG           |

| 1  | 1  | 1  | PHASE3 REG           |

Figure 19. Addressing the Control Registers

| D15 | D0  |

|-----|-----|

| MSB | LSB |

Figure 20. Frequency Register Bits

| D15 | D14 | D13 | D12 | D11 | D0  |

|-----|-----|-----|-----|-----|-----|

| X   | X   | X   | X   | MSB | LSB |

X = Don't Care

Figure 21. Phase Register Bits

REV. A -9-

### CIRCUIT DESCRIPTION

The AD9830 provides an exciting new level of integration for the RF/Communications system designer. The AD9830 combines the Numerical Controlled Oscillator (NCO), SINE Look-Up table, Frequency and Phase Modulators, and a Digital-to-Analog Converter on a single integrated circuit.

The internal circuitry of the AD9830 consists of three main sections. These are:

Numerical Controlled Oscillator (NCO) + Phase Modulator SINE Look-Up Table

Digital-to-Analog Converter

The AD9830 is a fully integrated Direct Digital Synthesis (DDS) chip. The chip requires one reference clock, two low precision resistors and eight decoupling capacitors to provide digitally created sine waves up to 25 MHz. In addition to the generation of this RF signal, the chip is fully capable of a broad range of simple and complex modulation schemes. These modulation schemes are fully implemented in the digital domain allowing accurate and simple realization of complex modulation algorithms using DSP techniques.

### THEORY OF OPERATION

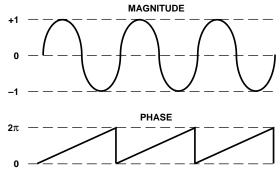

Sine waves are typically thought of in terms of their magnitude form a (t) = sin ( $\omega t$ ). However, these are nonlinear and not easy to generate except through piece wise construction. On the other hand, the angular information is linear in nature. That is, the phase angle rotates through a fixed angle for each unit of time. The angular rate depends on the frequency of the signal by the traditional rate of  $\omega = 2\pi f$

Figure 22. Sine Wave

Knowing that the phase of a sine wave is linear and given a reference interval (clock period), the phase rotation for that period can be determined.

$$\Delta Phase = \omega \delta t$$

Solving for  $\omega$

$$\omega = \Delta P hase / \delta t = 2\pi f$$

Solving for f and substituting the reference clock frequency for the reference period ( $1/f_{MCLK} = \delta t$ )

$$f = \Delta Phase \times f_{MCLK}/2\pi$$

The AD9830 builds the output based on this simple equation. A simple DDS chip can implement this equation with three major subcircuits.

### **Numerical Controlled Oscillator + Phase Modulator**

This consists of two frequency select registers, a phase accumulator and four phase offset registers. The main component of the NCO is a 32-bit phase accumulator which assembles the phase component of the output signal. Continuous time signals have a phase range of 0 to  $2\pi$ . Outside this range of numbers, the sinusoid functions repeat themselves in a periodic manner. The digital implementation is no different. The accumulator simply scales the range of phase numbers into a multibit digital word. The phase accumulator in the AD9830 is implemented with 32 bits. Therefore, in the AD9830,  $2\pi = 2^{32}$ . Likewise, the  $\Delta Phase$  term is scaled into this range of numbers  $0 < \Delta Phase < 2^{32}$  –1. Making these substitutions into the equation above

$$f = \Delta Phase \times f_{MCLK}/2^{32}$$

where  $0 < \Delta Phase < 2^{32}$

With a clock signal of 50 MHz and a phase word of 051EB852 hex

$$f = 51EB852 \times 50 \text{ MHz}/2^{32} = 1.000000000931 \text{ MHz}$$

The input to the phase accumulator (i.e., the phase step) can be selected either from the FREQ0 Register or FREQ1 Register and this is controlled by the FSELECT pin. NCOs inherently generate continuous phase signals, thus avoiding any output discontinuity when switching between frequencies. More complex frequency modulation schemes can be implemented by updating the contents of these registers. This facilitates complex frequency modulation schemes, such as GMSK.

Following the NCO, a phase offset can be added to perform phase modulation using the 12-bit PHASE Registers. The contents of this register are added to the most significant bits of the NCO. The AD9830 has four PHASE registers. The resolution of the phase registers equals  $2\pi/4096.$

### Sine Look-Up Table (LUT)

To make the output useful, the signal must be converted from phase information into a sinusoidal value. Since phase information maps directly into amplitude, a ROM LUT converts the phase information into amplitude. To do this, the digital phase information is used to address a sine ROM LUT. Although the NCO contains a 32-bit phase accumulator, the output of the NCO is truncated to 12 bits. Using the full resolution of the phase accumulator is impractical and unnecessary as this would require a look-up table of  $2^{32}$  entries.

It is necessary only to have sufficient phase resolution in the LUTs such that the dc error of the output waveform is dominated by the quantization error in the DAC. This requires the look-up table to have two more bits of phase resolution than the 10-bit DAC.

### **Digital-to-Analog Converter**

The AD9830 includes a high impedance current source 10-bit DAC, capable of driving a wide range of loads at different speeds. Full-scale output current can be adjusted, for optimum power and external load requirements, through the use of a single external resistor ( $R_{\rm SET}$ ).

full-scale voltage developed across it does not exceed the voltage compliance range. Since full-scale current is controlled by  $R_{\rm SET}$ , adjustments to  $R_{\rm SET}$  can balance changes made to the load resistor. However, if the DAC full-scale output current is significantly less than 20 mA, the linearity of the DAC may degrade.

### **DSP and MPU Interfacing**

The AD9830 has a parallel interface, with 16 bits of data being loaded during each write cycle.

The frequency or phase registers are loaded by asserting the  $\overline{WR}$ signal. The destination register for the 16-bit data is selected using the address inputs A0, A1 and A2. The phase registers are 12 bits wide so, only the 12 LSBs need to be valid—the 4 MSBs of the 16 bit word do not have to contain valid data. Data is loaded into the AD9830 by pulsing WR low, the data being latched into the AD9830 on the rising edge of WR. The values of inputs A0, A1 and A2 are also latched into the AD9830 on the WR rising edge. The appropriate register is updated on the next MCLK rising edge. To ensure that the AD9830 contains valid data at the rising edge of MCLK, the rising edge of the  $\overline{WR}$  pulse should not coincide with the rising MCLK edge. The WR pulse must occur several nanoseconds before the MCLK rising edge. If the  $\overline{WR}$  rising edge occurs at the MCLK rising edge, there is an uncertainty of one MCLK cycle regarding the loading of the destination register—the destination register may be loaded with the new data immediately or the destination register may be updated on the next MCLK rising edge. To avoid any uncertainty, the times listed in the specifications should be complied with.

FSELECT, PSEL0 and PSEL1 are sampled on the MCLK rising edge. Again, these inputs should be valid when an MCLK rising edge occurs as there will be an uncertainty of one MCLK cycle introduced otherwise. When these inputs change value, there will be a pipeline delay before control is transferred to the selected register—there will be a pipeline delay before the analog output is controlled by the selected register. Similarly, there is a delay when a new word is written to a register. PSEL0, PSEL1, FSELECT and  $\overline{\rm WR}$  have latencies of six MCLK cycles.

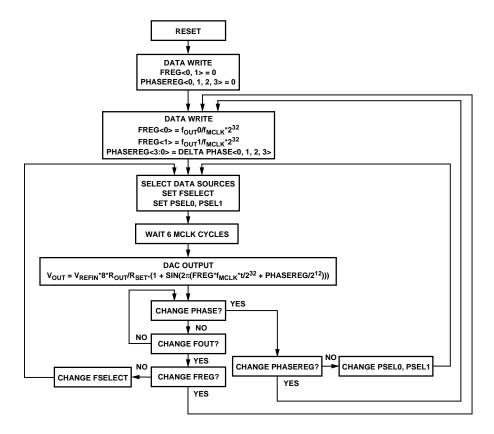

The flow chart in Figure 23 shows the operating routine for the AD9830. When the AD9830 is powered up, the part should be reset using  $\overline{RESET}$ . This will reset the phase accumulator to zero so that the analog output is at midscale.  $\overline{RESET}$  does not reset the phase and frequency registers. These registers will contain invalid data and, therefore, should be set to zero by the user.

The registers to be used should be loaded, the analog output being  $f_{MCLK}/2^{32}\times FREG$  where FREG is the value contained in the selected frequency register. This signal will be phase shifted by an amount  $2\pi/4096\times PHASEREG$  where PHASEREG is the value contained in the selected phase register. When FSELECT, PSEL0 and PSEL1 are programmed, there will be a pipeline delay of approximately 6 MCLK cycles before the analog output reacts to the change on these inputs.

Figure 23. Flow Chart for AD9830 Initialization and Operation

REV. A -11-

### **APPLICATIONS**

The AD9830 contains functions which make it suitable for modulation applications. The part can be used to perform simple modulation such as FSK. More complex modulation schemes such as GMSK and QPSK can also be implemented using the AD9830. In a FSK application, the two frequency registers of the AD9830 are loaded with different values, one frequency will represent the space frequency while the other will represent the mark frequency. The digital data stream is fed to the FSELECT pin which will cause the AD9830 to modulate the carrier frequency between the two values.

The AD9830 has four phase registers which enable the part to perform PSK. With phase shift keying, the carrier frequency is phase shifted, the phase being altered by an amount which is related to the bit stream being input to the modulator. The presence of four shift registers eases the interaction needed between the DSP and the AD9830.

The frequency and phase registers can be written to continuously, if required. The maximum update rate equals the frequency of the MCLK. However, if a selected register is loaded with a new word, there will be a delay of 6 MCLK cycles before the analog output will change accordingly.

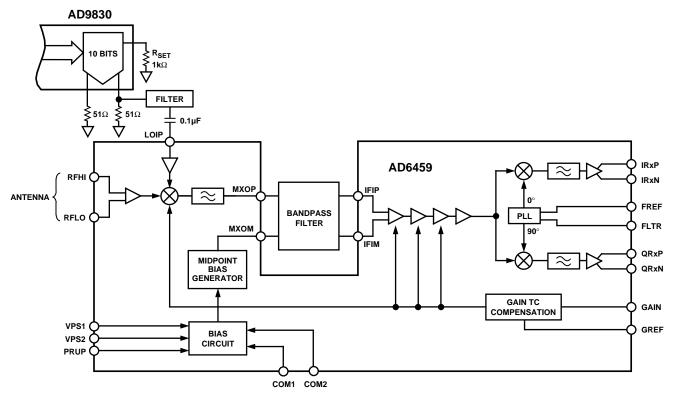

The AD9830 is also suitable for signal generator applications. With its low current consumption, the part is suitable for mobile applications in which it can be used as a local oscillator. Figure 24 shows the interface between the AD9830 and AD6459 which is a down converter used on the receive side of mobile phones or basestations.

Figure 24. AD9830 and AD6459 Receiver Circuit

–12– REV. A

### **Grounding and Layout**

The printed circuit board that houses the AD9830 should be designed so that the analog and digital sections are separated and confined to certain areas of the board. This facilitates the use of ground planes which can be separated easily. A minimum etch technique is generally best for ground planes as it gives the best shielding. Digital and analog ground planes should only be joined in one place. If the AD9830 is the only device requiring an AGND to DGND connection, then the ground planes should be connected at the AGND and DGND pins of the AD9830. If the AD9830 is in a system where multiple devices require AGND to DGND connections, the connection should be made at one point only, a star ground point that should be established as close as possible to the AD9830.

Avoid running digital lines under the device as these will couple noise onto the die. The analog ground plane should be allowed to run under the AD9830 to avoid noise coupling. The power supply lines to the AD9830 should use as large a track as is possible to provide low impedance paths and reduce the effects of glitches on the power supply line. Fast switching signals like clocks should be shielded with digital ground to avoid radiating noise to other sections of the board. Avoid crossover of digital and analog signals. Traces on opposite sides of the board should run at right angles to each other. This will reduce the effects of feedthrough through the board. A microstrip technique is by far the best but is not always possible with a double-sided board. In this technique, the component side of the board is dedicated to ground planes while signals are placed on the other side

Good decoupling is important. The analog and digital supplies to the AD9830 are independent and separately pinned out to minimize coupling between analog and digital sections of the device. All analog and digital supplies should be decoupled to AGND and DGND respectively with 0.1  $\mu$ F ceramic capacitors in parallel with 10  $\mu$ F tantalum capacitors. To achieve the best from the decoupling capacitors, they should be placed as close as possible to the device, ideally right up against the device. In systems where a common supply is used to drive both the AVDD and DVDD of the AD9830, it is recommended that the system's AVDD supply be used. This supply should have the recommended analog supply decoupling between the AVDD pins of the AD9830 and AGND and the recommended digital supply decoupling capacitors between the DVDD pins and DGND.

#### **AD9830 Evaluation Board**

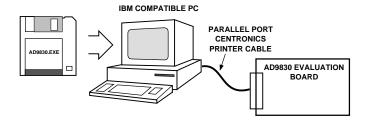

The AD9830 Evaluation Board allows designers to evaluate the high performance AD9830 DDS Modulator with a minimum of effort.

To prove that this device will meet the user's waveform synthesis requirements, the user only requires a +5 V power supply, an IBM-compatible PC and a spectrum analyzer along with the evaluation board. The evaluation setup is shown below.

The DDS Evaluation kit includes a populated, tested AD9830 printed circuit board along with software which controls the AD9830 in a Windows environment.

Figure 25. AD9830 Evaluation Board Setup

### **Using the AD9830 Evaluation Board**

The AD9830 Evaluation kit is a test system designed to simplify the evaluation of the AD9830. Provisions to control the AD9830 from the printer port of an IBM-compatible PC are included along with the necessary software. An application note is also available with the evaluation board which gives information on operating the evaluation board.

### **Prototyping Area**

An area is available on the evaluation board where the user can add additional circuits to the evaluation test set. Users may want to build custom analog filters for the outputs or add buffers and operational amplifiers which are to be used in the final application.

### **XO vs. External Clock**

The AD9830 can operate with master clocks up to 50 MHz. A 50 MHz oscillator is included on the evaluation board. However, this oscillator can be removed and an external CMOS clock connected to the part, if required.

### **Power Supply**

Power to the AD9830 evaluation board must be provided externally through the pin connections. The power leads should be twisted to reduce ground loops.

REV. A -13-

R1-R3

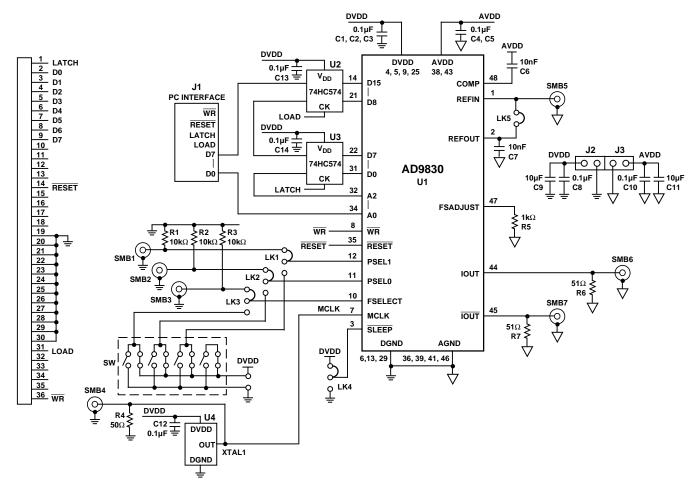

Figure 26. Evaluation Board Layout

| COMPONENT LIST      |                               | Links              |                                |

|---------------------|-------------------------------|--------------------|--------------------------------|

| Integrated Circuits |                               | LK5                | Two Pin Link                   |

| U1                  | AD9830 (48-Pin TQFP)          | LK1, LK2, LK3, LK4 | Three Pin Link                 |

| U2, U3              | 74HC574 Latches               | Switch             |                                |

| XTAL1               | OSC XTAL 50 MHz               | SW                 | End Stackable Switch (SDC      |

| Capacitors          |                               |                    | Double Throw)                  |

| C9, C11             | 10 μF Tantalum Capacitor      | Sockets            |                                |

| C8, C10, C12-C14    | 0.1 μF Ceramic Capacitor      | SMB1-SMB7          | Sub-Miniature BNC Connector    |

| C1-C5               | 0.1 μF Ceramic Chip Capacitor | SIVIDI-SIVIDI      | Sub-ivilliature BIVC Connector |

| C6, C7              | 10 nF Ceramic Capacitor       | Connectors         |                                |

| Resistors           | •                             | J2, J3             | PCB Mounting Terminal Block    |

|                     | 1 hO Desistan                 | J1                 | 36-Pin Edge Connector          |

| R5                  | 1 kΩ Resistor                 |                    | •                              |

| R6, R7              | 51 $\Omega$ Resistor          |                    |                                |

| R4                  | 50 Ω Resistor                 |                    |                                |

$10 \ k\Omega$  Resistor

-14- REV. A

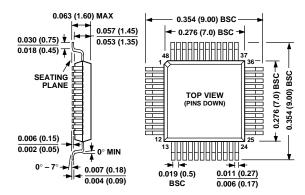

### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

### 48-Lead TQFP (ST-48)

REV. A -15-