# 100 MSPS/140 MSPS Analog Flat Panel Interface

# AD9884A

#### **FEATURES**

140 MSPS Maximum Conversion Rate 500 MHz Analog Bandwidth 0.5 V to 1.0 V Analog Input Range 400 ps p-p PLL Clock Jitter Power-Down Mode 3.3 V Power Supply 2.5 V to 3.3 V Three-State CMOS Outputs Demultiplexed Output Ports Data Clock Output Provided Low Power: 570 mW Typical Internal PLL Generates CLOCK from HSYNC Serial Port Interface Fully Programmable Supports Alternate Pixel Sampling for Higher-Resolution Applications

APPLICATIONS RGB Graphics Processing LCD Monitors and Projectors Plasma Display Panels Scan Converters

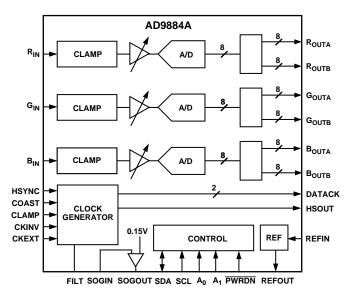

#### FUNCTIONAL BLOCK DIAGRAM

#### **GENERAL DESCRIPTION**

The AD9884A is a complete 8-bit 140 MSPS monolithic analog interface optimized for capturing RGB graphics signals from personal computers and workstations. Its 140 MSPS encode rate capability and full-power analog bandwidth of 500 MHz supports display resolutions of up to  $1280 \times 1024$  (SXGA) at 75 Hz with sufficient input bandwidth to accurately acquire and digitize each pixel.

To minimize system cost and power dissipation, the AD9884A includes an internal +1.25 V reference, PLL to generate a pixel clock from HSYNC, and programmable gain, offset and clamp circuits. The user provides only a +3.3 V power supply, analog input, and HSYNC signals. Three-state CMOS outputs may be powered by a supply between 2.5 V and 3.3 V.

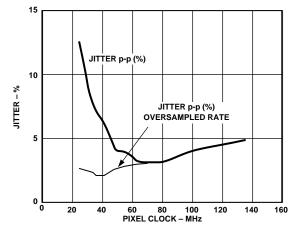

The AD9884A's on-chip PLL generates a pixel clock from the HSYNC input. Pixel clock output frequencies range from

20 MHz to 140 MHz. PLL clock jitter is typically 400 ps p-p relative to the input reference. When the COAST signal is presented, the PLL maintains its output frequency in the absence of HSYNC. A 32-step sampling phase adjustment is provided. Data, HSYNC and Data Clock output phase relationships are always maintained. The PLL can be disabled and an external clock input provided as the pixel clock.

A clamp signal is generated internally or may be provided by the user through the CLAMP input pin. This device is fully programmable via a two-wire serial port.

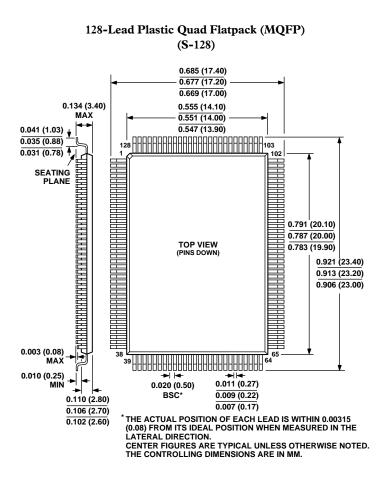

Fabricated in an advanced CMOS process, the AD9884A is provided in a space-saving 128-lead MQFP surface mount plastic package and is specified over a 0°C to +70°C temperature range.

#### REV. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

#

|                                                 |              | Test     |              | 884AKS-1        | 00                 |               | 884AKS-1  | 40                 |                  |

|-------------------------------------------------|--------------|----------|--------------|-----------------|--------------------|---------------|-----------|--------------------|------------------|

| Parameter                                       | Temp         | Level    | Min          | оочако-т<br>Тур | Max                | Min           | тур       | Max                | Unit             |

| RESOLUTION                                      |              |          |              | 8               |                    |               | 8         |                    | Bits             |

| DC ACCURACY                                     |              |          |              |                 |                    |               |           |                    |                  |

| Differential Nonlinearity                       | +25°C        | Ι        |              | $\pm 0.5$       | $\pm 1.0$          |               | ±0.5      | +1.15/-1.0         | LSB              |

|                                                 | Full         | VI       |              |                 | $\pm 1.0$          |               |           | +1.25/-1.0         | LSB              |

| Integral Nonlinearity                           | +25°C        | Ι        |              | $\pm 0.5$       | ±1.25              |               | $\pm 0.8$ | $\pm 1.4$          | LSB              |

|                                                 | Full         | VI       | -            | _               | ±1.75              | -             |           | $\pm 2.5$          | LSB              |

| No Missing Codes                                | Full         | VI       | Gı           | aranteed        |                    | Gı            | aranteed  |                    |                  |

| ANALOG INPUT                                    |              |          |              |                 |                    |               |           |                    |                  |

| Input Voltage Range                             |              |          |              |                 |                    |               |           |                    |                  |

| Minimum                                         | Full         | VI       |              |                 | 0.5                |               |           | 0.5                | V p-p            |

| Maximum                                         | Full         | VI       | 1.0          |                 |                    | 1.0           |           |                    | V p-p            |

| Gain Tempco                                     | +25°C        | V        |              | 100             |                    |               | 280       |                    | ppm/°C           |

| Input Bias Current                              | +25°C        | I        |              |                 | 1                  |               |           | 1                  | μA               |

|                                                 | Full         | VI       |              | -               | 1                  |               | _         | 1                  | μA               |

| Input Offset Voltage                            | Full         | VI       |              | 7               | 50                 |               | 7         | 50                 | mV               |

| Input Full-Scale Matching                       | Full         | VI<br>VI | 22           | 1.5             | 5.0<br>25          | 22            | 1.5       | 5.0<br>25          | %FS              |

| Offset Adjustment Range                         | Full         | VI       | 22           | 23.5            | 25                 | 22            | 23.5      | 25                 | %FS              |

| REFERENCE OUTPUT                                |              |          |              |                 |                    |               |           |                    |                  |

| Output Voltage                                  | Full         | VI       | +1.20        | +1.25           | +1.30              | +1.20         | +1.25     | +1.30              | V                |

| Temperature Coefficient                         | Full         | V        |              | ±50             |                    |               | ±50       |                    | ppm/°C           |

| SWITCHING PERFORMANCE                           |              |          |              |                 |                    |               |           |                    |                  |

| Maximum Conversion Rate                         | Full         | VI       | 100          |                 |                    | 140           |           |                    | MSPS             |

| Minimum Conversion Rate                         | Full         | IV       |              |                 | 10                 |               |           | 10                 | MSPS             |

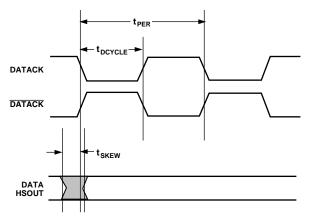

| Data to Clock Skew, t <sub>SKEW</sub>           | Full         | IV       | -0.5         |                 | +2.0               | -0.5          |           | +2.0               | ns               |

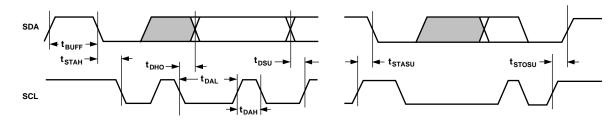

| t <sub>BUFF</sub>                               | Full         | VI       | 4.7          |                 |                    | 4.7           |           |                    | μs               |

| t <sub>STAH</sub>                               | Full         | VI       | 4.0          |                 |                    | 4.0           |           |                    | μs               |

| t <sub>DHO</sub>                                | Full         | VI       | 0            |                 |                    | 0             |           |                    | μs               |

| t <sub>DAL</sub>                                | Full         | VI       | 4.7          |                 |                    | 4.7           |           |                    | μs               |

| t <sub>DAH</sub>                                | Full         | VI       | 4.0          |                 |                    | 4.0           |           |                    | μs               |

| t <sub>DSU</sub>                                | Full         | VI       | 250          |                 |                    | 250           |           |                    | ns               |

| t <sub>STASU</sub>                              | Full         | VI       | 4.7          |                 |                    | 4.7           |           |                    | μs               |

| t <sub>STOSU</sub>                              | Full         | VI       | 4.0          |                 | 110                | 4.0           |           | 110                | μs               |

| HSYNC Input Frequency<br>Maximum PLL Clock Rate | Full<br>Full | IV<br>VI | 15<br>100    |                 | 110                | 15            |           | 110                | kHz<br>MHz       |

| Minimum PLL Clock Rate                          | Full         | IV<br>IV | 100          |                 | 20                 | 140           |           | 20                 | MHZ              |

| PLL Jitter                                      | +25°C        | IV       |              | 400             | $\frac{20}{700^1}$ |               | 475       | $\frac{20}{750^2}$ |                  |

| I LL JILLEI                                     | Full         | IV       |              | 100             | $1000^{1}$         |               | 115       | $1000^{2}$         | ps p-p<br>ps p-p |

| Sampling Phase Tempco                           | Full         | IV       |              | 15              | 1000               |               | 15        | 1000               | ps p p<br>ps/°C  |

| DIGITAL INPUTS                                  |              |          |              |                 |                    |               |           |                    | -                |

| Input Voltage, High (V <sub>IH</sub> )          | Full         | VI       | 2.5          |                 |                    | 2.5           |           |                    | v                |

| Input Voltage, Low (V <sub>II</sub> )           | Full         | VI       | 2.5          |                 | 0.8                | 2.5           |           | 0.8                | v                |

| Input Current, High (I <sub>IH</sub> )          | Full         | VI       |              |                 | -1.0               |               |           | -1.0               | μA               |

| Input Current, Low (I <sub>IL</sub> )           | Full         | VI       |              |                 | 1.0                |               |           | 1.0                | μΑ               |

| Input Capacitance                               | +25°C        | v        |              | 3               |                    |               | 3         |                    | pF               |

| DIGITAL OUTPUTS                                 |              |          |              |                 |                    |               |           |                    |                  |

| Output Voltage, High (V <sub>OH</sub> )         | Full         | VI       | $V_{DD} - 0$ | 1               |                    | $V_{DD} - 0.$ | 1         |                    | v                |

| Output Voltage, Low (V <sub>OL</sub> )          | Full         | VI<br>VI | • DD - 0.    |                 | 0.1                | * DD - 0.     |           | 0.1                | V                |

| Duty Cycle                                      | 1 ull        | * 1      |              |                 | 0.1                |               |           | 0.1                |                  |

| DATACK, DATACK                                  | Full         | IV       | 45           | 50              | 55                 | 45            | 50        | 55                 | %                |

|                                                 |              | <b></b>  | <b>*</b> -   | ~~              |                    | · · ·         | ~~        | ~ ~ ~              |                  |

|                                                                |       | Test  | AD   | 9884AKS- | 100  | AD   | 9884AKS- | 140  |      |

|----------------------------------------------------------------|-------|-------|------|----------|------|------|----------|------|------|

| Parameter                                                      | Temp  | Level | Min  | Тур      | Max  | Min  | Тур      | Max  | Unit |

| POWER SUPPLY                                                   |       |       |      |          |      |      |          |      |      |

| V <sub>D</sub> Supply Voltage                                  | Full  | IV    | 3.0  | 3.3      | 3.6  | 3.0  | 3.3      | 3.6  | V    |

| V <sub>DD</sub> Supply Voltage                                 | Full  | IV    | 2.2  | 3.3      | 3.6  | 2.2  | 3.3      | 3.6  | V    |

| PV <sub>D</sub> Supply Voltage                                 | Full  | IV    | 3.0  | 3.3      | 3.6  | 3.0  | 3.3      | 3.6  | V    |

| I <sub>D</sub> Supply Current (V <sub>D</sub> )                | +25°C | V     |      | 125      |      |      | 135      |      | mA   |

| I <sub>DD</sub> Supply Current (V <sub>DD</sub> ) <sup>3</sup> | +25°C | V     |      | 33       |      |      | 47       |      | mA   |

| IPV <sub>D</sub> Supply Current (PV <sub>D</sub> )             | +25°C | V     |      | 15       |      |      | 15       |      | mA   |

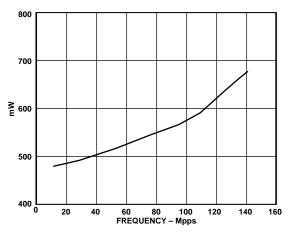

| Total Power Dissipation                                        | Full  | VI    |      | 570      | 675  |      | 650      | 775  | mW   |

| Power-Down Supply Current                                      | Full  | VI    |      | 2.0      | 25   |      | 2.0      | 25   | mA   |

| Power-Down Dissipation                                         | Full  | VI    |      | 6.6      | 82.5 |      | 6.6      | 82.5 | mW   |

| DYNAMIC PERFORMANCE                                            |       |       |      |          |      |      |          |      |      |

| Analog Bandwidth, Full Power                                   | +25°C | V     |      | 500      |      |      | 500      |      | MHz  |

| Transient Response                                             | +25°C | V     |      | 2        |      |      | 2        |      | ns   |

| Overvoltage Recovery Time                                      | +25°C | V     |      | 1.5      |      |      | 1.5      |      | ns   |

| Signal-to-Noise Ratio (SNR) <sup>4</sup>                       | +25°C | I     | 44.0 | 46.5     |      | 43.5 | 46.2     |      | dB   |

| (Without Harmonics)                                            | Full  | V     |      | 46.0     |      |      | 45.0     |      | dB   |

| $f_{IN} = 40.7 \text{ MHz}$                                    |       |       |      |          |      |      |          |      |      |

| Crosstalk                                                      | Full  | V     |      | 60       |      |      | 60       |      | dBc  |

| THERMAL CHARACTERISTICS                                        |       |       |      |          |      |      |          |      |      |

| $\theta_{IC}$ -Junction-to-Case                                |       |       |      |          |      |      |          |      |      |

| Thermal Resistance                                             |       | V     |      | 8.4      |      |      | 8.4      |      | °C/W |

| $\theta_{IA}$ –Junction-to-Ambient                             |       |       |      |          |      |      |          |      |      |

| Thermal Resistance                                             |       | V     |      | 35       |      |      | 35       |      | °C/W |

NOTES

<sup>1</sup>VCORNGE = 01, CURRENT = 001, PLLDIV = 1693<sub>10</sub>.

$^{2}$ VCORNGE = 10, CURRENT = 110, PLLDIV =  $1600_{10}$ .

<sup>3</sup>DEMUX = 1; DATACK and  $\overline{DATACK}$  load = 15 pF; Data load = 5 pF.

<sup>4</sup>Using external pixel clock.

Specifications subject to change without notice.

#### **ORDERING GUIDE**

| Model         | Temperature<br>Range | Package<br>Description | Package<br>Option |

|---------------|----------------------|------------------------|-------------------|

| AD9884AKS-140 |                      |                        | S-128             |

| AD9884AKS-100 | 0°C to +70°C         | MQFP                   | S-128             |

| AD9884A/PCB   | +25°C                | Evaluation Board       |                   |

#### EXPLANATION OF TEST LEVELS Test Level

- I. 100% production tested.

- II. 100% production tested at +25°C and sample tested at specified temperatures.

- III. Sample tested only.

- IV. Parameter is guaranteed by design and characterization testing.

- V. Parameter is a typical value only.

- VI. 100% production tested at +25°C; guaranteed by design and characterization testing.

#### **ABSOLUTE MAXIMUM RATINGS<sup>\*</sup>**

| $V_D$ , $PV_D$                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------|

| $PV_D$ to $V_D$ $\pm 0.5 V$                                                                                                       |

| $V_{DD}$                                                                                                                          |

| Analog Inputs $\dots \dots \dots$ |

| <b>REFIN</b>                                                                                                                      |

| Digital Inputs V <sub>D</sub> to 0.0 V                                                                                            |

| Digital Output Current 20 mA                                                                                                      |

| Operating Temperature                                                                                                             |

| Storage Temperature                                                                                                               |

| Maximum Junction Temperature +175°C                                                                                               |

| Maximum Case Temperature +150°C                                                                                                   |

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions outside of those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD9884A features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

| Signal Type      | Name                                                                                                                                                                  | Function                                                                                                                                                                                                                   | Value                                                                            | Package Pin                                                                                                                                                                                                                            |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inputs           | R <sub>AIN</sub>                                                                                                                                                      | Analog Input for RED Channel                                                                                                                                                                                               | 0.5 V to 1.0 V FS                                                                | 7                                                                                                                                                                                                                                      |

|                  | G <sub>AIN</sub>                                                                                                                                                      | Analog Input for GREEN Channel                                                                                                                                                                                             | 0.5 V to 1.0 V FS                                                                | 15                                                                                                                                                                                                                                     |

|                  | B <sub>AIN</sub>                                                                                                                                                      | Analog Input for BLUE Channel                                                                                                                                                                                              | 0.5 V to 1.0 V FS                                                                | 22                                                                                                                                                                                                                                     |

|                  | HSYNC                                                                                                                                                                 | Horizontal Sync Input                                                                                                                                                                                                      | 3.3 V CMOS                                                                       | 40                                                                                                                                                                                                                                     |

|                  | COAST                                                                                                                                                                 | Clock Generator Coast Input (Optional)                                                                                                                                                                                     | 3.3 V CMOS                                                                       | 41                                                                                                                                                                                                                                     |

|                  | CLAMP                                                                                                                                                                 | External Clamp Input (Optional)                                                                                                                                                                                            | 3.3 V CMOS                                                                       | 28                                                                                                                                                                                                                                     |

|                  | SOGIN                                                                                                                                                                 | Sync On Green Slicer Input (Optional)                                                                                                                                                                                      | 0.5 V to 1.0 V FS                                                                | 14                                                                                                                                                                                                                                     |

|                  | CKEXT                                                                                                                                                                 | External Clock Input (Optional)                                                                                                                                                                                            | 3.3 V CMOS                                                                       | 44                                                                                                                                                                                                                                     |

|                  | CKINV                                                                                                                                                                 | Sampling Clock Inversion (Optional)                                                                                                                                                                                        | 3.3 V CMOS                                                                       | 27                                                                                                                                                                                                                                     |

| Outputs          | $\begin{array}{c} D_{R}A_{7\text{-}0} \\ D_{R}B_{7\text{-}0} \\ D_{G}A_{7\text{-}0} \\ D_{G}B_{7\text{-}0} \\ D_{B}A_{7\text{-}0} \\ D_{B}B_{7\text{-}0} \end{array}$ | Data Output, Red Channel, Port A<br>Data Output, Red Channel, Port B<br>Data Output, Green Channel, Port A<br>Data Output, Green Channel, Port B<br>Data Output, Blue Channel, Port A<br>Data Output, Blue Channel, Port B | 3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS<br>3.3 V CMOS | 105–112<br>95–102<br>85–92<br>75–82<br>65–72<br>55–62                                                                                                                                                                                  |

|                  | DATACK                                                                                                                                                                | Data Output Clock                                                                                                                                                                                                          | 3.3 V CMOS                                                                       | 115                                                                                                                                                                                                                                    |

|                  | DATACK                                                                                                                                                                | Data Output Clock Complement                                                                                                                                                                                               | 3.3 V CMOS                                                                       | 116                                                                                                                                                                                                                                    |

|                  | HSOUT                                                                                                                                                                 | Horizontal Sync Output                                                                                                                                                                                                     | 3.3 V CMOS                                                                       | 117                                                                                                                                                                                                                                    |

|                  | SOGOUT                                                                                                                                                                | Sync On Green Slicer Output                                                                                                                                                                                                | 3.3 V CMOS                                                                       | 118                                                                                                                                                                                                                                    |

| Control          | SDA                                                                                                                                                                   | Serial Data I/O                                                                                                                                                                                                            | 3.3 V CMOS                                                                       | 29                                                                                                                                                                                                                                     |

|                  | SCL                                                                                                                                                                   | Serial Interface Clock                                                                                                                                                                                                     | 3.3 V CMOS                                                                       | 30                                                                                                                                                                                                                                     |

|                  | A <sub>0</sub> , A <sub>1</sub>                                                                                                                                       | Serial Port Address LSBs                                                                                                                                                                                                   | 3.3 V CMOS                                                                       | 31, 32                                                                                                                                                                                                                                 |

|                  | PWRDN                                                                                                                                                                 | Power-Down Control Input                                                                                                                                                                                                   | 3.3 V CMOS                                                                       | 125                                                                                                                                                                                                                                    |

| Analog Interface | REFOUT<br>REFIN<br>FILT                                                                                                                                               | Internal Reference Output<br>Reference Input<br>External Filter Connection                                                                                                                                                 | +1.25 V<br>+1.25 V ± 10%                                                         | 126<br>127<br>45                                                                                                                                                                                                                       |

| Power Supply     | V <sub>D</sub><br>V <sub>DD</sub><br>PV <sub>D</sub><br>GND                                                                                                           | Main Power Supply<br>Digital Output Power Supply<br>Clock Generator Power Supply<br>Ground                                                                                                                                 | 3.3 V ± 10%<br>2.5 V to 3.3 V ± 10%<br>3.3 V ± 10%<br>0 V                        | 4, 8, 10, 11, 16, 18, 19, 23, 25,<br>124, 128<br>54, 64, 74, 84, 94, 104, 114, 120<br>33, 34, 43, 48, 50<br>5, 6, 9, 12, 13, 17, 20, 21, 24, 26,<br>35, 39, 42, 47, 49, 51, 52, 53, 63,<br>73, 83, 93, 103, 113, 119, 121,<br>122, 123 |

| No Connect       | NC                                                                                                                                                                    |                                                                                                                                                                                                                            |                                                                                  | 1-3, 36-38, 46                                                                                                                                                                                                                         |

#### Table I. Package Interconnections

#### PIN CONFIGURATION

| PIN FUNCTION DESCRIPTIONS |

|---------------------------|

|---------------------------|

| Pin Name                                                           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

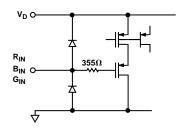

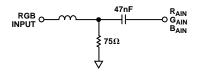

| INPUTS<br>R <sub>AIN</sub><br>G <sub>AIN</sub><br>B <sub>AIN</sub> | Analog Input for RED Channel<br>Analog Input for GREEN Channel<br>Analog Input for BLUE Channel<br>High impedance inputs that accepts the RED, GREEN, and BLUE channel graphics signals, respectively. The<br>three channels are identical, and can be used for any colors, but colors are assigned for convenient reference. They<br>accommodate input signals ranging from 0.5 V to 1.0 V full scale. Signals should be ac-coupled to these pins to<br>support clamp operation.                                                                                                                                                                                                                                                                                                          |

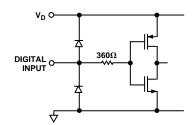

| HSYNC                                                              | Horizontal Sync Input<br>This input receives a logic signal that establishes the horizontal timing reference and provides the frequency refer-<br>ence for pixel clock generation. The logic sense of this pin is controlled by HSPOL. Only the <i>leading</i> edge of<br>HSYNC is active. When HSPOL = 0, the falling edge of HSYNC is used. When HSPOL = 1, the rising edge is<br>active. The input includes a Schmitt trigger for noise immunity, with a nominal input threshold of 1.5 V.<br>Electrostatic Discharge (ESD) protection diodes will conduct heavily if this pin is driven more than 0.5 V above<br>the 3.3 V power supply (or more than 0.5 V below ground). If a 5 V signal source is driving this pin, the signal<br>should be clamped or current limited.             |

| COAST                                                              | Clock Generator Coast Input (optional)<br>This input may be used to cause the pixel clock generator to stop synchronizing with HSYNC and continue pro-<br>ducing a clock at its present frequency and phase. This is useful when processing sources that fail to produce hori-<br>zontal sync pulses when in the vertical interval. The COAST signal is generally NOT required for PC-generated<br>signals. The logic sense of this pin is controlled by CSTPOL. COAST may be asserted at any time. When not<br>used, this pin must be grounded and CSTPOL programmed to 1. CSTPOL defaults to 1 at power-up.                                                                                                                                                                              |

| CLAMP                                                              | External Clamp Input (optional)<br>This logic input may be used to define the time during which the input signal is clamped to ground, establishing a<br>black reference. It should be exercised when a black signal is known to be present on the analog input channels,<br>typically during the back porch period of the graphics signal. The CLAMP pin is enabled by setting control bit<br>EXTCLMP to 1 (default power-up is 0). When disabled, this pin is ignored and the clamp timing is determined<br>internally by counting a delay and duration from the trailing edge of the HSYNC input. The logic sense of this pin<br>is controlled by CLAMPOL. When not used, this pin must be grounded and EXTCLMP programmed to 0.                                                        |

| SOGIN                                                              | Sync On Green Slicer Input (optional)<br>This input is provided to assist in processing signals with embedded sync, typically on the GREEN channel. The<br>pin is connected to a high speed comparator with an internally-generated threshold of 0.15 V. When connected to<br>a dc-coupled graphics signal with embedded sync, it will produce a noninverting digital output on SOGOUT that<br>changes state whenever the input signal crosses 0.15 V. This is usually a composite sync signal, containing both<br>vertical and horizontal sync information that must be separated before passing the horizontal sync signal to HSYNC.<br>The SOG slicer comparator continues to operate when the AD9884A is put into a power-down state. When not<br>used, this input should be grounded. |

| CKEXT                                                              | External Clock Input (optional)<br>This pin may be used to provide an external clock to the AD9884A, in place of the clock internally-generated from<br>HSYNC. This input is enabled by programming EXTCLK to 1. When an external clock is used, all other internal<br>functions operate normally. When unused, this pin should be tied through a 10 k $\Omega$ resistor to GROUND, and<br>EXTCLK programmed to 0. The clock phase adjustment still operates when an external clock source is used.                                                                                                                                                                                                                                                                                        |

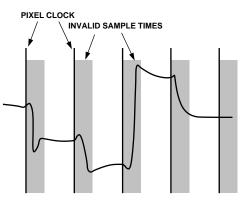

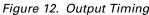

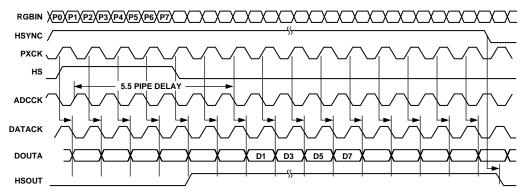

| CKINV                                                              | Sampling Clock Inversion (optional)<br>This pin may be used to invert the pixel sampling clock, which has the effect of shifting the sampling phase<br>180 degrees. This is in support of Alternate Pixel Sampling mode, wherein higher frequency input signals (up to<br>280 Mpps) may be captured by first sampling the odd pixels, then capturing the even pixels on the subsequent<br>frame. This pin should be exercised only during blanking intervals (typically vertical blanking) as it may produce<br>several samples of corrupted data during the phase shift. CKINV should be grounded when not used.                                                                                                                                                                          |

| Pin Name              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUTPUTS               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $D_RA_{7-0}$          | Data Output, Red Channel, Port A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $D_R B_{7-0}$         | Data Output, Red Channel, Port B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $D_GA_{7-0}$          | Data Output, Green Channel, Port A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $D_G B_{7-0}$         | Data Output, Green Channel, Port B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $D_BA_{7-0}$          | Data Output, Blue Channel, Port A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

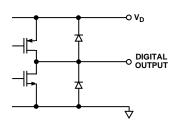

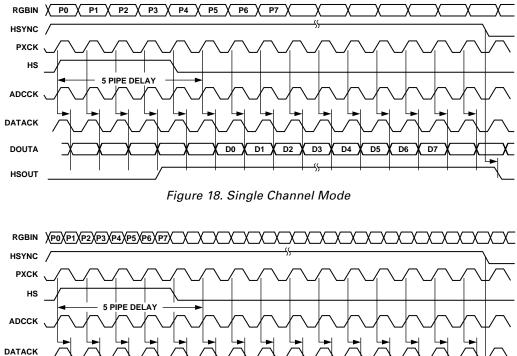

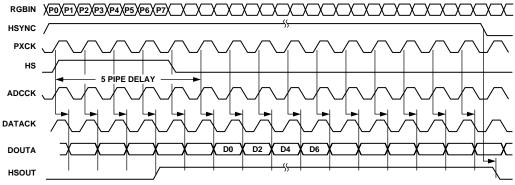

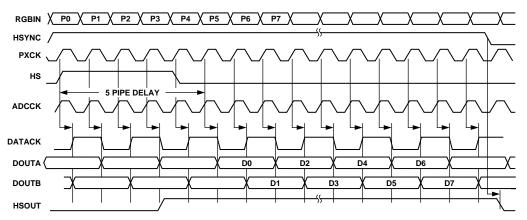

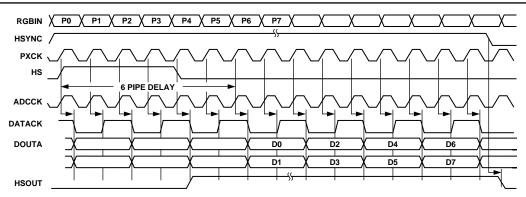

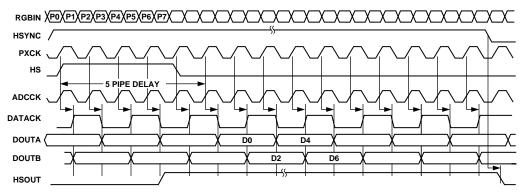

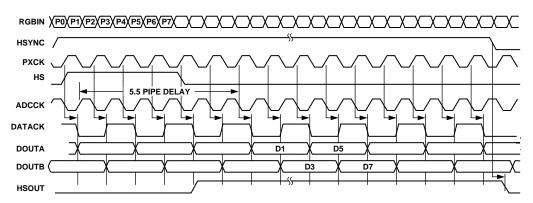

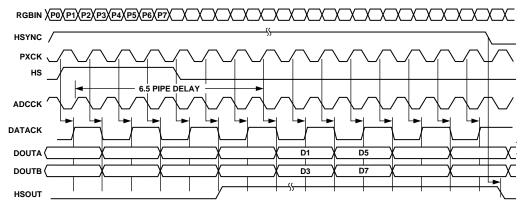

| $D_BB_{7-0}$          | Data Output, Blue Channel, Port B<br>The main data outputs. Bit 7 is the MSB. Each channel has two ports. When the part is operated in Single Chan-<br>nel mode (DEMUX = 0), all data are presented to Port A, and Port B is placed in a high impedance state. Pro-<br>gramming DEMUX to 1 establishes Dual Channel mode, wherein alternate pixels are presented to Port A and<br>Port B of each channel. These will appear simultaneously, two pixels presented at the time of every second input<br>pixel, when PAR is set to 1 (parallel mode). When PAR = 0, pixel data appear alternately on the two ports, one<br>new sample with each incoming pixel (interleaved mode). In Dual Channel mode, the first pixel sampled after<br>HSYNC is routed to Port A. The second pixel goes to Port B, the third to A, etc. The delay from pixel sampling<br>time to output is fixed. When the sampling time is changed by adjusting the PHASE register, the output timing is<br>shifted as well. The DATACK, DATACK and HSOUT outputs are also moved, so the timing relationship among<br>the signals is maintained. |

| DATACK<br>DATACK      | Data Output Clock<br>Data Output Clock Complement<br>Differential data clock output signals to be used to strobe the output data and HSOUT into external logic. They<br>are produced by the internal clock generator and are synchronous with the internal pixel sampling clock. When the<br>AD9884A is operated in Single Channel mode, the output frequency is equal to the pixel sampling frequency.<br>When operating in Dual Channel mode, the Data Output Clock and the Output Data are presented at one-half the<br>pixel rate. When the sampling time is changed by adjusting the PHASE register, the output timing is shifted as<br>well. The Data, DATACK, DATACK and HSOUT outputs are all moved, so the timing relationship among the<br>signals is maintained. Either or both signals may be used, depending on the timing mode and interface design<br>employed.                                                                                                                                                                                                                                    |

| HSOUT                 | Horizontal Sync Output<br>A reconstructed and phase-aligned version of the HSYNC input. This signal is always active HIGH. By maintain-<br>ing alignment with DATACK, DATACK, and Data, data timing with respect to horizontal sync can always be<br>clearly determined.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SOGOUT                | Sync On Green Slicer Output<br>The output of the Sync On Green slicer comparator. When SOGIN is presented with a dc-coupled ground-referenced<br>analog graphics signal containing composite sync, SOGOUT will produce a digital composite sync signal. This<br>signal gets no other processing on the AD9884A. The SOG slicer comparator continues to operate when the<br>AD9884A is put into a power-down state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

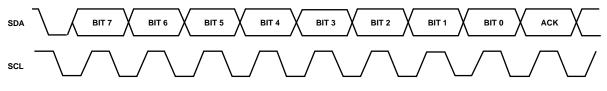

| <b>CONTROL</b><br>SDA | Serial Data I/O<br>Bidirectional data port for the serial interface port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SCL                   | Serial Interface Clock<br>Clock input for the serial interface port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| A <sub>1-0</sub>      | Serial Port Address LSBs<br>The two least significant bits of the serial port address are set by the logic levels on these pins. Connect a pin to<br>ground to set the address bit to 0. Tie it HIGH (to $V_D$ through 10 k $\Omega$ ) to set the address bit to 1. Using these pins,<br>the serial address may be set to any value from 98h to 9Fh. Up to four AD9884As may be used on the same serial<br>bus by appropriately setting these bits. They can also be used to change the AD9884A address if a conflict is found<br>with another device on the bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PWRDN                 | Power-Down Control Input<br>Bringing this pin LOW puts the AD9884A into a very low power dissipation mode. The output buffers are placed<br>in a high impedance state. The clock generator is stopped. The control register contents are maintained. The Sync<br>On Green Slicer (SOGOUT) and internal reference continue to function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### PIN FUNCTION DESCRIPTIONS (Continued)

| Pin Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANALOG INT      | TERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| REFOUT          | Internal Reference Output<br>Output from the internal 1.25 V bandgap reference. This output is intended to drive relatively light loads. It can<br>drive the AD9884A Reference input directly, but should be externally buffered if it is used to drive other loads as<br>well. The absolute accuracy of this output is $\pm 4\%$ , and the temperature coefficient is $\pm 50$ ppm, which is adequate<br>for most AD9884A applications. If higher accuracy is required, an external reference may be employed. If an exter-<br>nal reference is used, tie this pin to ground through a 0.1 µF capacitor. |

| REFIN           | Reference Input<br>The reference input accepts the master reference voltage for all AD9884A internal circuitry (+1.25 V $\pm$ 10%). It<br>may be driven directly by the REFOUT pin. Its high impedance presents a very light load to the reference source.<br>This pin should be bypassed to Ground with a 0.1 $\mu$ F capacitor.                                                                                                                                                                                                                                                                         |

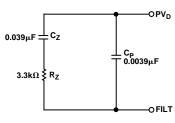

| FILT            | External Filter Connection<br>For proper operation, the pixel clock generator PLL requires an external filter. Connect the filter shown in <i>Figure</i><br>10 to this pin. For optimal performance, minimize noise and parasitics on this node.                                                                                                                                                                                                                                                                                                                                                          |

| POWER SUP       | PLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>D</sub>  | Main Power Supply<br>These pins supply power to the main elements of the circuit. It should be as quiet and filtered as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>DD</sub> | Digital Output Power Supply<br>A large number of output pins (up to 52) switching at high speed (up to 140 MHz) generates a lot of power supply<br>transients (noise). These supply pins are identified separately from the $V_D$ pins so special care can be taken to<br>minimize output noise transferred into the sensitive analog circuitry. If the AD9884A is interfacing with lower-<br>voltage logic, $V_{DD}$ may be connected to a lower supply voltage (as low as 2.5 V) for compatibility.                                                                                                     |

| PV <sub>D</sub> | Clock Generator Power Supply<br>The most sensitive portion of the AD9884A is the clock generation circuitry. These pins provide power to the<br>clock PLL and help the user design for optimal performance. The designer should provide "quiet," noise-free<br>power to these pins.                                                                                                                                                                                                                                                                                                                       |

| GND             | Ground<br>The ground return for all circuitry on chip. It is recommended that the AD9884A be assembled on a single solid<br>ground plane, with careful attention to ground current paths. See the Design Guide for details.                                                                                                                                                                                                                                                                                                                                                                               |

#### CONTROL REGISTER MAP

The AD9884A is initialized and controlled by a set of registers that determine the operating modes. An external controller is employed to write and read the control registers through the 2-line serial interface port.

#### Table II. Control Register Map

| Reg  | Bit    | Default         | Mnemonic | Function                    |

|------|--------|-----------------|----------|-----------------------------|

| PLL  | Divi   | der Contro      | ol       |                             |

| 00   | 7-0    | 01101001        | PLLDIVM  | PLL Divide Ratio MSBs       |

| 01   | 7–4    | 1101••••        | PLLDIVL  | PLL Divide Ratio LSBs       |

| 01   | 3–0    | ••••0000        |          | Reserved, Set to Zero       |

| Inpu | t Ga   | in              |          |                             |

| 02   |        | 1000000         | REDGAIN  | Red Channel Gain Adjust     |

| 03   | 7–0    | 10000000        | GRNGAIN  | Green Channel Gain Adjust   |

| 04   | 7–0    | 10000000        | BLUGAIN  | Blue Channel Gain Adjust    |

| Inpu | t Of   | fset            |          |                             |

| 05   | 7–2    | 100000••        | REDOFST  | Red Channel Offset Adjust   |

| 05   | 1-0    | •••••00         |          | Reserved, Set to Zero       |

| 06   | 7–2    | 100000••        | GRNOFST  | Green Channel Offset Adjust |

| 06   | 1–0    | •••••00         |          | Reserved, Set to Zero       |

| 07   | 7–2    | 100000••        | BLUOFST  | Blue Channel Offset Adjust  |

| 07   | 1–0    | •••••00         |          | Reserved, Set to Zero       |

| Clan | np T   | iming           |          |                             |

| 08   | 7-0    | 1000000         | CLPLACE  | Clamp Placement             |

| 09   | 7–0    | 10000000        | CLDUR    | Clamp Duration              |

| Gen  | eral ( | Control 1       |          |                             |

| 0A   | 7      | 1 • • • • • • • | DEMUX    | Output Port Select          |

| 0A   | 6      | •1•••••         | PAR      | Output Timing Select        |

| 0A   | 5      | ••1••••         | HSPOL    | HSYNC Polarity              |

| 0A   | 4      | •••1••••        | CSTPOL   | COAST Polarity              |

| 0A   | 3      | •••0•••         | EXTCLMP  | Clamp Signal Source         |

| 0A   | 2      | •••••1••        | CLAMPOL  | Clamp Signal Polarity       |

| 0A   | 1      | ••••••0•        | EXTCLK   | External Clock Select       |

| 0A   | 0      | ••••••0         |          | Reserved, Set to Zero       |

| Cloc | k Ge   | nerator Co      | ontrol   |                             |

| 0B   | 7–3    | 10000•••        | PHASE    | Clock Phase Adjust          |

| 0B   | 2–0    | •••••000        |          | Reserved, Set to Zero       |

| 0C   | 7      | 0•••••          |          | Reserved, Set to Zero       |

| 0C   | 6–5    | •01••••         | VCORNGE  | VCO Range Select            |

| 0C   | 4–2    | •••001••        | CURRENT  | Charge Pump Current         |

| 0C   | 1–0    | •••••00         |          | Reserved, Set to Zero       |

| Gen  | eral   | Control 2       |          |                             |

| 0D   | 7–5    | 000             |          | Reserved, Set to Zero       |

| 0D   | 4      | •••0••••        | OUTPHASE | Output Port Phase           |

| 0D   | 3–1    | ••••000•        | REVID    | Die Revision ID             |

| 0D   | 0      | ••••••0         |          | Reserved, Set to Zero       |

| 0E   | 7–0    | 00000000        |          | Reserved, Set to Zero       |

Table III. Default Register Values

| Reg | Value     |     | Reg | Value       |     |

|-----|-----------|-----|-----|-------------|-----|

| 00  | 01101001  | 69h | 08  | 1000000     | 80h |

| 01  | 1101 0000 | D0h | 09  | 10000000    | 80h |

| 02  | 10000000  | 80h | 0A  | 11110100    | F4h |

| 03  | 10000000  | 80h | 0B  | 10000 000   | 80h |

| 04  | 10000000  | 80h | 0C  | 0 01 001 00 | 24h |

| 05  | 100000 00 | 80h | 0D  | 00000000    | 00h |

| 06  | 100000 00 | 80h | 0E  | 0000xxx0    | 0xh |

| 07  | 100000 00 | 80h | 0F  | 00000000    | 00h |

#### CONTROL REGISTER DETAIL PLL DIVIDER CONTROL

| 00 7-0 PLLDIVM PLL Divide Ratio MSBs |

|--------------------------------------|

|--------------------------------------|

The eight most significant bits of the 12-bit PLL divide ratio PLLDIV. *The operational divide ratio is PLLDIV* + 1.

The PLL derives a master clock from an incoming HSYNC signal. The master clock frequency is then divided by an integer value, and the divider's output is phase-locked to HSYNC. This PLLDIV value determines the number of pixel times (pixels plus horizontal blanking overhead) per line. This is typically 20% to 30% more than the number of active pixels in the display.

The 12-bit value of PLLDIV supports divide ratios from 2 to 4095. The higher the value loaded in this register, the higher the resulting clock frequency with respect to a fixed HSYNC frequency.

VESA has established some standard timing specifications, which will assist in determining the value for PLLDIV as a function of horizontal and vertical display resolution and frame rate (Table VII). However, many computer systems do not conform precisely to the recommendations, and these numbers should be used only as a guide. The display system manufacturer should provide automatic or manual means for optimizing PLLDIV. An incorrectly set PLLDIV will usually produce one or more vertical noise bars on the display. The greater the error, the greater the number of bars produced.

The power-up default value of PLLDIV is 1693 (PLLDIVM = 69h, PLLDIVL = Dxh).

| 01 7-4 PLLDIVL PLL Divide Ratio LSBs |

|--------------------------------------|

|--------------------------------------|

The four least significant bits of the 12-bit PLL divide ratio PLLDIV. *The operational divide ratio is PLLDIV* + 1.

The power-up default value of PLLDIV is 1693 (PLLDIVM = 69h, PLLDIVL = Dxh).

#### INPUT GAIN

| 02 | 7-0 | REDGAIN | Red Channel Gain Adjust |

|----|-----|---------|-------------------------|

|----|-----|---------|-------------------------|

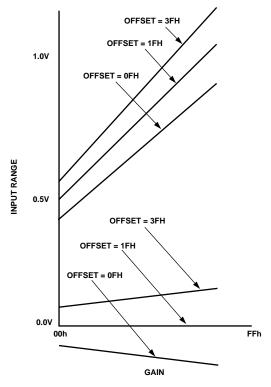

An 8-bit word that sets the gain of the RED channel. The AD9884A can accommodate input signals with a full-scale range of between 0.5 V and 1.0 V p-p. Setting REDGAIN to 255 corresponds to an input range of 1.0 V. A REDGAIN of 0 establishes an input range of 0.5 V. Note that *increasing* REDGAIN results in the picture having *less* contrast (the input signal uses fewer of the available converter codes). See Figure 8.

The power-up default value is REDGAIN = 80h.

| 03 7–0 GRNGAIN Green C | hannel Gain Adjust |

|------------------------|--------------------|

|------------------------|--------------------|

An 8-bit word that sets the gain of the GREEN channel. See REDGAIN (02).

The power-up default value is GRNGAIN = 80h.

| 04 7–0 BLUGAIN Blue Channel Ga | n Adjust |

|--------------------------------|----------|

|--------------------------------|----------|

An 8-bit word that sets the gain of the BLUE channel. See REDGAIN (02).

The power-up default value is BLUGAIN = 80h.

#### INPUT OFFSET

| 0. | 5 | 7–2 | REDOFST | Red Channel Offset Adjust |

|----|---|-----|---------|---------------------------|

|----|---|-----|---------|---------------------------|

A six-bit offset binary word that sets the dc offset of the RED channel.

One LSB of offset adjustment equals approximately one LSB change in the ADC offset. Therefore, the absolute magnitude of the offset adjustment scales as the gain of the channel is changed (Figure 9). A nominal setting of 31 results in the channel nominally clamping the back porch (during the clamping interval) to code 00. An offset setting of 63 results in the channel clamping to code 31 of the ADC. An offset setting of 0 clamps to code -31 (off the bottom of the range). Increasing the value of REDOFST decreases the brightness of the channel.

The power-up default value is REDOFST = 80h.

| 06 | 7–2 | GRNOFST | Green Channel Offset Adjust |

|----|-----|---------|-----------------------------|

|----|-----|---------|-----------------------------|

A six-bit offset binary word that sets the dc offset of the GREEN channel. See REDOFST (05).

The power-up default value is GRNOFST = 80h.

A six-bit offset binary word that sets the DC offset of the GREEN channel. See REDOFST (05).

The power-up default value is BLUOFST = 80h.

#### CLAMP TIMING

| 08 7-0 | CLPLACE | Clamp Placement |

|--------|---------|-----------------|

|--------|---------|-----------------|

An 8-bit register that sets the position of the internally generated clamp.

When EXTCLMP = 0, a clamp signal is generated internally, at a position established by CLPLACE and for a duration set by CLDUR. Clamping is started CLPLACE pixel periods after the trailing edge of HSYNC. CLPLACE may be programmed to any value between 1 and 255. CLPLACE = 0 is not supported.

The clamp should be placed during a time that the input signal presents a stable black-level reference, usually the back porch period between HSYNC and the image. A value of 08h will usually work.

When EXTCLMP = 1, this register is ignored.

The power-up default value is CLPLACE = 80h.

| 09 7-0 CLDUR Clamp Duration |

|-----------------------------|

|-----------------------------|

An 8-bit register that sets the duration of the internally generated clamp.