# Precision Low Noise, Low Input Bias Current Operational Amplifiers

# OP1177/OP2177/OP4177

#### **FEATURES**

Low offset voltage: 60 µV maximum

Very low offset voltage drift: 0.7  $\mu$ V/°C maximum

Low input bias current: 2 nA maximum

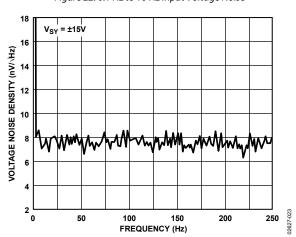

Low noise: 8 nV/√Hz typical

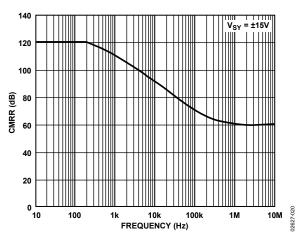

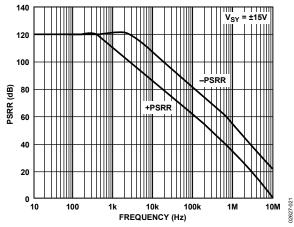

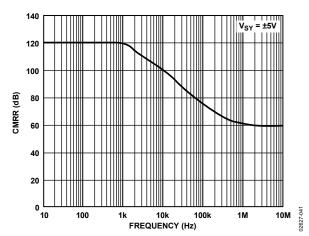

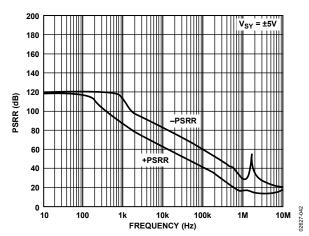

CMRR, PSRR, and  $A_{VO}$  > 120 dB minimum Low supply current: 400  $\mu$ A per amplifier Dual supply operation:  $\pm 2.5$  V to  $\pm 15$  V

Unity gain stable No phase reversal

Inputs internally protected beyond supply voltage

#### **APPLICATIONS**

Wireless base station control circuits

Optical network control circuits

Instrumentation

Sensors and controls

Thermocouples

Resistor thermal detectors (RTDs)

Strain bridges

Shunt current measurements

Precision filters

#### **GENERAL DESCRIPTION**

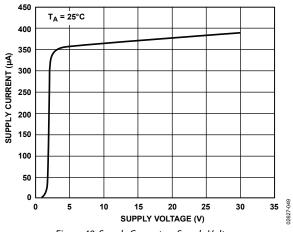

The OPx177 family consists of very high precision, single, dual, and quad amplifiers featuring extremely low offset voltage and drift, low input bias current, low noise, and low power consumption. Outputs are stable with capacitive loads of over 1000 pF with no external compensation. Supply current is less than 500  $\mu A$  per amplifier at 30 V. Internal 500  $\Omega$  series resistors protect the inputs, allowing input signal levels several volts beyond either supply without phase reversal.

Unlike previous high voltage amplifiers with very low offset voltages, the OP1177 and OP2177 are available in a tiny MSOP 8-lead surface-mount package, and the OP4177 is available in a 14-lead TSSOP. Moreover, specified performance in the MSOP and the TSSOP is identical to performance in the SOIC package.

The OPx177 family offers the widest specified temperature range of any high precision amplifier in surface-mount

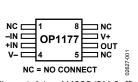

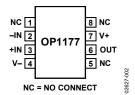

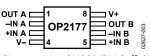

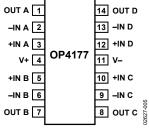

#### **PIN CONFIGURATIONS**

Figure 1. 8-Lead MSOP (RM-Suffix)

Figure 2. 8-Lead SOIC\_N (R-Suffix)

Figure 3. 8-Lead MSOP (RM-Suffix)

Figure 4. 8-Lead SOIC\_N (R-Suffix)

Figure 5. 14-Lead SOIC\_N (R-Suffix)

Figure 6. 14-Lead TSSOP (RU-Suffix)

packaging. All versions are fully specified for operation from  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  for the most demanding operating environments.

Applications for these amplifiers include precision diode power measurement, voltage and current level setting, and level detection in optical and wireless transmission systems. Additional applications include line-powered and portable instrumentation and controls—thermocouple, RTD, strain-bridge, and other sensor signal conditioning—and precision filters.

The OP1177 (single) and the OP2177 (dual) amplifiers are available in 8-lead MSOP and 8-lead narrow SOIC packages. The OP4177 (quad) is available in 14-lead TSSOP and 14-lead narrow SOIC packages. MSOP and TSSOP are available in tape and reel only.

# **TABLE OF CONTENTS**

| Features                                 | Overload Recovery Time                         |

|------------------------------------------|------------------------------------------------|

| Applications                             | THD + Noise                                    |

| Pin Configurations                       | Capacitive Load Drive                          |

| General Description                      | Stray Input Capacitance Compensation           |

| Revision History                         | Reducing Electromagnetic Interference          |

| Specifications                           | Proper Board Layout                            |

| Electrical Characteristics               | Difference Amplifiers                          |

| Absolute Maximum Ratings                 | A High Accuracy Thermocouple Amplifier         |

| Thermal Resistance                       | Low Power Linearized RTD                       |

| ESD Caution5                             | Single Operational Amplifier Bridge            |

| Typical Performance Characteristics      | Realization of Active Filters                  |

| Functional Description                   | Band-Pass KRC or Sallen-Key Filter21           |

| Total Noise-Including Source Resistors14 | Channel Separation21                           |

| Gain Linearity14                         | References on Noise Dynamics and Flicker Noise |

| Input Overvoltage Protection             | Outline Dimensions                             |

| Output Phase Reversal                    | Ordering Guide                                 |

| Settling Time                            |                                                |

| REVISION HISTORY                         |                                                |

| 7/06—Rev. C to Rev. D                    | 4/02—Rev. A to Rev. B                          |

| Changes to Table 45                      | Added OP4177Global                             |

| Changes to Figure 51                     | Edits to Specifications2                       |

| Changes to Figure 52                     | Edits to Electrical Characteristics Headings4  |

| Changes to Figure 54                     | Edits to Ordering Guide4                       |

| Changes to Figure 58 to Figure 61        | •                                              |

| Changes to Figure 62 and Figure 63       | 11/01—Rev. 0 to Rev. A                         |

| Changes to Figure 64                     | Edit to Features1                              |

| Changes to Figure 65 and Figure 66       | Edits to TPC 65                                |

| Changes to Figure 67 and Figure 68       | FIG.1. Design of Later LV and a                |

| Removed SPICE Model Section              | 7/01—Revision 0: Initial Version               |

| Updated Outline Dimensions               |                                                |

| Changes to Ordering Guide                |                                                |

| 4/04—Rev. B to Rev. C                    |                                                |

| Changes to Ordering Guide 4              |                                                |

| Changes to TPC 65                        |                                                |

| Changes to TPC 26                        |                                                |

| Updated Outline Dimensions               |                                                |

### **SPECIFICATIONS**

$V_{\text{S}} = \pm 5.0$  V,  $V_{\text{CM}} = 0$  V,  $T_{\text{A}} = 25^{\circ}\text{C}$  , unless otherwise noted.

Table 1.

| Parameter                    | Symbol               | Conditions                                                             | Min  | Typ <sup>1</sup> | Max  | Unit     |

|------------------------------|----------------------|------------------------------------------------------------------------|------|------------------|------|----------|

| INPUT CHARACTERISTICS        |                      |                                                                        |      |                  |      |          |

| Offset Voltage               |                      |                                                                        |      |                  |      |          |

| OP1177                       | Vos                  |                                                                        |      | 15               | 60   | μV       |

| OP2177/OP4177                | Vos                  |                                                                        |      | 15               | 75   | μV       |

| OP1177/OP2177                | Vos                  | -40°C < T <sub>A</sub> < +125°C                                        |      | 25               | 100  | μV       |

| OP4177                       | Vos                  | -40°C < T <sub>A</sub> < +125°C                                        |      | 25               | 120  | μV       |

| Input Bias Current           | I <sub>B</sub>       | -40°C < T <sub>A</sub> < +125°C                                        | -2   | +0.5             | +2   | nA       |

| Input Offset Current         | los                  | -40°C < T <sub>A</sub> < +125°C                                        | -1   | +0.2             | +1   | nA       |

| Input Voltage Range          |                      |                                                                        | -3.5 |                  | +3.5 | V        |

| Common-Mode Rejection Ratio  | CMRR                 | $V_{CM} = -3.5 \text{ V to } +3.5 \text{ V}$                           | 120  | 126              |      | dB       |

|                              |                      | -40°C < T <sub>A</sub> < +125°C                                        | 118  | 125              |      | dB       |

| Large Signal Voltage Gain    | Avo                  | $R_L = 2 k\Omega$ , $V_O = -3.5 V to +3.5 V$                           | 1000 | 2000             |      | V/mV     |

| Offset Voltage Drift         |                      |                                                                        |      |                  |      |          |

| OP1177/OP2177                | ΔV <sub>os</sub> /ΔT | -40°C < T <sub>A</sub> < +125°C                                        |      | 0.2              | 0.7  | μV/°C    |

| OP4177                       | ΔV <sub>os</sub> /ΔT | -40°C < T <sub>A</sub> < +125°C                                        |      | 0.3              | 0.9  | μV/°C    |

| OUTPUT CHARACTERISTICS       |                      |                                                                        |      |                  |      |          |

| Output Voltage High          | V <sub>OH</sub>      | $I_L = 1 \text{ mA}, -40^{\circ}\text{C} < T_A < +125^{\circ}\text{C}$ | +4   | +4.1             |      | V        |

| Output Voltage Low           | V <sub>OL</sub>      | $I_L = 1 \text{ mA}, -40^{\circ}\text{C} < T_A < +125^{\circ}\text{C}$ |      | -4.1             | -4   | V        |

| Output Current               | Іоит                 | V <sub>DROPOUT</sub> < 1.2 V                                           |      | ±10              |      | mA       |

| POWER SUPPLY                 |                      |                                                                        |      |                  |      |          |

| Power Supply Rejection Ratio |                      |                                                                        |      |                  |      |          |

| OP1177                       | PSRR                 | $V_S = \pm 2.5 \text{ V to } \pm 15 \text{ V}$                         | 120  | 130              |      | dB       |

|                              |                      | -40°C < T <sub>A</sub> < +125°C                                        | 115  | 125              |      | dB       |

| OP2177/OP4177                | PSRR                 | $V_S = \pm 2.5 \text{ V to } \pm 15 \text{ V}$                         | 118  | 121              |      | dB       |

|                              |                      | -40°C < T <sub>A</sub> < +125°C                                        | 114  | 120              |      | dB       |

| Supply Current per Amplifier | I <sub>SY</sub>      | $V_0 = 0 V$                                                            |      | 400              | 500  | μΑ       |

|                              |                      | -40°C < T <sub>A</sub> < +125°C                                        |      | 500              | 600  | μA       |

| DYNAMIC PERFORMANCE          |                      |                                                                        |      |                  |      | Ť.       |

| Slew Rate                    | SR                   | $R_L = 2 k\Omega$                                                      |      | 0.7              |      | V/µs     |

| Gain Bandwidth Product       | GBP                  |                                                                        |      | 1.3              |      | MHz      |

| NOISE PERFORMANCE            |                      |                                                                        |      |                  |      |          |

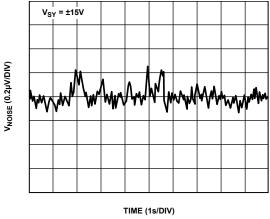

| Voltage Noise                | e <sub>n</sub> p-p   | 0.1 Hz to 10 Hz                                                        |      | 0.4              |      | μV p-p   |

| Voltage Noise Density        | e <sub>n</sub>       | f = 1 kHz                                                              |      | 7.9              | 8.5  | nV/√Hz   |

| Current Noise Density        | in                   | f = 1 kHz                                                              |      | 0.2              |      | pA/√Hz   |

| MULTIPLE AMPLIFIERS CHANNEL  |                      |                                                                        |      |                  |      | <b>†</b> |

| SEPARATION                   | Cs                   | DC                                                                     |      | 0.01             |      | μV/V     |

|                              |                      | f = 100 kHz                                                            |      | -120             |      | dB       |

<sup>&</sup>lt;sup>1</sup> Typical values cover all parts within one standard deviation of the average value. Average values given in many competitor data sheets as "typical" give unrealistically low estimates for parameters that can have both positive and negative values.

### **ELECTRICAL CHARACTERISTICS**

$V_{\text{S}}=\pm 15$  V,  $V_{\text{CM}}=0$  V,  $T_{\text{A}}=25^{\circ}\text{C},$  unless otherwise noted.

Table 2.

| Parameter                    | Symbol                   | Conditions                                                             | Min   | Typ <sup>1</sup> | Max   | Unit   |

|------------------------------|--------------------------|------------------------------------------------------------------------|-------|------------------|-------|--------|

| INPUT CHARACTERISTICS        |                          |                                                                        |       |                  |       |        |

| Offset Voltage               |                          |                                                                        |       |                  |       |        |

| OP1177                       | Vos                      |                                                                        |       | 15               | 60    | μV     |

| OP2177/OP4177                | Vos                      |                                                                        |       | 15               | 75    | μV     |

| OP1177/OP2177                | Vos                      | -40°C < T <sub>A</sub> < +125°C                                        |       | 25               | 100   | μV     |

| OP4177                       | $V_{OS}$                 | $-40^{\circ}\text{C} < \text{T}_{A} < +125^{\circ}\text{C}$            |       | 25               | 120   | μV     |

| Input Bias Current           | I <sub>B</sub>           | -40°C < T <sub>A</sub> < +125°C                                        | -2    | +0.5             | +2    | nA     |

| Input Offset Current         | los                      | -40°C < T <sub>A</sub> < +125°C                                        | -1    | +0.2             | +1    | nA     |

| Input Voltage Range          |                          |                                                                        | -13.5 |                  | +13.5 | V      |

| Common-Mode Rejection Ratio  | CMRR                     | $V_{CM} = -13.5 \text{ V to } +13.5 \text{ V},$                        |       |                  |       |        |

|                              |                          | -40°C < T <sub>A</sub> < +125°C                                        | 120   | 125              |       | dB     |

| Large Signal Voltage Gain    | Avo                      | $R_L = 2 k\Omega$ , $V_O = -13.5 V to +13.5 V$                         | 1000  | 3000             |       | V/mV   |

| Offset Voltage Drift         |                          |                                                                        |       |                  |       |        |

| OP1177/OP2177                | $\Delta V_{OS}/\Delta T$ | -40°C < T <sub>A</sub> < +125°C                                        |       | 0.2              | 0.7   | μV/°C  |

| OP4177                       | $\Delta V_{OS}/\Delta T$ | -40°C < T <sub>A</sub> < +125°C                                        |       | 0.3              | 0.9   | μV/°C  |

| OUTPUT CHARACTERISTICS       |                          |                                                                        |       |                  |       |        |

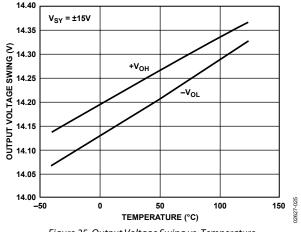

| Output Voltage High          | Vон                      | $I_L = 1 \text{ mA}, -40^{\circ}\text{C} < T_A < +125^{\circ}\text{C}$ | +14   | +14.1            |       | V      |

| Output Voltage Low           | V <sub>OL</sub>          | $I_L = 1 \text{ mA}, -40^{\circ}\text{C} < T_A < +125^{\circ}\text{C}$ |       | -14.1            | -14   | V      |

| Output Current               | Іоит                     | V <sub>DROPOUT</sub> < 1.2 V                                           |       | ±10              |       | mA     |

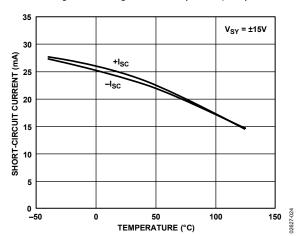

| Short-Circuit Current        | I <sub>sc</sub>          |                                                                        |       | ±35              |       | mA     |

| POWER SUPPLY                 |                          |                                                                        |       |                  |       |        |

| Power Supply Rejection Ratio |                          |                                                                        |       |                  |       |        |

| OP1177                       | PSRR                     | $V_S = \pm 2.5 \text{ V to } \pm 15 \text{ V}$                         | 120   | 130              |       | dB     |

|                              |                          | -40°C < T <sub>A</sub> < +125°C                                        | 115   | 125              |       | dB     |

| OP2177/OP4177                | PSRR                     | $V_S = \pm 2.5 \text{ V to } \pm 15 \text{ V}$                         | 118   | 121              |       | dB     |

|                              |                          | -40°C < T <sub>A</sub> < +125°C                                        | 114   | 120              |       | dB     |

| Supply Current per Amplifier | I <sub>SY</sub>          | $V_O = 0 V$                                                            |       | 400              | 500   | μΑ     |

|                              |                          | -40°C < T <sub>A</sub> < +125°C                                        |       | 500              | 600   | μΑ     |

| DYNAMIC PERFORMANCE          |                          |                                                                        |       |                  |       |        |

| Slew Rate                    | SR                       | $R_L = 2 k\Omega$                                                      |       | 0.7              |       | V/µs   |

| Gain Bandwidth Product       | GBP                      |                                                                        |       | 1.3              |       | MHz    |

| NOISE PERFORMANCE            |                          |                                                                        |       |                  |       |        |

| Voltage Noise                | e <sub>n</sub> p-p       | 0.1 Hz to 10 Hz                                                        |       | 0.4              |       | μV p-p |

| Voltage Noise Density        | en                       | f = 1 kHz                                                              |       | 7.9              | 8.5   | nV/√Hz |

| Current Noise Density        | İn                       | f = 1 kHz                                                              |       | 0.2              |       | pA/√Hz |

| MULTIPLE AMPLIFIERS CHANNEL  |                          |                                                                        |       |                  |       |        |

| SEPARATION                   | Cs                       | DC                                                                     |       | 0.01             |       | μV/V   |

|                              |                          | f = 100 kHz                                                            |       | -120             |       | dB     |

<sup>&</sup>lt;sup>1</sup> Typical values cover all parts within one standard deviation of the average value. Average values given in many competitor data sheets as "typical" give unrealistically low estimates for parameters that can have both positive and negative values.

### **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Parameter                            | Rating               |

|--------------------------------------|----------------------|

| Supply Voltage                       | 36 V                 |

| Input Voltage                        | $V_{S-}$ to $V_{S+}$ |

| Differential Input Voltage           | ±Supply Voltage      |

| Storage Temperature Range            |                      |

| R, RM, and RU Packages               | −65°C to +150°C      |

| Operating Temperature Range          |                      |

| OP1177/OP2177/OP4177                 | -40°C to +125°C      |

| Junction Temperature Range           |                      |

| R, RM, and RU Packages               | −65°C to +150°C      |

| Lead Temperature, Soldering (10 sec) | 300°C                |

|                                      |                      |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

**Table 4. Thermal Resistance**

| Package Type                    | θ <sub>JA</sub> | θ <sub>JC</sub> | Unit |

|---------------------------------|-----------------|-----------------|------|

| 8-Lead MSOP (RM-8) <sup>1</sup> | 190             | 44              | °C/W |

| 8-Lead SOIC_N (R-8)             | 158             | 43              | °C/W |

| 14-Lead SOIC_N (R-14)           | 120             | 36              | °C/W |

| 14-Lead TSSOP (RU-14)           | 240             | 43              | °C/W |

<sup>&</sup>lt;sup>1</sup> MSOP is only available in tape and reel.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

### TYPICAL PERFORMANCE CHARACTERISTICS

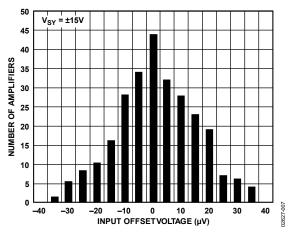

Figure 7. Input Offset Voltage Distribution

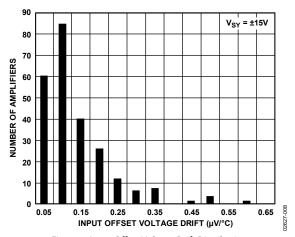

Figure 8. Input Offset Voltage Drift Distribution

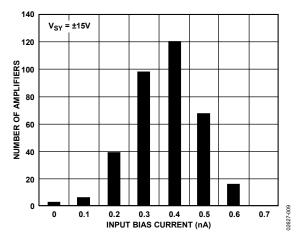

Figure 9. Input Bias Current Distribution

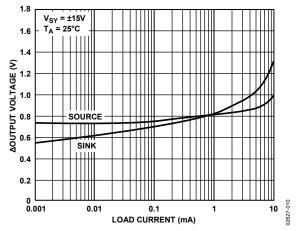

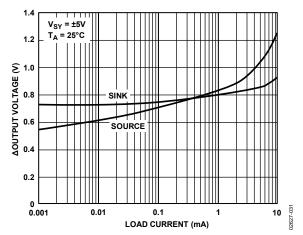

Figure 10. Output Voltage to Supply Rail vs. Load Current

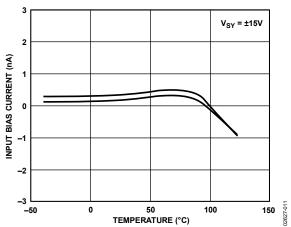

Figure 11. Input Bias Current vs. Temperature

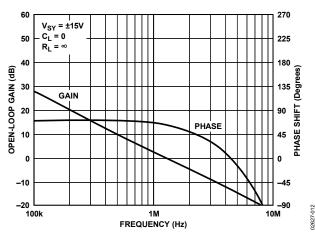

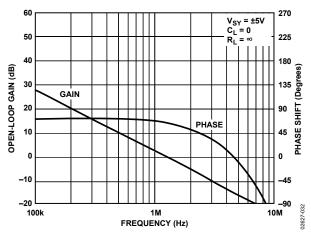

Figure 12. Open-Loop Gain and Phase Shift vs. Frequency

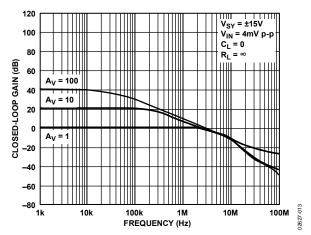

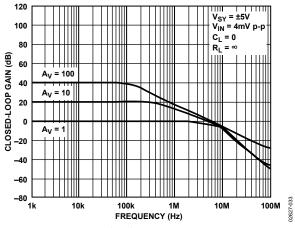

Figure 13. Closed-Loop Gain vs. Frequency

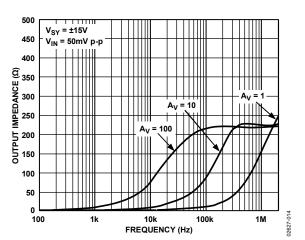

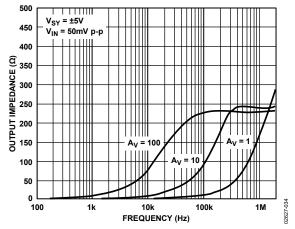

Figure 14. Output Impedance vs. Frequency

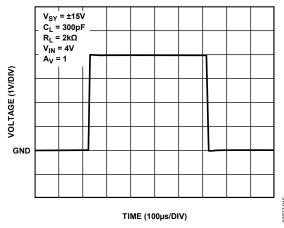

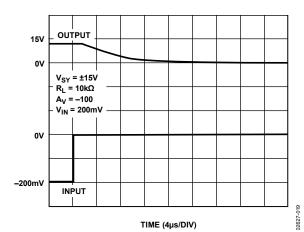

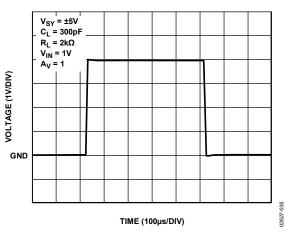

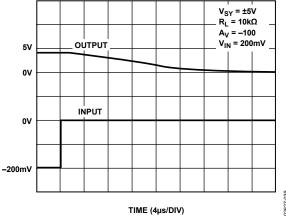

Figure 15. Large Signal Transient Response

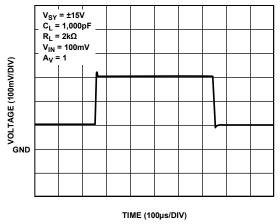

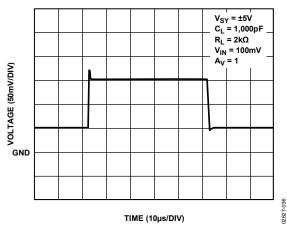

Figure 16. Small Signal Transient Response

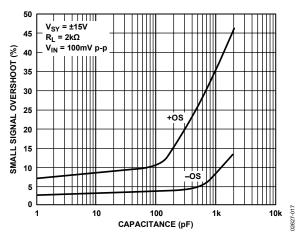

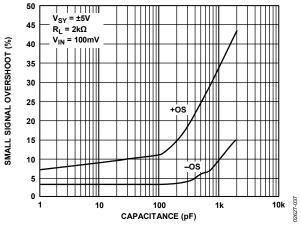

Figure 17. Small Signal Overshoot vs. Load Capacitance

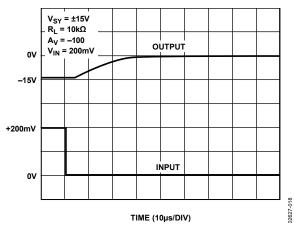

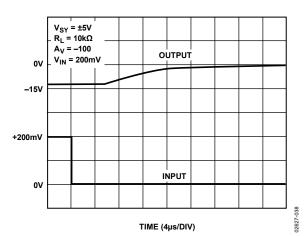

Figure 18. Positive Overvoltage Recovery

Figure 19. Negative Overvoltage Recovery

Figure 20. CMRR vs. Frequency

Figure 21. PSRR vs. Frequency

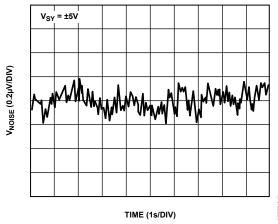

Figure 22. 0.1 Hz to 10 Hz Input Voltage Noise

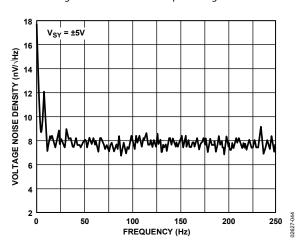

Figure 23. Voltage Noise Density vs. Frequency

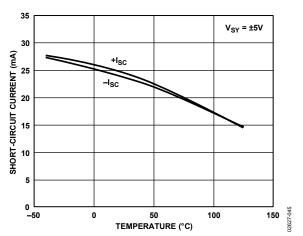

Figure 24. Short-Circuit Current vs. Temperature

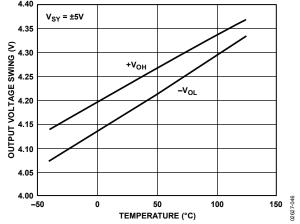

Figure 25. Output Voltage Swing vs. Temperature

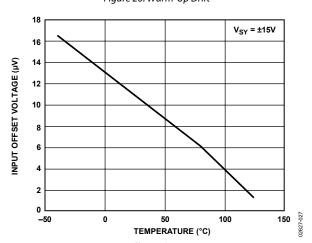

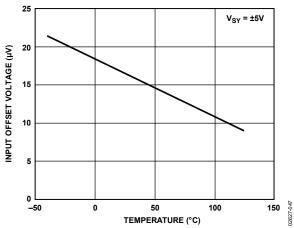

${\it Figure~27. Input~Offset~Voltage~vs.}~ Temperature$

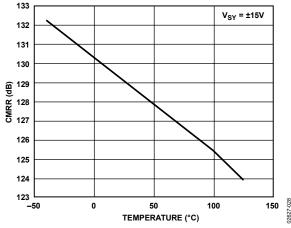

Figure 28. CMRR vs. Temperature

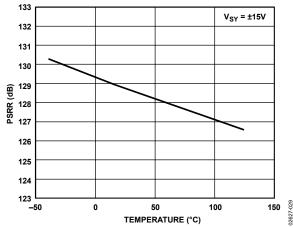

Figure 29. PSRR vs. Temperature

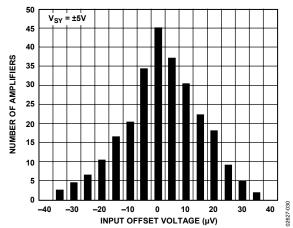

Figure 30. Input Offset Voltage Distribution

Figure 31. Output Voltage to Supply Rail vs. Load Current

Figure 32. Open-Loop Gain and Phase Shift vs. Frequency

Figure 33. Closed-Loop Gain vs. Frequency

Figure 34. Output Impedance vs. Frequency

Figure 35. Large Signal Transient Response

Figure 36. Small Signal Transient Response

Figure 37. Small Signal Overshoot vs. Load Capacitance

Figure 38. Positive Overvoltage Recovery

Figure 39. Negative Overvoltage Recovery

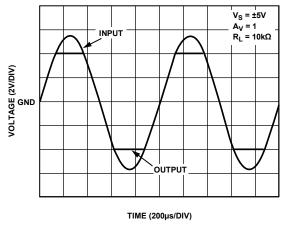

Figure 40. No Phase Reversal

Figure 41. CMRR vs. Frequency

Figure 42. PSRR vs. Frequency

Figure 43. 0.1 Hz to 10 Hz Input Voltage Noise

Figure 44. Voltage Noise Density vs. Frequency

Figure 45. Short-Circuit Current vs. Temperature

Figure 46. Output Voltage Swing vs. Temperature

Figure 47. Input Offset Voltage vs. Temperature

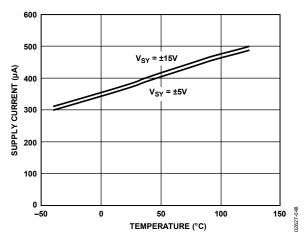

Figure 48. Supply Current vs. Temperature

Figure 49. Supply Current vs. Supply Voltage

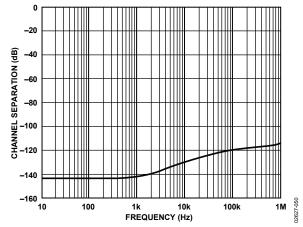

Figure 50. Channel Separation vs. Frequency

### FUNCTIONAL DESCRIPTION

The OPx177 series is the fourth generation of Analog Devices, Inc., industry-standard OP07 amplifier family. OPx177 is a very high precision, low noise operational amplifier with the highly desirable combination of extremely low offset voltage and very low input bias currents. Unlike JFET amplifiers, the low bias and offset currents are relatively insensitive to ambient temperatures, even up to 125°C.

For the first time, Analog Devices proprietary process technology and linear design expertise have produced a high voltage amplifier with superior performance to the OP07, OP77, and OP177 in a tiny MSOP 8-lead package. Despite its small size, the OPx177 offers numerous improvements, including low wideband noise, very wide input and output voltage range, lower input bias current, and complete freedom from phase inversion.

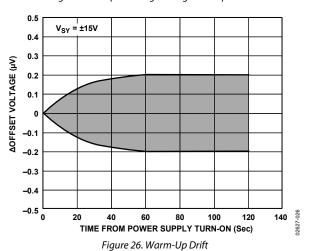

OPx177 has the widest specified operating temperature range of any similar device in a plastic surface-mount package. This is increasingly important as PC board and overall system sizes continue to shrink, causing internal system temperatures to rise. Power consumption is reduced by a factor of four from the OP177, and bandwidth and slew rate increase by a factor of two. The low power dissipation and very stable performance vs. temperature also act to reduce warm-up drift errors to insignificant levels.

Open-loop gain linearity under heavy loads is superior to competitive parts, such as the OPA277, improving dc accuracy and reducing distortion in circuits with high closed-loop gains. Inputs are internally protected from overvoltage conditions referenced to either supply rail.

Like any high performance amplifier, maximum performance is achieved by following appropriate circuit and PC board guidelines. The following sections provide practical advice on getting the most out of the OPx177 under a variety of application conditions.

#### TOTAL NOISE-INCLUDING SOURCE RESISTORS

The low input current noise and input bias current of the OPx177 make it useful for circuits with substantial input source resistance. Input offset voltage increases by less than 1  $\mu V$ maximum per 500  $\Omega$  of source resistance.

The total noise density of the OPx177 is

$$e_{n,TOTAL} = \sqrt{e_n^2 + (i_n R_S)^2 + 4kTR_S}$$

where:

$e_n$  is the input voltage noise density.  $i_n$  is the input current noise density.  $R_S$  is the source resistance at the noninverting terminal. *k* is Boltzmann's constant (1.38 ×  $10^{-23}$  J/K). T is the ambient temperature in Kelvin ( $T = 273 + {}^{\circ}\text{C}$ ).

For  $R_S < 3.9 \text{ k}\Omega$ ,  $e_n$  dominates and

$$e_{n,TOTAL} \approx e_n$$

For 3.9 k $\Omega$  <  $R_S$  < 412 k $\Omega$ , voltage noise of the amplifier, current noise of the amplifier translated through the source resistor, and thermal noise from the source resistor all contribute to the total

For  $R_s > 412 \text{ k}\Omega$ , the current noise dominates and

$$e_{n,TOTAL} \approx i_n R_S$$

The total equivalent rms noise over a specific bandwidth is expressed as

$$E_n = \left(e_{n, TOTAL}\right) \sqrt{BW}$$

where BW is the bandwidth in Hertz.

The preceding analysis is valid for frequencies larger than 50 Hz. When considering lower frequencies, flicker noise (also known as 1/f noise) must be taken into account.

For a reference on noise calculations, refer to the Band-Pass KRC or Sallen-Key Filter section.

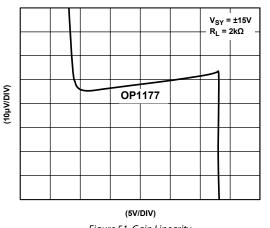

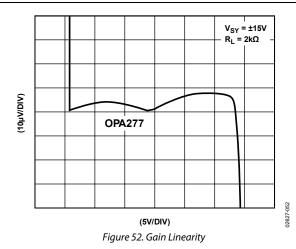

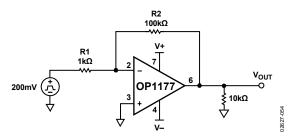

#### **GAIN LINEARITY**

Gain linearity reduces errors in closed-loop configurations. The straighter the gain curve, the lower the maximum error over the input signal range is. This is especially true for circuits with high closed-loop gains.

The OP1177 has excellent gain linearity even with heavy loads, as shown in Figure 51. Compare its performance to the OPA277, shown in Figure 52. Both devices are measured under identical conditions, with  $R_L = 2 \text{ k}\Omega$ . The OP2177 (dual) has virtually no distortion at lower voltages. Compared to the OPA277 at several supply voltages and various loads, OP1177 performance far exceeds that of its counterpart.

Figure 51. Gain Linearity

#### INPUT OVERVOLTAGE PROTECTION

When their input voltage exceeds the positive or negative supply voltage, most amplifiers require external resistors to protect them from damage.

The OPx177 has internal protective circuitry that allows voltages as high as 2.5 V beyond the supplies to be applied at the input of either terminal without any harmful effects

Use an additional resistor in series with the inputs if the voltage exceeds the supplies by more than 2.5 V. The value of the resistor can be determined from the formula

$$\frac{\left(V_{IN} - V_{S}\right)}{R_{S} + 500\,\Omega} \le 5\,\text{mA}$$

With the OPx177 low input offset current of <1 nA maximum, placing a 5 k $\Omega$  resistor in series with both inputs adds less than 5  $\mu V$  to input offset voltage and has a negligible impact on the overall noise performance of the circuit.

$5~k\Omega$  protects the inputs to more than 27 V beyond either supply. Refer to the THD + Noise section for additional information on noise vs. source resistance.

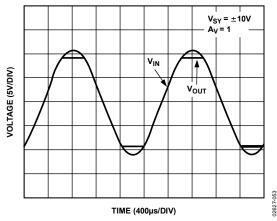

#### **OUTPUT PHASE REVERSAL**

Phase reversal is defined as a change of polarity in the amplifier transfer function. Many operational amplifiers exhibit phase reversal when the voltage applied to the input is greater than the maximum common-mode voltage. In some instances, this can cause permanent damage to the amplifier. In feedback loops, it can result in system lockups or equipment damage. The OPx177 is immune to phase reversal problems even at input voltages beyond the supplies.

Figure 53. No Phase Reversal

#### **SETTLING TIME**

Settling time is defined as the time it takes an amplifier output to reach and remain within a percentage of its final value after application of an input pulse. It is especially important in measurement and control circuits in which amplifiers buffer analog-to-digital inputs or digital-to-analog converter outputs.

To minimize settling time in amplifier circuits, use proper bypassing of power supplies and an appropriate choice of circuit components. Resistors should be metal film types, because they have less stray capacitance and inductance than their wirewound counterparts. Capacitors should be polystyrene or polycarbonate types to minimize dielectric absorption.

The leads from the power supply should be kept as short as possible to minimize capacitance and inductance. The OPx177 has a settling time of about 45  $\mu$ s to 0.01% (1 mV) with a 10 V step applied to the input in a noninverting unity gain.

#### **OVERLOAD RECOVERY TIME**

Overload recovery is defined as the time it takes the output voltage of an amplifier to recover from a saturated condition to its linear response region. A common example is one in which the output voltage demanded by the circuit's transfer function lies beyond the maximum output voltage capability of the amplifier. A 10 V input applied to an amplifier in a closed-loop gain of 2 demands an output voltage of 20 V. This is beyond the output voltage range of the OPx177 when operating at  $\pm 15$  V supplies and forces the output into saturation.

Recovery time is important in many applications, particularly where the operational amplifier must amplify small signals in the presence of large transient voltages.

Figure 54. Test Circuit for Overload Recovery Time

Figure 18 shows the positive overload recovery time of the OP1177. The output recovers in less than 4  $\mu$ s after being overdriven by more than 100%.

The negative overload recovery of the OP1177 is 1.4  $\mu$ s, as seen in Figure 19.

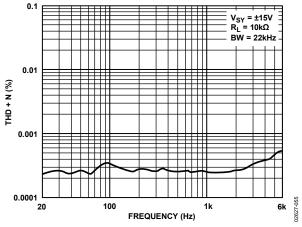

#### **THD + NOISE**

The OPx177 has very low total harmonic distortion. This indicates excellent gain linearity and makes the OPx177 a great choice for high closed-loop gain precision circuits.

Figure 55 shows that the OPx177 has approximately 0.00025% distortion in unity gain, the worst-case configuration for distortion.

Figure 55. THD + N vs. Frequency

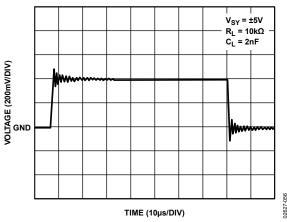

#### **CAPACITIVE LOAD DRIVE**

OPx177 is inherently stable at all gains and capable of driving large capacitive loads without oscillation. With no external compensation, the OPx177 safely drives capacitive loads up to 1000 pF in any configuration. As with virtually any amplifier, driving larger capacitive loads in unity gain requires additional circuitry to assure stability.

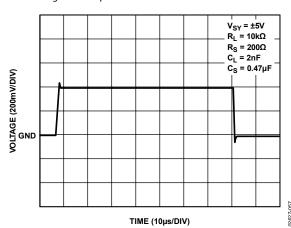

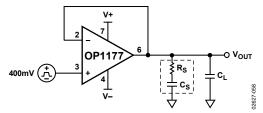

In this case, a snubber network is used to prevent oscillation and reduce the amount of overshoot. A significant advantage of this method is that it does not reduce the output swing because the Resistor  $R_S$  is not inside the feedback loop.

Figure 56 is a scope photograph of the output of the OPx177 in response to a 400 mV pulse. The load capacitance is 2 nF. The circuit is configured in positive unity gain, the worst-case condition for stability.

As shown in Figure 58, placing an R-C network parallel to the load capacitance ( $C_L$ ) allows the amplifier to drive higher values of  $C_L$  without causing oscillation or excessive overshoot.

There is no ringing, and overshoot is reduced from 27% to 5% using the snubber network.

Optimum values for  $R_S$  and  $C_S$  are tabulated in Table 5 for several capacitive loads, up to 200 nF. Values for other capacitive loads can be determined experimentally.

**Table 5. Optimum Values for Capacitive Loads**

| CL     | Rs    | Cs      |

|--------|-------|---------|

| 10 nF  | 20 Ω  | 0.33 μF |

| 50 nF  | 30 Ω  | 6.8 nF  |

| 200 nF | 200 Ω | 0.47 μF |

Figure 56. Capacitive Load Drive Without Snubber

Figure 57. Capacitive Load Drive with Snubber

Figure 58. Snubber Network Configuration

CAUTION: The snubber technique cannot recover the loss of bandwidth induced by large capacitive loads.

#### STRAY INPUT CAPACITANCE COMPENSATION

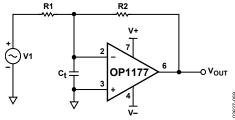

The effective input capacitance in an operational amplifier circuit  $(C_t)$  consists of three components. These are the internal differential capacitance between the input terminals, the internal common-mode capacitance of each input to ground, and the external capacitance including parasitic capacitance. In the circuit in Figure 59, the closed-loop gain increases as the signal frequency increases.

The transfer function of the circuit is

$$1+\frac{R2}{R1}\left(1+sC_tR1\right)$$

indicating a zero at

$$s = \frac{R2 + R1}{R2R1C_t} = \frac{1}{2\pi (R1/R2)C_t}$$

Depending on the value of R1 and R2, the cutoff frequency of the closed-loop gain can be well below the crossover frequency. In this case, the phase margin  $(\Phi_m)$  can be severely degraded, resulting in excessive ringing or even oscillation.

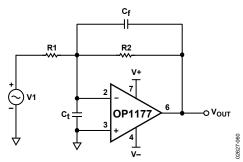

A simple way to overcome this problem is to insert a capacitor in the feedback path, as shown in Figure 60.

The resulting pole can be positioned to adjust the phase margin.

Setting  $C_f = (R1/R2) C_t$  achieves a phase margin of 90°.

Figure 59. Stray Input Capacitance

Figure 60. Compensation Using Feedback Capacitor

#### REDUCING ELECTROMAGNETIC INTERFERENCE

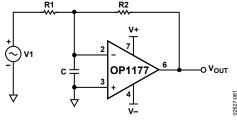

A number of methods can be utilized to reduce the effects of EMI on amplifier circuits.

In one method, stray signals on either input are coupled to the opposite input of the amplifier. The result is that the signal is rejected according to the amplifier's CMRR.

This is usually achieved by inserting a capacitor between the inputs of the amplifier, as shown in Figure 61. However, this method can also cause instability, depending on the value of capacitance.

Figure 61. EMI Reduction

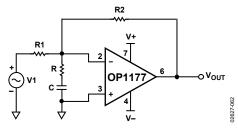

Placing a resistor in series with the capacitor (see Figure 62) increases the dc loop gain and reduces the output error. Positioning the breakpoint (introduced by R-C) below the secondary pole of the operational amplifier improves the phase margin and, therefore, stability.

R can be chosen independently of C for a specific phase margin according to the formula

$$R = \frac{R2}{a(if_2)} - \left(1 + \frac{R2}{R1}\right)$$

where:

*a* is the open-loop gain of the amplifier.  $f_2$  is the frequency at which the phase of  $a = \Phi_m - 180^\circ$ .

Figure 62. Compensation Using Input R-C Network

#### PROPER BOARD LAYOUT

The OPx177 is a high precision device. To ensure optimum performance at the PC board level, care must be taken in the design of the board layout.

To avoid leakage currents, the surface of the board should be kept clean and free of moisture. Coating the surface creates a barrier to moisture accumulation and helps reduce parasitic resistance on the board.

Keeping supply traces short and properly bypassing the power supplies minimizes power supply disturbances due to output current variation, such as when driving an ac signal into a heavy load. Bypass capacitors should be connected as closely as possible to the device supply pins. Stray capacitances are a concern at the outputs and the inputs of the amplifier. It is recommended that signal traces be kept at least 5 mm from supply lines to minimize coupling.

A variation in temperature across the PC board can cause a mismatch in the Seebeck voltages at solder joints and other points where dissimilar metals are in contact, resulting in thermal voltage errors. To minimize these thermocouple effects, resistors should be oriented so heat sources warm both ends equally. Input signal paths should contain matching numbers and types of components where possible, in order to match the number and type of thermocouple junctions. For example, dummy components such as zero value resistors can be used to match real resistors in the opposite input path. Matching components should be located in close proximity and should be oriented in the same manner. Leads should be of equal length so that thermal conduction is in equilibrium. Heat sources on the PC board should be kept as far away from amplifier input circuitry as is practical.

The use of a ground plane is highly recommended. A ground plane reduces EMI noise and also helps to maintain a constant temperature across the circuit board.

#### **DIFFERENCE AMPLIFIERS**

Difference amplifiers are used in high accuracy circuits to improve the common-mode rejection ratio (CMRR).

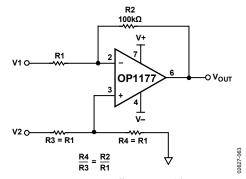

Figure 63. Difference Amplifier

In the single instrumentation amplifier (see Figure 63),

where:

$$\frac{R4}{R3} = \frac{R2}{R1}$$

$$V_O = \frac{R2}{R1} (V_2 - V_1)$$

a mismatch between the ratio R2/R1 and R4/R3 causes the common-mode rejection ratio to be reduced.

To better understand this effect, consider that, by definition,

$$CMRR = \frac{A_{DM}}{A_{CM}}$$

where  $A_{DM}$  is the differential gain and  $A_{CM}$  is the common-mode gain.

$$A_{DM} = \frac{V_O}{V_{DIFF}} \text{ and } A_{CM} = \frac{V_O}{V_{CM}}$$

$$V_{DIFF} = V_1 - V_2 \text{ and } V_{CM} = \frac{1}{2} (V_1 + V_2)$$

For this circuit to act as a difference amplifier, its output must be proportional to the differential input signal.

From Figure 63,

$$V_{O} = -\left(\frac{R2}{RI}\right)V_{I} + \left[\frac{\left(1 + \frac{R2}{RI}\right)}{\left(1 + \frac{R3}{R4}\right)}\right]V_{2}$$

Arranging terms and combining the equations above yields:

$$CMRR = \frac{R4R1 + R3R2 + 2R4R2}{2R4R1 - 2R2R3} \tag{1}$$

The sensitivity of CMRR with respect to the R1 is obtained by taking the derivative of CMRR, in Equation 1, with respect to R1.

$$\frac{\delta CMRR}{\delta R1} = \frac{\delta}{\delta R1} \left( \frac{R1R4}{2R1R4 - 2R2R3} + \frac{2R2R4 + R2R3}{2R1R4 - 2R2R3} \right)$$

$$\frac{\delta CMRR}{\delta R1} = \frac{1}{2 - \frac{(2R2R3)}{R1R4}}$$

Assuming that

$$R1 \approx R2 \approx R3 \approx R4 \approx R$$

and

$$R(1 - \delta) < R1, R2, R3, R4 < R(1 + \delta)$$

the worst-case CMRR error arises when

$$R1 = R4 = R(1 + \delta)$$

and  $R2 = R3 = R(1 - \delta)$

Plugging these values into Equation 1 yields

$$CMRR_{MIN} \cong \left| \frac{1}{2\delta} \right|$$

where  $\delta$  is the tolerance of the resistors.

Lower tolerance value resistors result in higher common-mode rejection (up to the CMRR of the operational amplifier).

Using 5% tolerance resistors, the highest CMRR that can be guaranteed is 20 dB. Alternatively, using 0.1% tolerance resistors results in a common-mode rejection ratio of at least 54 dB (assuming that the operational amplifier CMRR  $\times$  54 dB).

With the CMRR of OPx177 at 120 dB minimum, the resistor match is the limiting factor in most circuits. A trimming resistor can be used to further improve resistor matching and CMRR of the difference amplifier circuit.

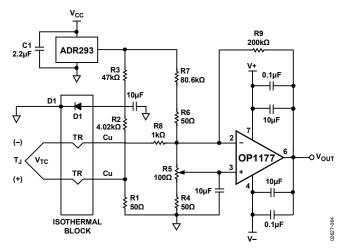

#### A HIGH ACCURACY THERMOCOUPLE AMPLIFIER

A thermocouple consists of two dissimilar metal wires placed in contact. The dissimilar metals produce a voltage

$$V_{TC} = \alpha (T_I - T_R)$$

where:

$T_I$  is the temperature at the measurement of the hot junction.  $T_R$  is the temperature at the cold junction.

$\alpha$  is the Seebeck coefficient specific to the dissimilar metals used in the thermocouple.

$V_{TC}$  is the thermocouple voltage.  $V_{TC}$  becomes larger with increasing temperature.

Maximum measurement accuracy requires cold junction compensation of the thermocouple. To perform the cold junction compensation, apply a copper wire short across the terminating junctions (inside the isothermal block) simulating a 0°C point. Adjust the output voltage to zero using the R5 trimming resistor, and remove the copper wire.

The OPx177 is an ideal amplifier for thermocouple circuits because it has a very low offset voltage, excellent PSRR and CMRR, and low noise at low frequencies.

It can be used to create a thermocouple circuit with great linearity. Resistor R1, Resistor R2, and Diode D1, shown in Figure 64, are mounted in an isothermal block.

Figure 64. Type K Thermocouple Amplifier Circuit

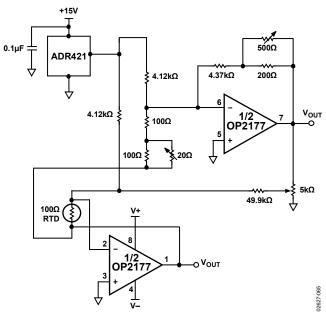

#### **LOW POWER LINEARIZED RTD**

A common application for a single element varying bridge is an RTD thermometer amplifier, as shown in Figure 65. The excitation is delivered to the bridge by a 2.5 V reference applied at the top of the bridge.

RTDs may have thermal resistance as high as 0.5°C to 0.8°C per mW. In order to minimize errors due to resistor drift, the current through each leg of the bridge must be kept low. In this circuit, the amplifier supply current flows through the bridge. However, at the OPx177 maximum supply current of 600  $\mu A$ , the RTD dissipates less than 0.1 mW of power, even at the highest resistance. Errors due to power dissipation in the bridge are kept under 0.1°C.

Calibration of the bridge can be made at the minimum value of temperature to be measured by adjusting R<sub>P</sub> until the output is zero.

To calibrate the output span, set the full-scale and linearity potentiometers to midpoint and apply a 500°C temperature to the sensor or substitute the equivalent 500°C RTD resistance.

Adjust the full-scale potentiometer for a 5 V output. Finally, apply 250°C or the equivalent RTD resistance and adjust the linearity potentiometer for 2.5 V output. The circuit achieves better than  $\pm 0.5$ °C accuracy after adjustment.

Figure 65. Low Power Linearized RTD Circuit

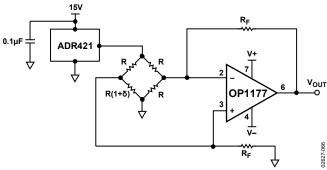

#### SINGLE OPERATIONAL AMPLIFIER BRIDGE

The low input offset voltage drift of the OP1177 makes it very effective for bridge amplifier circuits used in RTD signal conditioning. It is often more economical to use a single bridge operational amplifier as opposed to an instrumentation amplifier.

In the circuit shown in Figure 66, the output voltage at the operational amplifier is

$$V_{O} = \frac{R2}{R} \left[ V_{REF} \left( \frac{\delta}{\frac{R1}{R} + \left( 1 + \frac{R1}{R2} \right) (1 + \delta)} \right) \right]$$

where  $\delta = \Delta R/R$  is the fractional deviation of the RTD resistance with respect to the bridge resistance due to the change in temperature at the RTD.

For  $\delta \ll 1$ , the preceding expression becomes

$$\begin{split} V_O & \cong \left(\frac{R2}{R}\right) V_{REF} \left(\frac{\delta}{1 + \frac{R1}{R} + \frac{R1}{R2}}\right) = \\ & \left[\left(\frac{R2}{R}\right) \left(1 + \frac{R1}{R2}\right) + \left(\frac{R1}{R2}\right)\right] V_{REF} \delta \end{split}$$

With  $V_{\text{REF}}$  constant, the output voltage is linearly proportional to  $\delta$  with a gain factor of

$$V_{REF} \left( \frac{R2}{R} \right) \left[ \left( 1 + \frac{R1}{R2} \right) + \left( \frac{R1}{R2} \right) \right]$$

Figure 66. Single Bridge Amplifier

### REALIZATION OF ACTIVE FILTERS

#### **BAND-PASS KRC OR SALLEN-KEY FILTER**

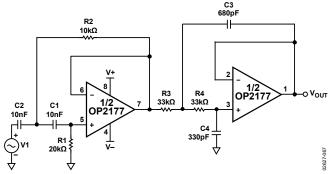

The low offset voltage and the high CMRR of the OPx177 make it an excellent choice for precision filters, such as the band-pass KRC filter shown in Figure 67. This filter type offers the capability to tune the gain and the cutoff frequency independently.

Because the common-mode voltage into the amplifier varies with the input signal in the KRC filter circuit, a high CMRR is required to minimize distortion. Also, the low offset voltage of the OPx177 allows a wider dynamic range when the circuit gain is chosen to be high.

The circuit of Figure 67 consists of two stages. The first stage is a simple high-pass filter whose corner frequency (f<sub>c</sub>) is

$$\frac{1}{2\pi\sqrt{C1C2R1R2}}\tag{2}$$

and whose

$$Q = K \sqrt{\frac{RI}{R2}} \tag{3}$$

where *K* is the dc gain.

Choosing equal capacitor values minimizes the sensitivity and simplifies Equation 2 to

$$\frac{1}{2\pi C\sqrt{R1R2}}$$

The value of Q determines the peaking of the gain vs. frequency (ringing in transient response). Commonly chosen values for Q are generally near unity.

Setting  $Q = \frac{1}{\sqrt{2}}$  yields minimum gain peaking and minimum ringing. Determine values for R1 and R2 by using Equation 3. For  $Q = \frac{1}{\sqrt{2}}$ , R1/R2 = 2 in the circuit example. Pick R1 = 5 k $\Omega$  and R2 = 10 k $\Omega$  for simplicity.

The second stage is a low-pass filter whose corner frequency can be determined in a similar fashion. For R3 = R4 = R

$$fc = \frac{1}{2\pi R \sqrt{\frac{C3}{C4}}}$$

and  $Q = \frac{1}{2} \sqrt{\frac{C3}{C4}}$

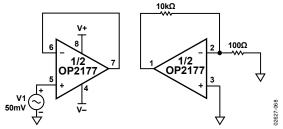

#### **CHANNEL SEPARATION**

Multiple amplifiers on a single die are often required to reject any signals originating from the inputs or outputs of adjacent channels. OP2177 input and bias circuitry is designed to prevent feedthrough of signals from one amplifier channel to the other. As a result, the OP2177 has an impressive channel separation of greater than  $-120~\mathrm{dB}$  for frequencies up to  $100~\mathrm{kHz}$  and greater than  $-115~\mathrm{dB}$  for signals up to  $1~\mathrm{MHz}$ .

Figure 67. Two-Stage, Band-Pass KRC Filter

Figure 68. Channel Separation Test Circuit

# REFERENCES ON NOISE DYNAMICS AND FLICKER NOISE

S. Franco, Design with Operational Amplifiers and Analog Integrated Circuits. McGraw-Hill, 1998.

Analog Devices, Inc., *The Best of* Analog Dialogue, *1967 to 1991*. Analog Devices, Inc., 1991.

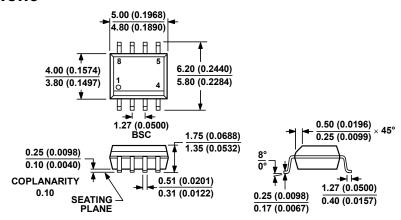

### **OUTLINE DIMENSIONS**

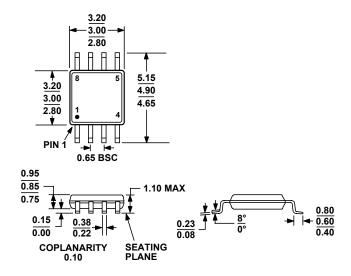

#### COMPLIANT TO JEDEC STANDARDS MS-012-AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 69. 8-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-8)

Dimensions shown in millimeters and (inches)

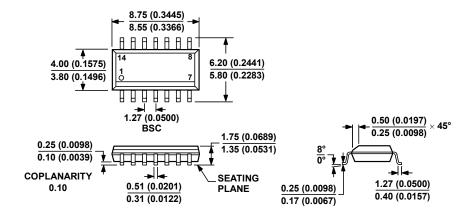

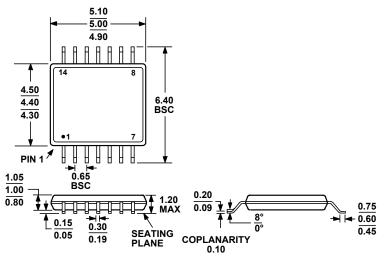

#### **COMPLIANT TO JEDEC STANDARDS MS-012-AB**

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 70. 14-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-14) Dimensions shown in millimeters and (inches) D606-A

#### **COMPLIANT TO JEDEC STANDARDS MO-187-AA**

Figure 71. 8-Lead Mini Small Outline Package [MSOP] (RM-8) Dimensions shown in millimeters

COMPLIANT TO JEDEC STANDARDS MO-153-AB-1

Figure 72. 14-Lead Thin Shrink Small Outline Package [TSSOP] (RU-14) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model                        | Temperature Range | Package Description | Package Option | Branding |

|------------------------------|-------------------|---------------------|----------------|----------|

| OP1177AR                     | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| OP1177AR-REEL                | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| OP1177AR-REEL7               | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| OP1177ARZ <sup>1</sup>       | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| OP1177ARZ-REEL <sup>1</sup>  | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| OP1177ARZ-REEL7 <sup>1</sup> | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| OP1177ARM-R2                 | -40°C to +125°C   | 8-Lead MSOP         | RM-8           | AZA      |

| OP1177ARM-REEL               | -40°C to +125°C   | 8-Lead MSOP         | RM-8           | AZA      |

| OP1177ARMZ-R2 <sup>1</sup>   | -40°C to +125°C   | 8-Lead MSOP         | RM-8           | AZA#     |

| OP1177ARMZ-REEL <sup>1</sup> | -40°C to +125°C   | 8-Lead MSOP         | RM-8           | AZA#     |

| OP2177AR                     | −40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| OP2177AR-REEL                | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| OP2177AR-REEL7               | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| OP2177ARZ <sup>1</sup>       | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| OP2177ARZ-REEL <sup>1</sup>  | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| OP2177ARZ-REEL7 <sup>1</sup> | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| OP2177ARM-R2                 | -40°C to +125°C   | 8-Lead MSOP         | RM-8           | B2A      |

| OP2177ARM-REEL               | -40°C to +125°C   | 8-Lead MSOP         | RM-8           | B2A      |

| OP2177ARMZ-R2 <sup>1</sup>   | -40°C to +125°C   | 8-Lead MSOP         | RM-8           | B2A#     |

| OP2177ARMZ-REEL <sup>1</sup> | -40°C to +125°C   | 8-Lead MSOP         | RM-8           | B2A#     |

| OP4177AR                     | -40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| OP4177AR-REEL                | -40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| OP4177AR-REEL7               | -40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| OP4177ARZ <sup>1</sup>       | -40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| OP4177ARZ-REEL <sup>1</sup>  | -40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| OP4177ARZ-REEL7 <sup>1</sup> | -40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| OP4177ARU                    | -40°C to +125°C   | 14-Lead TSSOP       | RU-14          |          |

| OP4177ARU-REEL               | -40°C to +125°C   | 14-Lead TSSOP       | RU-14          |          |

| OP4177ARUZ <sup>1</sup>      | -40°C to +125°C   | 14-Lead TSSOP       | RU-14          |          |

| OP4177ARUZ-REEL <sup>1</sup> | -40°C to +125°C   | 14-Lead TSSOP       | RU-14          |          |

$<sup>^1</sup>$  Z = Pb-free part; # denotes Pb-free product may be top or bottom marked.