# Broadband Modem Mixed-Signal Front End

AD9876

#### **FEATURES**

Low Cost 3.3 V CMOS Mixed-Signal Front End (MxFE™)

Converter for Broadband Modems

10-/12-Bit D/A Converter (TxDAC+®)

64/32 MSPS Input Word Rate

2×/4× Interpolating LPF or BPF Transmit Filter

128 MSPS DAC Output Update Rate

Wide (26 MHz) Transmit Bandwidth

Power-Down Mode

10-/12-Bit 50 MSPS A/D Converter

Fourth Order Low-Pass Filter 12 MHz or 26 MHz

with Bypass

-6 dB to +36 dB Programmable Gain Amplifier

Internal Clock Multiplier (PLL)

Clock Outputs

APPLICATIONS

Powerline Networking

Home Phone Networking

xDSL

Broadband Wireless

Home RF

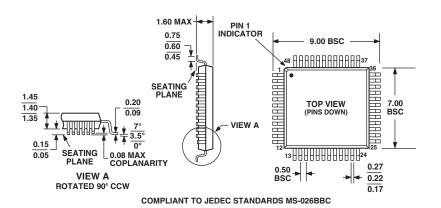

48-Lead LQFP Package

**Voltage Regulator Controller**

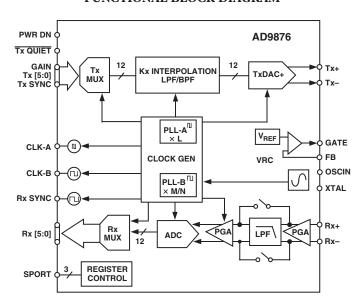

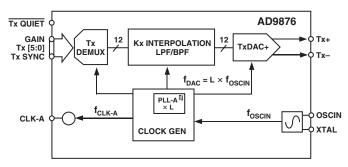

### FUNCTIONAL BLOCK DIAGRAM

### PRODUCT DESCRIPTION

The AD9876 is a single-supply broadband modem mixed-signal front end (MxFE) IC. The device contains a transmit path interpolation filter and DAC and a receive path PGA, LPF, and ADC supporting a variety of broadband modem applications. Also on-chip is a PLL clock multiplier that provides all required clocks from a single crystal or clock input. The AD9876 provides 12-bit converter performance on both the Tx and Rx path.

The TxDAC+ uses a selectable digital 2× or 4× interpolation low-pass or band-pass filter to further oversample transmit data and reduce the complexity of analog reconstruction filtering. The transmit path signal bandwidth can be as high as 26 MHz at an input data rate of 64 MSPS. The 12-bit DAC provides differential current outputs for optimum noise and distortion performance. The DAC full-scale current can be adjusted from 2 to 20 mA by a single resistor, providing 20 dB of additional gain range.

The receive path consists of a PGA, LPF, and ADC. The PGA has a gain range of -6 dB to +36 dB, programmable in 2 dB steps, adding 42 dB of dynamic range to the receive path. The receive

path LPF cutoff frequency can be programmed to either 12 MHz or 26 MHz. The filter cutoff frequency can also be tuned or bypassed where filter requirements differ. The 12-bit ADC uses a multistage differential pipeline architecture to achieve excellent dynamic performance with low power consumption.

The AD9876 provides a voltage regulator controller (VRC) that can be used with an external power MOSFET transistor to form a cost-effective 1.3 V linear regulator.

The digital transmit and receive ports are each multiplexed to a bus width of six bits and are clocked at a frequency of twice the 12-bit word rate.

The AD9876 ADC and/or DAC can also be used at sampling rates as high as 64 MSPS in a 6-bit resolution nonmultiplexed mode.

The AD9876 is pin compatible with the 10-bit AD9875. Both are available in a space-saving 48-lead LQFP package. They are specified over the industrial ( $-40^{\circ}$ C to  $+85^{\circ}$ C) temperature range.

MxFE is a trademark of Analog Devices, Inc. TxDAC+ is a registered trademark of Analog Devices, Inc.

### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

ax: 781/326-8703 © Analog Devices, Inc., 2002

# $\label{eq:continuous} \textbf{AD9876-SPECIFICATIONS} \begin{subarray}{l} (V_S = 3.3 \ V \pm 10\%, \ f_{OSCIN} = 32 \ MHz, \ f_{DAC} = 128 \ MHz, \ Gain = -6 \ dB, \ R_{SET} = 4.02 \ k\Omega, \ DAC \ single-ended load, unless otherwise noted. ) \\ \end{subarray}$

| Parameter                                                                                                                                                                                                                                                                                                                   | Temp                                              | Test<br>Level             | Min                        | Typ                                                                                                                        | Max                     | Unit                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|---------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------------------------|

| OSCIN CHARACTERISTICS Frequency Range Duty Cycle Input Capacitance Input Impedance                                                                                                                                                                                                                                          | Full<br>Full<br>25°C<br>25°C                      | III<br>III<br>II          | 10<br>40                   | 50<br>3<br>100                                                                                                             | 64<br>60                | MHz<br>%<br>pF<br>MΩ                    |

| CLOCK OUTPUT CHARACTERISTICS CLK A Jitter (f <sub>CLKA</sub> Derived from PLL) CLK A Duty Cycle CLK B Jitter (f <sub>CLKB</sub> Derived from PLL) CLK B Duty Cycle                                                                                                                                                          | 25°C<br>25°C<br>25°C<br>25°C                      | III<br>III<br>III         |                            | 14<br>50 ±5<br>33<br>50 ±5                                                                                                 |                         | ps rms<br>%<br>ps rms<br>%              |

| Tx CHARACTERISTICS Tx Path Latency, 4× Interpolation Interpolation Filter Bandwidth (-0.1 dB)                                                                                                                                                                                                                               | Full                                              | II                        |                            | 86                                                                                                                         |                         | f <sub>DAC</sub> Cycles                 |

| 4× Interpolation, LPF 2× Interpolation, LPF TxDAC                                                                                                                                                                                                                                                                           | Full<br>Full                                      | II                        |                            | 13<br>26                                                                                                                   |                         | MHz<br>MHz                              |

| Resolution Conversion Rate Full-Scale Output Current Voltage Compliance Range Gain Error Output Offset (Single-Ended) Differential Nonlinearity Integral Nonlinearity Output Capacitance Phase Noise @ 1 kHz Offset, 10 MHz Signal                                                                                          | Full Full Full Full Full Full Full 25°C 25°C 25°C | II II III III III III III | 10<br>2<br>-0.5<br>-5<br>0 | $   \begin{array}{c}     12 \\     10 \\     \pm 2 \\     2 \\     \pm 1 \\     \pm 2 \\     5 \\     -100   \end{array} $ | 128<br>20<br>+1.5<br>+5 | Bits MHz mA V % FS µA LSB LSB pF dBc/Hz |

| Signal-to-Noise and Distortion (SINAD)  10 MHz Analog Out AD9876 (20 MHz BW) Wideband SFDR (to Nyquist, 64 MHz Max)  5 MHz Analog Out  10 MHz Analog Out                                                                                                                                                                    | Full<br>25°C<br>25°C<br>25°C                      | III<br>III<br>III         | 62.5                       | 65<br>80<br>74                                                                                                             |                         | dB<br>dBc<br>dBc                        |

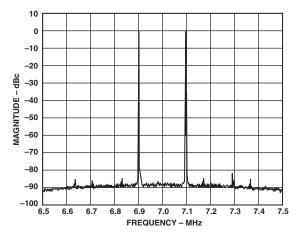

| Narrow-Band SFDR (3 MHz Window):<br>10 MHz Analog Out<br>IMD (f1 = 6.9 MHz, f2 = 7.1 MHz)                                                                                                                                                                                                                                   | 25°C<br>25°C                                      | III                       |                            | 88<br>-80                                                                                                                  |                         | dBc<br>dBFS                             |

| Rx PATH CHARACTERISTICS Resolution Conversion Rate Pipeline Delay, ADC Clock Cycles                                                                                                                                                                                                                                         | NA<br>Full<br>NA                                  | NA<br>II<br>NA            | 7.5                        | 12<br>5.5                                                                                                                  | 64                      | Bits<br>MHz<br>Cycles                   |

| DC Accuracy Differential Nonlinearity Integral Nonlinearity Dynamic Performance (ADC Clocked Direct) (A <sub>IN</sub> = -0.5 dBFS, f = 5 MHz)                                                                                                                                                                               | Full<br>Full                                      | II                        | -1.0<br>-4.5               | ±0.25<br>±0.5                                                                                                              | +1.0<br>+3.5            | LSB<br>LSB                              |

| @ f <sub>OSCIN</sub> = 32 MHz Signal-to-Noise and Distortion Ratio (SINAD) Effective Number of Bits (ENOB) Signal-to-Noise Ratio (SNR) Total Harmonic Distortion (THD) Spurious-Free Dynamic Range (SFDR) Dynamic Performance (ADC Clocked, PLLB/2) (A <sub>IN</sub> = -0.5 dBFS, f = 5 MHz) @ F <sub>PLLB/2</sub> = 50 MHz | Full<br>Full<br>25°C<br>25°C<br>25°C              | I III III                 | 60.8<br>9.8                | 63.2<br>10.2<br>64<br>-70<br>72                                                                                            |                         | dB<br>Bits<br>dB<br>dB                  |

| Signal-to-Noise and Distortion Ratio (SINAD) Effective Number of Bits (ENOB) Signal-to-Noise Ratio (SNR) Total Harmonic Distortion (THD) Spurious-Free Dynamic Range (SFDR)                                                                                                                                                 | 25°C<br>25°C<br>25°C<br>25°C<br>25°C              | III<br>III<br>III         |                            | 56<br>9.3<br>59<br>-63<br>68                                                                                               |                         | dB<br>Bits<br>dB<br>dB                  |

-2- REV. A

|                                                                                |              | Test       |               |      |                                             |

|--------------------------------------------------------------------------------|--------------|------------|---------------|------|---------------------------------------------|

| Parameter                                                                      | Temp         | Level      | Min Typ       | Max  | Unit                                        |

| Rx PATH GAIN/OFFSET                                                            |              |            |               |      |                                             |

| Minimum Programmable Gain                                                      | 25°C         | III        | -6            |      | dB                                          |

| Maximum Programmable Gain (12 MHz Filter)                                      | 25°C         | III        | 36            |      | dB                                          |

| Maximum Programmable Gain (26 MHz Filter)                                      | 25°C         | III        | 30            |      | dB                                          |

| Gain Step Size                                                                 | 25°C         | III        | 2             |      | dB                                          |

| Gain Step Accuracy                                                             | 25°C         | III        | ±0.4          |      | dB                                          |

| Gain Range Error                                                               | 25°C         | III        | ±1.0          |      | dB                                          |

| Offset Error, PGA Gain = 0 dB<br>Absolute Gain Error                           | 25°C<br>25°C | III        | ±10<br>±0.8   |      | LSB<br>dB                                   |

|                                                                                | 25°C         | 111        | Ξ0.8          |      | ив                                          |

| Rx PATH INPUT CHARACTERISTICS                                                  | F11          | 111        | 4             |      | 37 d                                        |

| Input Voltage Range                                                            | Full<br>25°C | III<br>III | 4 4           |      | Vppd                                        |

| Input Capacitance<br>Differential Input Resistance                             | 25°C         | III        | 270           |      | $\begin{array}{c} pF \\ \Omega \end{array}$ |

| Input Bandwidth (–3 dB)                                                        | 25°C         | III        | 50            |      | MHz                                         |

| Input Referred Noise (at –36 dB Gain with Filter)                              | 25°C         | III        | 16            |      | μV rms                                      |

| Input Referred Noise (at –6 dB Gain with Filter)                               | 25°C         | III        | 684           |      | μV rms                                      |

| Common-Mode Rejection                                                          | 25°C         | III        | 40            |      | dB                                          |

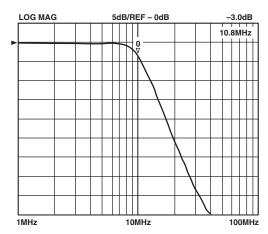

| Rx PATH LPF (Low Cutoff Frequency)                                             |              |            |               |      |                                             |

| Cutoff Frequency                                                               | 25°C         | III        | 12            |      | MHz                                         |

| Cutoff Frequency Variation                                                     | 25°C         | III        | ±7            |      | %                                           |

| Attenuation @ 22 MHz                                                           | 25°C         | III        | 20            |      | dB                                          |

| Pass-Band Ripple                                                               | 25°C         | III        | ±1.0          |      | dB                                          |

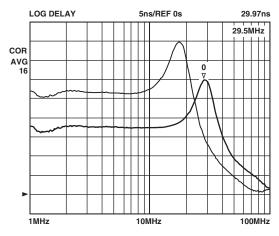

| Group Delay Variation                                                          | 25°C         | III        | 30            |      | ns                                          |

| Settling Time                                                                  | 2500         | ***        | 1.50          |      |                                             |

| (to 1% FS, Min to Max Gain Change) Total Harmonic Distortion at Max Gain (THD) | 25°C<br>25°C | III<br>III | 150<br>-68    |      | ns<br>dBc                                   |

|                                                                                | 23 C         | 111        | -00           |      | dbc                                         |

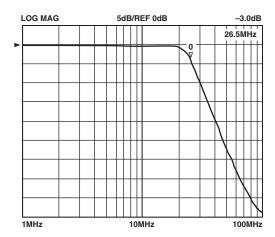

| Rx PATH LPF (High Cutoff Frequency) Cutoff Frequency                           | 25°C         | III        | 26            |      | MHz                                         |

| Cutoff Frequency Variation                                                     | 25°C         | III        | ±7            |      | %                                           |

| Attenuation @ 44 MHz                                                           | 25°C         | III        | 20            |      | dB                                          |

| Pass-Band Ripple                                                               | 25°C         | III        | ±1.2          |      | dB                                          |

| Group Delay Variation                                                          | 25°C         | III        | 15            |      | ns                                          |

| Settling Time                                                                  |              |            |               |      |                                             |

| (to 1% FS, Min to Max Gain Change)                                             | 25°C         | III        | 80            |      | ns                                          |

| Total Harmonic Distortion at Max Gain (THD)                                    | 25°C         | III        | -65           |      | dBc                                         |

| Rx PATH DIGITAL HPF                                                            |              |            |               |      |                                             |

| Latency (ADC Clock Source Cycles)                                              | Full         | II         | 1             |      | Cycle                                       |

| Roll-Off in Stop Band                                                          | Full         | II         | 6             |      | dB/Octave                                   |

| −3 dB Frequency                                                                | Full         | II         | $f_{ADC}/400$ |      | Hz                                          |

| Rx PATH DISTORTION PERFORMANCE                                                 |              |            |               |      |                                             |

| IMD: $f1 = 6.5 \text{ MHz}$ , $f2 = 7.7 \text{ MHz}$                           |              |            |               |      |                                             |

| 12 MHz Filter: 0 dB Gain                                                       | 25°C         | III        | -65           |      | dBc                                         |

| : 30 dB Gain                                                                   | 25°C         | III        | -57           |      | dBc                                         |

| 26 MHz Filter: 0 dB Gain                                                       | 25°C         | III        | -65<br>5.6    |      | dBc                                         |

| : 30 dB Gain                                                                   | 25°C         | III        | -56           |      | dBc                                         |

| POWER-DOWN/DISABLE TIMING                                                      | F "          |            |               | 000  |                                             |

| DAC I ON offer Tv QUIET Asserted                                               | Full         | II         |               | 200  | ns                                          |

| DAC I <sub>OUT</sub> ON after Tx QUIET De-Asserted                             | Full         | II         |               | 1    | μs                                          |

| Power-Down Delay (Active to Power-Down) DAC                                    | Full         | II         |               | 400  | ns                                          |

| Interpolator                                                                   | Full         | II         |               | 200  | ns                                          |

| Power-Up Delay (Power-Down to Active)                                          | 1 411        |            |               | 200  | 110                                         |

| DAC                                                                            | Full         | II         |               | 40   | μs                                          |

| PLL                                                                            | Full         | II         |               | 10   | μs                                          |

| ADC                                                                            | Full         | II         |               | 1000 | μs                                          |

| PGA                                                                            | Full         | II         |               | 1    | μs                                          |

| LPF                                                                            | Full         | II         |               | 1    | μs                                          |

| Interpolator                                                                   | Full         | II         |               | 200  | ns                                          |

| VRC                                                                            | Full         | II         |               | 2    | μs                                          |

| Minimum RESET Pulsewidth Low (t <sub>RL</sub> )                                | Full         | II         |               | 5    | f <sub>OSCIN</sub> Cycles                   |

REV. A -3-

| Parameter                                                                                                                      | Temp         | Test<br>Level | Min                    | Тур         | Max         | Unit      |

|--------------------------------------------------------------------------------------------------------------------------------|--------------|---------------|------------------------|-------------|-------------|-----------|

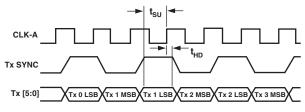

| Tx PATH INTERFACE                                                                                                              |              |               |                        |             |             |           |

| Maximum Input Nibble Rate, 2× Interpolation                                                                                    | Full         | II            | 128                    |             |             | MHz       |

| Tx Setup Time (t <sub>SU</sub> )                                                                                               | Full         | II            | 3.0                    |             |             | ns        |

| Tx Hold Time (t <sub>HD</sub> )                                                                                                | Full         | II            | 0                      |             |             | ns        |

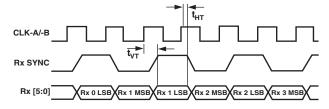

| Rx PATH INTERFACE                                                                                                              |              |               |                        |             |             |           |

| Maximum Output Nibble Rate                                                                                                     | Full         | II            | 110                    |             |             | MHz       |

| Rx Data Valid Time (t <sub>VT</sub> )                                                                                          | Full         | II<br>II      | 1 5                    |             | 3.0         | ns        |

| Rx Data Hold Time (t <sub>HT</sub> )                                                                                           | Full         | 11            | 1.5                    |             |             | ns        |

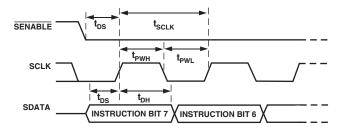

| SERIAL CONTROL BUS                                                                                                             | Full         | II            | 25                     |             |             | MHz       |

| Maximum SCLK Frequency (f <sub>SCLK</sub> )<br>Clock Pulsewidth High (t <sub>PWH</sub> )                                       | Full         | II            | 25<br>18               |             |             | ns        |

| Clock Pulsewidth Low (t <sub>PWI</sub> )                                                                                       | Full         | II            | 18                     |             |             | ns        |

| Clock Rise/Fall Time                                                                                                           | Full         | II            |                        |             | 1           | ms        |

| Data/Chip-Select Setup Time (t <sub>DS</sub> )                                                                                 | Full         | II            | 25                     |             |             | ns        |

| Data Hold Time (t <sub>DH</sub> )                                                                                              | Full         | II            | 0                      |             | • •         | ns        |

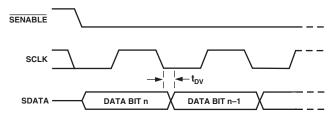

| Data Valid Time (t <sub>DV</sub> )                                                                                             | Full         | II            |                        |             | 20          | ns        |

| CMOS LOGIC INPUTS                                                                                                              |              |               |                        |             |             |           |

| Logic "1" Voltage                                                                                                              | Full         | II            | V <sub>DRVDD</sub> – 0 | 0.7         | 0.4         | V         |

| Logic "0" Voltage<br>Logic "1" Current                                                                                         | Full<br>Full | II<br>II      |                        |             | $0.4 \\ 12$ | V<br>μA   |

| Logic "0" Current                                                                                                              | Full         | II            |                        |             | 12          | μΑ        |

| Input Capacitance                                                                                                              | 25°C         | III           |                        | 3           |             | μF        |

| CMOS LOGIC OUTPUTS (1 mA Load)                                                                                                 |              |               |                        |             |             |           |

| Logic "1" Voltage                                                                                                              | Full         | II            | V <sub>DRVDD</sub> - 0 | 0.6         |             | V         |

| Logic "0" Voltage                                                                                                              | Full         | II            |                        |             | 0.4         | V         |

| Digital Output Rise/Fall Time                                                                                                  | Full         | II            | 1.5                    |             | 2.5         | ns        |

| POWER SUPPLY                                                                                                                   |              |               |                        |             |             |           |

| All Blocks Powered Up                                                                                                          | F 11         |               |                        | 262         | •           |           |

| I <sub>S_TOTAL</sub> (Total Supply Current) I <sub>S_TOTAL</sub> (Tx QUIET Pin Asserted)                                       | Full<br>25°C | I<br>III      |                        | 262<br>172  | 288         | mA<br>mA  |

| Digital Supply Current (I <sub>DRVDD</sub> + I <sub>DVDD</sub> )                                                               | 25°C         | III           |                        | 77          |             | mA        |

| Analog Supply Current (I <sub>AVDD</sub> )                                                                                     | 25°C         | III           |                        | 185         |             | mA        |

| Power Consumption of Functional Blocks:                                                                                        |              |               |                        |             |             |           |

| Rx LPF                                                                                                                         | 25°C         | III           |                        | 110         |             | mA        |

| ADC and SPGA                                                                                                                   | 25°C         | III           |                        | 55          |             | mA        |

| Rx Reference<br>Interpolator                                                                                                   | 25°C<br>25°C | III           |                        | 2<br>33     |             | mA<br>mA  |

| DAC                                                                                                                            | 25°C         | III           |                        | 18          |             | mA        |

| PLL-B                                                                                                                          | 25°C         | III           |                        | 8           |             | mA        |

| PLL-A                                                                                                                          | 25°C         | III           |                        | 24          |             | mA        |

| Voltage Regulator Controller                                                                                                   | 25°C         | III           |                        | 1           |             | mA        |

| All Blocks Powered Down Supply Current I <sub>s</sub> , f <sub>OSCIN</sub> = 32 MHz                                            | Full         | II            |                        | 19          | 22          | mA        |

| Supply Current I <sub>S</sub> , $f_{OSCIN} = 32$ WH12<br>Supply Current I <sub>S</sub> , $f_{OSCIN}$ Idle                      | Full         | II            |                        | 10          | 12          | mA        |

| Power Supply Rejection                                                                                                         |              |               |                        | - 0         |             |           |

| Tx Path ( $\Delta V_S = \pm 10\%$ )                                                                                            | 25°C         | III           |                        | 62          |             | dB        |

| Rx Path ( $\Delta V_S = \pm 10\%$ )                                                                                            | 25°C         | III           |                        | 54          |             | dB        |

| RECEIVE-TO-TRANSMIT ISOLATION                                                                                                  |              |               |                        |             |             |           |

| (10 MHz, Full-Scale Sine Wave Output/Output)                                                                                   | 0500         |               |                        | 7.7         |             | ID.       |

| Isolation: Tx Path to Rx Path, Gain = +36 dB<br>Isolation: Rx Path to Tx Path, Gain = -6 dB                                    | 25°C<br>25°C | III           |                        | -75<br>-70  |             | dB<br>dB  |

|                                                                                                                                | 25 0         | 111           |                        | -10         |             | ив        |

| VOLTAGE REGULATOR CONTROLLER                                                                                                   | E11          | <sub>T</sub>  | 1.25                   | 1 20        | 1 25        |           |

| Output Voltage (V <sub>FB</sub> with SI2301 Connected)<br>Line Regulation ( $\Delta V_{FB\%}/\Delta V_{DVDD\%} \times 100\%$ ) | Full<br>25°C | I             | 1.25                   | 1.30<br>100 | 1.35        | V %       |

| Line Regulation ( $\Delta V_{FB}/\Delta V_{DVDD}/\Delta \times 100\%$ ) Load Regulation ( $\Delta V_{FB}/\Delta I_{LOAD}$ )    | 25°C         | III           |                        | 60          |             | $m\Omega$ |

| Maximum Load Current (I <sub>LOAD</sub> )                                                                                      | Full         | II            | 250                    | -           |             | mA        |

Specifications subject to change without notice.

### **ABSOLUTE MAXIMUM RATINGS\***

| Power Supply $(V_S)$                      |

|-------------------------------------------|

| Digital Output Current 5 mA               |

| Digital Inputs0.3 V to DRVDD + 0.3 V      |

| Analog Inputs0.3 V to AVDD + 0.3 V        |

| Operating Temperature40°C to +85°C        |

| Maximum Junction Temperature 150°C        |

| Storage Temperature65°C to +150°C         |

| Lead Temperature (Soldering 10 sec) 300°C |

<sup>\*</sup>Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **EXPLANATION OF TEST LEVELS**

- I Devices are 100% production tested at 25°C and guaranteed by design and characterization testing for industrial operating temperature range (-40°C to +85°C).

- II Parameter is guaranteed by design and/or characterization testing.

- III Parameter is a typical value only.

### THERMAL CHARACTERISTICS

#### Thermal Resistance

48-Lead LQFP

$\theta_{IA} = 57^{\circ}C/W$

$\theta_{IC} = 28^{\circ} \text{C/W}$

#### **ORDERING GUIDE**

| Model                  | Temperature Range                | Package Description              | Package Option |

|------------------------|----------------------------------|----------------------------------|----------------|

| AD9876BST<br>AD9876-EB | -40°C to +85°C<br>-40°C to +85°C | 48-Lead LQFP<br>Evaluation Board | ST-48          |

| AD9876BSTRL            | −40°C to +85°C                   | BST Reel                         |                |

### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD9876 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. A -5-

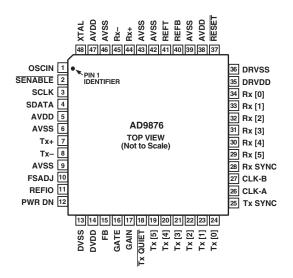

### PIN FUNCTION DESCRIPTIONS

| Pin No.              | Mnemonic | Function                                                    |

|----------------------|----------|-------------------------------------------------------------|

| 1                    | OSCIN    | Crystal Oscillator Inverter Input                           |

| 2                    | SENABLE  | Serial Bus Enable Input                                     |

| 3                    | SCLK     | Serial Bus Clock Input                                      |

| 4                    | SDATA    | Serial Bus Data I/O                                         |

| 5, 38, 47            | AVDD     | Analog 3.3 V Power Supply                                   |

| 6, 9, 39, 42, 43, 46 | AVSS     | Analog Ground                                               |

| 7                    | Tx+      | Transmit DAC+ Output                                        |

| 8                    | Tx-      | Transmit DAC- Output                                        |

| 10                   | FSADJ    | DAC Full-Scale Output Current Adjust with External Resistor |

| 11                   | REFIO    | DAC Band Gap Decoupling Node                                |

| 12                   | PWR DN   | Power-Down Input                                            |

| 13                   | DVSS     | Digital Ground                                              |

| 14                   | DVDD     | Digital 3.3 V Power Supply                                  |

| 15                   | FB       | Regulator Feedback Input                                    |

| 16                   | GATE     | Regulator Output to FET Gate                                |

| 17                   | GAIN     | Transmit Data Port (Tx [5:0]) Mode Select Input             |

| 18                   | Tx QUIET | Transmit Quiet Input                                        |

| 19-24                | Tx [5:0] | Transmit Data Input                                         |

| 25                   | Tx SYNC  | Transmit Synchronization Strobe Input                       |

| 26                   | CLK-A    | $L \times f_{OSCIN}$ Clock Output                           |

| 27                   | CLK-B    | $M/N \times f_{OSCIN}$ Clock Output                         |

| 28                   | Rx SYNC  | Receive Data Synchronization Strobe Output                  |

| 29-34                | Rx[5:0]  | Receive Data Output                                         |

| 35                   | DRVDD    | Digital I/O 3.3 V Power Supply                              |

| 36                   | DRVSS    | Digital I/O Ground                                          |

| 37                   | RESET    | Reset Input                                                 |

| 40                   | REFB     | ADC Reference Decoupling Node                               |

| 41                   | REFT     | ADC Reference Decoupling Node                               |

| 44                   | Rx+      | Receive Path + Input                                        |

| 45                   | Rx-      | Receive Path – Input                                        |

| 48                   | XTAL     | Crystal Oscillator Inverter Output                          |

### PIN CONFIGURATION

-6- REV. A

# DEFINITIONS OF SPECIFICATIONS CLOCK JITTER

The clock jitter is a measure of the intrinsic jitter of the PLL generated clocks. It is a measure of the jitter from one rising and of the clock with respect to another edge of the clock nine cycles later.

## DIFFERENTIAL NONLINEARITY ERROR (DNL, NO MISSING CODES)

An ideal converter exhibits code transitions that are exactly 1 LSB apart. DNL is the deviation from this ideal value. Guaranteed no missing codes to 10-bit resolution indicates that all 1024 codes, respectively, must be present over all operating ranges.

### INTEGRAL NONLINEARITY ERROR (INL)

Linearity error refers to the deviation of each individual code from a line drawn from "negative full scale" through "positive full scale." The point used as negative full scale occurs 1/2 LSB before the first code transition. Positive full scale is defined as a level 1 1/2 LSB beyond the last code transition. The deviation is measured from the middle of each particular code to the true straight line.

### **PHASE NOISE**

Single-sideband phase noise power density is specified relative to the carrier (dBc/Hz) at a given frequency offset (1 kHz) from the carrier. Phase noise can be measured directly on a generated single tone with a spectrum analyzer that supports noise marker measurements. It detects the relative power between the carrier and the offset (1 kHz) sideband noise and takes the resolution bandwidth (rbw) into account by subtracting 10 log(rbw). It also adds a correction factor that compensates for the implementation of the resolution bandwidth, log display, and detector characteristic.

### **OUTPUT COMPLIANCE RANGE**

The range of allowable voltage at the output of a current-output DAC. Operation beyond the maximum compliance limits may cause either output stage saturation, resulting in nonlinear performance or breakdown.

### SPURIOUS-FREE DYNAMIC RANGE (SFDR)

The difference, in dB, between the rms amplitude of the DACs output signal (or ADCs input signal) and the peak spurious signal over the specified bandwidth (Nyquist bandwidth, unless otherwise noted).

### PIPELINE DELAY (LATENCY)

The number of clock cycles between conversion initiation and the associated output data being made available.

### OFFSET ERROR

First transition should occur for an analog value 1/2 LSB above negative full scale. Offset error is defined as the deviation of the actual transition from that point.

### **GAIN ERROR**

The first code transition should occur at an analog value 1/2 LSB above negative full scale. The last transition should occur for an analog value 1 1/2 LSB below the nominal full scale. Gain error is the deviation of the actual difference between the first and last code transitions and the ideal difference between the first and last code transitions.

### INPUT REFERRED NOISE

The rms output noise is measured using histogram techniques. The ADC output codes' standard deviation is calculated in LSB and converted to an equivalent voltage. This results in a noise figure that can be directly referred to the Rx input of the AD9876.

### SIGNAL-TO-NOISE AND DISTORTION RATIO (SINAD)

SINAD is the ratio of the rms value of the measured input signal to the rms sum of all other spectral components below the Nyquist frequency, including harmonics but excluding dc. The value for SINAD is expressed in decibels.

### **EFFECTIVE NUMBER OF BITS (ENOB)**

For a sine wave, SINAD can be expressed in terms of the number of bits. Using the following formula:

$$N = (SINAD - 1.76) dB / 6.02$$

it is possible to get a measure of performance expressed as N, the effective number of bits.

### SIGNAL-TO-NOISE RATIO (SNR)

SNR is the ratio of the rms value of the measured input signal to the rms sum of all other spectral components below the Nyquist frequency, excluding harmonics and dc. The value for SNR is expressed in decibels.

### TOTAL HARMONIC DISTORTION (THD)

THD is the ratio of the rms sum of the first six harmonic components to the rms value of the measured input signal and is expressed as a percentage or in decibels.

### **POWER SUPPLY REJECTION**

Power supply rejection specifies the converters maximum full-scale change when the supplies are varied from nominal to minimum and maximum specified voltages.

REV. A -7-

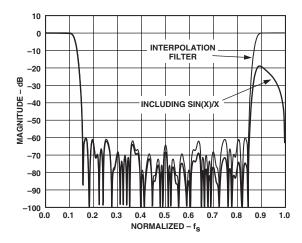

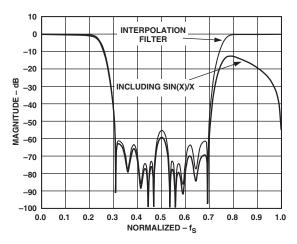

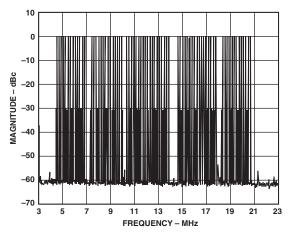

### **AD9876**—Typical Tx Digital Filter Performance Characteristics

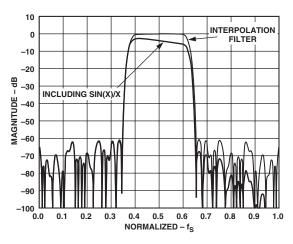

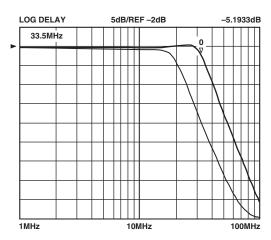

TPC 1. 4× Low-Pass Interpolation Filter

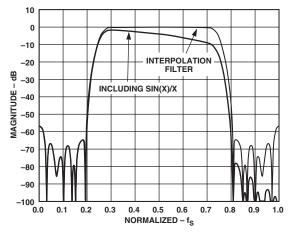

TPC 2. 2× Low-Pass Interpolation Filter

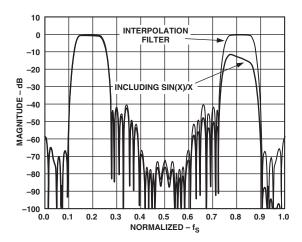

TPC 3.  $4\times$  Band-Pass Interpolation Filter,  $f_S/2$  Modulation, Adjacent Image Preserved

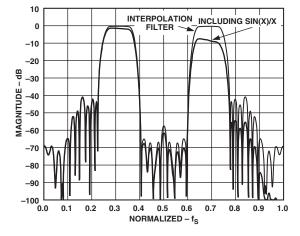

TPC 4.  $2 \times$  Band-Pass Interpolation Filter,  $f_S/2$  Modulation, Adjacent Image Preserved

TPC 5.  $4 \times$  Band-Pass Interpolation Filter,  $f_S/4$  Modulation, Lower Image Preserved

TPC 6.  $4 \times$  Band-Pass Interpolation Filter,  $f_S/4$  Modulation, Upper Image Preserved

-8- REV. A

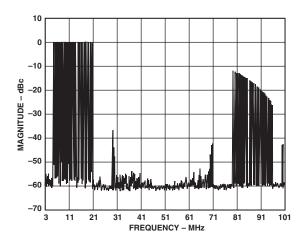

### Typical AC Characteristics Curves for TxDAC+ $(R_{SET} = 4.02 \text{ k}\Omega)$ , $R_{DAC} = 100 \Omega)$

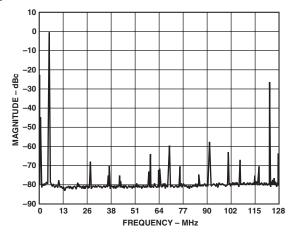

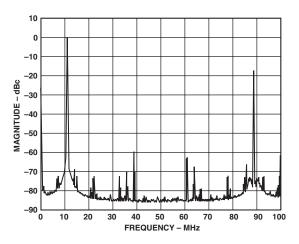

TPC 7. Single-Tone Spectral Plot @  $f_{DATA}$  = 32 MSPS,  $f_{OUT}$  = 5 MHz, 4× LPF

TPC 8. Single-Tone Spectral Plot @  $f_{DATA}$  = 50 MSPS,  $f_{OUT}$  = 11 MHz, 2× LPF

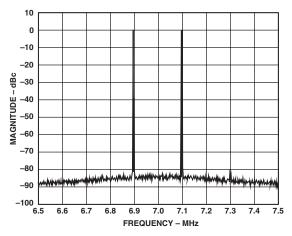

TPC 9. Dual-Tone Spectral Plot @  $f_{DATA}$  = 32 MSPS,  $f_{OUT}$  = 6.9 MHz and 7.1 MHz, 4× LPF

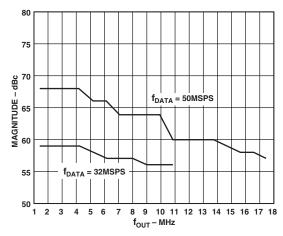

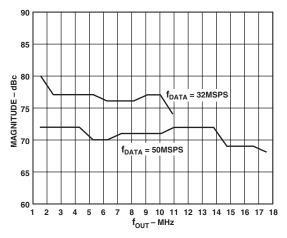

TPC 10. Out-of-Band SFDR vs.  $f_{OUT}$  @  $f_{DATA}$  = 32 MSPS and 50 MSPS

TPC 11. In-Band SFDR vs.  $f_{OUT} @ f_{DATA} = 32 \text{ MSPS}$  and 50 MSPS

TPC 12. Dual-Tone Spectral Plot @  $f_{DATA}$  = 50 MSPS,  $f_{OUT}$  = 6.9 MHz and 7.1 MHz, 2× LPF

REV. A -9-

### Typical AC Characteristics Curves for TxDAC (R<sub>SET</sub> = 4.02 k $\Omega$ , R<sub>DAC</sub> = 100 $\Omega$ )

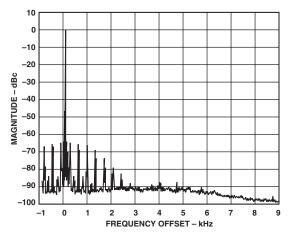

TPC 13. Phase Noise Plot @  $f_{DATA}$  = 32 MSPS,  $f_{OUT}$  = 10 MHz, 4× LPF

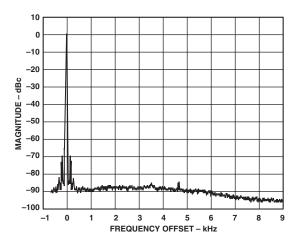

TPC 14. Phase Noise Plot @  $f_{DATA} = 50$  MSPS,  $f_{OUT} = 10$  MHz,  $2 \times$  LPF

TPC 15. In-Band Multitone Spectral Plot @  $f_{DATA} = 50$  MSPS,  $f_{OUT} = k \times 195$  kHz,  $2 \times LPF$

TPC 16. Wideband Multitone Spectral Plot @  $f_{DATA} = 50$  MSPS,  $f_{OUT} = k \times 195$  kHz,  $2 \times LPF$

-10- REV. A

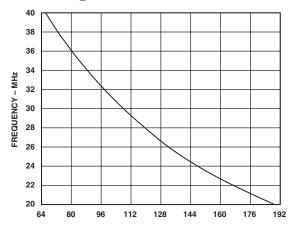

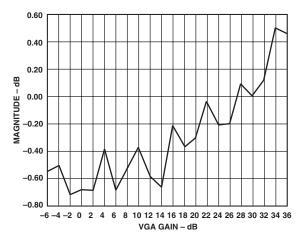

# **Typical Tx Digital Filter Performance Characteristics**

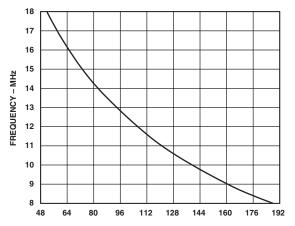

TPC 17. Rx vs. Tuning Target,  $f_{ADC} = 32$  MHz, LPF with Wideband Rx LPF = 1

TPC 18. PGA Gain Error vs. Gain

TPC 19.  $f_C$  vs. Tuning Target,  $f_{ADC}$  = 32 MHz, LPF with Wideband Rx LPF = 0

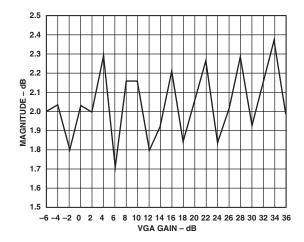

TPC 20. PGA Gain Step Size vs. Gain

REV. A –11–

# Typical AC Characterization Curves for Rx Path

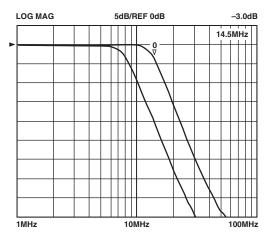

TPC 21. Rx LPF Frequency Response, Low  $f_C$  Nominal Tuning Targets

TPC 22. Rx LPF Frequency Response, High  $f_C$  Nominal Tuning Targets

TPC 23. Rx LPF Frequency Response, Low  $f_C$  0 × 60 and 0 × 96 Turning Targets

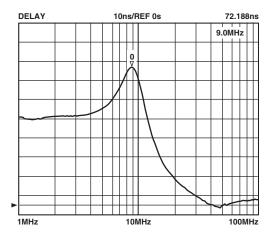

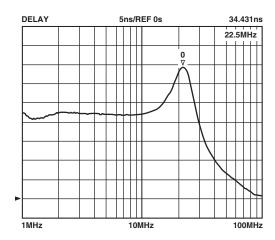

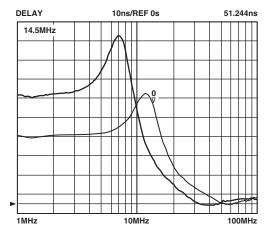

TPC 24. Rx LPF Group Delay, Low  $f_{\rm C}$  Nominal Tuning Targets

TPC 25. Rx LPF Group Delay, High  $f_c$ , Nominal Tuning Targets

TPC 26. Rx LPF Group Delay, Low  $f_C$ ,  $0 \times 60$  and  $0 \times 96$  Tuning Targets

-12- REV. A

### Typical AC Characterization Curves for Rx Path (continued)

TPC 27. Rx LPF Frequency Response, High  $f_c$ ,  $0 \times 60$  and  $0 \times 96$  Tuning Targets

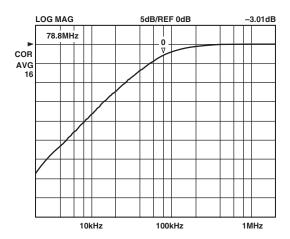

TPC 28. Rx HPF Frequency Response,  $f_{ADC} = 32 \text{ MHz}$

TPC 29. Rx Path Setting, 1/2 Scale Rising Step with Gain Change

TPC 30. Rx LPF Group Delay, High  $f_C$ , 0 × 60 and 0 × 96 Tuning Targets

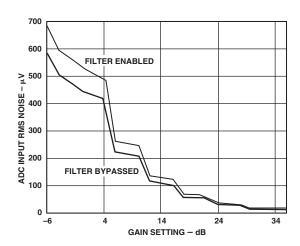

TPC 31. Rx Input Referred Noise vs. Gain @  $f_{ADC}$  = 32 MSPS,  $f_{IN}$  = 1 MHz

TPC 32. Rx Path Setting, 1/2 Scale Falling Step with Gain Change

REV. A -13-

### Typical AC Characterization Curves for Rx Path (Gain = -6 dB, $f_{IN} = 5 MHz$ )

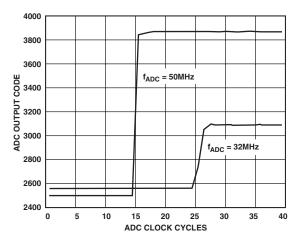

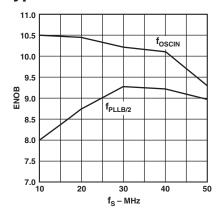

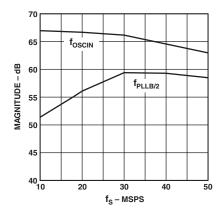

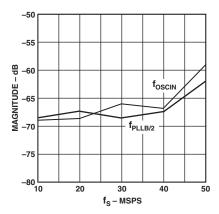

TPC 33. Rx Path ENOB vs. f<sub>ADC</sub>

TPC 34. Rx Path SNR vs. f<sub>ADC</sub>

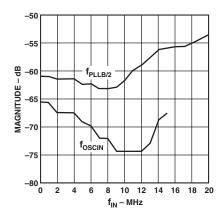

TPC 35. Rx Path THD vs. f<sub>ADC</sub>

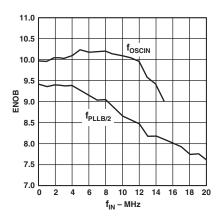

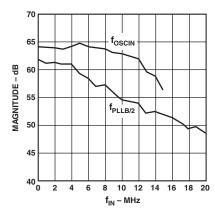

TPC 36. Rx Path ENOB vs. f<sub>IN</sub>

TPX 37. Rx Path SNR vs. f<sub>IN</sub>

TPC 38. Rx Path THD vs. f<sub>IN</sub>

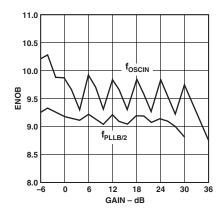

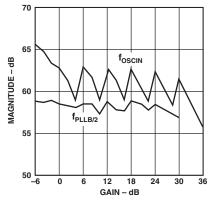

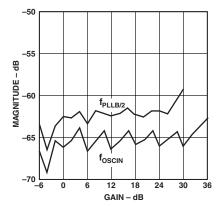

TPC 39. Rx Path ENOB vs. Gain

TPC 40. Rx Path SNR vs. Gain

TPC 41. Rx Path THD vs. Gain

-14- REV. A

### TRANSMIT PATH

The AD9876 transmit path consists of a digital interface port, a programmable interpolation filter, and a transmit DAC. All clock signals required by these blocks are generated from the  $f_{\rm OSCIN}$  signal by the PLL-A clock generator. The block diagram below shows the interconnection between the major functional components of the transmit path.

Figure 1. Transmit Path Block Diagram

#### DIGITAL INTERFACE PORT

The Transmit Digital Interface Port has several modes of operation. In its default configuration, the Tx Port accepts six bit nibbles through the Tx [5:0] and Tx SYNC pins and demultiplexes the data into 12-bit words before passing it to the interpolation filter. The input data is sampled on the rising edge of  $f_{\rm CLK-A}$ .

Additional programming options for the Tx Port allow: sampling the input data on the falling edge of  $f_{CLK-A}$ , inversion or disabling of  $f_{CLK-A}$ , and reversing the order of the nibbles. Also, the Tx Port interface can be controlled by the GAIN pin to provide direct access to the Rx Path Gain Adjust Register. All of these modes are fully described in the Register Programming Definitions section of this data sheet.

The data format is twos complement, as shown below:

011 . . 11: Maximum

000 . . 01: Midscale + 1 LSB

000 . . 00: Midscale

111 . . 11: Midscale – 1 LSB

111 . . 10: Midscale - 2 LSB

100 . . 00: Minimum

The data can be translated to a straight binary data format by simply inverting the most significant bit.

The timing of the interface is fully described in the Transmit Port Timing section of this data sheet.

### PLL-A CLOCK DISTRIBUTION

Figure 1 shows the clock signals used in the transmit path. The DAC sampling clock,  $f_{DAC}$ , is generated by PLL-A.  $f_{DAC}$  has a frequency equal to  $L \times f_{OSCIN}$ , where  $f_{OSCIN}$  is the internal signal generated either by the crystal oscillator when a crystal is connected between the OSCIN and XTAL pins, or by the clock that is fed into the OSCIN pin, and L is the multiplier programmed through the serial port. L can have the values of 1, 2, 4, or 8.

The transmit path expects a new half-word of data at the rate of  $f_{\text{CLK-A}}$ . When the Tx multiplexer is enabled, the frequency of Tx Port is:

$$f_{CLK-A} = 2 \times f_{DAC}/K = 2 \times L \times f_{OSCIN}/K$$

where K is the interpolation factor that can be programmed to be 1, 2, or 4. When the Tx multiplexer is disabled, the frequency of the Tx Port is:

$$f_{CLK-A} = f_{DAC}/K = L \times f_{OSCIN}/K$$

Note, this will result in a 6-bit data path.

### INTERPOLATION FILTER

The interpolation filter can be programmed to run at  $2\times$  and  $4\times$  upsampling ratios in each of three different modes. The transfer functions of these six configurations are shown in TPCs 1–6. The X-axis of each of these figures corresponds to the frequency normalized to  $f_{DAC}$ . These transfer functions show both the discrete time transfer function of the interpolation filters alone and with the SIN(x)/x transfer function of the DAC. The interpolation filter can also be programmed into a pass-through mode if no interpolation filtering is desired.

The contents of the interpolation filter are not cleared by hardware or software resets. It is recommended to "flush" the transmit path with zeros before transmitting data.

The table below contains the following parameters as a function of the mode that it is programmed.

Latency – The number of clock cycles from the time a digital impulse is written to the DAC until the peak value is output at the T+ and T- pins.

Flush – The number of clock cycles from the time a digital impulse is written to the DAC until the output at the Tx+ and Tx- pins settles to zero.

$f_{LOWER}$  (0.1 dB, 3 dB) – This indicates the lower 0.1 dB or 3 dB cutoff frequency of the interpolation filter as a fraction of  $f_{DAC}$ , the DAC sampling frequency.

$f_{UPPER}$  (0.1 dB, 3 dB) – This indicates the upper 0.1 dB or 3 dB cutoff frequency of the interpolation filter as a fraction of  $f_{DAC}$ , the DAC sampling frequency.

Table I. Interpolation Filter Parameters vs. Mode

| Register 7 [7:4]                          | 0 × 0                 | 0 × 1   | 0 × 4               | 0 × 5           | 0 × 8            | 0 × C            |

|-------------------------------------------|-----------------------|---------|---------------------|-----------------|------------------|------------------|

| Mode                                      | $4 \times \text{LPF}$ | 2 × LPF | $4 \times BPF$ Adj. | 2 × BPF<br>Adj. | 4 × BPF<br>Lower | 4 × BPF<br>Upper |

| Latency, f <sub>DAC</sub><br>Clock Cycles | 86                    | 30      | 86                  | 3               | 86               | 86               |

| Flush, f <sub>DAC</sub><br>Clock Cycles   | 128                   | 48      | 128                 | 48              | 148              | 142              |

| f <sub>LOWER</sub> , 0.1 dB               | 0                     | 0       | 0.398               | 0.276           | 0.148/<br>0.774  | 0.274/<br>0.648  |

| f <sub>UPPER</sub> , 0.1 dB               | 0.102                 | 0.204   | 0.602               | 0.724           | 0.226/<br>0.852  | 0.352/<br>0.762  |

| f <sub>LOWER</sub> , 3 dB                 | 0                     | 0       | 0.381               | 0.262           | 0.131/<br>0.757  | 0.257/<br>0.631  |

| f <sub>UPPER</sub> , 3 dB                 | 0.119                 | 0.238   | 0.619               | 0.738           | 0.243/<br>0.869  | 0.369/<br>0.743  |

REV. A -15-

#### D/A CONVERTER

The AD9876 DAC provides differential output current on the Tx+ and Tx- pins. The value of the output currents are complementary, meaning that they will always sum to  $I_{FS}$ , the full-scale current of the DAC. For example, when the current from Tx+ is at full-scale, the current from Tx- is zero. The two currents will typically drive a resistive load that will convert the output currents to a voltage. The Tx+ and Tx- output currents are inherently ground seeking and should each be connected to matching resistors,  $R_{I}$ , that are tied directly to AGND.

The full-scale output current of the DAC is set by the value of the resistor placed from the FSADJ pin to AGND. The relationship between the resistor,  $R_{\rm SET}$ , and the full-scale output current is governed by the following equation:

$$I_{ES} = 39.4/R_{SET}$$

The full-scale current can be set from 2 to 20 mA. Generally, there is a trade-off between DAC performance and power consumption. The best DAC performance will be realized at an  $I_{FS}$  of 20 mA. However, the value of  $I_{FS}$  adds directly to the overall current consumption of the device.

The single-ended voltage output appearing at the Tx+ and Tx-nodes are:

$$V_{Tx+} = I_{Tx+} \times R_L$$

$$V_{Tx-} = I_{Tx-} \times R_L$$

Note that the full-scale voltage of  $V_{Tx+}$  and  $V_{Tx-}$  should not exceed the maximum output compliance range of 1.5 V to prevent signal compression. To maintain optimum distortion and linearity performance, the maximum voltages at  $V_{Tx+}$  and  $V_{Tx-}$  should not exceed 0.5 V.

The single-ended full-scale voltage at either output node will be:

$$V_{ES} = I_{ES} \times R_L$$

The differential voltage,  $V_{DIFF}$ , appearing across  $V_{Tx+}$  and  $V_{Tx-}$  is:

$$\begin{aligned} V_{\textit{DIFF}} &= \left(T_{\textit{Tx}\,+} - T_{\textit{Tx}\,-}\right) \times R_L \\ &\text{and} \\ V_{\textit{DIFF}} &_{\textit{FS}} &= I_{\textit{FS}} \times R_L \end{aligned}$$

For optimum performance, a differential output interface is recommended since any common-mode noise or distortion can be suppressed.

It should be noted that the differential output impedance of the DAC is  $2 \times R_L$  and any load connected across the two output resistors will load down the output voltage accordingly.

### RECEIVE PATH DESCRIPTION

The receive path consists of a two-stage PGA, a continuous time, 4-pole LPF, an ADC, a digital HPF, and a digital data multiplexer. Also working in conjunction with the receive path is an offset correction circuit and a digital phase-lock loop. Each of these blocks will be discussed in detail in the following sections.

### PROGRAMMABLE GAIN AMPLIFIER

The PGA has a programmable gain range from -6 dB to +36 dB if the narrower (approximately 12 MHz) LPF bandwidth is

selected, or if the LPF is bypassed. If the wider (approximately 26 MHz) LPF bandwidth is selected, the gain range is -6 dB to +30 dB. The PGA is comprised of two sections, a continuous time PGA (CPGA) and a switched capacitor PGA (SPGA). The CPGA has possible gain settings of 0, 6, 12, 18, 24, and 30. The SPGA has possible gain settings of -6, -4, -2, 0, +2, +4, and +6 dB. Table V shows how the gain is distributed for each programmed gain setting.

The CPGA input appears at the device Rx+ and Rx– input pins. The input impedance of this stage is nominally 270  $\Omega$  differential and is not gain dependent. It is best to ac-couple the input signal to this stage and let the inputs self bias. This will lower the offset voltage of the input signal, which is important at higher gains, since any offset will lower the output compliance range of the CPGA output. When the inputs are driven by direct coupling, the dc level should be AVDD/2. However, this could lead to larger dc offsets and consequently reduce the dynamic range of the Rx path.

### **LOW-PASS FILTER**

The low-pass filter (LPF) is a programmable, multistage, fourth order filter comprised of two real poles and a complex pole pair. The first real pole is implemented within the CPGA. The second filter stage implements a complex pair of poles. The last real pole is implemented in a buffer stage that drives the SPGA.

There are two pass-band settings for the LPF. Within each pass band the filters are tunable over about a  $\pm 30\%$  frequency range. The formula for the cutoff frequency is:

$$\begin{split} f_{CUTOFF\ LOW} &= f_{ADC} \times 64 \big/ \big( 64 + Target \big) \\ f_{CUTOFF\ HIGH} &= f_{ADC} \times 158 \big/ \big( 64 + Target \big) \end{split}$$

where *Target* is the decimal value programmed as the tuning target in Register 5.

This filter may also be bypassed by setting Bit 0 of Register 4. In this case, the bandwidth of the Rx path will decrease with increasing gain and will be approximately 50 MHz at the highest gain settings.

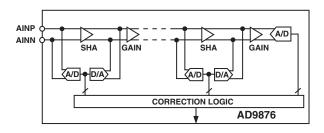

### **ADC**

The AD9876's analog-to-digital converter implements a pipelined multistage architecture to achieve high sample rates while consuming low power. The ADC distributes the conversion over several smaller A/D subblocks, refining the conversion with progressively higher accuracy as it passes the results from stage to stage. As a consequence of the distributed conversion, ADCs require a small fraction of the 2<sup>N</sup> comparators used in a traditional n-bit flash-type A/D. A sample-and-hold function within each of the stages permits the first stage to operate on a new input sample while the remaining stages operate on preceding samples. Each stage of the pipeline, excluding the last, consists of a low resolution flash A/D connected to a switched capacitor DAC and interstage residue amplifier (MDAC). The residue amplifier amplifies the difference between the reconstructed DAC output and the flash input for the next stage in the pipeline. One bit of redundancy is used in each one of the stages to facilitate digital correction of flash errors. The last stage simply consists of a flash A/D.

–16– REV. A

Figure 2. ADC Theory of Operation

The digital data outputs of the ADC are represented in two's complement format. They saturate to full scale or zero when the input signal exceeds the input voltage range.

The twos complement data format is shown below:

011 . . 11: Maximum

000 . . 01: Midscale + 1 LSB

000 . . 00: Midscale

111 . . 11: Midscale - 1 LSB

111 . . 10: Midscale - 2 LSB

100 . . 00: Minimum

The maximum value will be output from the ADC when the Rx+ input is 1 V or more greater than the Rx- input. The minimum value will be output from the ADC when the Rx- input is 1 V or more greater than the Rx+ input. This results in a full-scale ADC voltage of 2 Vppd.

The data can be translated to straight binary data format by simply inverting the most significant bit.

The best ADC performance will be achieved when the ADC clock source is selected from f<sub>OSCIN</sub> and the OSCIN pin is driven from a low jitter clock source. The amount of degradation from jitter on the ADC clock will depend on how quickly the input is varying at the sampling instance. TPC 36 charts this effect in the form of ENOB vs. input frequency for the two clocking scenarios.

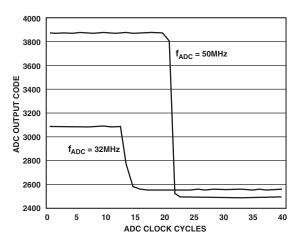

The maximum sample rate of the ADC in Full-Precision Mode, that is outputting 12 bits, is 55 MSPS. TPC 33 shows the ADC performance in ENOB versus  $f_{\rm ADC}$ . The maximum sample rate of the ADC in Half-Precision Mode, that is outputting five bits, is 64 MSPS. The timing of the interface is fully described in the Receive Port Timing section of this data sheet.

### **DIGITAL HPF**

Following the ADC, there is a bypassable digital HPF. The response is a single-pole IIR HPF. The transfer function is:

$$H(z) = (1-0.99994Z^{-1})/(1-98466Z^{-1})$$

where the sampling period is equal to the ADC clock period. This results in a 3 dB frequency approximately 1/400th of the ADC sampling rate. The transfer functions are plotted for 32 MSPS and 50 MSPS in TPC 29 and TPC 32.

The digital HPF introduces a 1 ADC clock cycle latency. If the HPF function is not desired, the HPF can be bypassed and the latency will not be incurred.

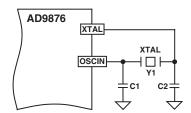

#### CLOCK AND OSCILLATOR CIRCUITRY

The AD9876's internal oscillator generates all sampling clocks from a fundamental frequency quartz crystal. Figure 3a shows how the quartz crystal is connected between OSCIN (Pin 1) and XTAL (Pin 48) with parallel resonant load capacitors as specified by the crystal manufacturer. The internal oscillator circuitry can also be overdriven by a TTL-level clock applied to OSCIN with XTAL left unconnected.

The PLL has a frequency capture range between 10 MHz and 64 MHz.

Figure 3a. Connections for a Fundamental Mode Crystal

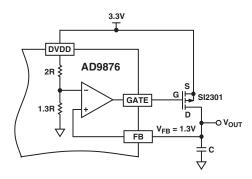

### **VOLTAGE REGULATOR CONTROLLER**

The AD9876 contains an on-chip voltage regulator controller (VRC) for providing a linear 1.3 V supply for low voltage digital circuitry or other external use. The VRC consists of an op amp and a resistive voltage divider. As shown in Figure 3b, the resistive divider establishes a voltage of 1.3 V at the inverting input of the amplifier when DVDD is equal to its nominal voltage of 3.3 V. The feedback loop around the op amp will adjust the gate voltage such that the voltage at the FB pin,  $V_{\rm FB}$ , will be equal to the voltage at the inverting input of the op amp.

Figure 3b. Connections for 1.3 V Linear Regulator

The maximum current output from the circuit is largely dependent on the MOSFET device. For the SI2301 shown, 250 mA can be delivered. The regulated output voltage should have bulk decoupling and high frequency decoupling capacitors to ground as required by the load. The regulator circuit will be stable for capacitive loads between 0.1  $\mu F$  and 47  $\mu F$ .

It should be noted that the regulated output voltage,  $V_{FB}$ , is proportional to DVDD. Therefore, the percentage variation in DVDD will also be seen at the regulated output voltage. The load regulation is roughly equal to the ON resistance of the MOSFET device chosen. For the SI2301, this is about 60 m $\Omega$ .

REV. A –17–

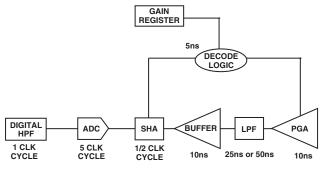

### AGC TIMING CONSIDERATIONS

When implementing the AGC timing loop, it is important to consider the delay and settling time of the Rx path in response to a change in gain. Figure 4 shows the delay the receive signal experiences through the blocks of the Rx path. Whether the gain is programmed through the serial port or over the Tx [5:0] pins, the gain takes effect immediately with the delays shown below. When gain changes do not involve the CPGA, the new gain will be evident in samples after seven ADC clock cycles. When the gain change does involve the CPGA, it takes an additional 45 ns to 70 ns due to the propagation delays of the buffer, LPF and PGA. Table V, details the PGA programming map.

Figure 4. AGC Timing

### **Transmit Port Timing**

The AD9876 transmit port consists of a 6-bit databus Tx [5:0], a clock, and a Tx SYNC signal. Two consecutive nibbles of the Tx data are multiplexed together to form a 12-bit data-word. The clock appearing on the CLK-A pin is a buffered version of the internal Tx data sampling clock. Data from the Tx port is read on the rising edge of this sampling clock. The Tx SYNC signal is used to indicate to which word a nibble belongs. The first nibble of every word is read while Tx SYNC is low, the second nibble of that same word is read on the following Tx SYNC high level. The timing is illustrated in the Figure 5.

Figure 5. Transmit Timing Diagram AD9876

The Tx Port is highly configurable and offers the following options. Negative edge sampling can be chosen by two different methods; either by certing the Tx Port Negative Edge Sampling Bit (Pog.

either by setting the Tx Port Negative Edge Sampling Bit (Register 3, Bit 7) or the Invert CLK-A Bit (Register 8, Bit 6). The main difference between the two methods is that setting Register 3, Bit 7 inverts the internal sampling clock and will affect only the transmit path, even if CLK-A is used to clock the Rx data. However, inverting CLK-A would affect both the Rx and Tx paths if they both use CLK-A.

The first nibble of each word can be read in as the least significant nibble by setting the Tx LS Nibble First Bit (Register 7, Bit 2).

Also, the Tx path can be used in a Reduced Resolution Mode by setting the Tx Port Multiplexer Bypass Bit (Register 7, Bit 0). In this mode, the Tx data-word becomes six bits and is read in a single cycle. The clocking modes are the same as described above, but the level of Tx SYNC is irrelevant.

If Tx SYNC is low for more than one clock cycle, the last transmit data will read continuously until Tx SYNC is brought high for the second nibble of a new transmit word. This feature can be used to "flush" the interpolator filters with zeros.

#### **PGA Adjust Timing**

In addition to the serial port, the Tx [5:1] pins can be used to write to the Rx Path Gain Adjust Bits (Register 6, Bits 4:0). This provides a faster way to update the PGA gain. A high level on the GAIN pin with Tx SYNC low programs the PGA setting on either the rising edge or falling edge of CLK-A. The GAIN pin must be held high, Tx SYNC must be held low, and GAIN data must be stable for three clock cycles to successfully update the PGA GAIN value. A low level on the GAIN pin enables data to be fed to the interpolator and DAC.

Figure 6. GAIN Programming

### **Receive Port Timing**

The AD9876 receives port consists of a six bit databus Rx [5:0], a clock, and an Rx SYNC signal. Two consecutive nibbles of the Rx data are multiplexed together to form a 10-/12-bit data-word. The Rx data is valid on the rising edge of CLK-A when the ADC Clock Source PLL-B/2 Bit (Register 3, Bit 6) is set to 0. The Rx SYNC signal is used to indicate to which word a nibble belongs. The first nibble of every word is transmitted while Rx SYNC is low, the second nibble of that same word is transmitted on the following Rx SYNC high level. When Rx SYNC is low, the sampled nibble is read as the most significant nibble. When the Rx SYNC is high, the sampled nibble is read as the least significant nibble. The timing is illustrated in Figure 7.

Figure 7. Receive Timing Diagram

The Rx Port is highly configurable and offers the following options.

Negative edge sampling can be chosen by setting the Invert CLK-A Bit (Register 8, Bit 6) or the Invert CLK-B Bit (Register 8, Bit 7), depending on the clock selected as the ADC sampling

–18– REV. A

source. Inverting CLK-A would affect the Tx sampling edge as well as the Rx sampling edge.

The first nibble of each word can be read in as the least significant nibble by setting the Rx LS Nibble First Bit (Register 8, Bit 2).

Also, the Rx path can be used in a Reduced Resolution Mode by setting the Rx Port Multiplexer Bypass Bit (Register 8, Bit 0). In this mode, the Rx data-word becomes six bits and is read in a single cycle. The Clocking Modes are the same as described above, but the level of Rx SYNC will stay low.

The Rx [5:0] pins can be put into a high impedance state by setting the Three-State Rx Port Bit (Register 8, Bit 3).

### SERIAL INTERFACE FOR REGISTER CONTROL

The serial port is a 3-wire serial communications port consisting of a clock (SCLK), chip select (SENABLE), and a bidirectional data (SDATA) signal. The interface allows read/write access to all registers that configure the AD9876 internal parameters. Single or multiple byte transfers are supported as well as MSB first or LSB first transfer formats.

### General Operation of the Serial Interface

Serial communication over the serial interface can be from 1 to 5 bytes in length. The first byte is always the instruction byte. The instruction byte establishes whether the communication is going to be a read or write access, the number of data bytes to be transferred, and the address of the first register to be accessed. The instruction byte transfer is complete immediately upon the 8th rising edge of SCLK after  $\overline{\text{SENABLE}}$  is asserted. Likewise, the data registers change *immediately* upon writing to the 8th bit of each data byte.

### **Instruction Byte**

The instruction byte contains the following information as shown below.

Table II. Instruction Byte Information

| MSB        |            |    |            |            |    |    | LSB |

|------------|------------|----|------------|------------|----|----|-----|

| <b>I</b> 7 | <b>I</b> 6 | 15 | <b>I</b> 4 | 13         | I2 | I1 | 10  |

| R/W        | N1         | N0 | <b>A</b> 4 | <b>A</b> 3 | A2 | A1 | A0  |

#### Bit I7 - R/W

This bit determines whether a read or a write data transfer will occur after the instruction byte write. Logic high indicates read operation; logic zero indicates a write operation.

### Bits I6:I5 - N1:N0

These two bits determine the number of bytes to be transferred during the data transfer cycle. The bit decodes are shown in the table below.

Table III. Decode Bits

| N1:N0 | Description      |

|-------|------------------|

| 0:0   | Transfer 1 Byte  |

| 0:1   | Transfer 2 Bytes |

| 1:0   | Transfer 3 Bytes |

| 1:1   | Transfer 4 Bytes |

#### Bits I4:I0 - A4:A0

These bits determine which register is accessed during the data transfer portion of the communications cycle. For multibyte transfers, this address is the starting byte address. The remaining register addresses are generated by the AD9876/AD9875.

### Serial Interface Port Pin Description SCLK—Serial Clock

The serial clock pin is used to synchronize data transfers to and from the AD9876 and to run the internal state machines. SCLK maximum frequency is 25 MHz. All data transmitted to the AD9876 is sampled on the rising edge of SCLK. All data read from the AD9876 is validated on the rising edge of SCLK and is updated on the falling edge.

### **SENABLE**—Serial Interface Enable

The SENABLE pin is active low. It enables the serial communication to the device. SENABLE select should stay low during the entire communication cycle. All input on the serial port is ignored when SENABLE is inactive.

### SDATA—Serial Data I/O

The signal on this line is sampled on the first eight rising edges of SCLK after SENABLE goes active. Data is then read from or written to the AD9876 depending on what was read.

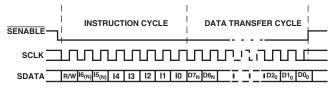

Figures 8 and 9 show the timing relationships between the three SPI signals.

Figure 8. Timing Diagram Register Write to AD9876

Figure 9. Timing Diagram Register Read from AD9876

### **MSB/LSB Transfers**

The AD9876 serial port can support both most significant bit (MSB) first or least significant bit (LSB) first data formats. The bit order is controlled by the SPI LSB First Bit (Register 0, Bit 6). The default value is 0, MSB first. Multibyte data transfers in MSB format can be completed by writing an instruction byte that includes the register address of the last address to be accessed. The AD9876 will automatically decrement the address for each successive byte required for the multibyte communication cycle.

When the SPI LSB First Bit (Register 0, Bit 6) is set high, the serial port interprets both instruction and data bytes LSB first. Multibyte data transfers in LSB format can be completed by writing an instruction byte that includes the register address of

the first address to be accessed. The AD9876 will automatically increment the address for each successive byte required for the multibyte communication cycle.

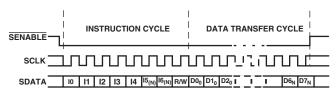

Figures 10a and 10b show how the serial port words are built for each of these modes.

Figure 10a. Serial Register Interface Timing MSB-First

Figure 10b. Serial Register Interface Timing LSB-First

### **Notes on Serial Port Operation**

The serial port is disabled and all registers are set to their default values during a hardware reset. During a software reset, all registers except Register 0 are set to their default values. Register 0 will remain at the last value sent, with the exception that the Software Reset Bit will be set to 0.

The serial port is operated by an internal state machine and is dependent on the number of SCLK cycles since the last time SENABLE went active. On every eighth rising edge of SCLK, a byte is transferred over the SPI. During a multibyte write cycle, this means the registers of the AD9876 are not simultaneously updated but occur sequentially. For this reason, it is recommended that single byte transfers be used when changing the SPI configuration or performing a software reset.

Table IV. Register Layout

| Address<br>(hex) | Bit 7                                   | Bit 6                                          | Bit 5                              | Bit 4                                                                    | Bit 3                          | Bit 2                             | Bit 1                             | Bit 0                                | Default<br>(hex) | Comments                         |

|------------------|-----------------------------------------|------------------------------------------------|------------------------------------|--------------------------------------------------------------------------|--------------------------------|-----------------------------------|-----------------------------------|--------------------------------------|------------------|----------------------------------|

| 0                |                                         | SPI<br>LSB First                               | Software<br>Reset                  |                                                                          |                                |                                   |                                   |                                      | 0 × 00           | Read/Write                       |

| 1                | Power-<br>Down<br>Regulator             | Power-<br>Down<br>PLL-B                        | Power-<br>Down<br>PLL-A            | Power-<br>Down<br>DAC                                                    | Power-<br>Down<br>Interpolator | Power-<br>Down<br>Rx<br>Reference | Power-<br>Down<br>ADC and<br>FPGA | Power-<br>Down<br>Rx LPF and<br>CPGA | 0 × 00           | Read/Write<br>PWR DN<br>Pin Low  |

| 2                | Power-<br>Down<br>Regulator             | Power-<br>Down<br>PLL-B                        | Power-<br>Down<br>PLL-A            | Power-<br>Down<br>DAC                                                    | Power-<br>Down<br>Interpolator | Power-<br>Down<br>Rx<br>Reference | Power-<br>Down<br>ADC and<br>FPGA | Power-<br>Down<br>Rx LPF and<br>CPGA | 0×9F             | Read/Write<br>PWR DN<br>Pin High |

| 3                | Tx Port<br>Negative<br>Edge<br>Sampling | ADC Clock<br>Source<br>PLL-B/2                 | (×M)                               | (×M) Multiplier (/N) Divider (×                                          |                                | er (/N) Divider (×M)              |                                   | I) Multiplier                        | 0 × 02           | Read/Write                       |

| 4                | Rx Port<br>Negative<br>Edge<br>Sampling | Rx LPF<br>Tuning<br>In Progress<br>(Read-Only) | Rx Path<br>DC Offset<br>Correction | Rx Digital<br>HPF<br>Bypass                                              | Fast ADC<br>Sampling           | Wideband<br>Rx LPF                | Enable<br>1-Pole<br>Rx LPF        | Rx LPF<br>Bypass                     | 0 × 01           | Read/Write                       |

| 5                |                                         |                                                | Rx L                               | PF f <sub>c</sub> Adjust                                                 | <7:0>                          |                                   |                                   |                                      | 0 × 80           | Read/Write                       |