# RENESAS

# 4286 Group SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

## DESCRIPTION

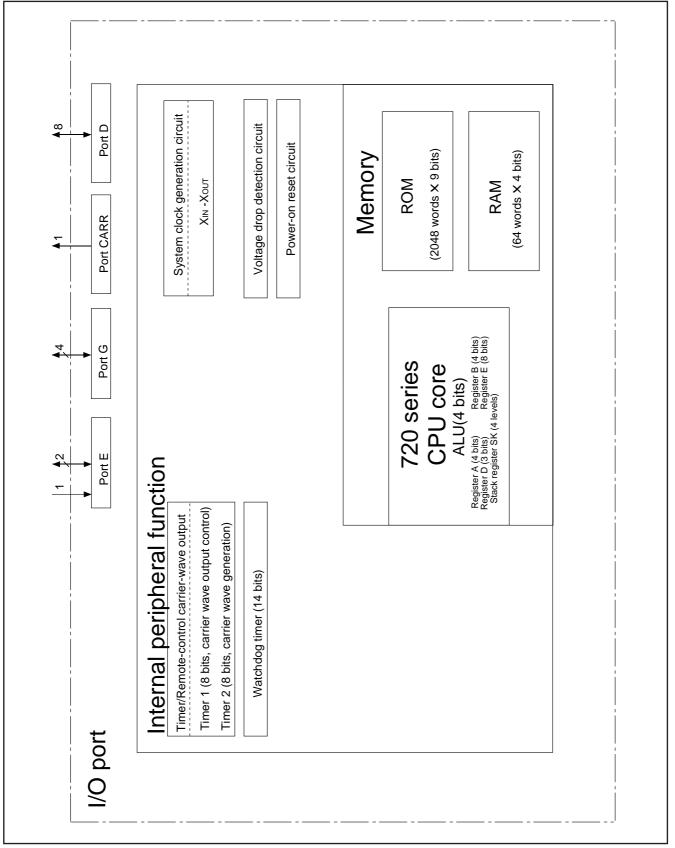

The 4286 Group is a 4-bit single-chip microcomputer designed with CMOS technology for single-function remote control transmitters. The computer is equipped with an 8-bit timer (has two reload registers) can be set various carrier wave and an 8bit timer (has a reload register) can be control the carrier wave output automatically.

The various microcomputers in the 4286 Group include variations of type as shown in the table below.

# **FEATURES**

- Minimum instruction execution time ...... 2.0  $\mu s$

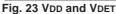

- Timer Timer 1 ..... 8-bit timer (This has a reload register and carrier wave output auto-control function) Timer 2 ...... 8-bit timer (This has two reload registers and carrier wave output function) • Logic operation function (XOR, OR, AND) • RAM back-up function • Key-on wakeup function (ports D0-D7, E0-E2, G0-G3) .... 15 • I/O port (ports D, E, G, CARR) ..... 16 Oscillation circuit ...... Ceramic resonance Watchdog timer ٠ Power-on reset circuit Voltage drop detection circuit Before CLVD instruction execution Reset occurrence ..... 1.5 V (Ta=25 °C) Reset release ..... 1.7 V (Ta=25 °C) After CLVD instruction execution Reset occurrence/Reset release ...... 1.7 V (Ta=25 °C)

# APPLICATION

Consumer remote control transmitters

| Part number    | ROM size<br>(× 9 bits) | RAM size<br>(× 4 bits) | Package                | ROM type      |

|----------------|------------------------|------------------------|------------------------|---------------|

| M34286G2-XXXGP | 2048 words             | 64 words               | PLSP0020JB-A (20P2F-A) | QzROM         |

| M34286G2GP     | 2048 words             | 64 words               | PLSP0020JB-A (20P2F-A) | QzROM (blank) |

**BLOCK DIAGRAM**

# PERFORMANCE OVERVIEW

| Pa                           | arameter  |              | Function                                                                                |  |

|------------------------------|-----------|--------------|-----------------------------------------------------------------------------------------|--|

| Number of basic instructions |           | ctions       | 72                                                                                      |  |

| Minimum instru               | uction ex | ecution time | 2.0 $\mu$ s (f(XIN) = 4.0 MHz, system clock = f(XIN)/2, VDD = 3.0 V)                    |  |

| Memory sizes                 | ROM       |              | 2048 words X 9 bits                                                                     |  |

|                              | RAM       |              | 64 words X 4 bits                                                                       |  |

| Input/Output                 | D0-D7     | I/O          | Eight 1-bit I/O ports with the pull-down function and key-on wakeup function            |  |

| ports                        | E0-E2     | I/O          | 3-bit I/O port with the pull-down function and key-on wakeup function                   |  |

|                              | G0–G3 I/O |              | 4-bit I/O port with the pull-down function and key-on wakeup function                   |  |

| CARR Output                  |           | Output       | 1-bit output port; CMOS output                                                          |  |

| Timer                        | Timer 1   |              | 8-bit timer with a reload register                                                      |  |

|                              | Timer 2   | 2            | 8-bit timer with two reload registers                                                   |  |

| Subroutine nes               | sting     |              | 4 levels (However, only 3 levels can be used when the TABP p instruction is executed)   |  |

| Device structur              | re        |              | CMOS silicon gate                                                                       |  |

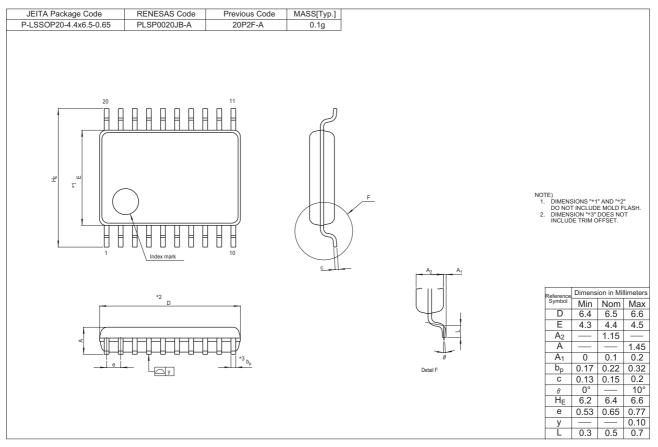

| Package                      |           |              | 20-pin plastic molded LSSOP (PLSP0020JB-A (20P2F-A))                                    |  |

| Operating temp               | perature  | range        | -40 to 85 °C                                                                            |  |

| Supply voltage               | •         |              | 1.8 V to 3.6 V                                                                          |  |

| Power<br>dissipation         | Active I  | mode         | 400 μA (V <sub>DD</sub> = 3 V, STCK=f(X <sub>IN</sub> )/8, f(X <sub>IN</sub> ) = 4 MHz) |  |

| (typical value)              | RAM b     | ack-up mode  | 0.1 μA (Ta = 25 °C, Vdd = 3 V)                                                          |  |

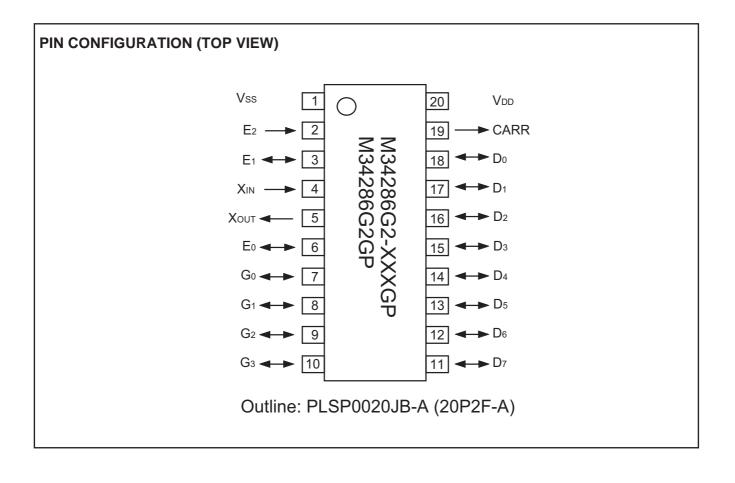

# **PIN DESCRIPTION**

| Pin   | Name                | Input/Output | Function                                                                                       |

|-------|---------------------|--------------|------------------------------------------------------------------------------------------------|

| Vdd   | Power supply        | —            | Connected to a plus power supply.                                                              |

| Vss   | Ground              | —            | Connected to a 0 V power supply.                                                               |

| Xin   | System clock input  | Input        | I/O pins of the system clock generating circuit. Connect a ceramic resonator                   |

| Хоит  | System clock output | Output       | between pins XIN and XOUT. The feedback resistor is built-in between pins XIN and XOUT.        |

| D0-D7 | I/O port D          | I/O          | 1-bit I/O port. For input use, set the latch of the specified bit to "0." When the built-      |

|       |                     |              | in pull-down transistor is turned on, the key-on wakeup function using "H" level               |

|       |                     |              | sense and the pull-down transistor become valid. The output structure is P-channel             |

|       |                     |              | open-drain.                                                                                    |

| E0-E2 | I/O port E          | Output       | 2-bit (E0, E1) output port. The output structure is P-channel open-drain.                      |

|       |                     | Input        | 3-bit input port. For input use (E0, E1), set the latch of the specified bit to "0."           |

|       |                     |              | When the built-in pull-down transistor is turned on, the key-on wakeup function                |

|       |                     |              | using "H" level sense and the pull-down transistor become valid. Port E2 has an                |

|       |                     |              | input-only port and has a key-on wakeup function using "H" level sense and pull-               |

|       |                     |              | down transistor.                                                                               |

| G0–G3 | I/O port G          | I/O          | 4-bit I/O port. For input use, set the latch of the specified bit to "0." The output structure |

|       |                     |              | is P-channel open-drain. When the built-in pull-down transistor is turned on, the key-         |

|       |                     |              | on wakeup function using "H" level sense and pull-down transistor become valid.                |

| CARR  | Carrier wave output | Output       | Carrier wave output pin for remote control. The output structure is CMOS circuit.              |

|       | for remote control  |              |                                                                                                |

# **CONNECTIONS OF UNUSED PINS**

| Pin    | Connection                          | Usage condition           |

|--------|-------------------------------------|---------------------------|

| D0-D7  | Open (Set the output latch to "1"). | Pull-down transistor OFF. |

|        | Open (Set the output latch to "0"). |                           |

|        | Connect to VDD.                     | Pull-down transistor OFF. |

| E0, E1 | Open (Set the output latch to "1"). | Pull-down transistor OFF. |

|        | Open (Set the output latch to "0"). |                           |

|        | Connect to VDD.                     | Pull-down transistor OFF. |

| E2     | Open.                               |                           |

|        | Connect to Vss.                     |                           |

| G0-G3  | Open (Set the output latch to "1"). | Pull-down transistor OFF. |

|        | Open (Set the output latch to "0"). |                           |

|        | Connect to VDD.                     | Pull-down transistor OFF. |

| CARR   | Open.                               |                           |

(Note when connecting to Vss and VDD)

• Connect the unused pins to Vss or Vbb at the shortest distance and use the thick wire against noise.

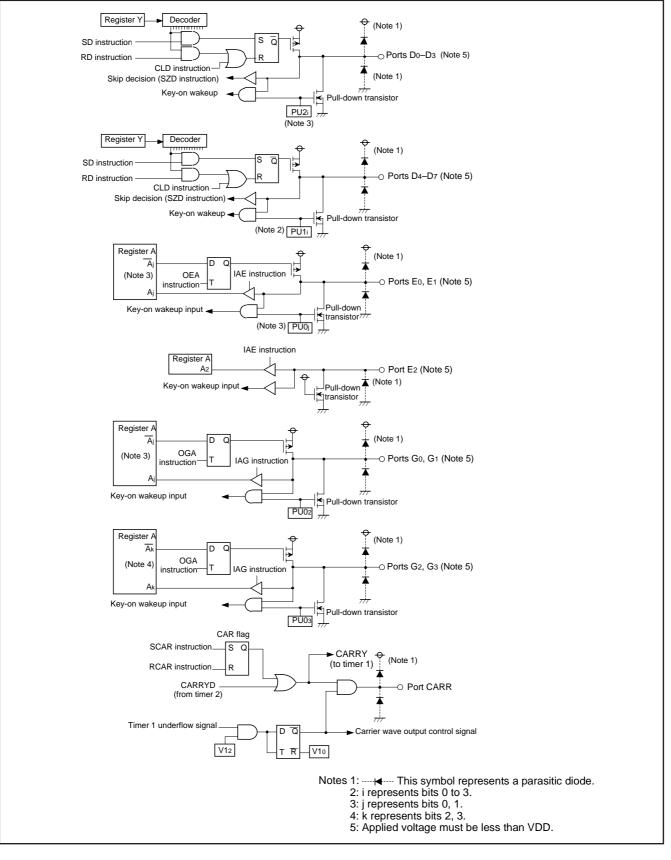

#### **PORT FUNCTION**

| Port      | Dim   | Input/ |                      | Control | Control      | Control   | Remark                 |

|-----------|-------|--------|----------------------|---------|--------------|-----------|------------------------|

| FUIL      | Pin   | Output | Output structure     | bits    | instructions | registers | Remark                 |

| Port D    | D0-D7 | I/O    | P-channel open-drain | 1 bit   | SD           | PU1, PU2  | Pull-down function and |

|           |       | (8)    |                      |         | RD           |           | key-on wakeup function |

|           |       |        |                      |         | CLD          |           | (programmable)         |

|           |       |        |                      |         | SZD          |           |                        |

| Port E    | Eo    | I/O    | P-channel open-drain | Output: | OEA          | PU0       | Pull-down function and |

|           | E1    | (2)    |                      | 2 bits  | IAE          |           | key-on wakeup function |

|           |       |        |                      | Input:  |              |           | (programmable)         |

|           | E2    | Input  |                      | 3 bits  | IAE          |           |                        |

|           |       | (1)    |                      |         |              |           |                        |

| Port G    | G0–G3 | I/O    | P-channel open-drain | 4 bits  | OGA          | PU0       | Pull-down function and |

|           |       | (4)    |                      |         | IAG          |           | key-on wakeup function |

|           |       |        |                      |         |              |           | (programmable)         |

| Port CARR | CARR  | Output | CMOS                 | 1 bit   | SCAR         |           |                        |

|           |       | (1)    |                      |         | RCAR         |           |                        |

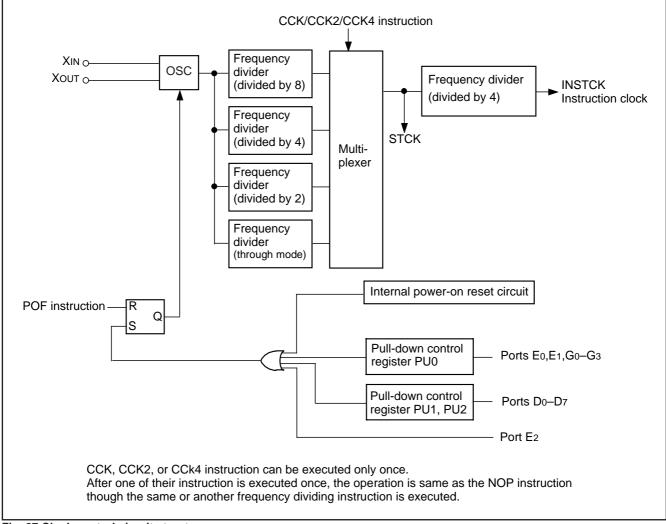

# DEFINITION OF CLOCK AND CYCLE

• System clock (STCK)

The system clock is the source clock for controlling this product. It can be selected as shown below whether to use the Oscillation dividing instruction.

CCK, CCK2, or CCK4 instruction can be executed only once. After one of their instruction is executed once, the operation is same as the NOP instruction though the same or another frequency dividing instruction is executed.

The system clock returns to its initial state (f(XIN)/8) when system is returnd from RAM back-up mode.

| Oscillation dividing<br>instruction | System clock | Instruction clock |

|-------------------------------------|--------------|-------------------|

| No use                              | f(XIN)/8     | f(XIN)/32         |

| CCK used                            | f(XIN)       | f(XIN)/4          |

| CCK2 used                           | f(XIN)/2     | f(XIN)/8          |

| CCK4 used                           | f(XIN)/4     | f(XIN)/16         |

• Instruction clock (INSTCK)

The instruction clock is a signal derived by dividing the system clock by 4, and is the basic clock for controlling CPU. The one instruction clock cycle is equivalent to one machine cycle.

• Machine cycle

The machine cycle is the cycle required to execute the instruction.

# PORT BLOCK DIAGRAMS

# FUNCTION BLOCK OPERATIONS CPU

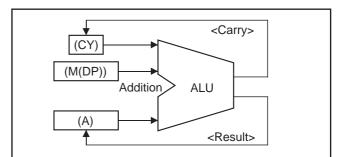

#### (1) Arithmetic logic unit (ALU)

The arithmetic logic unit ALU performs 4-bit arithmetic such as 4-bit data addition, comparison, and bit manipulation.

#### (2) Register A and carry flag

Register A is a 4-bit register used for arithmetic, transfer, exchange, and I/O operation.

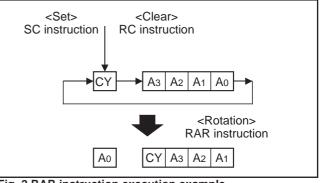

Carry flag CY is a 1-bit flag that is set to "1" when there is a carry with the AMC instruction (Figure 1).

It is unchanged with both A n instruction and AM instruction. The value of  $A_0$  is stored in carry flag CY with the RAR instruction (Figure 2).

Carry flag CY can be set to "1" with the SC instruction and cleared to "0" with the RC instruction.

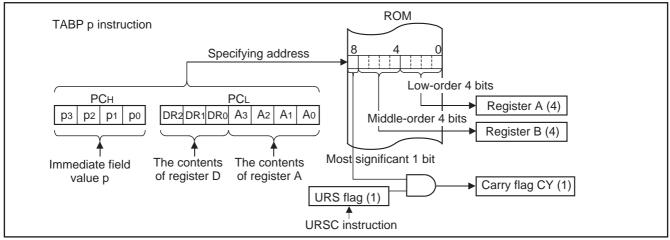

#### (3) Registers B and E

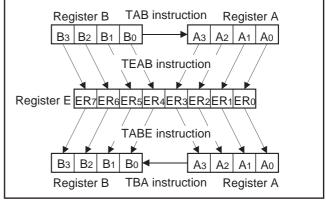

Register B is a 4-bit register used for temporary storage of 4bit data, and for 8-bit data transfer together with register A. Register E is an 8-bit register. It can be used for 8-bit data transfer with register B used as the high-order 4 bits and register A as the low-order 4 bits (Figure 3).

#### (4) Register D

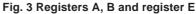

Register D is a 3-bit register.

It is used to store a 7-bit ROM address together with register A and is used as a pointer within the specified page when the TABP p, BLA p, or BMLA p instruction is executed (Figure 4).

Fig. 1 AMC instruction execution example

Fig. 2 RAR instruction execution example

Fig. 4 TABP p instruction execution example

(5) Most significant ROM code reference enable flag (URS) URS flag controls whether to refer to the contents of the most significant 1 bit (bit 8) of ROM code when executing the TABP p instruction. If URS flag is "0," the contents of the most significant 1 bit of ROM code is not referred even when executing the TABP p instruction. However, if URS flag is "1," the contents of the most significant 1 bit of ROM code is set to flag CY when executing the TABP p instruction (Figure 4).

URS flag is "0" after system is released from reset and returned from RAM back-up mode. It can be set to "1" with the URSC instruction, but cannot be cleared to "0."

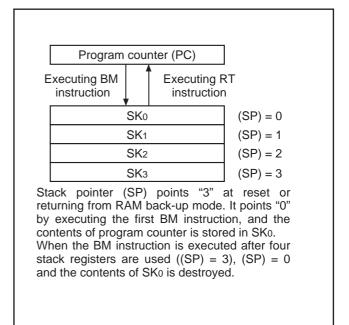

#### (6) Stack registers (SKs) and stack pointer (SP)

Stack registers (SKs) are used to temporarily store the contents of program counter (PC) just before branching until returning to the original routine when;

- performing a subroutine call, or

- executing the table reference instruction (TABP p).

Stack registers (SKs) are four identical registers, so that subroutines can be nested up to 4 levels. However, one of stack registers is used when executing a table reference instruction. Accordingly, be careful not to over the stack. The contents of registers SKs are destroyed when 4 levels are exceeded.

The register SK nesting level is pointed automatically by 2-bit stack pointer (SP).

Figure 5 shows the stack registers (SKs) structure.

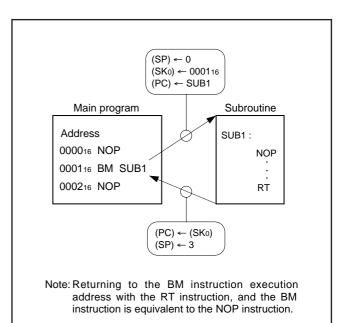

Figure 6 shows the example of operation at subroutine call.

#### (7) Skip flag

Skip flag controls skip decision for the conditional skip instructions and continuous described skip instructions.

Note : The 4286 Group just invalidates the next instruction when a skip is performed. The contents of program counter is not increased by 2. Accordingly, the number of cycles does not change even if skip is not performed. However, the cycle count becomes "1" if the TABP p, RT, or RTS instruction is skipped.

Fig. 5 Stack registers (SKs) structure

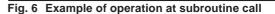

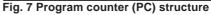

#### (8) Program counter (PC)

Program counter (PC) is used to specify a ROM address (page and address). It determines a sequence in which instructions stored in ROM are read. It is a binary counter that increments the number of instruction bytes each time an instruction is executed. However, the value changes to a specified address when branch instructions, subroutine call instructions, return instructions, or the table reference instruction (TABP p) is executed.

Program counter consists of PC<sub>H</sub> (most significant bit to bit 7) which specifies to a ROM page and PC<sub>L</sub> (bits 6 to 0) which specifies an address within a page. After it reaches the last address (address 127) of a page, it specifies address 0 of the next page (Figure 7).

Make sure that the  $\mathsf{PC}\mathsf{H}$  does not exceed after the last page of the built-in ROM.

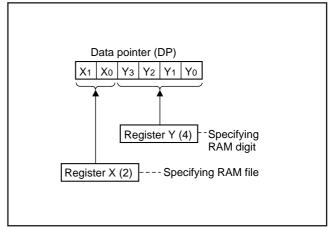

#### (9) Data pointer (DP)

Data pointer (DP) is used to specify a RAM address and consists of registers X and Y. Register X specifies a file and register Y specifies a RAM digit (Figure 8).

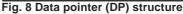

Register Y is also used to specify the port D bit position.

When using port D, set the port D bit position to register Y certainly and execute the SD, RD, or SZD instruction (Figure 9).

Fig. 9 SD instruction execution example

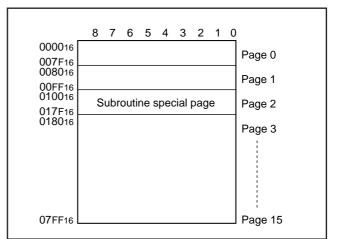

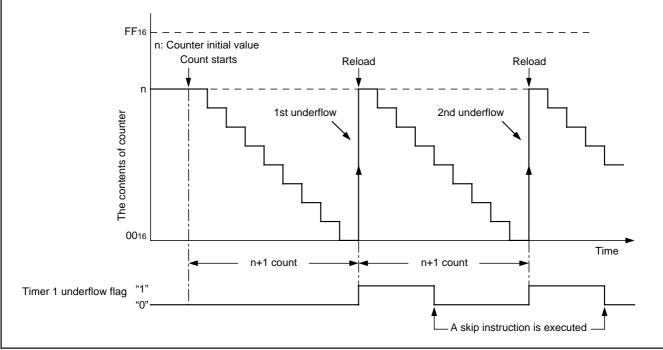

# **PROGRAM MEMORY (ROM)**

The program memory is a mask ROM. 1 word of ROM is composed of 9 bits. ROM is separated every 128 words by the unit of page (addresses 0 to 127).

#### Table 1 ROM size and pages

| Part number | ROM size (X 9 bits) | Pages        |

|-------------|---------------------|--------------|

| M34286G2    | 2048 words          | 16 (0 to 15) |

Page 2 (addresses 010016 to 017F16) is the special page for subroutine calls. Subroutines written in this page can be called from any page with the 1-word instruction (BM). Subroutines extending from page 2 to another page can also be called with the BM instruction when it starts on page 2.

ROM pattern of all addresses can be used as data areas with the TABP  $\ensuremath{\mathsf{p}}$  instruction.

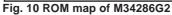

# DATA MEMORY (RAM)

1 word of RAM is composed of 4 bits, but 1-bit manipulation (with the SB j, RB j, and SZB j instructions) is enabled for the entire memory area. A RAM address is specified by a data pointer. The data pointer consists of registers X and Y. Set a value to the data pointer certainly when executing an instruction to access RAM.

Table 2 shows the RAM size. Figure 11 shows the RAM map.

#### Table 2 RAM size

| Part number | RAM size                     |

|-------------|------------------------------|

| M34286G2    | 64 words X 4 bits (256 bits) |

Fig. 11 RAM map

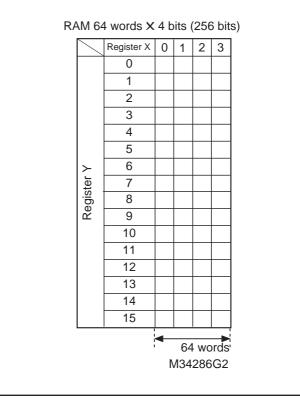

# TIMERS

The 4286 Group has the programmable timer.

• Programmable timer

The programmable timer has a reload register and enables the frequency dividing ratio to be set. It is decremented from a setting value n. When it underflows (count to n + 1), a timer 1 underflow flag is set to "1," new data is loaded from the reload register, and count continues (auto-reload function).

Fig. 12 Auto-reload function

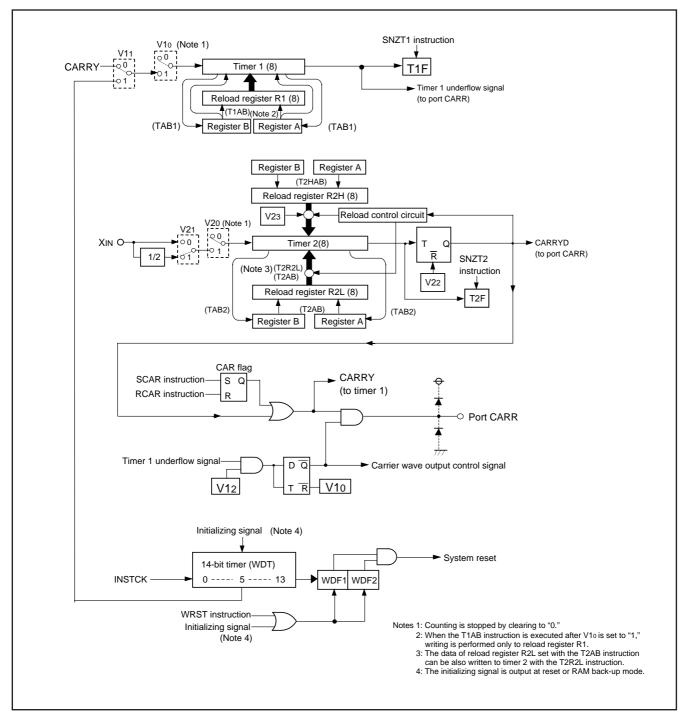

The 4286 Group timer consists of the following circuit.

- Timer 1 : 8-bit programmable timer

- Timer 2 : 8-bit programmable timer

These timers can be controlled with the timer control registers V1 and V2.

Each timer function is described below.

#### Table 3 Function related timer

| Circuit      | Structure              | Count source                                | Frequency      | Use of output signal        | Control  |

|--------------|------------------------|---------------------------------------------|----------------|-----------------------------|----------|

| Circuit      | Siluciule              | Count source                                | dividing ratio | Use of output signal        | register |

| Timer 1      | 8-bit programmable     | Carrier wave output (CARRY)                 | 1 to 256       | Carrier wave output control | V1       |

|              | binary down counter    | <ul> <li>Bit 5 of watchdog timer</li> </ul> |                |                             |          |

| Timer 2      | 8-bit programmable     | • f(XIN)                                    | 1 to 256       | Carrier wave output         | V2       |

|              | binary down counter    | • f(XIN)/2                                  |                |                             |          |

| 14-bit timer | 14-bit fixed frequency | Instruction clock                           | 16384          | Watchdog timer              |          |

|              |                        |                                             |                | Timer 1 count source        |          |

Fig. 13 Timers structure

#### Table 4 Control registers related to timer

|       | Timer control register V1                |   | t reset : 0002                            | at RAM back-up : 0002 | W |  |

|-------|------------------------------------------|---|-------------------------------------------|-----------------------|---|--|

| 1/10  | V12 Carrier wave output auto-control bit |   | Auto-control output by timer 1 is invalid |                       |   |  |

| V 12  |                                          |   | Auto-control output                       | t by timer 1 is valid |   |  |

| V/4 . | Timer 4 count course coloction hit       | 0 | Carrier wave output                       | it (CARRY)            |   |  |

| V I1  | V11 Timer 1 count source selection bit   |   | Bit 5 of watchdog ti                      | imer (WDT)            |   |  |

|       | Times descripted bit                     | 0 | Stop (Timer 1 state                       | e retained)           |   |  |

| V 10  | V10 Timer 1 control bit                  |   | Operating                                 |                       |   |  |

|      | Timer control register V2                    |   | reset : 00002                     | at RAM back-up : 00002                                | W |  |

|------|----------------------------------------------|---|-----------------------------------|-------------------------------------------------------|---|--|

| 1/20 | V23 Carrier wave "H" interval expansion bit  |   | To expand "H" interval is invalid |                                                       |   |  |

| VZ3  |                                              |   | To expand "H" inte                | To expand "H" interval is valid (when V22=1 selected) |   |  |

| 1/0- |                                              |   | Carrier wave gener                | ration function invalid                               |   |  |

| V22  | Carrier wave generation function control bit | 1 | Carrier wave gener                |                                                       |   |  |

| 1/0  |                                              | 0 | f(XIN)                            |                                                       |   |  |

| V21  | Timer 2 count source selection bit           | 1 | f(XIN)/2                          |                                                       |   |  |

| 1/0- | Time of a stall it                           | 0 | Stop (Timer 2 state               | e retained)                                           |   |  |

| V20  | Timer 2 control bit                          | 1 | Operating                         |                                                       |   |  |

Note: "W" represents write enabled.

- (1) Control registers related to timer

- Timer control register V1

Register V1 controls the timer 1 count source and autocontrol function of carrier wave output from port CARR by timer 1. Set the contents of this register through register A with the TV1A instruction.

Timer control register V2 Register V2 controls the timer 2 count source and the carrier wave generation function by timer. Set the contents of this register through register A with the TV2A instruction.

#### (2) Precautions

Note the following for the use of timers.

- Count source Stop timer 1 or timer 2 counting to change its count source.

Reading the count value

- Stop timer 1 or 2 counting and then execute the data read instruction (TAB1, TAB2) to read its data.

- Watchdog timer Be sure that the timing to execute the WRST instruction in order to operate WDT efficiently.

- Writing to reload register R1 When writing data to reload register R1 while timer 1 is operating, avoid a timing when timer 1 underflows.

Timer 1 count operation When the bit 5 of the watchdog timer (WDT) is selected as the timer 1 count source, the error of maximum  $\pm$  64  $\mu$ s (at the minimum instruction execution time : 2  $\mu$ s) is generated from timer 1 start until timer 1 underflow. When programming, be careful about this error.

- Stop of timer 2

- Avoid a timing when timer 2 underflows to stop timer 2.Writing to reload register R2H

- When writing data to reload register R2H while timer 2 is operating, avoid a timing when timer underflows.

- Timer 2 carrier wave output function When to expand "H" interval of carrier wave is valid, set "1" or more to reload register R2H.

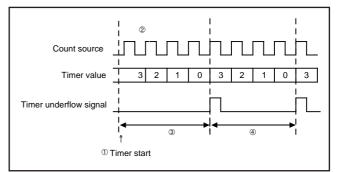

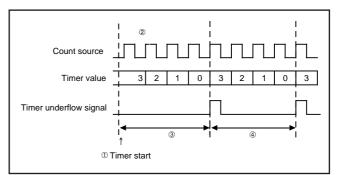

- Timer 1 and timer 2 carrier wave output function Count starts from the rising edge 2 in Fig. 14 after the first falling edge of the count source, after timer 1 and timer 2 operations start 1 in Fig. 14.

Time to first underflow ③ in Fig. 14 is different from time among next underflow ④ in Fig. 14 by the timing to start the timer and count source operations after count starts.

#### (3) Timer 1

Timer 1 is an 8-bit binary down counter with the timer 1 reload register (R1).

When timer is stopped, data can be set simultaneously in timer 1 and the reload register (R1) with the T1AB instruction.

When timer is operating, data can be set to only reload register R1 with the T1AB instruction.

When setting the next count data to reload register R1 at operating, set data before timer 1 underflows.

Timer 1 starts counting after the following process;

① set data in timer 1,

② select the count source with the bit 1 of register V1, and③ set the bit 0 of register V1 to "1."

Once count is started, when timer 1 underflows (the next count pulse is input after the contents of timer 1 becomes "0"), the timer 1 underflow flag (T1F) is set to "1," new data is loaded from reload register R1, and count continues (auto-reload function).

When a value set in reload register R1 is n, timer 1 divides the count source signal by n + 1 (n = 0 to 255).

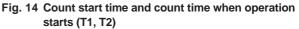

When the bit 2 of register V1 is set to "1," the carrier wave output enable/disable interval of port CARR is alternately generated each timer 1 underflows (Figure 15).

Data can be read from timer 1 to registers A and B. When reading the data, stop the counter and then execute the TAB1 instruction.

#### (4) Timer 2

Timer 2 is an 8-bit binary down counter with the timer 2 reload registers (R2H and R2L).

Data can be set simultaneously in timer 2 and the reload register (R2L) with the T2AB instruction.

The contents of reload register (R2L) set with the T2AB instruction can be set again to timer 2 with the T2R2L instruction. Data can be set to reload register (R2H) with the T2HAB instruction.

Timer 2 starts counting after the following process;

- ① set data in timer 2,

- $\ensuremath{\textcircled{}^{2}}$  select the count source with the bit 1 of register V2, and

- ③ select the valid/invalid of the carrier wave generation function by bit 2 of register V1 (when this function is valid, select the valid/invalid of the carrier wave "H" interval expansion by bit 3), and

④ set the bit 0 of register V1 to "1."

When the carrier wave generation function is invalid ( $V2_2="0"$ ), the following operation is performed;

Once count is started, when timer 2 underflows (the next count pulse is input after the contents of timer 2 becomes "0"), the timer 2 underflow flag (T2F) is set to "1," new data is loaded from reload register R2L, and count continues (auto-reload function).

When a value set in reload register R2L is n, timer 2 divides the count source signal by n + 1 (n = 0 to 255).

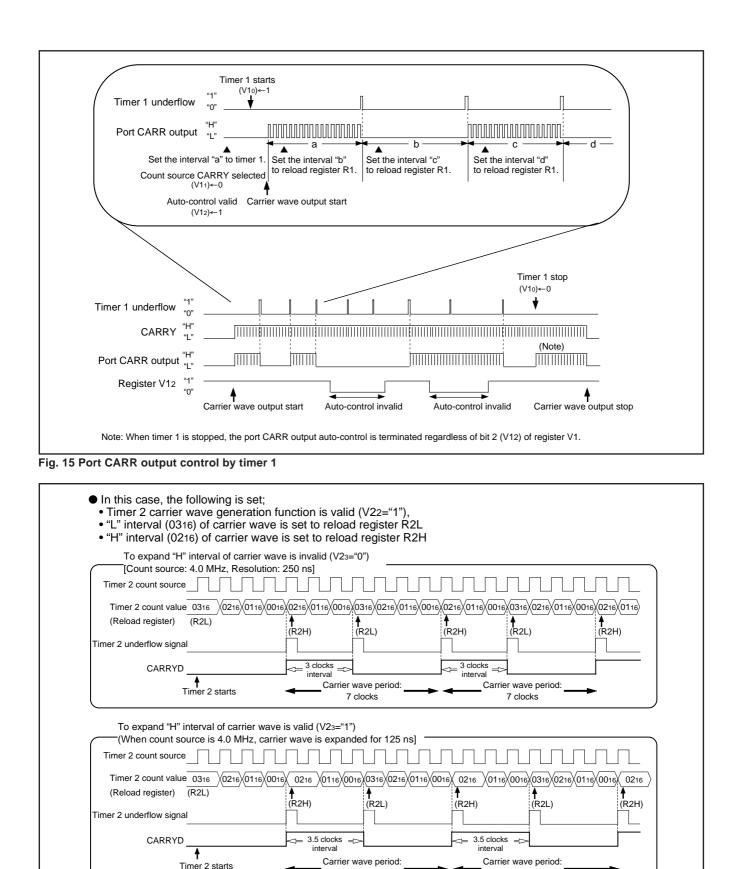

When the carrier wave generation function is valid (V22="1"), the carrier wave which has the "L" interval set to the reload register R2L and "H" interval set to the reload register R2H can be output (Figure 16).

After the count of the "L" interval of carrier wave is started, timer 2 underflows and the timer 2 underflow flag (T2F) is set

to "1". Then, the "H" interval data of carrier wave is reloaded from the reload register R2H, and count continues.

When timer underflows again after auto-reload, the T2F flag is set to "1". And then, the "L" interval data of carrier wave is reloaded from the reload register R2L, and count continues. After that, each timer underflows, data is reloaded from reload register R2H and R2L alternately.

When a value set in reload register R2H is n, "H" interval of carrier wave is as follows;

- ① When to expand "H" interval is invalid (V2<sub>3</sub> = "0"), Count source X (n+1), n = 0 to 255

- When to expand "H" interval is valid (V2<sub>3</sub> = "1"), Count source X (n+1.5), n = 1 to 255

When a value set in reload register R2L is m, "L" interval of carrier wave is as follows;

Count source X (m+1), m = 0 to 255

Data can be read from timer 2 to registers A and B. When reading the data, stop the counter and then execute the TAB2 instruction.

#### (5) Timer underflow flags (T1F, T2F)

Timer 1 underflow flag or timer 2 underflow flag is set to "1" when the timer 1 or timer 2 underflows. The state of flags T1F and T2F can be examined with the skip instruction (SNZT1, SNZT2).

Flags T1F and T2F are cleared to "0" when the next instruction is skipped with a skip instruction.

Fig. 16 Carrier wave generation example by timer 2

RENESAS

7.5 clocks

7.5 clocks

- In this case, the following is set;

- To expand "H" interval of carrier wave is invalid (V23 = "0"),

Timer 2 carrier wave generation function is valid (V22="1"),

- Count source XIN/2 selected (V21="1"),

- "L" interval (0316) of carrier wave is set to reload register R2L

"H" interval (0216) of carrier wave is set to reload register R2H

- Timer 2 count start timing Machine cycle Mi Mi + 1 Mi + 2 TV2A instruction execution cycle (V20) ←1 Instruction clock =f(XIN)/8Xin XIN/2 (Count source selected) Register V20 0316 (021ex 011ex 001ex 021ex 011ex 001ex 031ex 021e Timer 2 count value (Reload register) (R2L) **T** (R2L) (R2H) Timer 2 underflow signal CARRYD Timer 2 count start timing

| — Timer 2 count s                        | top timing                                                                                                                                                                                                                                                                                                                                                                                                                        |                           |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| (                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           |

| Machine cycle Mi                         | Mi + 1                                                                                                                                                                                                                                                                                                                                                                                                                            | Mi + 2                    |

|                                          | TV2A instruction execution cycle (V20)←0                                                                                                                                                                                                                                                                                                                                                                                          |                           |

| Instruction clock ==<br>f(XIN)/8         |                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           |

| Xin                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           |

| XIN/2<br>(Count source selected)         |                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           |

| Register V20                             |                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           |

| Timer 2 count value                      | (001a)(031a)(021a)(011a)(001a)(001a)(031a)(021a)(011a)(001a)(021a)                                                                                                                                                                                                                                                                                                                                                                |                           |

| (Reload register)                        | (R2L) (R2H) (R2L) (R2H)                                                                                                                                                                                                                                                                                                                                                                                                           |                           |

| Timer 2 underflow signal                 |                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           |

| CARRYD                                   | (Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                          |                           |

|                                          | Timer 2 count stop timing                                                                                                                                                                                                                                                                                                                                                                                                         | ]                         |

| wher<br>at the<br>wave<br>2: Whe<br>wave | In the carrier wave generation function is valid (V22="1"), avoid a time<br>timer 2 underflows to stop timer 2. When the timer 2 count stop occ<br>a same timing with the timer 2 underflows, hazard may occur in the c<br>output waveform.<br>In the timer 2 is stopped during "H" output of carrier wave while the c<br>generation function is valid, it is stopped after the "H" interval set to<br>ad register R2H is output. | curs<br>carrier<br>arrier |

Fig. 17 Timer 2 count start/stop timing

## WATCHDOG TIMER

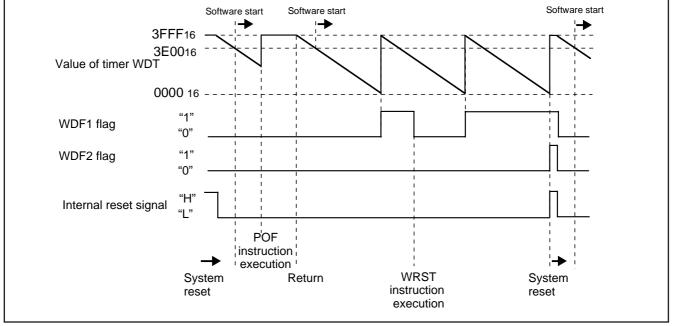

Watchdog timer provides a method to reset and restart the system when a program runs wild. Watchdog timer consists of 14-bit timer (WDT) and watchdog timer flags (WDF1, WDF2).

Watchdog timer downcounts the instruction clock (INSTCK) as the count source immediately after system is released from reset. When the timer WDT count value becomes 000016 and underflow occurs, the WDF1 flag is set to "1." Then, when the WRST instruction is not executed before the timer WDT counts 16383, WDF2 flag is set to "1" and internal reset signal is generated and system reset is performed.

Execute the WRST instruction at period of 16383 machine cycle or less to keep the microcomputer operation normal.

Timer WDT is also used for generation of oscillation stabilization time. When system is returned from reset and from RAM backup mode by key-input, software starts after the stabilization oscillation time until timer WDT downcounts to 3E0016 elapses. · Watchdog timer

Be sure that the timing to execute the WRST instruction in order to operate WDT efficiently.

### LOGIC OPERATION FUNCTION

The 4286 Group has the 4-bit logic operation function. The logic operation between the contents of register A and the low-order 4 bits of register E is performed and its result is stored in register A.

Each logic operation can be selected by setting logic operation selection register LO.

Set the contents of this register through register A with the TLOA instruction. The logic operation selected by register LO is executed with the LGOP instruction.

Table 5 shows the logic operation selection register LO.

#### Table 5 Logic operation selection register LO

| Lo  | Logic operation selection register LO |   | а               | t reset : 002                      | at RAM back-up : 002 | W |  |

|-----|---------------------------------------|---|-----------------|------------------------------------|----------------------|---|--|

|     |                                       |   | LO <sub>0</sub> | Logic operation function           |                      |   |  |

| LO1 |                                       | 0 | 0               | Exclusive logic OR operation (XOR) |                      |   |  |

|     | Logic operation selection bits        |   | 1               | OR operation (OR)                  |                      |   |  |

| LOO |                                       |   | 0               | AND operation (AND)                |                      |   |  |

|     |                                       |   | 1               | Not available                      |                      |   |  |

Note: "W" represents write enabled.

# **RESET FUNCTION**

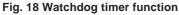

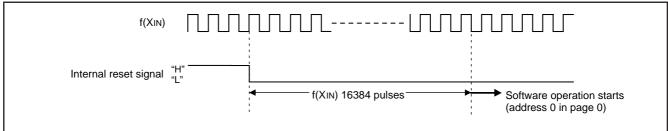

The 4286 Group has the power-on reset circuit, though it does not have RESET pin. System reset is performed automatically at power-on, and software starts program from address 0 in page 0.

In order to make the built-in power-on reset circuit operate efficiently, set the voltage rising time until V<sub>DD</sub>= 0 to 2.2 V is obtained at power-on 1ms or less (Ta = -20 °C to 85 °C).

#### Note on Power-on reset

Under the following condition, the system reset occurs by the built-in the power-on reset circuit of this product;

- when the supply voltage (VDD) rises from 0 V to 2.2 V, within 1 ms (Ta = -20 °C to 85 °C).

- Also, note that system reset does not occur under the following conditions;

- when the supply voltage (VDD) rises from the voltage higher than 0V, or

- when it takes more than 1 ms for the supply voltage (VDD) to rise from 0 V to 2.2 V (Ta = -20 °C to 85 °C).

Fig. 19 Reset release timing

Fig. 20 Power-on reset operation

#### (1) Internal state at reset

Table 6 shows port state at reset, and Figure 21 shows internal state at reset (they are retained after system is released from reset).

The contents of timers, registers, flags and RAM except shown in Figure 21 are undefined, so set the initial value to them.

#### Table 6 Port state at reset

| Name   | State at reset                                  |  |  |  |  |  |

|--------|-------------------------------------------------|--|--|--|--|--|

| D0-D7  | High impedance state (Pull-down transistor OFF) |  |  |  |  |  |

| G0–G3  | High impedance state (Pull-down transistor OFF) |  |  |  |  |  |

| E0, E1 | High impedance state (Pull-down transistor OFF) |  |  |  |  |  |

| CARR   | "L" output                                      |  |  |  |  |  |

Note: The contents of all output latch is initialized to "0."

| • Program counter (PC)                                   |

|----------------------------------------------------------|

| Address 0 in page 0 is set to program counter.           |

| • Power down flag (P)0                                   |

| • Timer 1 underflow flag (T1F)0                          |

| Timer 2 underflow flag (T2F)                             |

| Timer control register V1                                |

| Timer control register V2                                |

| Port CARR output flag (CAR)                              |

| Pull-down control register PU0                           |

| Pull-down control register PU1                           |

| Pull-down control register PU2                           |

| Logic operation selection register LO                    |

| Most significant ROM code reference enable flag (URS)    |

| • Carry flag (CY)                                        |

| • Register A                                             |

| • Register B                                             |

| • Register X X X                                         |

| • Register Y                                             |

| Stack pointer (SP)     1 1     "X" represents undefined. |

Fig. 21 Internal state at reset

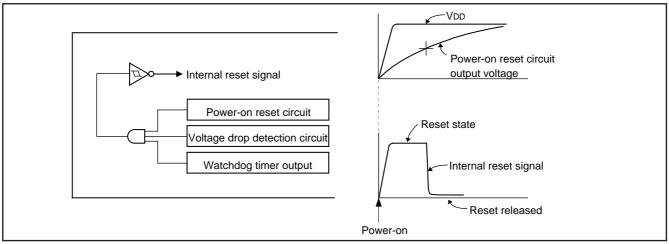

# **VOLTAGE DROP DETECTION CIRCUIT**

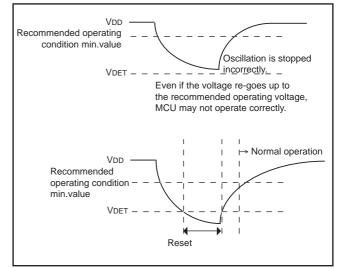

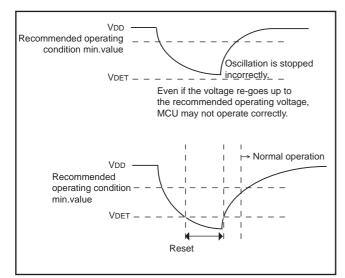

System reset is performed when the supply voltage goes the reset occurrence voltage or less.

When the supply voltage goes reset release voltage or more, the oscillation circuit goes to be in the operating enabled state and system reset is released.

The reset occurrence voltage value is selectable by the CLVD instruction execution.

Refer to the electrical characteristics for reset occurrence value and reset release voltage value.

The voltage drop detection circuit is stopped and power dissipation is reduced in the RAM back-up mode with the initialized CPU stopped.

#### Note on voltage drop detection circuit

The voltage drop detection circuit detection voltage of this product is set up lower than the minimum value of the supply voltage of the recommended operating conditions.

As the actual operating minimum voltage is lower than the reset generation voltage, the MCU will operate correctly unless oscillation stops before the supply voltage reaches the reset generation voltage during CPU operation.

When designing a system, test the operation thoroughly by confirming the oscillation stop voltage and frequency of the oscillator.

Fig. 22 Voltage drop detection circuit operation waveform

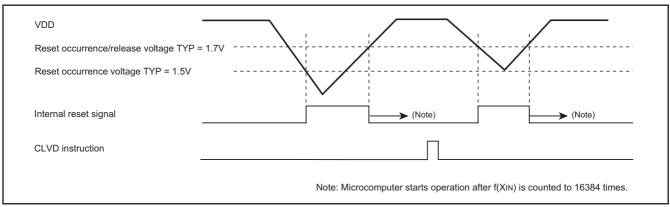

# **RAM BACK-UP MODE**

The 4286 Group has the RAM back-up mode.

When the POF instruction is executed, system enters the RAM back-up state.

As oscillation stops retaining RAM, the functions and states of reset circuit at RAM back-up mode, power dissipation can be reduced without losing the contents of RAM. Table 7 shows the function and states retained at RAM back-up. Figure 24 shows the state transition.

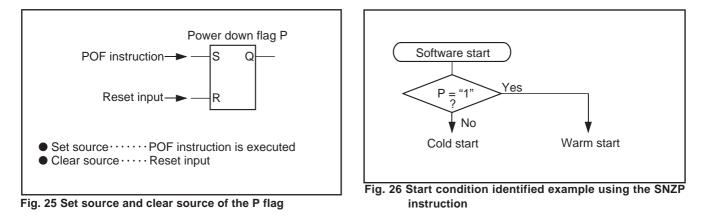

#### (1) Warm start condition

When the external wakeup signal is input after the system enters the RAM back-up state by executing the POF instruction, the CPU starts executing the software from address 0 in page 0. In this case, the P flag is "1."

#### (2) Cold start condition

The CPU starts executing the software from address 0 in page

- 0 when any of the following conditions is satisfied . • reset by power-on reset circuit is performed

- reset by power-on reset circuit is period

reset by watchdog timer is performed

- reset by watchdog time is performed

reset by voltage drop detection circuit is performed

- In this case, the P flag is "0."

#### (3) Identification of the start condition

Warm start (return from the RAM back-up state) or cold start (return from the normal reset state) can be identified by examining the state of the power down flag (P) with the SNZP instruction.

#### Table 7 Functions and states retained at RAM back-up

| Function                                              | RAM back-up |

|-------------------------------------------------------|-------------|

| Program counter (PC), registers A, B,                 | x           |

| carry flag (CY), stack pointer (SP) (Note 2)          | ~           |

| Contents of RAM                                       | 0           |

| Port CARR                                             | ×           |

| Ports D0-D7                                           | 0           |

| Ports E0, E1                                          | 0           |

| Port G                                                | 0           |

| Timer control registers V1, V2                        | ×           |

| Pull-down control registers PU0, PU1, PU2             | 0           |

| Logic operation selection register LO                 | ×           |

| Timer 1 function, Timer 2 function                    | X           |

| Timer underflow flags (T1F, T2F)                      | ×           |

| Watchdog timer (WDT)                                  | ×           |

| Watchdog timer flags (WDF1, WDF2)                     | ×           |

| Most significant ROM code reference enable flag (URS) | ×           |

Notes 1: "O" represents that the function can be retained, and "X" represents that the function is initialized. Registers and flags other than the above are undefined at RAM back-up, and set an initial value after returning.

2:The stack pointer (SP) points the level of the stack register and is initialized to "112" at RAM back-up.

#### Fig. 24 State transition

REJ03B0251-0100

#### (4) Return signal

An external wakeup signal is used to return from the RAM back-up mode. Table 8 shows the return condition for each return source.

#### Table 8 Return source and return condition

| Return source   | Return condition                | Remarks                                                               |  |  |

|-----------------|---------------------------------|-----------------------------------------------------------------------|--|--|

| Ports Do-D7     | Return by an external "H" level | Only key-on wakeup function of the port whose pull-down transistor is |  |  |

|                 | input.                          | turned ON by register PU1 and PU2 are valid.                          |  |  |

| Ports E0, E1, G | Return by an external "H" level | Only key-on wakeup function of the port whose pull-down transistor    |  |  |

|                 | input.                          | turned ON by register PU0 is valid.                                   |  |  |

| Port E2         | Return by an external "H" level | Key-on wakeup function is always valid.                               |  |  |

|                 | input.                          |                                                                       |  |  |

#### (5) Pull-down control register

Registers PU0, PU1, and PU2 are 4-bit registers and control the ON/OFF of pull-down transistor and key-on wakeup function for ports  $E_0$ ,  $E_1$ , G and ports  $D_0$ – $D_7$ .

Set the contents of register PU0, PU1, or PU2 through register A with the TPU0A, TPU1A, or TPU2A instruction, respectively.

#### Table 9 Pull-down control registers

|       | Pull-down control register PU0                                     |   | reset : 00002                                   | at RAM back-up : state retained                | W |  |  |  |

|-------|--------------------------------------------------------------------|---|-------------------------------------------------|------------------------------------------------|---|--|--|--|

| PU03  | Ports G <sub>2</sub> , G <sub>3</sub> pull-down transistor control | 0 | Pull-down transisto                             | ull-down transistor OFF, key-on wakeup invalid |   |  |  |  |

| P003  | bit                                                                | 1 | Pull-down transisto                             | Pull-down transistor ON, key-on wakeup valid   |   |  |  |  |

| DUIOs | Ports G <sub>0</sub> , G <sub>1</sub> pull-down transistor control | 0 | Pull-down transistor OFF, key-on wakeup invalid |                                                |   |  |  |  |

| P002  | PU02 bit                                                           |   | Pull-down transistor ON, key-on wakeup valid    |                                                |   |  |  |  |

|       | PU01 Port E1 pull-down transistor control bit                      |   | Pull-down transistor OFF, key-on wakeup invalid |                                                |   |  |  |  |

| P001  |                                                                    |   | Pull-down transistor ON, key-on wakeup valid    |                                                |   |  |  |  |

| DUIOs | Port Es pull down transistor control hit                           | 0 | Pull-down transisto                             | r OFF, key-on wakeup invalid                   |   |  |  |  |

| PU00  | Port E <sub>0</sub> pull-down transistor control bit               | 1 | Pull-down transistor ON, key-on wakeup valid    |                                                |   |  |  |  |

| Pull-down control register PU1 |                                                      | at reset : 00002 |                                                   | at RAM back-up : state retained W |  |

|--------------------------------|------------------------------------------------------|------------------|---------------------------------------------------|-----------------------------------|--|

| DUI                            |                                                      |                  | Pull-down transisto                               | r OFF, key-on wakeup invalid      |  |

| PU13                           | Port D7 pull-down transistor control bit             | 1                | Pull-down transistor ON, key-on wakeup valid      |                                   |  |

| PU12                           | Part Danull down transistor control bit              | 0                | Pull-down transistor OFF, key-on wakeup invalid   |                                   |  |

| PUI2                           | Port D <sub>6</sub> pull-down transistor control bit | 1                | Pull-down transisto                               | r ON, key-on wakeup valid         |  |

| PU11                           | Port Dr. null down transistor control bit            | 0                | ) Pull-down transistor OFF, key-on wakeup invalid |                                   |  |

| FUN                            | Port D <sub>5</sub> pull-down transistor control bit | 1                | Pull-down transistor ON, key-on wakeup valid      |                                   |  |

| PU10                           | Port Dr null down transistor control bit             | 0                | Pull-down transistor OFF, key-on wakeup invalid   |                                   |  |

| PUI0                           | Port D4 pull-down transistor control bit             | 1                | Pull-down transistor ON, key-on wakeup valid      |                                   |  |

| Pull-down control register PU2 |                                                      | at reset : 00002 |                                                 | at RAM back-up : state retained | W |  |

|--------------------------------|------------------------------------------------------|------------------|-------------------------------------------------|---------------------------------|---|--|

| PU23                           |                                                      |                  | Pull-down transisto                             | r OFF, key-on wakeup invalid    |   |  |

| P023                           | Port D <sub>3</sub> pull-down transistor control bit | 1                | Pull-down transisto                             | r ON, key-on wakeup valid       |   |  |

|                                |                                                      | 0                | Pull-down transistor OFF, key-on wakeup invalid |                                 |   |  |

| PU22                           | Port D <sub>2</sub> pull-down transistor control bit | 1                | Pull-down transistor ON, key-on wakeup valid    |                                 |   |  |

| PU21                           | Port Dr. pull down transistor control bit            | 0                | Pull-down transistor OFF, key-on wakeup invalid |                                 |   |  |

| P021                           | Port D1 pull-down transistor control bit             | 1                | Pull-down transistor ON, key-on wakeup valid    |                                 |   |  |

| PU20                           | Port Da null down transistor control hit             | 0                | Pull-down transistor OFF, key-on wakeup invalid |                                 |   |  |

| FU20                           | Port D <sub>0</sub> pull-down transistor control bit | 1                | Pull-down transisto                             | r ON, key-on wakeup valid       |   |  |

Note: "W" represents write enabled.

# **CLOCK CONTROL**

The clock control circuit consists of the following circuits.

- System clock generating circuit

- · Control circuit to stop the clock oscillation

- · Control circuit to return from the RAM back-up state

Fig. 27 Clock control circuit structure

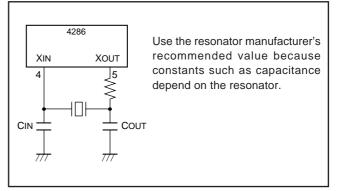

System clock signal  $f(X_{IN})$  is obtained by externally connecting a ceramic resonator. Connect this external circuit to pins  $X_{IN}$  and  $X_{OUT}$  at the shortest distance as shown Figure 28.

A feedback resistor is built-in between XıN pin and XouT pin.

Fig. 28 Ceramic resonator external circuit

# LIST OF PRECAUTIONS

#### ① Noise and latch-up prevention

Connect a capacitor on the following condition to prevent noise and latch-up;

- connect a bypass capacitor (approx. 0.01  $\mu\text{F})$  between pins VDD and Vss at the shortest distance,

- · equalize its wiring in width and length, and

- use the thickest wire.

- Port E2 is also used as VPP pin. Connect this pin to Vss through the resistor about 5kΩ which is assigned to E2/VPP pin as close as possible at the shortest distance.

#### ② Register initial values 1

The initial value of the following registers are undefined after system is released from reset. After system is released from reset, set initial values.

- Register D (3 bits)

- Register E (8 bits)

#### ③ Register initial values 2

The initial value of the following registers are undefined at RAM backup. After system is returned from RAM back-up, set initial values.

- Register X (4 bits)

- Register Y (4 bits)

- Register D (3 bits)

- Register E (8 bits)

#### ④ Stack registers (SKs)

Stack registers (SK<sub>s</sub>) are four identical registers, so that subroutines can be nested up to 4 levels. However, one of stack registers is used when executing a table reference instruction. Accordingly, be careful not to over the stack. The contnts of registers SK<sub>s</sub> are destroyed when 4 levels are exceeded.

#### S Notes on unused pins

| Pin    | Connection                          | Usage condition           |

|--------|-------------------------------------|---------------------------|

| D0-D7  | Open (Set the output latch to "1"). | Pull-down transistor OFF. |

|        | Open (Set the output latch to "0"). |                           |

|        | Connect to VDD.                     | Pull-down transistor OFF. |

| E0, E1 | Open (Set the output latch to "1"). | Pull-down transistor OFF. |

|        | Open (Set the output latch to "0"). |                           |

|        | Connect to VDD.                     | Pull-down transistor OFF. |

| E2     | Open.                               |                           |

|        | Connect to Vss.                     |                           |

| G0-G3  | Open (Set the output latch to "1"). | Pull-down transistor OFF. |

|        | Open (Set the output latch to "0"). |                           |

|        | Connect to VDD.                     | Pull-down transistor OFF. |

| CARR   | Open.                               |                           |

(Note when connecting to Vss and VDD)

Connect the unused pins to Vss and Vbb at the shortest distance and use the thick wire against noise.

#### 6 Timer

Count source Stop timer 1 or timer 2 counting to change its count source.

- Reading the count value

Stop timer 1 or 2 counting and then execute the data read instruction (TAB1, TAB2) to read its data.

- Watchdog timer

Be sure that the timing to execute the WRST instruction in order to operate WDT efficiently.

- Writing to reload register R1 When writing data to reload register R1 while timer 1 is operating, avoid a timing when timer 1 underflows.

- Timer 1 count operation When the bit 5 of the watchdog timer (WDT) is selected as the timer 1 count source, the error of maximum  $\pm 64 \,\mu s$  (at the minimum instruction execution time :  $2 \,\mu s$ ) is generated from timer 1 start until timer 1 underflow. When programming, be careful about this error.

- Stop of timer 2

- Avoid a timing when timer 2 underflows to stop timer 2.

- Writing to reload register R2H

When writing data to reload register R2H while timer 2 is operating, avoid a timing when timer underflows.

- Timer 2 carrier wave output function When to expand "H" interval of carrier wave is valid, set "1" or more to reload register R2H.

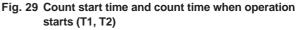

- Timer 1 and timer 2 carrier wave output function Count starts from the rising edge 2 in Fig. 29 after the first falling edge of the count source, after timer 1 and timer 2 operations start 1 in Fig. 29.

Time to first underflow ③ in Fig. 29 is different from time among next underflow ④ in Fig. 29 by the timing to start the timer and count source operations after count starts.

⑦ Program counter

Make sure that the program counter does not specify after the last page of the built-in ROM.

#### 8 Power-on reset

Under the following condition, the system reset occurs by the built-in the power-on reset circuit of this product;

- when the supply voltage (VDD) rises from 0 V to 2.2 V, within 1 ms (Ta = -20 °C to 85 °C).

- Also, note that system reset does not occur under the following conditions;

- when the supply voltage (VDD) rises from the voltage higher than 0V, or

- when it takes more than 1 ms for the supply voltage (VDD) to rise from 0 V to 2.2 V (Ta = -20 °C to 85 °C).

#### Voltage drop detection circuit

The voltage drop detection circuit detection voltage of this product is set up lower than the minimum value of the supply voltage of the recommended operating conditions.

As the actual operating minimum voltage is lower than the reset generation voltage, the MCU will operate correctly unless oscillation stops before the supply voltage reaches the reset generation voltage during CPU operation.

When designing a system, test the operation thoroughly by confirming the oscillation stop voltage and frequency of the oscillator.

#### Fig. 30 VDD and VDET

#### Note on Power Source Voltage

When the power source voltage value of a microcomputer is less than the value which is indicated as the recommended operating conditions, the microcomputer does not operate normally and may perform unstable operation.

In a system where the power source voltage drops slowly when the power source voltage drops or the power supply is turned off, reset a microcomputer when the supply voltage is less than the recommended operating conditions and design a system not to cause errors to the system by this unstable operation.

#### 11 QzROM

- Be careful not to apply overvoltage to MCU. The contents of QzROM may be overwritten because of overvoltage. Take care especially at turning on the power.

- (2) As for the product shipped in blank, Renesas does not perform the writing test to user ROM area after the assembly process though the QzROM writing test is performed enough before the assembly process. Therefore, a writing error of approx.0.1 % may occur. Moreover, please note the contact of cables and foreign bodies on a socket, etc. because a writing environment may cause some writing errors.

#### 12 Notes On ROM Code Protect

(QzROM product shipped after writing)

As for the QzROM product shipped after writing, the ROM code protect is specified according to the ROM option setup data in the mask file which is submitted at ordering.

The ROM option setup data in the mask file is "0016" for protect enabled or "FF16" for protect disabled.

Note that the mask file which has nothing at the ROM option data or has the data other than "0016" and "FF16" can not be accepted.

## INSTRUCTIONS

The 4286 Group has the 72 instructions. Each instruction is described as follows;

(1) List of instruction function

- (2) Machine instructions (index by alphabet)

- (3) Machine instructions (index by function)

- (4) Instruction code table

### SYMBOL

The symbols shown below are used in the following list of instruction function and the machine instructions.

| Symbol | Contents                                        | Symbol            | Contents                                      |

|--------|-------------------------------------------------|-------------------|-----------------------------------------------|

| A      | Register A (4 bits)                             | D                 | Port D (8 bits)                               |

| В      | Register B (4 bits)                             | E                 | Port E (3 bits)                               |

| DR     | Register D (3 bits)                             | G                 | Port G (4 bits)                               |

| ER     | Register E (8 bits)                             | CARR              | Port CARR (1 bit)                             |

| V1     | Timer control register V1 (3 bits)              | CAR               | CAR flag (1 bit)                              |

| V2     | Timer control register V2 (4 bits)              |                   |                                               |

| PU0    | Pull-down control register PU0 (4 bits)         | х                 | Hexadecimal variable                          |

| PU1    | Pull-down control register PU1 (4 bits)         | у                 | Hexadecimal variable                          |

| PU2    | Pull-down control register PU2 (4 bits)         |                   |                                               |

| LO     | Logic operation selection register LO (2 bits)  | р                 | Hexadecimal variable                          |

|        |                                                 | n                 | Hexadecimal constant which represents the     |

| х      | Register X (2 bits)                             |                   | immediate value                               |

| Y      | Register Y (4 bits)                             | j                 | Hexadecimal constant which represents the     |

| DP     | Data pointer (6 bits)                           |                   | immediate value                               |

|        | (It consists of registers X and Y)              | A3A2A1A0          | Binary notation of hexadecimal variable A     |

| PC     | Program counter (11 bits)                       |                   | (same for others)                             |

| РСн    | High-order 4 bits of program counter            |                   |                                               |

| PC∟    | Low-order 7 bits of program counter             | ←                 | Direction of data movement                    |

| SK     | Stack register (11 bits X 4)                    | $\Leftrightarrow$ | Data exchange between a register and memory   |

| SP     | Stack pointer (2 bits)                          | ?                 | Decision of state shown before "?"            |

| CY     | Carry flag                                      | ()                | Contents of registers and memories            |

| R1     | Timer 1 reload register                         | —                 | Negate, Flag unchanged after executing        |

| T1     | Timer 1                                         |                   | instruction                                   |

| T1F    | Timer 1 underflow flag                          | M(DP)             | RAM address pointed by the data pointer       |

| R2H    | Timer 2 reload register                         | а                 | Label indicating address a6 a5 a4 a3 a2 a1 a0 |

| R2L    | Timer 2 reload register                         | р, а              | Label indicating address a6 a5 a4 a3 a2 a1 a0 |

| T2     | Timer 2                                         |                   | in page p3 p2 p1 p0                           |

| T2F    | Timer 2 underflow flag                          | С                 | Hex. number C + Hex. number x (also same for  |

| WDT    | Watchdog timer                                  | +                 | others)                                       |

| WDF1   | Watchdog timer flag 1                           | х                 |                                               |

| WDF2   | Watchdog timer flag 2                           |                   |                                               |

| URS    | Most significant ROM code reference enable flag |                   |                                               |

| Р      | Power down flag                                 |                   |                                               |

| STCK   | System clock                                    |                   |                                               |

| INSTCK | Instruction clock                               |                   |                                               |

Note : The 4286 Group just invalidates the next instruction when a skip is performed. The contents of program counter is not increased by 2. Accordingly, the number of cycles does not change even if skip is not performed. However, the cycle count becomes "1" if the TABP p, RT, or RTS instruction is skipped.

# LIST OF INSTRUCTION FUNCTION

| Grouping                      | Mnemonic | Function                                                       | Page | Grouping             | Mnemonic | Function                                                                            | Page |

|-------------------------------|----------|----------------------------------------------------------------|------|----------------------|----------|-------------------------------------------------------------------------------------|------|

|                               | ТАВ      | (A) ← (B)                                                      | 41   |                      | LA n     | (A) ← n                                                                             | 34   |

|                               |          |                                                                |      |                      |          | n = 0 to 15                                                                         |      |

|                               | ТВА      | (B) ← (A)                                                      | 43   |                      | TABP p   | (SP) ← (SP) + 1                                                                     | 42   |

| fer                           | TAY      | (A) ← (Y)                                                      | 43   |                      | таве р   | (SF) ← (SF) + 1<br>(SK(SP)) ← (PC)                                                  | 42   |

| ans                           |          |                                                                |      |                      |          | (РСн) ← p p=0 to 15                                                                 |      |

| Register to register transfer | TYA      | (Y) ← (A)                                                      | 45   |                      |          | (PCL) ← (DR2–DR0, A3–A0)                                                            |      |

| egist                         |          |                                                                |      |                      |          | When URS=0                                                                          |      |

| to te                         | TEAB     | $(ER_7 - ER_4) \leftarrow (B)$                                 | 43   |                      |          | $(B) \leftarrow (ROM(PC))7 \text{ to } 4$ $(A) \leftarrow (ROM(PC))3 \text{ to } 0$ |      |

| ster                          |          | (ER3–ER0) ← (A)                                                |      |                      |          | $(A) \leftarrow (ROM(PC))_{3 to 0}$<br>When URS=1                                   |      |

| Regi                          | TABE     | (B) ← (ER7–ER4)                                                | 42   |                      |          | (CY) ← (ROM(PC)) <sub>8</sub>                                                       |      |

|                               |          | (A) ← (ER3–ER0)                                                |      |                      |          | (B) ← (ROM(PC))7 to 4                                                               |      |

|                               |          |                                                                |      |                      |          | $(A) \leftarrow (ROM(PC)) \text{3 to 0}$                                            |      |

|                               | TDA      | $(DR_2-DR_0) \leftarrow (A_2-A_0)$                             | 43   |                      |          | $(PC) \leftarrow (SK(SP))$                                                          |      |

|                               | LXY x, y | (X) ← x, x = 0 to 3                                            | 34   |                      |          | (SP) ← (SP) – 1                                                                     |      |

| es                            |          | $(Y) \leftarrow y, y = 0 \text{ to } 15$                       |      | ç                    | AM       | (A) ← (A) + (M(DP))                                                                 | 29   |

| RAM addresses                 |          |                                                                |      | Arithmetic operation |          |                                                                                     |      |

| addı                          | INY      | (Y) ← (Y) + 1                                                  | 33   | ledo                 | AMC      | $(A) \leftarrow (A) + (M(DP)) + (CY)$                                               | 29   |

| AM                            | DEV      |                                                                | 22   | etic                 |          | (CY) ← Carry                                                                        |      |

|                               | DEY      | (Y) ← (Y) − 1                                                  | 33   | thm                  | An       | (A) ← (A) + n                                                                       | 29   |

|                               | TAM j    | (A) ← (M(DP))                                                  | 42   | Ari                  |          | n = 0 to 15                                                                         | 25   |

|                               |          | $(X) \leftarrow (X) EXOR(j)$                                   |      |                      |          |                                                                                     |      |

|                               |          | j = 0 to 3                                                     |      |                      | SC       | (CY) ← 1                                                                            | 37   |

|                               | VANA:    |                                                                | 40   |                      | DO       |                                                                                     | 20   |

|                               | XAM j    | $(A) \longleftrightarrow (M(DP))$ $(X) \leftarrow (X) EXOR(j)$ | 46   |                      | RC       | (CY) ← 0                                                                            | 36   |

|                               |          | j = 0  to  3                                                   |      |                      | szc      | (CY) = 0 ?                                                                          | 40   |

|                               |          |                                                                |      |                      |          |                                                                                     |      |

|                               | XAMD j   | $(A) \longleftrightarrow (M(DP))$                              | 46   |                      | CMA      | $(A) \leftarrow (\overline{A})$                                                     | 32   |

| sfer                          |          | $(X) \leftarrow (X) EXOR(j)$                                   |      |                      |          |                                                                                     | 25   |

| rans                          |          | j = 0 to 3<br>(Y) $\leftarrow$ (Y) - 1                         |      |                      | RAR      | $\rightarrow$ CY $\rightarrow$ A3A2A1A0                                             | 35   |

| RAM to register transfer      |          |                                                                |      |                      | LGOP     | Logic operation                                                                     | 34   |

| egis                          | XAMI j   | $(A) \longleftrightarrow (M(DP))$                              | 46   |                      |          | instruction                                                                         |      |

| to l                          |          | $(X) \leftarrow (X) EXOR(j)$                                   |      |                      |          | XOR, OR, AND                                                                        |      |

| SAM                           |          | j = 0  to  3                                                   |      |                      | 00.      |                                                                                     | 07   |