# **STE1000P**

## SINGLE PORT GIGABIT ETHERNET TRANSCEIVER

### PRODUCT PREVIEW

#### 1 GENERAL DESCRIPTION

The STE1000P designed by STMicroelectronics, is a high performance, ultra low power, single port transceiver that performs all the physical layer interface functions for Gigabit Ethernet over 100-meter CAT 5 cabling. It also provides 100BASE-TX and 10BASE-T Ethernet capabilities, which enables a smooth migration from current 10/100 networks to 1000Mbps-based networks.

#### 2 MAIN FEATURES

- Fully standards compliant: IEEE 802.3, IEEE 802.3u, IEEE 802.3z and IEEE 802.3ab

- Six different operating modes

- 1000BASE-T Full Duplex and 1000BASE-T Half Duplex

- 100BASE-TX Full Duplex and 100BASE-TX Half Duplex

- 10BASE-T Full Duplex and 10BASE-T Half Duplex

- BER of better than or equal to 10<sup>-10</sup> in 1000BASE-T mode, 10<sup>-8</sup> in 100BASE-TX mode.

- Configurable MAC interface: MII, GMII or TBI

- Automatic configure operating mode and MAC interface

- Hardware configuration for default operation

- Automatic detection and correction of pair swaps (Auto-MDIX), pair skew and pair polarity

- Management interface

- Management interrupt

- Baseline wander compensation

- On-chip transmit wave-shaping

- On-chip hybrid circuit

- 10KB jumbo frames

- Internal, external and remote loop back

- LED indication: link mode, status, speed, activity, and collision

- Power down mode

Package Options: PQFP128

Ordering Part Number: STE1000P

JTAG (IEEE 1149.1) interface

#### 2.1 OPERATING CONDITIONS

Supply voltage: 1.8V for core, 3.3V for I/O

Temperature range: 0-85° C

Power consumption: 600mW (typical)

#### 3 TYPICAL APPLICATIONS

- Ethernet Switches

- Hubs/Repeaters

- Up-link Interfaces

- Network Interface Cards (NICs)

- LAN on Mother board (LOM)

#### 4 FUNCTIONAL DESCRIPTION

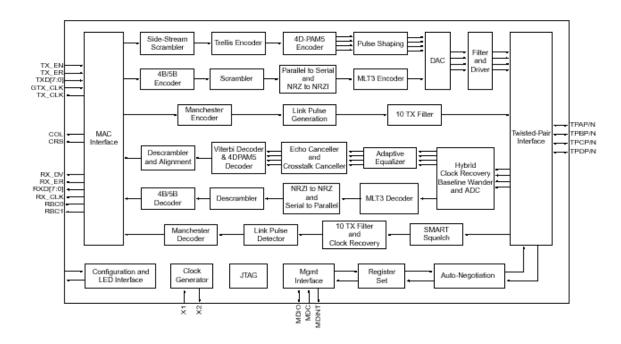

The STE1000P chip consists of 8 functional blocks:

- Auto-Negotiation block, which is responsible for advertising the chip's capabilities and establishing the link.

- Management Register block, which contains all the configuration registers

- Management Data Interface

- Physical Coding Sublayer block, which contains the 1000/100/10 Base T sub-blocks

- Mac Interface.

- DPMA: Digital Physical Media Attachment, which consists of 1000/100/10 Base T subblocks:

- Clock Distribution and Reset circuitry.

- LED: Light Emitting Diodes circuitry.

May 2002 1/2

Figure 1: STE1000P Block Diagram

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics 2002 STMicroelectronics - All Rights Reserved

#### STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.

http://www.st.com