# Brushless DC (BLDC) Single-Chip Motor Drive IC

The ECN30102 is a fully integrated, single-chip BLDC motor driver that facilitates a rapid design process and low part count solution. The chip integrates BLDC Logic with a 3-Phase Inverter containing six (6) 250V rated IGBTs and a Charge Pump TOP Arm bias. To reduce motor current losses, a BLDC motor can now be driven directly from rectified 110VAC (up to 185VDC) power lines, or from any DC power bus down to 20VDC. On-Chip Brushless (electronic) commutation logic is fully integrated with analog OSC/PWM functions that permit an analog (VSP) voltage to control motor speed.

## Description

- Integrated, Single-Chip Direct BLDC Motor Driver IC

- Integrated 3-Phase BLDC motors operating from a 185VDC (down to 20VDC) voltage bus

- Integrated Charge Pump Creates constant TOP Arm bias independent of motor speed

- Integrated 3-Phase Brushless (Electronic) commutation via external Hall ICs

- Integrated 3-Phase 6-IGBT Motor Bridge with on-chip free-wheeling diodes

- Pinout and Board Layout are compatible with the existing Hitachi ECN3018

- Breakdown, Max rated 250VDC/1.2A

- Latch-Up free monolithic IC built with a high voltage Dielectric Isolation (DI) process

- Available in 3 package types with built-in heat sink (Tab)

### **Functions and Features**

- Simple Variable Speed Control via a single (VSP) analog input

- PWM Speed Control without requiring a MicroController

- PWM duty cycle generator provides a 0% to 100% speed control range

- Tachometer Generates a (RPM/60)x(P/2)x3 Hertz speed signal (FG)

- BOTTOM Arms switch at up to 20kHz via an on-chip OSC/PWM

- On-Chip 7.5VDC regulator (CB) with a guaranteed Min load (25mA)

- Over-Current protection is set by an external Sense Resistor (RS)

- Under-Voltage protection for TOP and BOTTOM IGBT Arms

- Low Stand-By power

- An all output IGBT Shut-OFF function

HITACHI

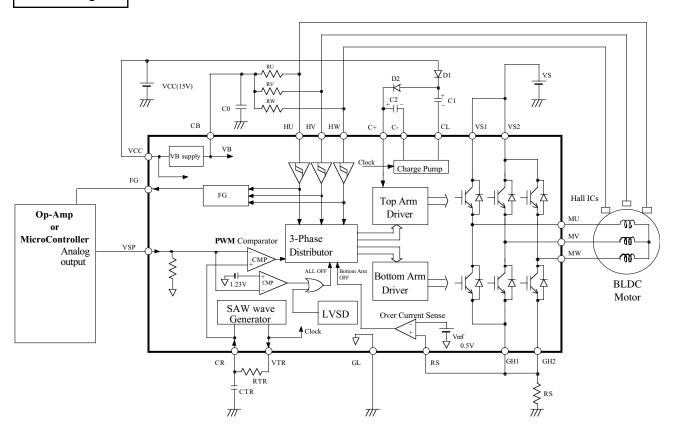

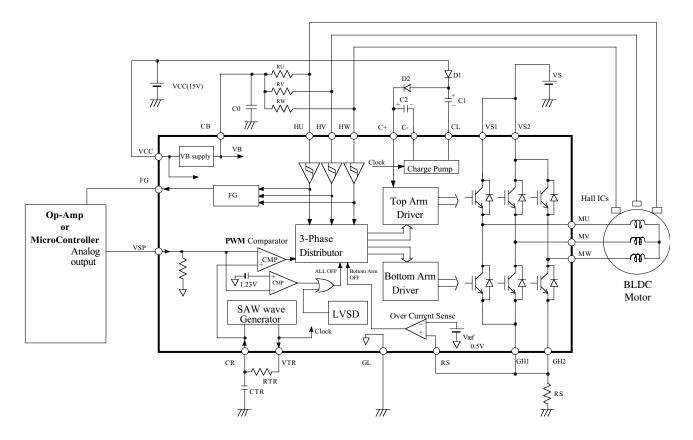

**Block Diagram**

Figure 1 Block Diagram

NOTE: A Speed Reverse Function for Single Chip BLDC Motor Drive ICs (such as this ECN30102) is discussed in Motor Control Tech Tips, Volume 1, Issue 9 (Oct '02). "Implementing Single Chip Safe Direction Reversal and TACH Pulse" (see our web pages).

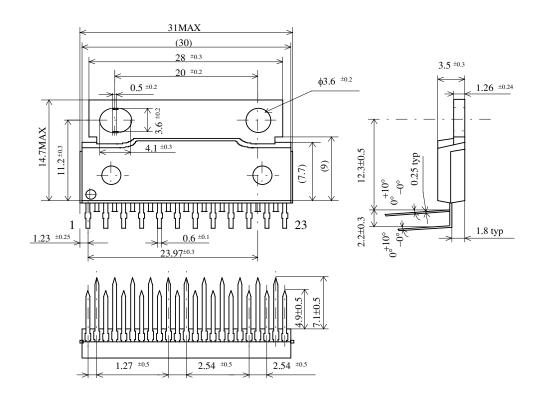

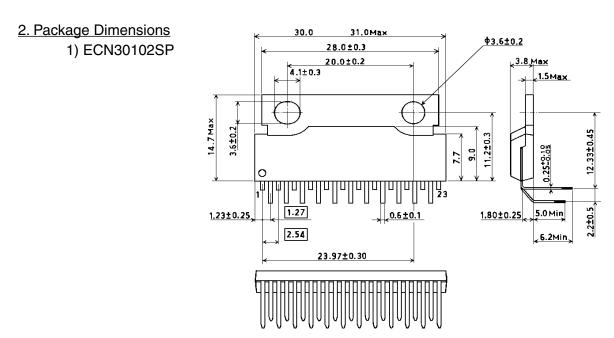

Part Names and Packaging

ECN30102SP (Package Type:SP-23TA)

ECN30102SPV (Package Type:SP-23TB)

ECN30102SPR (Package Type:SP-23TR)

### 1. Maximum Allowable Ratings

|     |                       |       |        |            |                |      | Ta = 25 °C |  |  |

|-----|-----------------------|-------|--------|------------|----------------|------|------------|--|--|

| NO. | Items                 |       | Symbol | Terminals  | Ratings        | Unit | Condition  |  |  |

| 1   | Output Device         |       | VSM    | VS1, VS2   | 250            | V    |            |  |  |

|     | Breakdown Volt        | age   |        | MU, MV, MW |                |      |            |  |  |

| 2   | Analog Supply voltage |       | VCC    | VCC        | 18             | V    |            |  |  |

| 3   | Input voltage         |       | VIN    | VSP, RS    | -0.5 to VB+0.5 | V    |            |  |  |

|     |                       |       |        | HU, HV, HW |                |      |            |  |  |

| 4   | Output current        | Pulse | IP     | MU, MV, MW | 1.2            | А    | Note 1     |  |  |

| 5   |                       | DC    | IDC    |            | 0.7            |      |            |  |  |

| 6   | VB supply current     |       | IBMAX  | СВ         | 50             | mA   |            |  |  |

| 7   | Junction Operating    |       | Тјор   | -          | -20 to +135    | °C   | Note 2     |  |  |

|     | Temperature           |       |        |            |                |      |            |  |  |

| 8   | Storage temperature   |       | Tstg   | -          | -40 to +150    | °C   |            |  |  |

General Note: To determine appropriate deratings for these absolute maximum ratings, see pages 13 and 14 (the Appendix) paragraphs 1.1, 1.2, 1.3 and 1.4. Please refer to the "Precautions for Use" on our website.

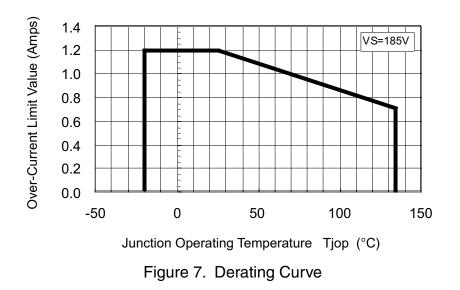

Note 1: Output IGBTs can handle this peak motor current at up to 25 °C junction operating temperature (see Appendix Figure 7). Motor current transients (during Start & Speed-Up) may require a Soft Start circuit to limit these initial currents. See: Motor Control Tech Tips, Volume 1, Issue 1 (Feb'02), "Motor Soft-Start" on our website. Also see Motor Control Tech Tips, Volume 1, Issue 7 (Aug '02), "BLDC Power Bus Under/ Over Voltage Protection" on our website.

Note 2: Thermal resistance

- 1) Between junction and IC case (Tab): Rj-c = 4 °C/W

- 2) Between junction and air:  $Rj-a = 40 \circ C/W$

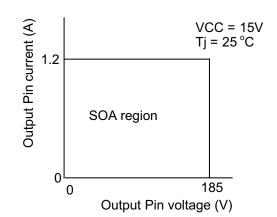

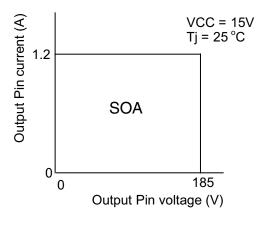

- 1.1 Safe Operating Area (SOA) and Derating

The ECN30102 should never be used outside the SOA shown, where the current and voltage are at the MU, MV and MW pins (motor coils) when the phase is changed (turned-OFF).

# HITACHI

## 2. Electrical characteristics

| 5   | Suffix (T; Top arm, B; Bottom arm) |                   |         |            |      | Ta = | 25 °C |      |                                       |        |

|-----|------------------------------------|-------------------|---------|------------|------|------|-------|------|---------------------------------------|--------|

| NO  |                                    | Items             | Symbols | Terminals  | MIN  | TYP  | MAX   | Unit | Conditions                            |        |

| 1   | Supply Voltage                     |                   | VSop    | VS1, VS2   | 20   | 141  | 185   | V    |                                       |        |

| 2   |                                    |                   | VCCop   | VCC        | 13.5 | 15   | 16.5  | V    |                                       |        |

| 3   | Standby Cur                        | rent              | ISH     | VS1, VS2   | -    | 0.25 | 0.5   | mA   | VSP=0V, VS=141V                       |        |

| 4   |                                    |                   | ICC     | VCC        | -    | 6    | 12    | mA   | VSP=0V,VCC=15V,IB=0A                  |        |

| 5   | IGBT FVD                           |                   | VONT    | MU, MV, MW | -    | 2.0  | 3.0   | V    | I=0.5A, VCC=15V                       |        |

| 6   |                                    |                   | VONB    | MU, MV, MW | -    | 2.0  | 3.0   | V    | I=0.5A, VCC=15V                       |        |

| 7   | Output                             | Turn ON           | TdONT   | MU, MV, MW | -    | 0.5  | 2.0   | μs   | VS=141V, VCC=15V                      |        |

| 8   | Delay                              |                   | TdONB   | MU, MV, MW | -    | 0.5  | 2.0   | μs   | I=0.7A                                |        |

| 9   | Time                               | Turn OFF          | TdOFFT  | MU, MV, MW | -    | 1.0  | 2.0   | μs   | Resistive Load                        |        |

| 10  |                                    |                   | TdOFFB  | MU, MV, MW | -    | 0.8  | 2.0   | μs   | 1                                     |        |

| 11  | Free wheel                         |                   | VFDT    | MU, MV, MW | -    | 2.0  | 2.5   | V    | I=0.5A                                |        |

| 12  | Diode FVD                          |                   | VFDB    | MU, MV, MW | -    | 2.2  | 2.7   | V    | 1                                     |        |

| 13  | Output Resis                       | stance            | RVTR    | VTR        | -    | 200  | 400   | Ω    | VCC=15V                               |        |

| 14  | SAW                                | H or Low Level    | VSAWH   |            | 4.9  | 5.4  | 6.1   | V    | VCC=15V                               |        |

| 15  | Wave                               |                   | VSAWL   | CR         | 1.7  | 2.1  | 2.5   | V    | Note 1                                |        |

| 16  |                                    | Amplitude         | VSAWW   |            | 2.8  | 3.3  | 3.8   | V    | VCC=15V Note 2                        |        |

| 17  | Reference vo                       | oltage            | Vref    | RS         | 0.45 | 0.5  | 0.55  | V    | VCC=15V                               |        |

| 18  |                                    | Voltage           | VIH     |            | 3.5  | -    | -     | V    | VCC=15V                               |        |

| 19  | Hall                               |                   | VIL     | HU,        | -    | -    | 1.5   | V    |                                       | _      |

| 20  | Signal<br>Inputs                   | Current           | IIL     | HV,<br>HW  | -100 | -    | -     | μA   | HU, HV, HW=0V<br>VCC=15V              | Note   |

| 21  |                                    |                   | IIH     |            | -30  | -    | -     | μA   | HU, HV, HW <del>=</del> 5V<br>VCC=15V | 3      |

| 22  |                                    | Current           | IVSPH   | VSP        | 5    | -    | 50    | μA   | VSP=5V, VCC=15V<br>Note 4             |        |

| 23  | VSP<br>Input                       | Offset Voltage    | SPCOMOF |            | -40  | 10   | 60    | mV   | VCC=15V<br>Refer to CR terminal       |        |

| 24  | -                                  | All OFF operation | Voff    |            | 0.85 | 1.23 | 1.6   | V    | VCC=15V                               |        |

| 25  |                                    | Voltage           | VB      |            | 6.8  | 7.5  | 8.2   | V    | VCC=15V, IB=0A                        |        |

| 26  | VB Supply                          | Current           | IB      | СВ         | -    | -    | 25    | mA   | 50mAMaxAllowable                      | Rating |

| 26a | Output                             | Regulation        | δVB     |            | -    | -    | -100  | mV   | VCC = 15V, IB =                       | 25mA   |

| 27  |                                    |                   | RFGP    |            | -    | 1.5  | 3.0   | kΩ   | IFG=+1mA                              | Note   |

| 28  |                                    |                   | RFGN    | FG         | -    | 0.7  | 1.5   | kΩ   | IFG=-1mA                              | 5      |

| 29  | Detect voltage                     |                   | LVSDON  | VCC,       | 10.0 | 11.5 | 12.9  | V    |                                       |        |

| 30  | LVSD                               | Recover Voltage   | LVSDOFF | MU, MV, MW | 10.1 | 12.0 | 13.0  | V    | Note 6                                |        |

| 31  |                                    | Hysteresis        | Vrh     |            | 0.1  | -    | 0.9   | V    | 1                                     |        |

|     | RS terminal                        |                   | IILRS   | RS         | -100 | -    | -     | μA   | VCC= 15V, VSP=0V, F                   | RS=0V  |

Note 1. See Standard Applications in Section 4, page 8 to set the SAW wave frequency.

Note 2. The amplitude of SAW (i.e., VSAWW) is determined by the following equation: VSAWW = VSAWH – VSAWL

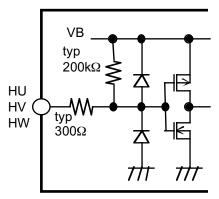

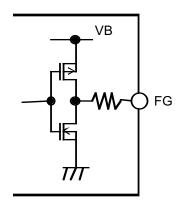

Note 3. Internal Pull Up resistors are typically 200 k $\Omega$ . The equivalent circuit is shown in Fig. 2.

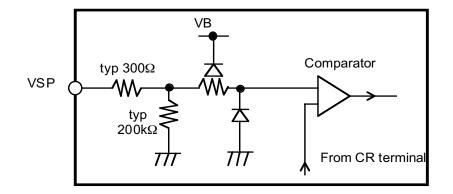

Note 4. Internal Pull Down resistors are typically 200 k $\Omega$ . The equivalent circuit is shown in Fig. 3.

Note 5. The equivalent circuit is shown in Fig. 4.

Note 6. The LVSD (Low Voltage Shut Down) function Detects and Shuts-Down at lower VCC.

Figure 2 Equivalent circuit around HU, HV, HW

Figure 3 Equivalent circuit around VSP

Figure 4 Equivalent circuit around FG

# HITACHI

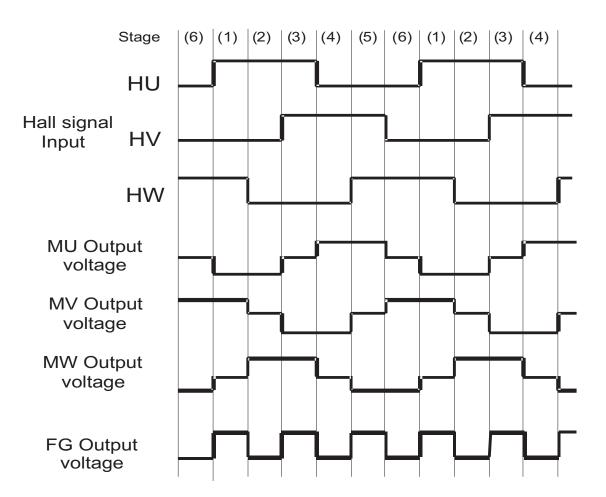

## 3. IGBT Motor Bridge Commutation and Logic Functions

## 3.1 Truth table

| stage | Hall | signal | Input |     | U      | ,   | V      | W   |        | FG     |

|-------|------|--------|-------|-----|--------|-----|--------|-----|--------|--------|

|       | HU   | ΗV     | HW    | Тор | Bottom | Тор | Bottom | Тор | Bottom | Output |

|       |      |        |       | arm | arm    | arm | arm    | arm | arm    |        |

| (1)   | Н    | L      | Н     | OFF | ON     | ON  | OFF    | OFF | OFF    | Н      |

| (2)   | Н    | L      | L     | OFF | ON     | OFF | OFF    | ON  | OFF    | L      |

| (3)   | Н    | Н      | L     | OFF | OFF    | OFF | ON     | ON  | OFF    | Н      |

| (4)   | L    | Н      | L     | ON  | OFF    | OFF | ON     | OFF | OFF    | L      |

| (5)   | L    | Н      | Н     | ON  | OFF    | OFF | OFF    | OFF | ON     | Н      |

| (6)   | L    | L      | Н     | OFF | OFF    | ON  | OFF    | OFF | ON     | L      |

| -     | L    | L      | L     | OFF | OFF    | OFF | OFF    | OFF | OFF    | L      |

| -     | Н    | Н      | Н     | OFF | OFF    | OFF | OFF    | OFF | OFF    | Н      |

3.2 Timing chart

### 3.3 PWM operation

The PWM signal is generated by comparing the input voltage at the VSP pin with an internal SAW wave voltage (available at the CR pin). The Duty Cycle of the resulting PWM signal is thus directly, linearly controlled by VSP pin voltage: from the Min of VSAWL to the Max of VSAWH. That is, when VSP is below VSAWL, the PWM duty cycle is at the Minimum value of 0%. When VSP is above VSAWH, the PWM duty is at the Maximum value of 100%. ECN30102 operates in 2 quadrants by chopping the BOTTOM Arms with this PWM duty cycle during the appropriate commutation times (phases). Thus, the duty cycle controls motor torque and speed.

### 3.4 Motor Over-Current limiting operation

Over-Current is monitored via the voltage drop across an external resistance RS. If the input voltage at the RS pin exceeds the internal Reference voltage (Vref is typically 0.5V), all BOTTOM Arms are Turned-OFF. Following an Over Current event, reset is automatically attempted during each period of the on-chip OSC. This on-chip OSC signal is available at the VTR pin. If the Over-Current function is not used, the RS pin must be connected to the GL pin with less than  $100\Omega$ .

### 3.5 VCC Under-Voltage Detection

If VCC drops below LVSDON (11.5V typ), all IGBTs TOP and BOTTOM Arms Turn-OFF. Normal operation returns when VCC rises above LVSDOFF: the value of LVSDOFF is LVSDON + Vrh.

### 3.6 The all output IGBT Shut-OFF function

When the VSP pin drops below Voff (1.23V typ), all IGBTs TOP and BOTTOM Arms Shut-OFF

| VSP input voltage     | TOP Arm outputs               | BOTTOM Arm outputs            |

|-----------------------|-------------------------------|-------------------------------|

| $0V \le VSP \le Voff$ | All IGBTs are OFF             | All IGBTs are OFF             |

| Voff ≤ VSP < VSAWL    | Following the 3.1 Truth Table | All IGBTs are OFF             |

| VSP ≥ VSAWL           | Following the 3.1 Truth Table | Following the 3.1 Truth Table |

While the motor is rotating, if the VSP pin drops below Voff, the motor stops. Under this condition, the VS voltage could rise but, in all cases, VS must not exceed the 250VDC Breakdown Voltage.

## 4. Standard application

#### 4.1 External components

| Components | Standard value                                                                    | Usage                                     | Remarks                             |

|------------|-----------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------|

| C0         | 0.22µF ± 20%                                                                      | Filters the internal<br>power supply (VB) | Stress voltage is VB (=8.2V)        |

| C1, C2     | 1.0μF ± 20%                                                                       | The Charge Pump                           | Stress voltage is VCC               |

| D1, D2     | Hitachi DFG1C4 (Glass<br>mold type), DFM1F4<br>(Resin mold type)<br>or equivalent | The Charge Pump                           | 400V, 1A<br>trr ≤ 100ns             |

| RS         | Note 1                                                                            | Sets Over-Current limit                   |                                     |

| CTR        | 1800 pF ± 5%                                                                      | Sets PWM frequency                        | Stress voltage is VB (=8.2V) Note 2 |

| RTR        | 22 kΩ ± 5%                                                                        | Sets PWM frequency                        | Stress voltage is VB (=8.2V) Note 2 |

Note 1: Peak Start-Up current (IO) is fixed by the Over-Current limit detection/protection function. This requires the user to provide a sense resistor (RS) scaled to detect the desired Peak Start-Up current. The value of RS can be calculated by substituting the maximum Vref value (0.55V) and the Peak current desired. Recognize that the resultant value of RS is the minimum value of the required resistor, which is the worst case value.

RS = Vref / IO

Where: IO is in Amps, Vref = 0.55V and RS is the low tolerance value of the required resistor.

Since this triggers Over-Current protection, IO represents the Peak (MAX) desired current in a given design. To determine the Sense Resistor RS, refer to the above comments and Appendix paragraphs 1.2 and 1.3.

Note 2: The PWM frequency is approximated by the following equation:

FPWM (in Hertz) ~ 0.494 / ( CTR x RTR ) ... Note: CTR is in Farads, RTR is in Ohms

Note 3: A standard value for the Hall resistors RU, RV, RW is 5.6 k $\Omega$   $\pm$  5%

# HITACHI

Figure 5. Block Diagram

NOTE: A Speed Reverse Function for Single Chip BLDC Motor Drive ICs (such as this ECN30102) is discussed in Motor Control Tech Tips, Volume 1, Issue 9 (Oct '02). "Implementing Single Chip Safe Direction Reversal and TACH Pulse" (see our web pages).

### 4.2 Input Pins

In some applications, input pins may be noise sensitive due to their high impedance. This can be minimized with the use of external resistance and/or capacitance as follows:

- A pull down resistor of 5.6 k $\Omega$  ± 5% from the VSP pin to ground (the GL pin).

- A 500 pF  $\pm$  20% ceramic capacitor from HU, HV, HW and VSP pins to ground (the GL pin).

# HITACHI

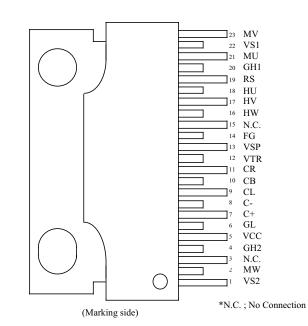

### 5. Pinout

### 6. Pin Definitions

| Terminal<br>No. | Symbol | Definition                                                           | Remarks      |

|-----------------|--------|----------------------------------------------------------------------|--------------|

| 1               | VS2    | Power Supply for Upper IGBT of phases V and W                        | Note1, Note2 |

| 2               | MW     | W phase output (to BLDC motor coil W)                                | Note1        |

| 3               | NC     | No Connection                                                        | Note4        |

| 4               | GH2    | W phase emitter of IGBT and anode of FWD. Connect RS                 | Note3        |

| 5               | VCC    | Analog power supply                                                  |              |

| 6               | GL     | Analog ground                                                        |              |

| 7               | C+     | For the Charge Pump circuit, power supply for TOP Arm drive circuit  | Note1        |

| 8               | C-     | For the Charge Pump circuit                                          | Note1, Note2 |

| 9               | CL     | For the Charge Pump circuit                                          | Note1        |

| 10              | СВ     | Internally regulated (VB) power supply output                        |              |

| 11              | CR     | Connect resistance & capacitance to generate the PWM clock frequency |              |

| 12              | VTR    | Connect resistance to generate the PWM clock frequency               |              |

| 13              | VSP    | Input analog voltage that varies the PWM duty cycle from 0% to 100%  |              |

| 14              | FG     | Tachometer output signal whose frequency is (RPM/60)x(P/2)x3 Hertz   |              |

| 15              | NC     | No Connection                                                        | Note4        |

| 16              | HW     | Input signal from the Hall IC of phase W                             |              |

| 17              | HV     | Input signal from the Hall IC of phase V                             |              |

| 18              | HU     | Input signal from the Hall IC of phase U                             |              |

| 19              | RS     | RS voltage detect input for the on-chip Over Current limit detection |              |

| 20              | GH1    | U and V phase emitters of IGBT and anode of FWD. Connect RS.         | Note3        |

| 21              | MU     | U phase output (to BLDC motor coil U)                                | Note1        |

| 22              | VS1    | Power Supply for Upper IGBT of phase U                               | Note1, Note2 |

| 23              | MV     | V phase output (to BLDC motor coil V)                                | Note1        |

Note1: This is a High Voltage pin.

Note2: The VS1, VS2 and C- pins are connected within the IC but, VS1 and VS2 must both be connected to the VS Supply Voltage by external wiring.

Note3: GH1 and GH2 are not connected within the IC and must be connected by external wiring. Note4: Not connected

### 7. Quality Assurance

7.1 Appearance and dimension

ANSI Z1.4-1993 General inspection levels II AQL 1.0%

7.2 Electrical characteristics ANSI Z1.4-1993 General inspection levels II AQL 0.65%

### 8. Do's and Don'ts

8.1 The tab should be attached to a heat sink by applying a torque of 0.39 to 0.78 N-m.

8.2 The tab should not be soldered.

8.3 To protect this chip from Electrical Static Discharge (ESD), the ECN 30102 should be handled in accordance with normal industry standard procedures for protection against damage due to ESD. For a more detailed discussion of this area, please refer to the web, "Precautions for Use" Section 5.

8.4 Depending on local industry/market regulations, conformal coating may be required for the following pin-to-pin spacings: 1-2, 2-4, 6-7, 8-9, 9-10, 20-21, 21-22, 22-23.

8.5 Protective function against short circuit (ex. load short, line-to-ground short or TOP/BOTTOM Arm shorts) is not built into this IC. External protection may be needed to prevent IC breakdown under these potential application conditions.

8.6 Hitachi high voltage ICs are manufactured to meet standard industrial grade reliability specifications. In cases where extremely high reliability is required (such as nuclear power control, aerospace and aviation, traffic equipment, life-support-related medical equipment, fuel control equipment and various kinds of safety equipment) system integrity must be achieved via fail-safe system design. Additionally, it is the responsibility of the designer to insure that any IC failure does not damage property or human life. Users should evaluate and consider employing the following design precautions:

a) Sufficient derating of the specifications should be utilized to minimize the possibility of failures based on the maximum ratings, operating temperature and environmental conditions.

b) Design redundancy should be applied so that application performance will be maintained even in a case of IC failure.

c) The system design should implement fail-safe design techniques to protect property and human life even where incorrect system operation is experienced.

### 9. Precautions for Safe Use

If semiconductor devices are handled in an inappropriate manner, failure may result. For this reason, be sure to read "Precautions for Use" on our website before use.

(If a semiconductor device fails, there may be cases in which the semiconductor device, wiring or wiring pattern will emit smoke or cause a fire or in which the semiconductor device will burst.)

### 10. Notices

1. This publication contains the specifications, characteristics (in figures and tables), dimensions and handling notes concerning power semiconductor products (hereinafter called "products" to aid in the selection of suitable products.

2. The specifications and dimensions, etc. stated in this publication are subject to change without prior notice to improve product's characteristics. Before ordering, purchasers are advised to contact Hitachi's sales department for the latest version of this publication and specifications.

3. In no event shall Hitachi be liable for any damage that may result from an accident or any other cause during operation of the user's units according to this publication. Hitachi asumes no responsibility for any intellectual property claims or any other problems that may result from applications of information, products or circuits described in this publication.

4. In no event shall Hitachi be liable for any failure in a semiconductor device or any secondary damage resulting from use at a value exceeding the absolute maximum rating.

5. No license is granted by this publication under any patents or other rights of any third party, or Hitachi, Ltd.

6. This publication may not be reproduced or duplicated, in any form, in whole or in part, without the expressed written permission of Hitachi, Ltd.

7. The products (technologies) described in this publication are not to be provided to any party whose purpose in their application will hinder maintenance of international peace and safety nor are they to be applied to that purpose by their direct purchasers or any third party. When exporting these products (technologies), the necessary procedures are to be taken in accordance with related laws and regulations.

Appendix - Supplementary and Reference Data

Refer to the derating information below when designing with the ECN30102. This information is provided for reference purposes only.

1. Safe Operating Area (SOA) and Derating

### 1.1 SOA

The ECN30102 should never be used outside the SOA shown below in Figure 6, where the current and voltage are at the MU, MV and MW pins (motor coils) when the phase is changed (turned-OFF).

Figure 6. SOA

1.2 Derating output current based on temperature

SOA has a dependence on junction operating temperature (Tjop). Determine the RS value according to the derating curve of Figure 7, include the MAX value of Vref and the LOW side tolerance of RS. For general reliability reasons, Junction Operating Temperature must not exceed 110  $^{\circ}$ C.

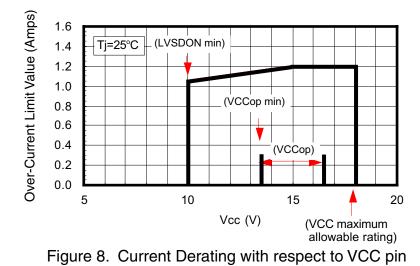

1.3 Power supply power-on sequence and derating for VCC

Power supply sequence of power-on should be VCC on first, then VS on, then VSP on. For power-off, it should be VSP off first, then VS off, then VCC off. If the value on the VSP pin is less than Voff, the power-on supply sequencing is not required. In the event power sequencing can not be assured, such as during a sudden power supply failure, the following will occur:

When IGBTs are forced to operate with lower gate voltages, the possibility of thermal failure arises because the IGBT saturation voltage rapidly increases. This is especially true if the VCC voltage is in the range between LVSDON Min and VCCop Min, that is in the range of 10.0V to 13.5V.

To avoid this occurrence, apply the VCC derating curve shown in Figure 8.

- 1.4 General Design Derating Standards

- a) Temperature Junction Operating Temperature must be kept under 110°C.

- b) Supply Voltage VS power supply voltage must be kept under 185V.

HITACHI

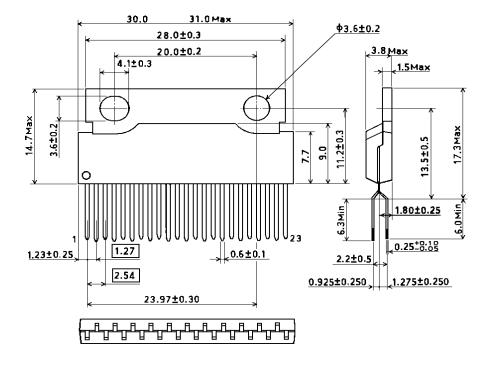

### 3) ECN30102SPV

2) ECN30102SPR