# 16384-word×1-bit Dynamic Random Access Memory

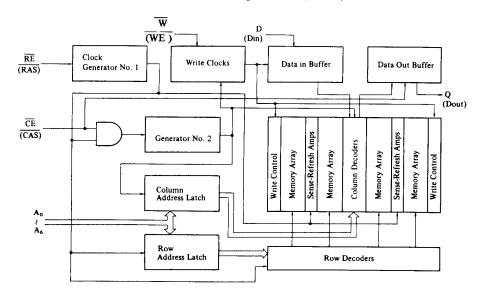

The HM4816 is a new generation MOS dynamic RAM circuit organized as 16,384 words by 1 bit. As a state-of-the art MOS memory device, the HM4816 (16K RAM) incorporates advanced circuit techniques designed to provide wide operating margins, both internally and to the system user, while achieving performance levels in speed and power previously seen only in MOSTEK's high performance MK4027 (4K RAM).

The technology used to fabricate the HM4816 is HITACHI's double-poly, N-channel silicon gate process.

This process, coupled with the use of a single transistor dynamic storage cell provides the maximum possible circuit density and reliability, while maintaining high performance capability.

The use of dynamic circuitry throughout, including sense amplifiers, assures that power dissipation is minimized without any sacrifice in speed or operating margin. These factors combine to make the HM4816 a truly superior RAM product.

Multiplexed address inputs (a feature pioneered by MOSTEK for its 4K RAMs) permits the HM4816 to be packaged in a standard 16-pin DIP.

This recognized industry standard package configuration, while compatible with widely available automated testing and insertion equipment, provides highest possible system bit densities and simplifies system upgrade from 4K to 16K RAMs Non-critical clock timing requirements allow use of the multiplexing technique while maintaining high performance.

#### ■ FEATURES

- Single 5V supply

- Low power standby and operation

(Standby: 55mW max, operation: 440mW max)

- Fast access time & cycle time

- (access time: 100ns max, cycle time: 200ns min)

- Directly TTL compatible: All inputs & outputs

- Output data controlled by CAS and unlatched at end of cycle to allow two dimensional chip selection and extended page boundary

- Common I/O capability using "early write" operation

- Read modify write, RAS only refresh and page mode capability

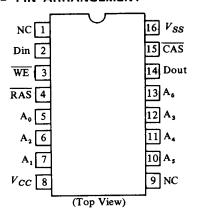

#### ■ PIN ARRANGEMENT

#### ABSOLUTE MAXIMUM RATINGS

| Item                                 | Symbol           | HM4816    | Unit |  |

|--------------------------------------|------------------|-----------|------|--|

| Voltage on any pin relative to GND   | $V_T$            | -1.0~+7.0 | V    |  |

| Power supply voltage relative to GND | V <sub>CC</sub>  | -0.5~+7.0 | V    |  |

| Short-circuit Output Current         | Iout             | 50        | mA   |  |

| Power Dissipation                    | $P_T$            | 1.0       | W    |  |

| Operating Temperature                | Topr             | 0~+70     | °C   |  |

| Storage Temperature                  | T <sub>stg</sub> | -65~+150  | °C   |  |

# ■ RECOMMENDED DC OPERATING CONDITIONS

| Item                                            | Symbol            | min. | typ. | max. | Units | Notes |

|-------------------------------------------------|-------------------|------|------|------|-------|-------|

| Supply voltage                                  | <b>V</b> cc       | 4.5  | 5.0  | 5.5  | V     | 1     |

|                                                 | Vss               | 0    | 0    | 0    | V     | 1,2   |

| Input high(logic 1) voltage RAS, CAS, WE        | V <sub>IH</sub> c | 2.7  |      | 6.0  | V     | 1     |

| Input high(logic 1) voltage except RAS, CAS, WE | V <sub>IH</sub>   | 2.7  |      | 6.0  | V     | 1     |

| Input low(logic 0) voltage all inputs           | V <sub>II</sub> . | -1.0 |      | 0.8  | V     | 1     |

Notes: 1. All voltages referenced to  $V_{SS}$ .

2. Output voltage will swing from V<sub>SS</sub> to V<sub>CC</sub> when activated with no current loading.

### ■ DC ELECTRICAL CHARACTERISTICS

| Item                   | Symbol  | Test Conditions                                                                         | min. | typ. | max. | Unit |

|------------------------|---------|-----------------------------------------------------------------------------------------|------|------|------|------|

| Operating current      | Icci    | $\overline{RAS}$ , $\overline{CAS}$ cycling, $t_{RC} = 200$ ns, Note 2                  |      | _    | 80   | mA   |

| Standby current        | Icc 2   | $\overline{RAS} = V_{IHC}$ , Dout = high impedance                                      |      | _    | 10   | mA   |

| Refresh current        | Iccs    | $\overline{RAS}$ cycling, $\overline{CAS} = V_{IHC}$ ; $t_{RC} = 200$ ns                | _    |      | 55   | mA   |

| Page mode current      | Icc4    | $\overline{RAS} = V_{IL}$ , $\overline{CAS}$ cycling, $t_{PC} = 120 \text{ns}$ ; Note 2 |      | _    | 55   | mA   |

| Input leakage current  | II (L)  | $V_{IN}=0$ to 6V, all other pins=0V                                                     | -10  |      | 10   | μΑ   |

| Output leakage current | Io ( L) | V <sub>OUT</sub> =0 to 5.5V, Dout is disabled                                           | -10  |      | 10   | μА   |

| Output high voltage    | Von     | Note 1, $I_{out} = -5 \text{mA}$                                                        | 2.4  | _    | Vcc  | V    |

| Output low voltage     | Vol     | $I_{OUT}=4.2\mathrm{mA}$                                                                | _    | _    | 0.4  | V    |

Notes: 1. Output voltage will swing from  $V_{SS}$  to  $V_{CC}$  when activated with no current loading.

I<sub>CC1</sub> and I<sub>CC4</sub> depend upon output loading. During readout of high level data V<sub>CC</sub> is connected through a low impedance (135Ω typ) to data out. At all other times I<sub>CC</sub> consists of leakage currents only.

#### ■ A.C. ELECTRICAL CHARACTERISTICS $(T_a=0 \text{ to } 70\%, V_{CC}=5.0\text{V}\pm10\%)$

| Item                                         | Symbol         | min. | typ. | max.  | Unit | Note |

|----------------------------------------------|----------------|------|------|-------|------|------|

| Random read or write cycle Time              | t RC           | 200  | _    |       | ns   | 3    |

| Read-write Cycle Time                        | t rwc          | 200  |      |       | ns   | 3    |

| Page Mode Cycle Time                         | t pc           | 120  |      |       | ns   |      |

| Access Time from RAS                         | trac           |      | _    | 100   | ns   | 4,6  |

| Access Time from CAS                         | tere           | _    |      | 65    | ns   | 5,6  |

| Output Buffer Turn-off Delay                 | toff           | 0    | _    | 25    | ns   | 7    |

| Transition Time (rise & fall)                | tт             | 3    |      | 25    | ns   | 2    |

| RAS Precharge                                | t RP           | 65   | _    |       | ns   |      |

| RAS Pulse Width                              | tras           | 100  | _    | 10000 | ns   |      |

| RAS Hold Time                                | t RSH          | 65   |      | -     | ns   |      |

| CAS Pulse Width                              | teas           | 65   | _    | 10000 | ns   |      |

| RAS to CAS Delay Time                        | t RCD          | 15   | _    | 35    | ns   | 8    |

| CAS to RAS Precharge Time                    | t CRP          | 40   |      | _     | ns   |      |

| Row Address Set-up Time                      | t ASR          | 0    | _    |       | ns   |      |

| Row Address Hold Time                        | t RAH          | 15   |      | _     | ns   |      |

| Column Address Set-up Time                   | tasc           | 0    | _    | _     | ns   |      |

| Column Address Hold Time                     | t CAH          | 35   | _    |       | ns   |      |

| Column Address Hold Time reference to RAS    | t A R          | 70   |      | -     | ns   |      |

| Read Command Set-up Time                     | t RCS          | 0    | _    |       | ns   |      |

| Read Command Hold Time                       | t RCH          | 10   | _    |       | ns   |      |

| Write Command Hold Time                      | twcн           | 40   |      | _     | ns   |      |

| Write Command Hold Time reference to RAS     | twc R          | 75   |      | _     | ns   |      |

| Write Command Pulse Width                    | twp            | 30   | _    |       | ns   |      |

| Write Command to RAS Lead Time               | t RWL          | 45   | _    | _     | ns   |      |

| Write Command to CAS Lead Time               | t cwr.         | 45   | _    | _     | ns   |      |

| Data-in Set-up Time                          | t v s          | 0    |      |       | ns   | 9    |

| Data-in Hold Time                            | t D H          | 40   |      | _     | ns   | 9    |

| Data-in Hold Time reference to RAS           | <b>t</b> D H R | 75   | _    |       | ns   |      |

| CAS Precharge Time(for page mode cycle only) | t ∈ PP         | 40   | _    | _     | ns   |      |

| Refresh Period                               | t REF          | _    | _    | 2     | ns   |      |

| WE Command Set-up Time                       | twes           | -10  | _    | _     | ns   | 10   |

| CAS to WE Delay                              | t cwo          | 45   | _    |       | ns   | 10   |

| RAS to WE Delay                              | t RWD          | 80   |      |       | ns   | 10   |

| CAS Hold Time                                | t c s н        | 100  |      |       | ns   |      |

### NOTES:

- 1. AC measurements assume  $t_T = 5ns$ .

- V<sub>IHC</sub>(min) or V<sub>IH</sub> (min) and V<sub>IL</sub> (max) are reference levels for measuring timing of input signals. Also transition times are measured between V<sub>IHC</sub> or V<sub>IH</sub> and V<sub>IL</sub>.

- 3. The specification for  $t_{RC}$  (min) and  $t_{RWC}$  (min) are used only to indicate cycle time at which proper operation over the full temperature range (0°C +  $T_a \le 70$ °C) is assured.

- 4. Assumes that  $t_{RCD} \le t_{RCD}$  (max.). If  $t_{RCD}$  is greater than the maximum recommended value shown in this table,  $t_{RAC}$  will increase by the amount that  $t_{RCD}$  exceeds the value shown.

- 5. Assumes that  $t_{RCD} \ge t_{RCD}$  (max).

- Measured with a load equivalent to 2 TTL loads and 100pF.

- toff (max) defines the time at which the output achieves the open circuit condition and is not referenced to output voltage levels.

- Operation within the t<sub>RCD</sub> (max) limit insures that t<sub>RAC</sub> (max) can be met, t<sub>RCD</sub> (max) is specified as a reference point only; if t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub> (max) limit, then access time is controlled exclusively by t<sub>CAC</sub>.

- These parameters are referenced to CAS leading edge in early write cycles and to WE leading edge in delayed write or readmodify-write cycles.

- 10.twcs, tcwD and trwD are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only; If twcs ≥ twcs (min), the cycle is an early write cycle and the data out pin will remain open circuit (high impedance) throughout the entire cycle; If tcwD ≥ tcwD (min) and trwD ≥ trwD (min), the cycle is a read-write cycle and the data out will contain data read from the selected cell; If neither of the above sets of conditions is satisfied the condition of the data out (at access time) is indeterminate.

### ■ CAPACITANCE $(Ta=0 \text{ to } 70\%, Vcc=5.0V\pm10\%)$

| Item                              | Symbol     | min. | typ. | max. | Unit | Note |

|-----------------------------------|------------|------|------|------|------|------|

| Input Capacitance (Ao to Ao), Din | C11        |      | 4    | 6    | pF   | 1    |

| Input Capacitance RAS, CAS, WE    | C12        |      | 5    | 7    | pF   | 2    |

| Output Capacitance (Dout)         | <i>C</i> o | _    | 5    | 7    | pF   | 2,3  |

Notes: 1. Effective capacitance calculated from the equation  $C = I \circ \Delta t / \Delta V$  with  $\Delta V = 3V$  and power supplies at nominal levels.

2.  $\overline{CAS} = V_{IHC}$  to disable  $D_{OUT}$ .

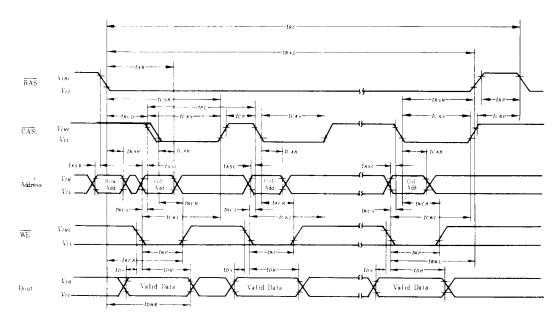

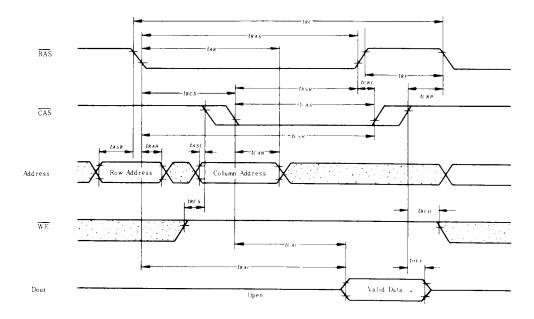

#### • READ CYCLE

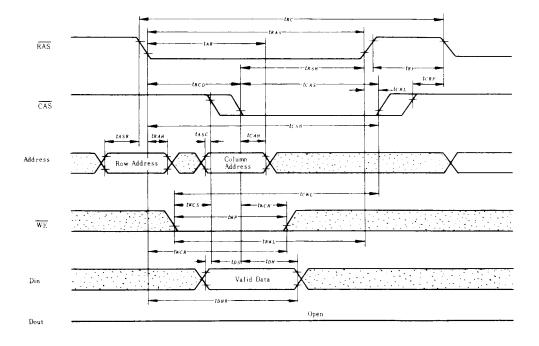

### • WRITE CYCLE

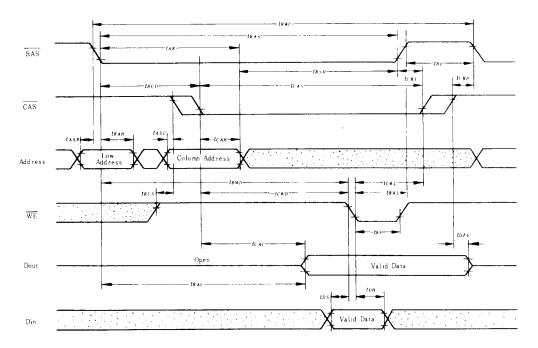

### • READ-WRITE/READ-MODIFY-WRITE CYCLE

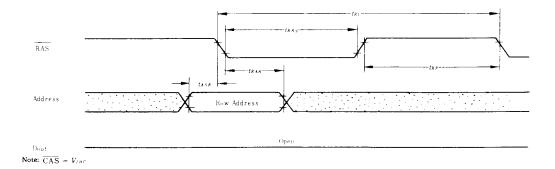

# • RAS-ONLY" REFRESH CYCLE

**@HITACHI**

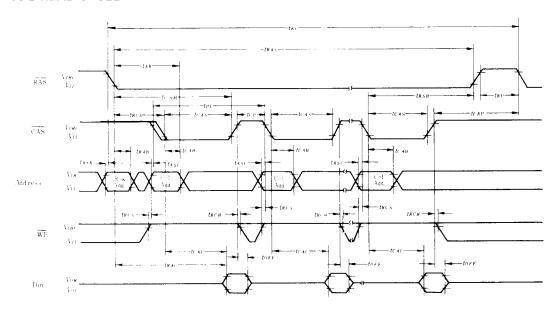

# • PAGE MODE READ CYCLE

# • PAGE MODE WRITE CYCLE