# Ultra-Low Distortion, High Speed Audio Operational Amplifier

# SSM-2131

#### FEATURES

- Low Distortion DC to 40kHz, A<sub>v</sub> = +10 ...... 0.01% Typ

- High Slew Rate ...... 40V/µs Min

- Gain-Bandwidth Product ...... 10MHz Typ

- APPLICATIONS

- Power Amplifier Driver

- Active Filter Circuits

- Parametric Equalizers

- Graphic Equalizers

- Mixing Consoles

- Voltage Summers

- Active Crossover Networks

#### **GENERAL DESCRIPTION**

The SSM-2131 is a fast JFET input operational amplifier intended for use in audio applications. The SSM-2131 offers a symmetric 50V/µs slew rate for low distortion and is internally compensated for unity gain operation. Power supply current is less than 6.5mA. Unity-gain stability, a wide full-power bandwidth of 800kHz, and excellent ability to handle transient overloads make the SSM-2131 an ideal amplifier for use in high performance audio amplifier circuits.

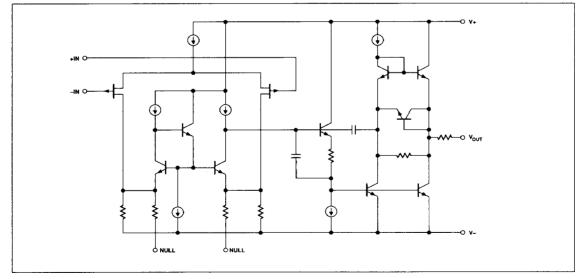

#### SIMPLIFIED SCHEMATIC

The SSM-2131's common-mode rejection of 80dB minimum over a ±11 range is exceptional for a high-speed amplifier. High CMR, combined with a minimum 500V/mV gain into a 10kΩ load ensures excellent linearity in both noninverting and inverting gain configurations. This means that distortion will be very low over a wide range of circuit configurations. The low offset provided by the JFET input stage often eliminates the need for AC coupling or for external offset trimming.

2

The SSM-2131 conforms to the standard 741 pinout with nulling to V–. The SSM-2131 upgrades the performance of circuits using the TL071 by direct replacement.

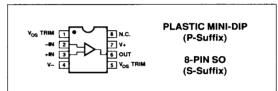

#### **PIN CONNECTIONS**

REV. A

#### ORDERING INFORMATION

| PACKAGE          |             | OPERATING            |  |

|------------------|-------------|----------------------|--|

| PLASTIC<br>8-PIN | SO<br>8-PIN | TEMPERATURE<br>RANGE |  |

| SSM2131P         | SSM2131S    | XIND.                |  |

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage                      | ±20V |

|-------------------------------------|------|

| Input Voltage (Note 1)              | ±20V |

| Differential Input Voltage (Note 1) |      |

| Output Short-Circuit De | 65°C to +175°C           |                 |           |

|-------------------------|--------------------------|-----------------|-----------|

| Storage Temperature I   |                          |                 |           |

| Operating Temperature   |                          |                 |           |

| Junction Temperature    |                          | –65°C           | to +175°C |

| Lead Temperature Rar    | nge (Soldering, 60       | sec)            | +300°C    |

| PACKAGE TYPE            | Θ <sub>jA</sub> (Note 2) | θ <sub>jc</sub> | UNITS     |

| 8-Pin Plastic DIP (P)   | 103                      | 43              | °C/W      |

| 8-Pin SO (S)            | 158                      | 43              | °C/W      |

| NOTES                   |                          |                 |           |

NOTES:

For supply voltages less than ±20V, the absolute maximum input voltage is equal to the supply voltage.

Θ<sub>jA</sub> is specified for worst case mounting conditions, i.e., Θ<sub>jA</sub> is specified for device in socket for P-DIP packages; Θ<sub>jA</sub> is specified for device soldered to printed circuit board for SO package.

### **ELECTRICAL CHARACTERISTICS** at V<sub>S</sub> = $\pm 15V$ , T<sub>A</sub> = 25°C, unless otherwise noted.

|                                 |                 |                                                                                                                      | SSM-2131          |                   |     |        |

|---------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-----|--------|

| PARAMETER                       | SYMBOL          | CONDITIONS                                                                                                           | MIN               | TYP               | MAX | UNITS  |

| Slew Rate                       | SR              |                                                                                                                      | 40                | 50                | -   | V/µs   |

| Gain-Bandwidth<br>Product       | GBW             | f <sub>o</sub> = 10kHz                                                                                               | -                 | 10                | -   | MHz    |

| Full-Power<br>Bandwidth         | BWp             | (Note 2)                                                                                                             | 600               | 800               | -   | kHz    |

| Total Harmonic<br>Distortion    | THD             | DC to 40kHz, $R_{\perp} = 10k\Omega$ , $A_{\nu} = +10$                                                               | -                 | 0.01              | -   | %      |

| Voltage Noise Density           | e               | f <sub>o</sub> = 10Hz<br>f <sub>o</sub> = 1kHz                                                                       |                   | 38<br>13          | -   | nV/√Hz |

| Current Noise Density           | i <sub>n</sub>  | f <sub>o</sub> = 1kHz                                                                                                | -                 | 0.007             | -   | pA/√Hz |

| Large-Signal<br>Voltage Gain    | A <sub>vo</sub> | $\begin{aligned} R_{L} &= 10k\Omega \\ R_{L} &= 2k\Omega \\ R_{L} &= 1k\Omega \\ T_{J} &= 25^{\circ}C \end{aligned}$ | 500<br>200<br>100 | 900<br>260<br>170 | -   | V/mV   |

| Output Voltage<br>Swing         | vo              | $R_{L} = 1k\Omega$                                                                                                   | ±11.5             | +12.5<br>-11.9    | _   | ν      |

| Offset Voltage                  | V <sub>os</sub> |                                                                                                                      | _                 | 1.5               | 6.0 | mV     |

| Input Bias Current              | I <sub>B</sub>  | $V_{CM} = 0V T_j = 25^{\circ}C$                                                                                      | _                 | 130               | 250 | рА     |

| Input Offset Current            | l <sub>os</sub> | $V_{CM} = 0V  T_j = 25^{\circ}C$                                                                                     | _                 | 6                 | 50  | рА     |

| Input Voltage Range             | IVR             | (Note 1)                                                                                                             | ±11.0             | +12.5<br>-12.0    | -   | v      |

| Common-Mode<br>Rejection        | CMR             | $V_{CM} = \pm 11V$                                                                                                   | 80                | 92                | -   | dB     |

| Power-Supply<br>Rejection Ratio | PSRR            | $V_{s} = \pm 10V$ to $\pm 20V$                                                                                       | -                 | 12                | 50  | μV/V   |

| Supply Current                  | l <sub>sy</sub> | No Loa <del>d</del><br>V <sub>O</sub> = 0V                                                                           | -                 | 5.1               | 6.5 | mA     |

| Short-Circuit<br>Current Limit  | Isc             | Output Shorted to Ground                                                                                             | ±20               | +33<br>28         | ±60 | mA     |

| Settling Time                   | ts              | 10V Step 0.01% (Note 3)                                                                                              | -                 | 0.9               | 1.2 | μs     |

| Overload Recovery<br>Time       | ton             |                                                                                                                      | -                 | 700               | -   | ns     |

#### 2-316 OPERATIONAL AMPLIFIERS

2

### **ELECTRICAL CHARACTERISTICS** at V<sub>S</sub> = $\pm$ 15V, T<sub>A</sub> = 25°C, unless otherwise noted. *Continued*

| PARAMETER                           |                  |                               | SSM-2131 |     |     |         |

|-------------------------------------|------------------|-------------------------------|----------|-----|-----|---------|

|                                     | SYMBOL           | CONDITIONS                    | MIN      | TYP | MAX | UNITS   |

| Phase Margin                        | øo               | 0dB Gain                      | -        | 47  | -   | degrees |

| Gain Margin                         | A <sub>180</sub> | 180° Open-Loop<br>Phase Shift | ·        | 9   | -   | dB      |

| Capacitive Load<br>Drive Capability | CL               | Unity-Gain Stable<br>(Note 4) | 100      | 300 | -   | pF      |

| Supply Voltage Range                | v <sub>s</sub>   |                               | ±8       | ±15 | ±20 | v       |

NOTES:

1. Guaranteed by CMR test.

2. Guaranteed by slew-rate test and formula  $BW_p = SR/(2\pi 10V_{PEAK})$ .

3. Settling time is guaranteed but not tested.

4. Guaranteed but not tested.

### **ELECTRICAL CHARACTERISTICS** at V<sub>s</sub> = $\pm 15V$ , $-40^{\circ}C \le T_A \le 85^{\circ}C$ , unless otherwise noted.

| PARAMETER                                 |                   |                                                                   | SSM-2131   |               |     |       |

|-------------------------------------------|-------------------|-------------------------------------------------------------------|------------|---------------|-----|-------|

|                                           | SYMBOL            | CONDITIONS                                                        | MIN        | ТҮР           | MAX | UNITS |

| Slew Rate                                 | SR                | R <sub>L</sub> ≠ 2kΩ                                              | 40         | 50            | -   | V/µs  |

| Large-Signal<br>Voltage Gain              | A <sub>vo</sub>   | $R_{L} = 10k\Omega  (Note 1)$ $R_{L} = 2k\Omega  V_{O} = \pm 10V$ | 200<br>100 | 500<br>160    | -   | V/mV  |

| Output Voltage<br>Swing                   | v <sub>o</sub>    | R <sub>L</sub> = 2kΩ                                              | ±11.0      | +12.3<br>11.8 | _   | v     |

| Offset Voltage                            | v <sub>os</sub>   |                                                                   | -          | 2.0           | 7.0 | mV    |

| Offset Voltage<br>Temperature Coefficient | TCV <sub>os</sub> |                                                                   |            | 8             | -   | µV/°C |

| Input Bias Current                        | н <sub>в</sub>    | (Note 1)                                                          | -          | 0.6           | 2.0 | nA    |

| Input Offset Current                      | l <sub>os</sub>   | (Note 1)                                                          | -          | 0.06          | 0.4 | nA    |

| Input Voltage Range                       | IVR               | (Note 2)                                                          | ±11.0      | +12.5<br>12.0 | -   | v     |

| Common-Mode<br>Rejection                  | CMR               | V <sub>CM</sub> = ±11V                                            | 80         | 94            | _   | dB    |

| Power-Supply<br>Rejection Ratio           | PSRR              | $V_{\rm S} = \pm 10$ V to $\pm 20$ V                              | _          | 6             | 50  | μV/V  |

| Supply Current                            | I <sub>SY</sub>   | No Load<br>V <sub>o</sub> = 0V                                    | -          | 5.1           | 6.5 | mA    |

| Short-Circuit<br>Current Limit            | Isc               | Output Shorted to Ground                                          | ±8         | -             | ±60 | mA    |

NOTES:

T<sub>1</sub> = 85°C.

Guaranteed by CMR test.

2. Cuaranteed by charitest.

REV. A

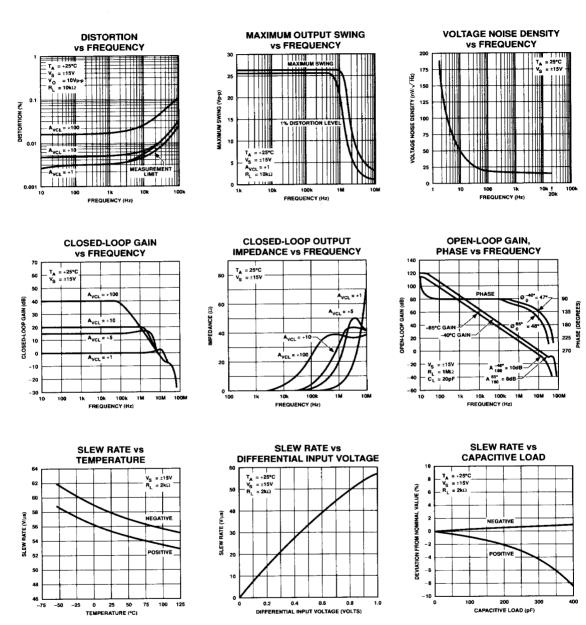

#### TYPICAL PERFORMANCE CHARACTERISTICS

#### 2-318 OPERATIONAL AMPLIFIERS

REV. A

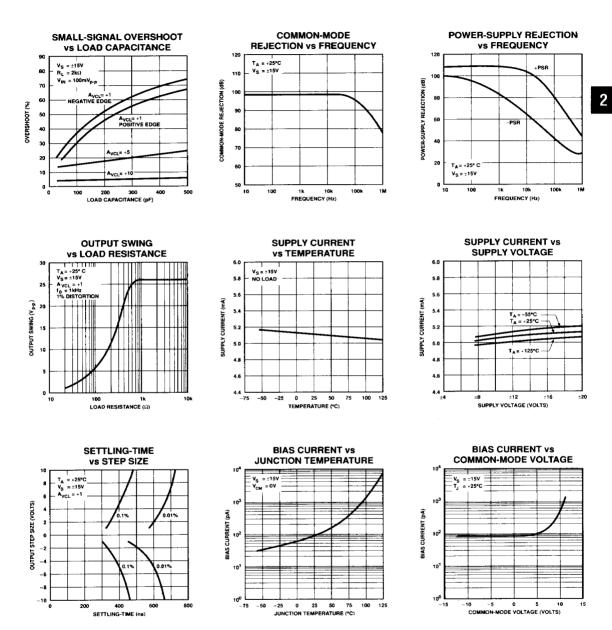

#### TYPICAL PERFORMANCE CHARACTERISTICS Continued

REV. A

#### **APPLICATIONS INFORMATION**

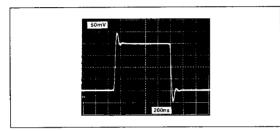

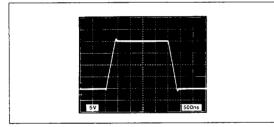

The SSM-2131 combines speed with a high level of input precision usually found only with slower devices. Well-behaved AC performance in the form of clean transient response, symmetrical slew rates and a high degree of forgiveness to supply decoupling are the hallmarks of this amplifier. AC gain and phase response are quite independent of temperature or supply voltage. Figure 1 shows the SSM-2131's small-signal response. Even with 75pF loads, there is minimal ringing in the output waveform. Large-signal response is shown in Figure 2. This figure clearly shows the SSM-2131's exceptionally close matching between positive and negative slew rates. Slew rate symmetry decreases the DC offset a system encounters when processing high-frequency signals, and thus reduces the DC current necessary for load driving.

**FIGURE 1**: Small-Signal Transient Response,  $Z_1 = 2k\Omega ||75pF$

**FIGURE 2:** Large-Signal Transient Response,  $Z_1 = 2k\Omega ||75pF$

As with most JFET-input amplifiers, the output of the SSM-2131 may undergo phase inversion if either input exceeds the specified input voltage range. Phase inversion will not damage the amplifier, nor will it cause an internal latch-up.

Supply decoupling should be used to overcome inductance and resistance associated with supply lines to the amplifier.

For most applications, a  $0.1\mu F$  to  $0.01\mu F$  capacitor should be placed between each supply pin and ground.

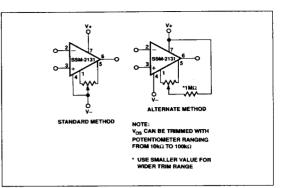

#### OFFSET VOLTAGE ADJUSTMENT

Offset voltage is adjusted with a  $10k\Omega$  to  $100k\Omega$  potentiometer as shown in Figure 3. The potentiometer should be connected between pins 1 and 5 with its wiper connected to the V– supply.

Alternately,  $V_{OS}$  may be nulled by attaching the potentiometer wiper through a 1M $\Omega$  resistor to the positive supply rail.

FIGURE 3: Input Offset Voltage Nulling

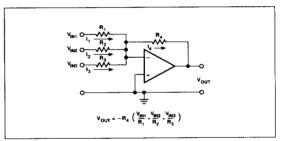

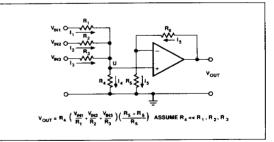

#### **VOLTAGE SUMMING**

Because of its extremely low input bias current and large unitygain bandwidth, the SSM-2131 is ideal for use as a voltage summer or adder.

The following figures show both an inverting and noninverting voltage adder.

FIGURE 4: Inverting Adder

FIGURE 5: Noninverting Adder

2-320 OPERATIONAL AMPLIFIERS

2

#### CURRENT FEEDBACK

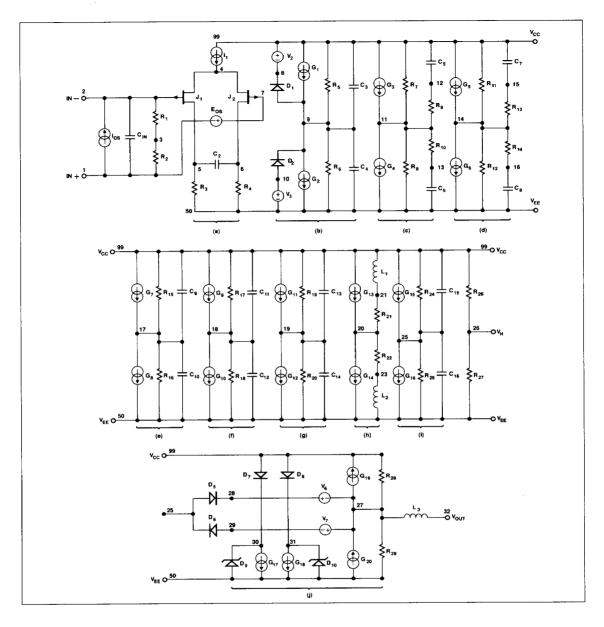

#### AUDIO POWER AMPLIFIER

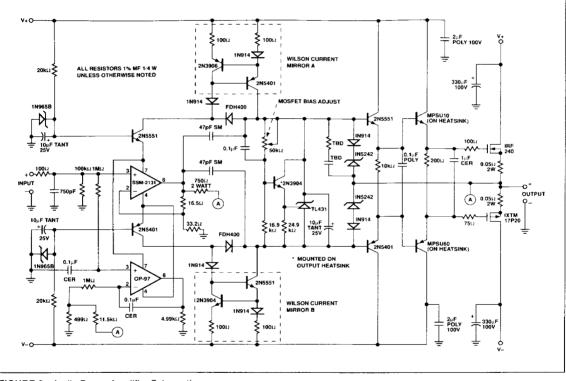

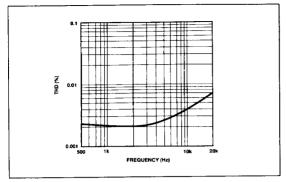

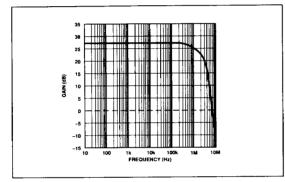

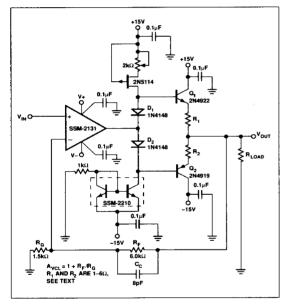

The SSM-2131 can be used as the input buffer in a current feedback audio power amplifier as shown in Figure 6. This design is capable of very good performance as shown in Figures 7, 8 and 9. At 1kHz and 50 watts output into an 8 $\Omega$  load, the amplifier generates just 0.002% THD, and is flat to 1MHz. The slew rate for the overall amplifier is more than adequate at 300V/µs and is responsible for the very low dynamic intermodulation distortion (DIM-100) that was measured at just 0.0017% at 50 watts output into 8 ohms. The total amplifier idling current for all tests was approximately 300mA; the V+/V++ and V-/V-- power supplies were both ±40V; and the gain was set to 24.0.

In a current feedback amplifier, a unity or low gain input buffer drives a low impedance network. Any differential current that flows in the collectors of the buffer (SSM-2131) output transistors is fed, via the two complementary Wilson current mirrors A and B, to a high impedance gain node where the high output voltage is generated.

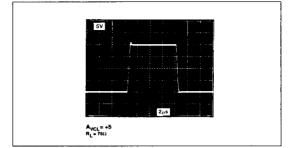

This voltage is then buffered by a double emitter follower driver stage and fed to the complementary power MOSFET output stage. No RC compensation network to ground or output inductor is required at the output of this amplifier to make it stable. As the 100kHz square wave response shows, there's no evidence of any instability in the circuit. Capacitive load compensation can be provided by the components marked TBD on the amplifier schematic. These were not used in the test, however.

FIGURE 6: Audio Power Amplifier Schematic

REV. A

FIGURE 7: THD vs. Frequency (at 50W into  $8\Omega$ ).

FIGURE 8: Frequency Response

FIGURE 9: 100kHz Square Wave into  $8\Omega$ .

One problem that is commonly encountered with current feedback amplifiers is that the mismatch between the two current mirrors A and B forces a small bias current to appear at the input buffer's output terminal. This bias current (usually in the range of 1-100 $\mu$ A) is multiplied by the feedback resistor of 750 $\Omega$  and generates an output offset that could be tens of millivolts in magnitude. Matched transistors could be used in the current mirrors, but these do not completely eliminate the output offset problem.

An inexpensive solution is to use a low power precision DC op amp, such as the OP-97, to control the amplifier's DC characteristics, thus overriding the DC offset due to mismatch in the current feedback loop. The OP-97 acts as a current output DC-servo amplifier that injects a compensating current into the emitters of the low voltage regulator transistors (that power the SSM-2131) to correct for current mirror mismatch. Since the OP-97 is set for an overall input-to-output gain of 24.0 as well, the DC output offset is equal to the OP-97's VOS x 24.0, which is roughly 1 millivolt. Thus, any offset trimming can be completely eliminated. Together, the SSM-2131 and OP-97 provide a level of performance that exceeds most of the requirements for audio power amplifers. The driver circuit can handle several pairs of power MOSFETs in the output stage if required. This topology can be used in circuits that must deliver several hundreds of watts to a load by using higher voltage transistors in the driver stage. Operation with rail voltages in excess of ±100V is possible. If more gain is desired, the SSM-2131 input buffer can have its gain increased from the nominal value of 1.5 used in this example to as much as 10 before its bandwidth drops below that of the current feedback section.

#### **DRIVING A HIGH-SPEED ADC**

The SSM-2131's open-loop output resistance is approximately 500. When feedback is applied around the amplifier, output resistance decreases in proportion to closed-loop gain divided by open-loop gain ( $A_{VCL}/A_{VOL}$ ). Output impedance increases as open-loop gain rols-off with frequency. High-speed analog-to-digital converters require low source impedances at high frequency. Output impedance at 1MHz is typically 507 or an SSM-2131 operating at unity-gain. If lower output impedances are required, an output buffer may be placed at the output of the SSM-2131.

2

#### **HIGH-CURRENT OUTPUT BUFFER**

The circuit in Figure 10 shows a high-current output stage for the SSM-2131 capable of driving a 75 $\Omega$  load with low distortion. Output current is limited by R<sub>1</sub> and R<sub>2</sub>. For good tracking between the output transistors Q<sub>1</sub>, Q<sub>2</sub>, and this biasing diodes D<sub>1</sub> and D<sub>2</sub>, thermal contact must be maintained between the transistor and its associated diode. If good thermal contact is not maintained, R<sub>1</sub> and R<sub>2</sub> must be increased to 5-6 $\Omega$  in order to prevent thermal runaway. Using 5 $\Omega$  resistors, the circuit easily drives a 75 $\Omega$  load (Figure 11). Output resistance is decreased and heavier loads may be driven by decreasing R<sub>1</sub> and R<sub>2</sub>.

Base current and biasing for Q<sub>1</sub> and Q<sub>2</sub> are provided by two current sources, the SSM-2131 and the JFET. The 2kQ potentiometer in the JFET current source should be trimmed for optimum transient performance. The case of the SSM-2210 should be connected to V–, and decoupled to ground with a 0.1µF capacitor. Compensation for the SSM-2131's input capacitance is provided by C<sub>C</sub>. The circuit may be operated at any gain, in the usual op amp configurations.

FIGURE 10: High-Current Output Buffer

#### DRIVING CAPACITIVE LOADS

Best performance will always be achieved by minimizing input and load capacitances around any high-speed amplifier. However, the SSM-2131 is guaranteed capable of driving a 100pF capacitive load over its full operating temperature range while

FIGURE 11: Output Buffer Large-Signal Response

operating at any gain including unity. Typically, an SSM-2131 will drive more than 250pF at any temperature. Supply decoupling does affect capacitive load driving ability. Extra care should be given to ensure good decoupling when driving capacitive loads; between 1 $\mu$ F and 10 $\mu$ F should be placed on each supply rail.

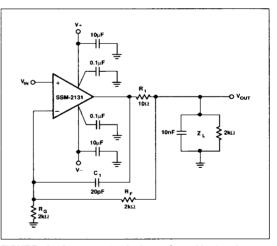

Large capacitive loads may be driven utilizing the circuit shown in Figure 12.  $R_1$  and  $C_1$  introduce a small amount of feedforward compensation around the amplifier to counteract the phase lag induced by the ouput impedance and load capacitance. At DC and low frequencies,  $R_1$  is contained within the feedback loop. At higher frequencies, feedforward compensation becomes increasingly dominant, and  $R_1$ 's effect on output impedance will become more noticeable.

FIGURE 12: Compensation for Large Capacitive Loads

REV. A

When driving very large capacitances, slew rate will be limited by the short-circuit current limit. Although the unloaded slew rate is insensitive to variations in temperature, the output current limit has a negative temperature coefficient, and is asymmetrical with regards to sourcing and sinking current. Therefore, slew rate into excessive capacities will decrease with increasing temperature, and will lose symmetry.

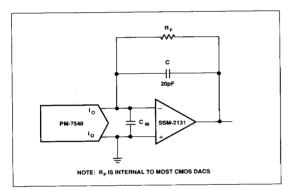

#### DAC OUTPUT AMPLIFIER

The SSM-2131 is an excellent choice for a DAC output amplifier, since its high speed and fast settling-time allow quick transitions between codes, even for full-scale changes in output level. The DAC output capacitance appears at the operational amplifier inputs, and must be compensated to ensure optimal settling speed. Compensation is achieved with capacitor C in Figure 13. C must be adjusted to account for the DAC's output capacitance, the op amp's input capacitance, and any stray capacitance at the inputs. With a bipolar DAC, an additional shunt resistor may be used to optimize response. This technique is described in PMI's application AN-24.

FIGURE 13: DAC Output Amplifier Circuit

Highest speed is achieved using bipolar DACs such as PMI's DAC-08, DAC-10 or DAC-312. The output capacitances of these converters are up to an order of magnitude lower than their CMOS counterparts, resulting in substantially faster settling-times. The high output impedance of bipolar DACs allows the output amplifier to operate in a true current-to-voltage mode, with a noise gain of unity, thereby retaining the amplifier's full bandwidth. Offset voltage has minimal effect on linearity with bipolar converters.

CMOS digital-to-analog converters have higher output capacitances and lower output resistances than bipolar DACs. This results in slower settling-times, higher sensitivity to offset voltages and a reduction in the output amplifier's bandwidth. These tradeoffs must be balanced against the CMOS DAC's advantages in terms of interfacing capability, power dissipation, accuracy levels and cost. Using the internal feedback resistor which is present on most CMOS converters, the gain applied to offset voltage varies between 4/3 and 2, depending upon output code. Contributions to linearity error will be as much as 2/3  $\rm V_{OS}$ . In a 10-volt 12-bit system, this may add up to an additional 1/5LSB DNL with

the SSM-2131. Amplifier bandwidth is reduced by the same gain factor applied to offset voltage, however the SSM-2131's 10MHz gain-bandwidth product results in no reduction of the CMOS converter's multiplying bandwidth.

Individual DAC data sheets should be consulted for more complete descriptions of the converters and their circuit applications.

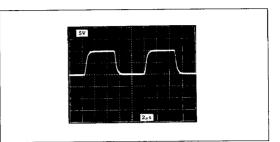

FIGURE 14: DAC Output Amplifier Response (PM-7545 DAC)

#### COMPUTER SIMULATIONS

The following pages show the SPICE macro-model for the SSM-2131 high-speed audio operational amplifier. This model was tested with, and is compatible with PSpice\* and HSPICE\*\*. The schematic and net-list are included here so that the model can easily be used. This model can accommodate multiple frequency poles and multiple zeroes, which is an advanced concept that results in more accurate AC and transient responses necessary for simulating the behavior of today's high-speed op amps. For example, 8 poles and 2 zeroes are required to sufficiently simulate the SSM-2131, which this advanced model can easily accommodate.

Throughout the SSM-2131 macro-model, RC networks produce the multiple poles and zeroes which simulate the SSM-2131's AC behavior. Each stage contains a pole or a pole-zero pair. The stages are separated from each other by voltage-controlled current sources so that the poles and zero locations do not interact. The only nonlinear elements in the entire model are two p-channel JFETs which comprise the input stage. Limiting the model to almost entirely linear circuit elements significantly reduces simulation time and simplifies model development.

\*PSpice is a registered trademark of MicroSim Corporation. \*\*HSPICE is a tradmark of Meta-Software, Inc.

2-324 OPERATIONAL AMPLIFIERS

REV. A

SSM-2131 MACRO-MODEL © PMI 1989 subckt SSM-2131 1 2 32 99 50 r17 18 99 r18 18 50 <u>9</u>9 \* INPUT STAGE & POLE AT 15.9 MHz c11 18 50 18 c12 18 99 g9 r1 1 3 3 5E11 99 99 910 18 2 5E11 50 r2 50 707.36 r3 5 r4 6 50 707.36 ī ž 5E-12 cin c2 5 6 7.08E-12 r19 19 99 50 r20 19 i1 99 4 1E-3 c13 19 99 2 4E-12 ios 1 c14 19 50 poly(1) 20 26 1E-3 1 7 1 eos g11 99 19 j1 j2 5 27 4 ix ğ12 19 50 6 4 jx \* SECOND STAGE & POLE AT 45 Hz . r21 20 r22 20 l1 21 l2 23 21 23 r5 9 99 176.84E6 r6 9 50 176.84E6 99 20E-12 poly(1) 5 6 3.96E-3 1.4137E-3 poly(1) 6 5 3.96E-3 1.4137E-3 2.5 3.1 c3 9 99 20E-12 50 20 g13 99 g14 20 c4 9 50 ğ g1 g2 v2 **9**9 50 ğ 50 **9**9 8 50 v3 10 dĺ 9 8 dx r24 25 r25 25 10 ğ 99 50 d2 dx c15 25 **9**9 \* POLE-ZERO PAIR AT 1.80 MHz/2.20 MHz c16 25 g15 99 50 25 r7 11 99 1E6 ğ16 25 50 r8 11 50 12 1E6 4.5E6 r9 11 r10 13 4.5E6 11 99 16.1E-15 c5 12 r26 26 r27 26 r28 27 r29 27 l3 27 99 c6 13 50 16.1E-15 50 g3 g4 9 26 1E-6 26 9 1E-6 99 11 99 11 50 50 32 \* POLE-ZERO PAIR AT 1.80 MHz/2.20 MHz g17 30 g18 31 g19 27 50 30 31 27 50 28 27 50 r11 14 99 1E6 99 27 27 29 r12 14 50 1E6 ğ20 4.5E6 4.5E6 15 r13 14 v6 v7 r14 c7 14 16 15 99 16.1E-15 25 29 d5 28 č8 16 **5**0 16.1E-15 đõ 25 g5 g6 99 14 11 26 1E-6 99 d7 30 14 50 26 11 1E-6 d8 99 31 50 30 \* POLE AT 53 MHz d9 ā10 50 31 r15 17 99 1E6 17 17 r16 50 1E6 3E-15 3E-15 c9 99 c9 17 c10 17 g7 99 g8 17 50 17 14 26 1E-6 26 14 1E-6 50

\* POLE AT 53 MHz 1E6 1E6 3E-15 3E-15 3E-15 17 26 1E-6 26 17 1E-6 \* POLE AT 53 MHz 1E6 1E6 3E-15 3E-15 18 26 1E-6 26 18 1E-6 \*COMMON-MODE GAIN NETWORK WITH ZERO AT 100 kHZ 1E6 1E6 1.5915 1.5915 3 26 1E-11 26 3 1E-11 \*POLE AT 79.6 MHz 1E6 1E6 2E-15 2E-15 19 26 1E-6 26 19 1E-6 **\*OUTPUT STAGE** 111.1E3 111.1E3 90 90 90 2.5E-7 25 27 11.1111E-3 27 25 11.1111E-3 99 25 11.1111E-3 25 50 11.1111E-3 0.7 0.7 dx dx dx dx dy dý \* MODELS USED  $\begin{array}{ll} \mbox{-model jx PJF(BETA=999.3E-6 VTO=-2.000 IS=4E-11)} \\ \mbox{-model dx} & D(IS=1E-15) \\ \mbox{-model dy} & D(IS=1E-15 BV=50) \end{array}$ •model dy D(IS •ends SSM-2131

REV. A

REV. A