NOT RECOMMENDED FOR NEW DESIGNS Please See LTC2978A for Drop-In Replacement

# FEATURES

- I<sup>2</sup>C/SMBus Serial Interface

- PMBus Compliant Command Set

- Configuration EEPROM with CRC

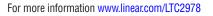

- Black Box Fault Logging to Internal EEPROM

- Differential Input, 16-Bit  $\Delta \Sigma$  ADC with Less Than ±0.25% of Total Unadjusted Error

- Eight Voltage Servos Precisely Adjust Output Voltages Using Eight 10-Bit DACs with Soft-Connect

- Monitors Eight Output Voltages and One Input Voltage and Internal Die Temperature

- 8-Channel Sequencer

- Programmable Watchdog Timer

- Eight UV/OV V<sub>OUT</sub> and One V<sub>IN</sub> Supervisor

- Supports Multi-Channel Fault Management

- Operates Autonomously without Additional Software

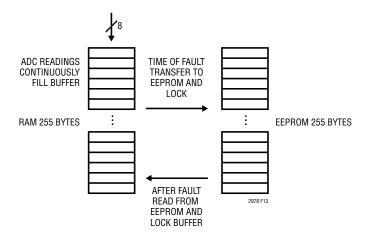

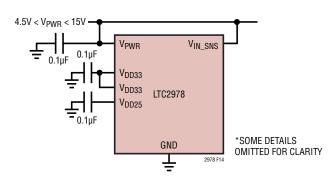

- LTC2978 Can Be Powered from 3.3V or 4.5V to 15V

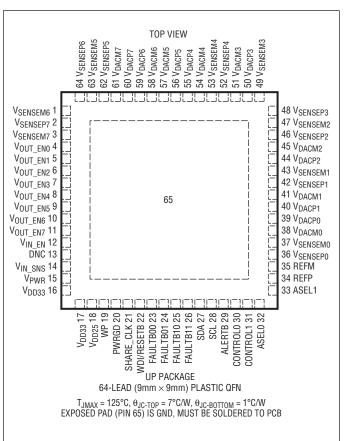

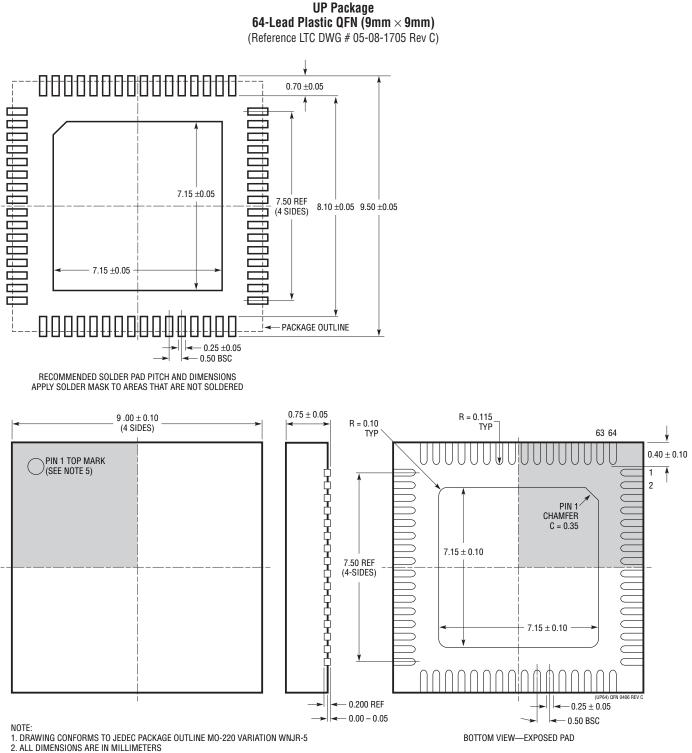

- Available in 64-pin 9mm × 9mm QFN Package

# **APPLICATIONS**

- Computers

- Network Servers

- Industrial Test and Measurement

- High Reliability Systems

- Medical Imaging

- Video

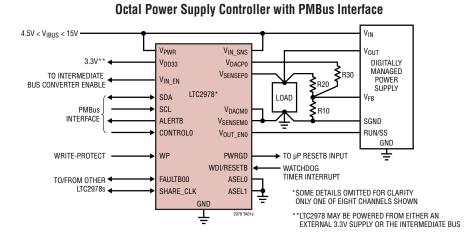

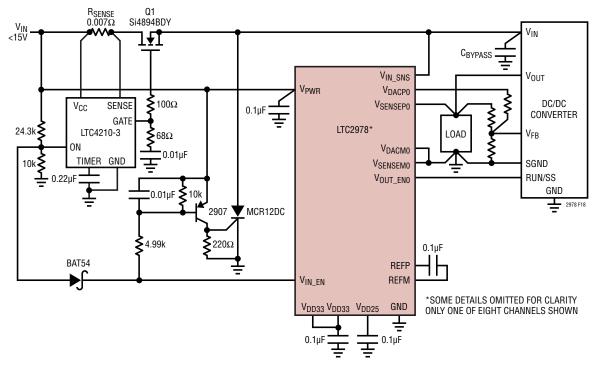

# TYPICAL APPLICATION

# Octal Digital Power Supply Manager with EEPROM

LTC2978

# DESCRIPTION

The LTC<sup>®</sup>2978 is an octal, digital power-supply monitor, supervisor, sequencer, and margin controller. Eight output channels can be managed per user defined configuration settings. Supervisory functions include fault OV/UV threshold limits for eight output channels and one input channel. Programmable fault dependencies and responses allow the power supplies to be disabled with optional retry after a fault has been detected. Serial bus telemetry allows eight output voltages, one input voltage, die temperature and fault status to be monitored. In addition, odd numbered channels can be configured to measure the voltage across a current sense resistor. Power supply sequencing, precision point-of-load voltage adjustment and margining are supported with PMBus commands. A programmable watchdog timer monitors microprocessor activity for a stalled condition and resets the microprocessor if necessary. The 1-wire synchronization bus supports power supply sequencing across multiple LTC digital power devices. User programmable parameters can be stored in EEPROM. Faults and telemetry data can be logged to EEPROM for diagnostic analysis.

**Δ7**, LT, LTC, LTM, PolyPhase, Linear Technology and the Linear logo are registered trademarks and LTpowerPlay ia a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents including 7382303 and 7420359.

# TABLE OF CONTENTS

| Features                              | 1   |

|---------------------------------------|-----|

| Applications                          | 1   |

| Typical Application                   | 1   |

| Description                           |     |

| Absolute Maximum Ratings              |     |

| Order Information                     |     |

| Pin Configuration                     |     |

| Electrical Characteristics            |     |

| PMBus Timing Diagram                  |     |

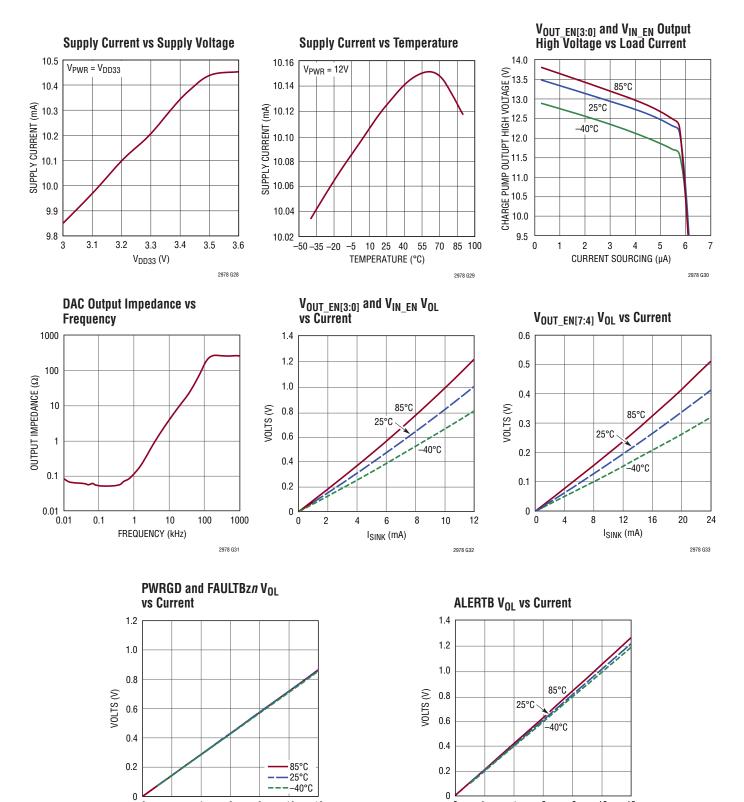

| Typical Performance Characteristics   |     |

| Pin Functions                         |     |

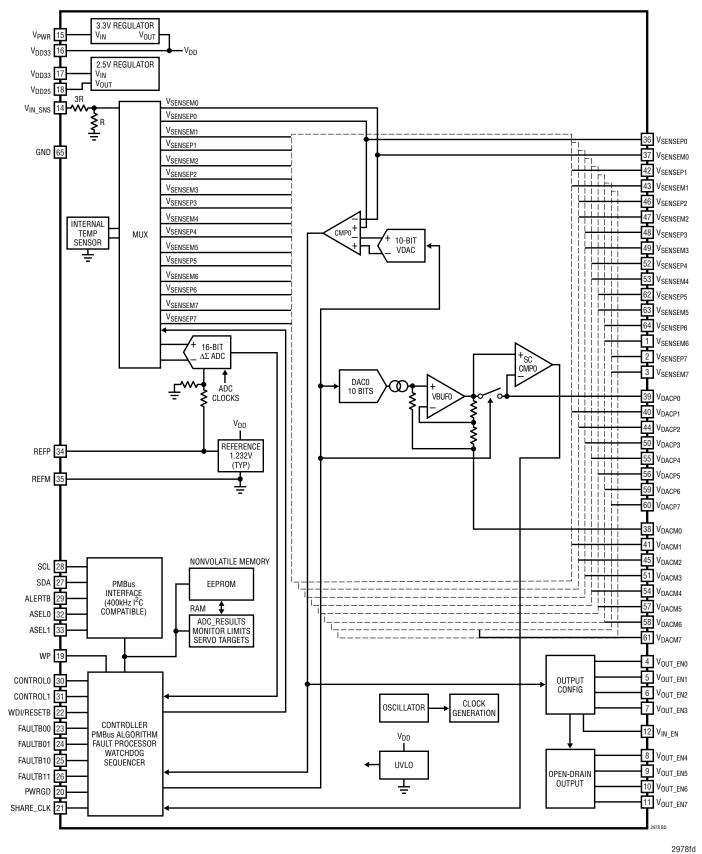

| Block Diagram                         |     |

| Operation                             |     |

| Operation Overview                    |     |

| EEPROM                                |     |

| Reset                                 |     |

| Write-Protect Pin                     |     |

|                                       |     |

| Other Operations                      |     |

| Clock Sharing                         |     |

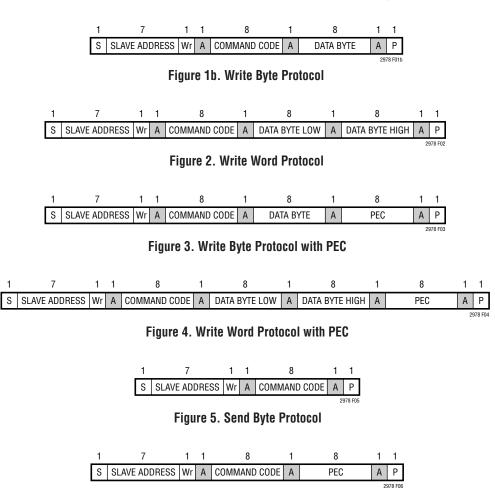

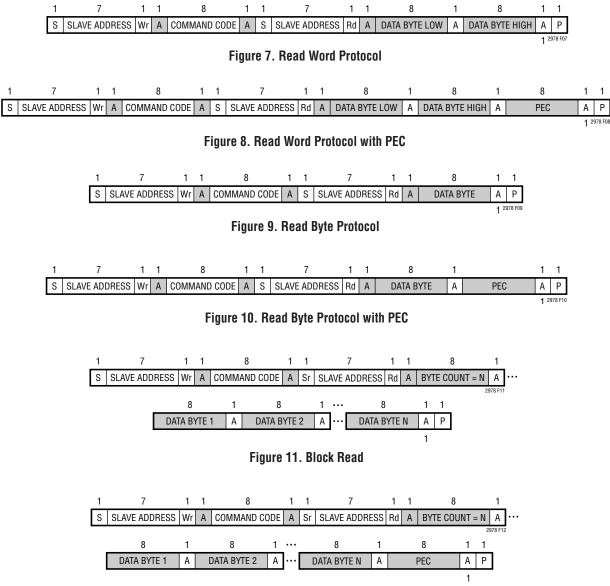

| PMBus Serial Digital Interface        |     |

| PMBus                                 |     |

| Device Address                        |     |

| Processing Commands                   |     |

| PMBus Command Summary                 |     |

| Summary Table                         |     |

| Data Formats                          |     |

| PMBus Command Description             |     |

| Operation, Mode and EEPROM Commands   |     |

| PAGE                                  |     |

| OPERATION                             |     |

| ON_OFF_CONFIG                         |     |

| CLEAR_FAULTS                          |     |

| WRITE_PROTECT                         |     |

| STORE_USER_ALL and RESTORE_USER_ALL   |     |

| CAPABILITY                            |     |

| VOUT_MODE                             |     |

| Output Voltage Related Commands       |     |

| VOUT_COMMAND, VOUT_MAX, VOUT_MARGI    |     |

| HIGH, VOUT_MARGIN_LOW, VOUT_OV_FAULT_ | _   |

| LIMIT, VOUT_OV_WARN_LIMIT, VOUT_UV_   |     |

| WARN_LIMIT, VOUT_UV_FAULT_LIMIT, POWE |     |

| GOOD_ON and POWER_GOOD_OFF            | .33 |

| Input Voltage Related Commands                   | 33  |

|--------------------------------------------------|-----|

| VIN_ON, VIN_OFF, VIN_OV_FAULT_LIMIT, VIN_        |     |

| OV_WARN_LIMIT, VIN_UV_WARN_LIMIT and             |     |

| VIN_UV_FAULT_LIMIT                               | 33  |

| Temperature Related Commands                     |     |

| OT_FAULT_LIMIT, OT_WARN_LIMIT, UT_WARN           |     |

| LIMIT and UT_FAULT_LIMIT                         |     |

| Timer Limits                                     |     |

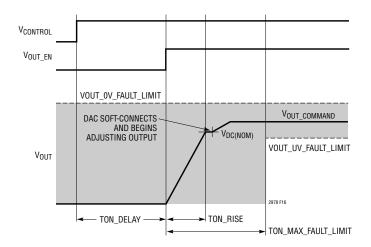

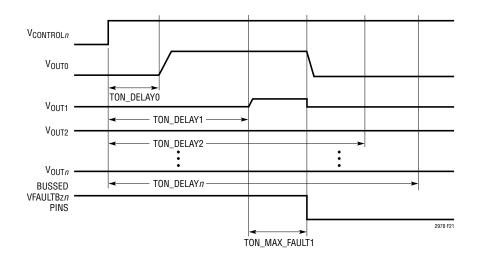

| TON_DELAY, TON_RISE, TON_MAX_FAULT_              | 94  |

| LIMIT and TOFF_DELAY                             | 3/1 |

| Fault Response for Voltages Measured by the High |     |

| Speed Supervisor                                 |     |

| VOUT_OV_FAULT_RESPONSE and VOUT_UV_              | 00  |

| FAULT_RESPONSE                                   | 35  |

| Fault Response for Values Measured by the ADC    |     |

| OT_FAULT_RESPONSE, UT_FAULT_RESPONSE,            |     |

| VIN_OV_FAULT_RESPONSE and VIN_UV_FAULT           |     |

| RESPONSE                                         |     |

| Timed Fault Response                             |     |

| TON_MAX_FAULT_RESPONSE                           | 36  |

| Status Commands                                  | 37  |

| STATUS_BYTE:                                     |     |

| STATUS_WORD:                                     |     |

| STATUS_VOUT                                      |     |

| STATUS_INPUT                                     |     |

| STATUS_TEMPERATURE                               |     |

| STATUS_CML                                       | 40  |

| STATUS_MFR_SPECIFIC                              |     |

| ADC Monitoring Commands                          | 41  |

| READ_VIN                                         | 41  |

| READ_VOUT                                        |     |

| READ_TEMPERATURE_1                               | 41  |

| PMBUS_REVISION                                   | 41  |

| Manufacturer Specific Commands                   |     |

| MFR_CONFIG_LTC2978                               | 42  |

| MFR_CONFIG_ALL_LTC2978                           | 43  |

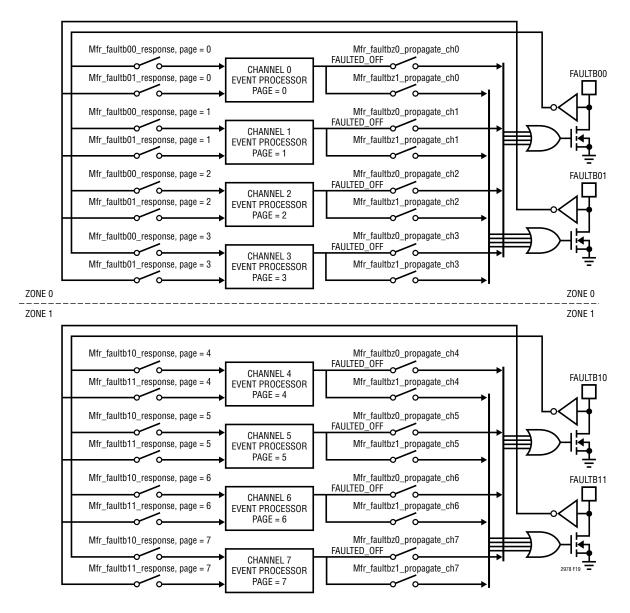

| MFR_FAULTz0_PROPAGATE, MFR_FAULTz1_              |     |

| PROPAGATE                                        |     |

| MFR_PWRGD_EN                                     |     |

| MFR_FAULTB00_RESPONSE, MFR_FAULTB01_             |     |

| RESPONSE, MFR_FAULTB10_RESPONSE and              |     |

| MFR_FAULTB11_RESPONSE                            | 46  |

# TABLE OF CONTENTS

| MFR_VINEN_OV_FAULT_RESPONSE                      | 47   |

|--------------------------------------------------|------|

| MFR_VINEN_UV_FAULT_RESPONSE                      |      |

| MFR RETRY DELAY                                  |      |

| MFR RESTART DELAY                                |      |

| MFR_VOUT_PEAK                                    |      |

| MFR VIN PEAK                                     |      |

| MFR_TEMPERATURE_PEAK                             |      |

| MFR_DAC                                          |      |

| MFR_POWERGOOD_ASSERTION_DELAY                    |      |

| Watchdog Operation                               |      |

| MFR_WATCHDOG_T_FIRST and MFR_                    |      |

| WATCHDOG_T                                       | 50   |

| MFR PAGE FF MASK                                 |      |

| MFR_PADS                                         | . 52 |

| MFR_I2C_BASE_ADDRESS                             | . 52 |

| MFR_SPECIAL_ID                                   |      |

| MFR_SPECIAL_LOT                                  | . 53 |

| MFR_VOUT_DISCHARGE_THRESHOLD                     | . 53 |

| MFR_COMMON                                       |      |

| MFR_SPARE0                                       | . 53 |

| MFR_SPARE2                                       | . 53 |

| MFR_VOUT_MIN                                     | .54  |

| MFR_VIN_MIN                                      | 54   |

| MFR_TEMPERATURE_MIN                              | .54  |

| Fault Log Operation                              |      |

| MFR_FAULT_LOG_STORE                              |      |

| MFR_FAULT_LOG_RESTORE                            | . 55 |

| MFR_FAULT_LOG_CLEAR                              | . 55 |

| MFR_FAULT_LOG_STATUS                             | . 55 |

| MFR_FAULT_LOG                                    |      |

| Applications Information                         |      |

| Overview                                         | . 62 |

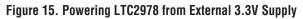

| Powering the LTC2978                             |      |

| Setting Command Register Values                  |      |

| Sequence, Servo, Margin and Restart Operations . | . 62 |

| Command Units On or Off                          |      |

| On Sequencing                                    |      |

| On State Operation                               |      |

| Servo Modes                                      |      |

| DAC Modes                                        |      |

| Margining                                        | .64  |

| 0110                                                       | ~ 4  |

|------------------------------------------------------------|------|

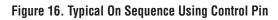

| Off Sequencing                                             |      |

| V <sub>OUT</sub> Off Threshold Voltage                     | .64  |

| Automatic Restart Via MFR_RESTART_DELAY                    | ~ 4  |

| Command and CONTROLn pin                                   |      |

| Fault Management                                           |      |

| Output Overvoltage and Undervoltage Faults                 |      |

| Output Overvoltage and Undervoltage Warnings               |      |

| Configuring the V <sub>IN_EN</sub> Output                  |      |

| Multichannel Fault Management                              |      |

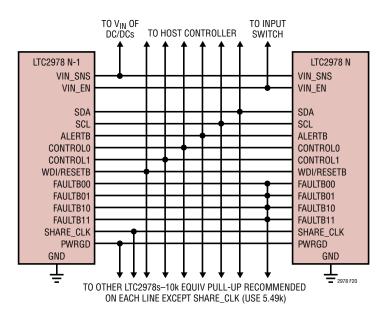

| Interconnect Between Multiple LTC2978's                    |      |

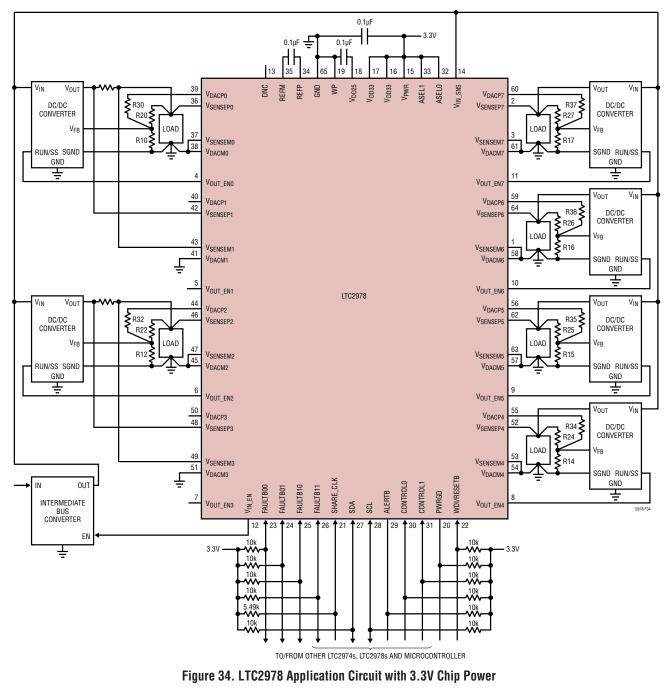

| Application Circuits                                       |      |

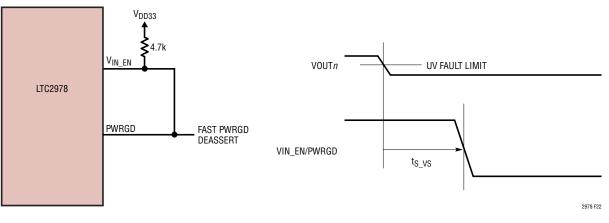

| Trimming and Margining DC/DC Converters wit                |      |

| External Feedback Resistors                                |      |

| Four-Step Resistor Selection Procedure for DC/             |      |

| Converters with External Feedback Resistors                |      |

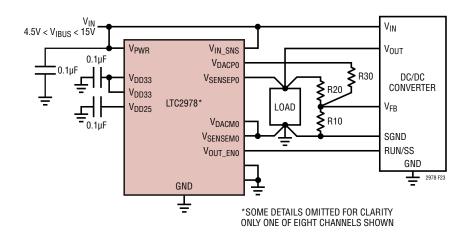

| Trimming and Margining DC/DC Converters wit                |      |

| TRIM Pin                                                   | .70  |

| Two-Step Resistor and DAC Full-Scale Voltage               |      |

| Selection Procedure for DC/DC Converters with              |      |

| TRIM Pin                                                   |      |

| Measuring Current                                          |      |

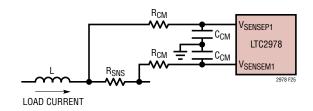

| Measuring Current with a Sense Resistor                    |      |

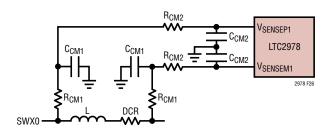

| Measuring Current with Inductor DCR                        |      |

| Single Phase Design Example                                |      |

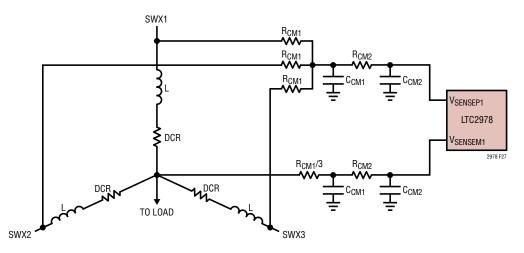

| Measuring Multiphase Currents                              |      |

| Multiphase Design Example                                  |      |

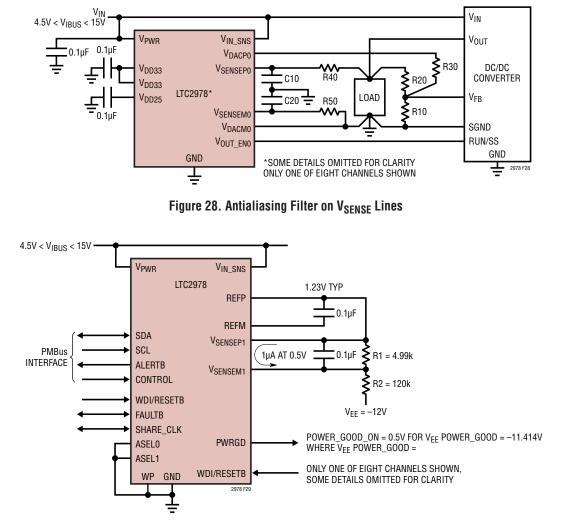

| Anti-aliasing Filter Considerations                        |      |

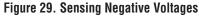

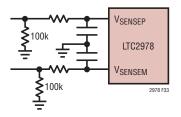

| Sensing Negative Voltages                                  |      |

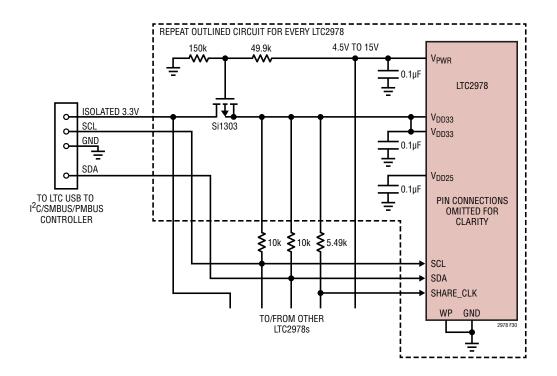

| Connecting the USB to I <sup>2</sup> C/SMBus/PMBus Control |      |

| to the LTC2978 in System                                   |      |

| LTpowerPlay: An Interactive GUI for Digital Power          |      |

| PCB Assembly and Layout Suggestions                        |      |

| Bypass Capacitor Placement                                 |      |

| Exposed Pad Stencil Design                                 |      |

| PC Board Layout                                            | .//  |

| Unused ADC Sense Inputs                                    |      |

| Package Description                                        |      |

| Revision History                                           |      |

| Typical Application                                        |      |

| Related Parts                                              | . XU |

# ABSOLUTE MAXIMUM RATINGS

#### (Notes 1, 2) Supply Voltages:

| Supply Voltages:                               |

|------------------------------------------------|

| V <sub>PWR</sub> to GND0.3V to 15V             |

| $V_{IN\_SNS}$ to GND                           |

| V <sub>DD33</sub> to GND–0.3V to 3.6V          |

| V <sub>DD25</sub> to GND                       |

| Digital Input/Output Voltages:                 |

| ALERTB, SDA, SCL, CONTROLO,                    |

|                                                |

| CONTROL1                                       |

| PWRGD, SHARE_CLK,                              |

| WDI/RESETB, WP0.3V to V <sub>DD33</sub> + 0.3V |

| FAULTB00, FAULTB01, FAULTB10,                  |

| FAULTB11–0.3V to V <sub>DD33</sub> + 0.3V      |

| ASEL0, ASEL1–0.3V to V <sub>DD33</sub> + 0.3V  |

| Analog Voltages:                               |

| REFP0.3V to 1.35V                              |

| REFM to GND0.3V to 0.3V                        |

| V <sub>SENSEP[7:0]</sub> to GND0.3V to 6V      |

| V <sub>SENSEM[7:0]</sub> to GND–0.3V to 6V     |

| $V_{OUT\_EN[3:0]}$ , $V_{IN\_EN}$ to GND       |

| $V_{OUT_{EN[7:4]}}$ to GND0.3V to 6V           |

| V <sub>DACP[7:0]</sub> to GND                  |

|                                                |

| V <sub>DACM[7:0]</sub> to GND0.3V to 0.3V      |

| Operating Junction Temperature Range:          |

| LTC2978C                                       |

| LTC2978I–40°C to 85°C                          |

| Storage Temperature Range                      |

# PIN CONFIGURATION

# **ORDER INFORMATION**

| LEAD FREE FINISH | TAPE AND REEL    | PART MARKING* | PACKAGE DESCRIPTION                   | TEMPERATURE RANGE JUNCTION |

|------------------|------------------|---------------|---------------------------------------|----------------------------|

| LTC2978CUP#PBF   | LTC2978CUP#TRPBF | LTC2978UP     | 64-Lead (9mm $	imes$ 9mm) Plastic QFN | 0°C to 70°C                |

| LTC2978IUP#PBF   | LTC2978IUP#TRPBF | LTC2978UP     | 64-Lead (9mm × 9mm) Plastic QFN       | -40°C to 85°C              |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_J = 25$ °C.  $V_{PWR} = V_{IN\_SNS} = 12V$ ,  $V_{DD33}$ ,  $V_{DD25}$ , REFP and REFM pins floating, unless otherwise indicated.  $C_{VDD33} = 100$ nF,  $C_{VDD25} = 100$ nF and  $C_{REF} = 100$ nF.

| SYMBOL                  | PARAMETER CONDITIONS                                     |                                                                                                                                                                                                                          | MIN | ТҮР  | MAX                                   | UNITS |                                                |

|-------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|---------------------------------------|-------|------------------------------------------------|

| Power-Supply            | Characteristics                                          |                                                                                                                                                                                                                          |     |      |                                       |       |                                                |

| V <sub>PWR</sub>        | V <sub>PWR</sub> Supply Input Operating Range            |                                                                                                                                                                                                                          |     | 4.5  |                                       | 15    | V                                              |

| I <sub>PWR</sub>        | V <sub>PWR</sub> Supply Current                          | $4.5V \le V_{PWR} \le 15V, V_{DD33}$ Floating                                                                                                                                                                            | •   |      | 10                                    | 13    | mA                                             |

| I <sub>VDD33</sub>      | V <sub>DD33</sub> Supply Current                         | $3.13V \le V_{DD33} \le 3.47V, V_{PWR} = V_{DD33}$                                                                                                                                                                       |     |      | 10                                    | 13    | mA                                             |

| V <sub>UVLO_VDD33</sub> | V <sub>DD33</sub> Undervoltage Lockout                   | V <sub>DD33</sub> Ramping Up, V <sub>PWR</sub> = V <sub>DD33</sub>                                                                                                                                                       |     | 2.35 | 2.55                                  | 2.8   | V                                              |

| _                       | V <sub>DD33</sub> Undervoltage Lockout<br>Hysteresis     |                                                                                                                                                                                                                          |     |      | 120                                   |       | mV                                             |

| V <sub>DD33</sub>       | Supply Input Operating Range                             | V <sub>PWR</sub> = V <sub>DD33</sub>                                                                                                                                                                                     |     | 3.13 |                                       | 3.47  | V                                              |

|                         | Regulator Output Voltage                                 | $4.5V \le V_{PWR} \le 15V$                                                                                                                                                                                               |     | 3.13 | 3.26                                  | 3.47  | V                                              |

|                         | Regulator Output Short-Circuit Current                   | V <sub>PWR</sub> = 4.5V, V <sub>DD33</sub> = 0V                                                                                                                                                                          |     | 75   | 90                                    | 140   | mA                                             |

| V <sub>DD25</sub>       | Regulator Output Voltage                                 | $3.13V \le V_{DD33} \le 3.47V$                                                                                                                                                                                           |     | 2.35 | 2.5                                   | 2.6   | V                                              |

|                         | Regulator Output Short-Circuit Current                   | V <sub>PWR</sub> = V <sub>DD33</sub> = 3.47V, V <sub>DD25</sub> = 0V                                                                                                                                                     |     | 30   | 55                                    | 80    | mA                                             |

| t <sub>INIT</sub>       | Initialization Time                                      | Time from V <sub>IN</sub> Applied Until the TON_DELAY Timer Starts                                                                                                                                                       |     | 135  |                                       |       | ms                                             |

| Voltage Refer           | ence Characteristics                                     |                                                                                                                                                                                                                          |     |      |                                       |       |                                                |

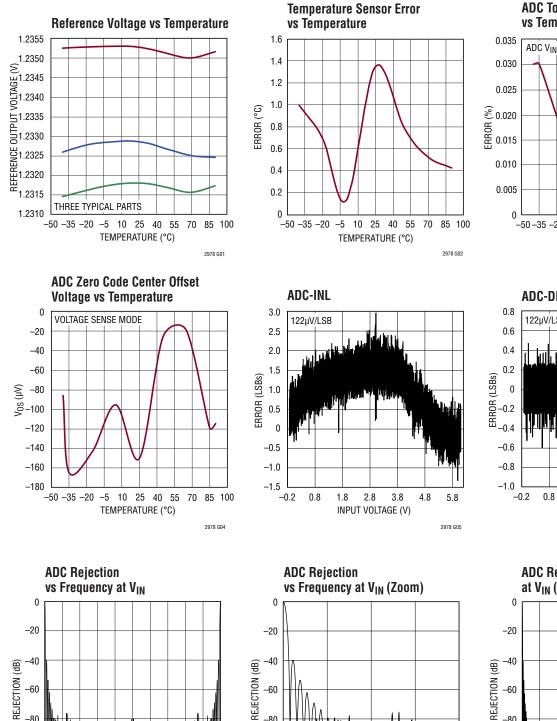

| V <sub>REF</sub>        | Output Voltage                                           |                                                                                                                                                                                                                          |     |      | 1.232                                 |       | V                                              |

|                         | Temperature Coefficient                                  |                                                                                                                                                                                                                          |     |      | 3                                     |       | ppm/°C                                         |

|                         | Hysteresis                                               | (Note 3)                                                                                                                                                                                                                 |     |      | 100                                   |       | ppm                                            |

| ADC Characte            | ristics                                                  |                                                                                                                                                                                                                          |     |      |                                       |       | <u> </u>                                       |

| VIN_ADC                 | Voltage Sense Input Range                                | Differential Voltage:<br>$V_{IN\_ADC} = (V_{SENSEPn} - V_{SENSEMn})$                                                                                                                                                     | •   | 0    |                                       | 6     | V                                              |

|                         |                                                          | Single-Ended Voltage: V <sub>SENSEMn</sub>                                                                                                                                                                               |     | -0.1 |                                       | 0.1   | V                                              |

|                         | Current Sense Input Range (Odd                           | Single-Ended Voltage: V <sub>SENSEPn</sub> , V <sub>SENSEMn</sub>                                                                                                                                                        | •   | -0.1 |                                       | 6     | V                                              |

|                         | Numbered Channels Only)                                  | Differential Voltage: V <sub>IN_ADC</sub>                                                                                                                                                                                |     | -170 |                                       | 170   | mV                                             |

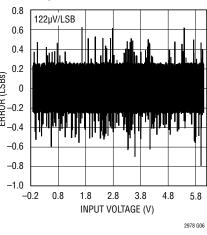

| N_ADC                   | Voltage Sense Resolution (Uses L16<br>Format)            | $0V \le V_{IN\_ADC} \le 6V$                                                                                                                                                                                              |     |      | 122                                   |       | μV/LSB                                         |

|                         | Current Sense Resolution (Odd<br>Numbered Channels Only) | $\begin{array}{l} 0mV \leq  V_{IN\_ADC}  < 16mV \mbox{ (Note13)} \\ 16mV \leq  V_{IN\_ADC}  < 32mV \\ 32mV \leq  V_{IN\_ADC}  < 63.9mV \\ 63.9mV \leq  V_{IN\_ADC}  < 127.9mV \\ 127.9mV \leq  V_{IN\_ADC}  \end{array}$ |     |      | 15.625<br>31.25<br>62.5<br>125<br>250 |       | μV/LSB<br>μV/LSB<br>μV/LSB<br>μV/LSB<br>μV/LSB |

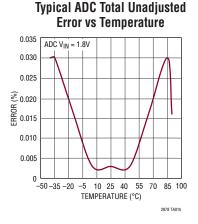

| TUE_ADC                 | Total Unadjusted Error                                   | $V_{IN\_ADC} \ge 1.8V$ (Note 4)                                                                                                                                                                                          |     |      |                                       | ±0.25 | %                                              |

| INL_ADC                 | Integral Nonlinearity                                    | Voltage Sense Mode (Note 5)                                                                                                                                                                                              |     |      |                                       | ±854  | μV                                             |

|                         |                                                          | Current Sense Mode, Odd Numbered<br>Channels Only, 15.6µV/LSB (Note 5)                                                                                                                                                   | •   |      |                                       | ±31.3 | μV                                             |

| DNL_ADC                 | Differential Nonlinearity                                | Voltage Sense Mode                                                                                                                                                                                                       |     |      |                                       | ±400  | μV                                             |

|                         |                                                          | Current Sense Mode, Odd Numbered<br>Channels Only                                                                                                                                                                        | •   |      |                                       | ±31.3 | μV                                             |

| V <sub>OS_ADC</sub>     | Offset Error                                             | Voltage Sense Mode                                                                                                                                                                                                       |     |      |                                       | ±250  | μV                                             |

| -                       |                                                          | Current Sense Mode, Odd Numbered<br>Channels Only                                                                                                                                                                        | •   |      |                                       | ±35   | μV                                             |

| GAIN_ADC                | Gain Error                                               | Voltage Sense Mode, V <sub>IN_ADC</sub> = 6V                                                                                                                                                                             |     |      |                                       | ±0.2  | %                                              |

|                         |                                                          | Current Sense Mode, Odd Numbered<br>Channels Only, V <sub>IN_ADC</sub> = ±0.17V                                                                                                                                          | •   |      |                                       | ±0.2  | %                                              |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_J = 25$ °C.  $V_{PWR} = V_{IN\_SNS} = 12V$ ;  $V_{DD33}$ ,  $V_{DD25}$ , REFP and REFM pins floating, unless otherwise indicated.  $C_{VDD33} = 100$ nF,  $C_{VDD25} = 100$ nF and  $C_{REF} = 100$ nF.

| SYMBOL                    | PARAMETER                                          | CONDITIONS                                                               |                                                |   | MIN          | ТҮР          | MAX          | UNITS  |

|---------------------------|----------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------|---|--------------|--------------|--------------|--------|

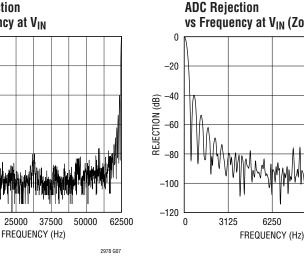

| t <sub>CONV_ADC</sub>     | Conversion Time                                    | Voltage Sense Mod                                                        | e (Note 6)                                     |   |              | 6.15         |              | ms     |

| -                         |                                                    | Current Sense Mode (Note 6)                                              |                                                |   |              | 24.6         |              | ms     |

|                           |                                                    | Temperature Input (Note 6)                                               |                                                |   |              | 24.6         |              | ms     |

| C <sub>IN_ADC</sub>       | Input Sampling Capacitance                         |                                                                          |                                                |   |              | 1            |              | pF     |

| f <sub>IN_ADC</sub>       | Input Sampling Frequency                           |                                                                          |                                                |   |              | 62.5         |              | kHz    |

|                           | Input Leakage Current                              | $V_{IN\_ADC} = 0V, 0V \le Current Sense Mod$                             | $V_{COMMONMODE} \le 6V,$                       | • |              |              | ±0.5         | μΑ     |

|                           | Differential Input Current                         | V <sub>IN_ADC</sub> = 0.17V, Cu                                          | Irrent Sense Mode                              |   |              | 80           | 250          | nA     |

|                           |                                                    | V <sub>IN ADC</sub> = 6V, Volta                                          | ge Sense Mode                                  |   |              | 10           | 15           | μA     |

| DAC Output C              | haracteristics                                     |                                                                          |                                                |   |              |              |              |        |

| N_V <sub>DACP</sub>       | Resolution                                         |                                                                          |                                                |   |              | 10           |              | Bits   |

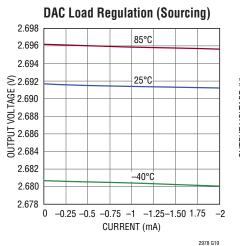

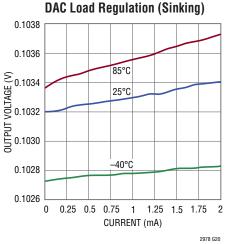

| V <sub>FS_VDACP</sub>     | Full-Scale Output Voltage<br>(Programmable)        | DAC Code = 0x3FF<br>DAC Polarity = 1                                     | Buffer Gain Setting_0<br>Buffer Gain Setting_1 | • | 1.32<br>2.53 | 1.38<br>2.65 | 1.44<br>2.77 | V<br>V |

| INL_V <sub>DACP</sub>     | Integral Nonlinearity                              | (Note 7)                                                                 |                                                |   |              |              | ±2           | LSB    |

| DNL_VDACP                 | Differential Nonlinearity                          | (Note 7)                                                                 |                                                |   |              |              | ±2.4         | LSB    |

| V <sub>OS_VDACP</sub>     | Offset Voltage                                     | (Note 7)                                                                 |                                                |   |              |              | ±10          | mV     |

|                           | Load Regulation $(V_{DACPn} - V_{DACMn})$          | V <sub>DACP</sub> = 2.65V, I <sub>VD</sub>                               | ACPn Sourcing = 2mA                            |   |              | 100          |              | ppm/mA |

|                           |                                                    | $V_{DACPn} = 0.1V$ , $I_{VDACPn}$ Sinking = 2mA                          |                                                |   |              | 100          |              | ppm/mA |

|                           | PSRR (V <sub>DACPn</sub> – V <sub>DACMn</sub> )    | DC: 3.13V ≤ V <sub>DD33</sub> :                                          | ≤ 3.47V, V <sub>PWR</sub> = V <sub>DD33</sub>  |   |              | 60           |              | dB     |

|                           |                                                    | 100mV Step in 20n                                                        | s with 50pF Load                               |   |              | 40           |              | dB     |

|                           | DC CMRR (V <sub>DACPn</sub> – V <sub>DACMn</sub> ) | $-0.1V \le V_{DACMn} \le 0$                                              | .1V                                            |   |              | 60           |              | dB     |

|                           | Leakage Current                                    | $V_{DACPn}$ Hi-Z, $0V \le V$                                             | $V_{DACPn} \le 6V$                             |   |              |              | ±100         | nA     |

|                           | Short-Circuit Current Low                          | V <sub>DACP</sub> Shorted to 0                                           | GND                                            |   | -10          |              | -4           | mA     |

|                           | Short-Circuit Current High                         | V <sub>DACP</sub> Shorted to V                                           | / <sub>DD33</sub>                              |   | 4            |              | 10           | mA     |

| C <sub>OUT</sub>          | Output Capacitance                                 | V <sub>DACP</sub> Hi-Z                                                   |                                                |   |              | 10           |              | pF     |

| ts_vdacp                  | DAC Output Update Rate                             | Fast Servo Mode                                                          |                                                |   |              | 250          |              | μs     |

| Voltage Supe              | rvisor Characteristics                             |                                                                          |                                                |   |              |              |              |        |

| V <sub>IN_VS</sub>        | Input Voltage Range (Programmable)                 | $V_{IN_VS} = (V_{SENSEPn} - V_{SENSEMn})$                                | Low Resolution Mode<br>High Resolution Mode    | • | 0<br>0       |              | 6<br>3.8     | V<br>V |

|                           |                                                    | Single-Ended Voltag                                                      | ge: V <sub>SENSEMn</sub>                       |   | -0.1         |              | 0.1          | V      |

| N_VS                      | Voltage Sensing Resolution                         | OV to 3.8V Range: H                                                      | ligh Resolution Mode                           |   |              | 4            |              | mV/LSB |

|                           |                                                    | OV to 6V Range: Lo                                                       | w Resolution Mode                              |   |              | 8            |              | mV/LSB |

| TUE_VS                    | Total Unadjusted Error                             | $2V \le V_{IN_VS} \le 6V, L$                                             | ow Resolution Mode                             |   |              |              | ±1.25        | %      |

|                           |                                                    | $\begin{array}{c} 1.5V < V_{IN\_VS} \leq 3.8 \\ \text{Mode} \end{array}$ | V, High Resolution                             | • |              |              | ±1.0         | %      |

|                           |                                                    | $0.8V \leq V_{IN\_VS} \leq 1.5$ Mode                                     | V, High Resolution                             | • |              |              | ±1.5         | %      |

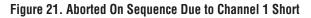

| t <sub>S_VS</sub>         | Update Rate                                        |                                                                          |                                                |   |              | 12.21        |              | μs     |

| V <sub>IN_SNS</sub> Input | Characteristics                                    |                                                                          |                                                |   |              |              |              |        |

| V <sub>VIN_SNS</sub>      | V <sub>IN_SNS</sub> Input Voltage Range            |                                                                          |                                                | • | 0            |              | 15           | V      |

| R <sub>VIN_SNS</sub>      | V <sub>IN SNS</sub> Input Resistance               |                                                                          |                                                |   | 70           | 90           | 110          | kΩ     |

T LINEAR

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_J = 25$ °C.  $V_{PWR} = V_{IN\_SNS} = 12V$ ;  $V_{DD33}$ ,  $V_{DD25}$ , REFP and REFM pins floating, unless otherwise indicated.  $C_{VDD33} = 100$ nF,  $C_{VDD25} = 100$ nF and  $C_{REF} = 100$ nF.

| SYMBOL                    | PARAMETER                                                  | CONDITIONS                                                                                                                                                                             |     | MIN       | ТҮР  | MAX  | UNITS  |

|---------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|------|------|--------|

| TUE <sub>VIN_SNS</sub>    | VIN_ON, VIN_OFF Threshold Total                            | $3V \le V_{VIN\_SNS} \le 8V$                                                                                                                                                           | •   |           |      | ±2.0 | %      |

|                           | Unadjusted Error                                           | V <sub>VIN_SNS</sub> > 8V                                                                                                                                                              | ٠   |           |      | ±1.0 | %      |

|                           | READ_VIN Total Unadjusted Error                            | $3V \le V_{VIN\_SNS} \le 8V$                                                                                                                                                           | •   |           |      | ±1.5 | %      |

|                           |                                                            | V <sub>VIN_SNS</sub> > 8V                                                                                                                                                              |     |           |      | ±1.0 | %      |

| DAC Soft-Con              | nect Comparator Characteristics                            | ·                                                                                                                                                                                      |     |           |      |      |        |

| V <sub>OS_CMP</sub>       | Offset Voltage                                             |                                                                                                                                                                                        | ٠   |           | ±3   | ±18  | mV     |

| Temperature               | Sensor Characteristics                                     | ·                                                                                                                                                                                      |     |           |      |      |        |

| TUE_TS                    | Total Unadjusted Error                                     |                                                                                                                                                                                        |     |           | ±1   |      | °C     |

| V <sub>OUT</sub> Enable ( | Dutput (V <sub>OUT_EN</sub> [3:0]) Characteristics         | ·                                                                                                                                                                                      |     |           |      |      |        |

| V <sub>VOUT_ENn</sub>     | Output High Voltage (Note 12)                              | $I_{VOUT_{ENn}} = -5\mu A, V_{DD33} = 3.3V$                                                                                                                                            |     | 11.6      | 12.5 | 14.7 | V      |

| IVOUT_ENn                 | Output Sourcing Current                                    | $V_{VOUT\_ENn}$ Pull-Up Enabled, $V_{VOUT\_ENn} = 1V$                                                                                                                                  | ٠   | -5        | -6   | -8   | μA     |

|                           | Output Sinking Current                                     | Strong Pull-Down Enabled,<br>V <sub>VOUT_ENn</sub> = 0.4V                                                                                                                              | •   | 3         | 5    | 8    | mA     |

|                           |                                                            | Weak Pull-Down Enabled, V <sub>VOUT_ENn</sub> = 0.4V                                                                                                                                   | •   | 33        | 50   | 60   | μA     |

|                           | Output Leakage Current                                     | Internal Pull-Up Disabled, $0V \le V_{VOUT\_ENn} \le 15V$                                                                                                                              | •   |           |      | ±1   | μΑ     |

| V <sub>OUT</sub> Enable ( | Dutput (V <sub>OUT_EN</sub> [7:4]) Characteristics         |                                                                                                                                                                                        |     |           |      |      |        |

| I <sub>VOUT_ENn</sub>     | Output Sinking Current                                     | Strong Pull-Down Enabled,<br>V <sub>OUT_ENn</sub> = 0.1V                                                                                                                               | •   | 3         | 6    | 9    | mA     |

|                           | Output Leakage Current                                     | $0V \le V_{VOUT\_ENn} \le 6V$                                                                                                                                                          | ٠   |           |      | ±1   | μA     |

| V <sub>IN</sub> Enable Ou | utput (V <sub>IN_EN</sub> ) Characteristics                |                                                                                                                                                                                        |     |           |      |      |        |

| V <sub>VIN_EN</sub>       | Output High Voltage                                        | $I_{VIN\_EN} = -5\mu A, V_{DD33} = 3.3V$                                                                                                                                               | •   | 11.6      | 12.5 | 14.7 | V      |

| IVIN_EN                   | Output Sourcing Current                                    | $V_{IN}_{EN}$ Pull-Up Enabled, $V_{VIN}_{EN}$ = 1V                                                                                                                                     | ٠   | -5        | -6   | -8   | μA     |

|                           | Output Sinking Current                                     | $V_{VIN_{EN}} = 0.4V$                                                                                                                                                                  | •   | 3         | 5    | 8    | mA     |

|                           | Leakage Current                                            | Internal Pull-Up Disabled, $0V \le V_{VIN_EN} \le 15V$                                                                                                                                 | •   |           |      | ±1   | μA     |

| EEPROM Cha                | racteristics                                               |                                                                                                                                                                                        |     |           |      |      |        |

| Endurance                 | (Notes 8, 11)                                              | 0°C < T <sub>J</sub> < 85°C During EEPROM Write<br>Operations                                                                                                                          | •   | 10,000    |      |      | Cycles |

| Retention                 | (Notes 8, 11)                                              | T <sub>J</sub> < 85°C                                                                                                                                                                  | ٠   | 10        |      |      | Years  |

| t <sub>MASS_WRITE</sub>   | Mass Write Operation Time (Note 9)                         | STORE_USER_ALL, 0°C < T <sub>J</sub> < 85°C During<br>EEPROM Write Operations                                                                                                          | •   |           | 440  | 4100 | ms     |

| Digital Inputs            | SCL, SDA, CONTROLO, CONTROL1, W                            | DI/RESETB, FAULTBOO, FAULTBO1, FAULTB10,                                                                                                                                               | FAU | LTB11, WP |      |      |        |

| VIH                       | High Level Input Voltage                                   |                                                                                                                                                                                        | ٠   | 2.1       |      |      | V      |

| VIL                       | Low Level Input Voltage                                    |                                                                                                                                                                                        | ٠   |           |      | 1.5  | V      |

| V <sub>HYST</sub>         | Input Hysteresis                                           |                                                                                                                                                                                        |     |           | 20   |      | mV     |

| I <sub>LEAK</sub>         | Input Leakage Current                                      | $0V \le V_{PIN} \le 5.5V$ , SDA, SCL, CONTROL <i>n</i> Pins Only                                                                                                                       | •   |           |      | ±2   | μΑ     |

|                           |                                                            | $\begin{array}{l} \text{OV} \leq \text{V}_{\text{PIN}} \leq \text{V}_{\text{DD33}} + 0.3\text{V}, \ \text{FAULTB}\textit{zn}, \\ \text{WDI/RESETB}, \ \text{WP Pins Only} \end{array}$ | •   |           |      | ±2   | μA     |

| t <sub>SP</sub>           | Pulse Width of Spike Suppressed                            | FAULTBzn, CONTROLn Pins Only                                                                                                                                                           |     |           | 10   |      | μs     |

|                           |                                                            | SDA, SCL Pins Only                                                                                                                                                                     |     |           | 98   |      | ns     |

| t <sub>FAULT_MIN</sub>    | Minimum Low Pulse Width for<br>Externally Generated Faults |                                                                                                                                                                                        |     | 110       |      |      | ms     |

|                           |                                                            |                                                                                                                                                                                        |     |           |      |      | 2978fd |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_J = 25$ °C.  $V_{PWR} = V_{IN\_SNS} = 12V$ ;  $V_{DD33}$ ,  $V_{DD25}$ , REFP and REFM pins floating, unless otherwise indicated.  $C_{VDD33} = 100$  F,  $C_{VDD25} = 100$  F and  $C_{REF} = 100$  F.

| SYMBOL                     | PARAMETER                                                                                                     | CONDITIONS                                                     |   | MIN                    | ТҮР       | MAX       | UNITS    |

|----------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|---|------------------------|-----------|-----------|----------|

| t <sub>resetb</sub>        | Pulse Width to Assert Reset                                                                                   | $V_{WDI/RESETB} \le 1.5V$                                      | • | 300                    |           |           | μs       |

| t <sub>WDI</sub>           | Pulse Width to Reset Watchdog Timer                                                                           | $V_{WDI/RESETB} \le 1.5V$                                      | • | 0.3                    |           | 200       | μs       |

| f <sub>WDI</sub>           | Watchdog Interrupt Input Frequency                                                                            |                                                                | • |                        |           | 1         | MHz      |

| CIN                        | Digital Input Capacitance                                                                                     |                                                                |   |                        | 10        |           | pF       |

| Digital Input S            | SHARE_CLK                                                                                                     |                                                                |   |                        |           |           |          |

| V <sub>IH</sub>            | High Level Input Voltage                                                                                      |                                                                | • | 1.6                    |           |           | V        |

| V <sub>IL</sub>            | Low Level Input Voltage                                                                                       |                                                                | • |                        |           | 0.8       | V        |

| f <sub>SHARE_CLK_IN</sub>  | Input Frequency Operating Range                                                                               |                                                                | • | 90                     |           | 110       | kHz      |

| t <sub>LOW</sub>           | Assertion Low Time                                                                                            | V <sub>SHARE_CLK</sub> < 0.8V                                  | • | 0.825                  |           | 1.1       | μs       |

| t <sub>RISE</sub>          | Rise Time                                                                                                     | V <sub>SHARE_CLK</sub> < 0.8V to V <sub>SHARE_CLK</sub> > 1.6V | • |                        |           | 450       | ns       |

| I <sub>LEAK</sub>          | Input Leakage Current                                                                                         | $0V \le V_{SHARE\_CLK} \le V_{DD33} + 0.3V$                    | • |                        |           | ±1        | μA       |

| C <sub>IN</sub>            | Input Capacitance                                                                                             |                                                                |   |                        | 10        |           | pF       |

| Digital Output             | s SDA, ALERTB, PWRGD, SHARE_CLK,                                                                              | FAULTBOO, FAULTBO1, FAULTB10, FAULTB1                          | 1 |                        |           |           | ·        |

| V <sub>OL</sub>            | Digital Output Low Voltage                                                                                    | I <sub>SINK</sub> = 3mA                                        | • |                        |           | 0.4       | V        |

| f <sub>SHARE_CLK_OUT</sub> | Output Frequency Operating Range                                                                              | 5.49k $\Omega$ Pull-Up to V <sub>DD33</sub>                    | • | 90                     | 100       | 110       | kHz      |

| Digital Inputs             |                                                                                                               |                                                                |   |                        |           |           | <u> </u> |

| V <sub>IH</sub>            | Input High Threshold Voltage                                                                                  |                                                                | • | V <sub>DD33</sub> -0.5 |           |           | V        |

| V <sub>IL</sub>            | Input Low Threshold Voltage                                                                                   |                                                                | • |                        |           | 0.5       | V        |

| I <sub>IH,IL</sub>         | High, Low Input Current                                                                                       | ASEL[1:0] = 0, V <sub>DD33</sub>                               | • |                        |           | ±95       | μA       |

| I <sub>IH, Z</sub>         | Hi-Z Input Current                                                                                            |                                                                | • |                        |           | ±24       | μA       |

| C <sub>IN</sub>            | Input Capacitance                                                                                             |                                                                |   |                        | 10        |           | pF       |

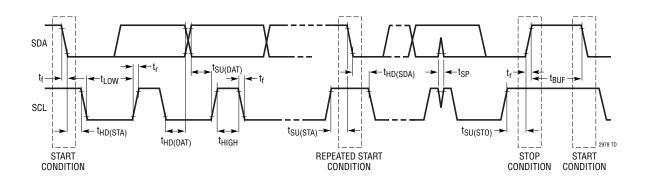

| Serial Bus Tim             | ning Characteristics                                                                                          | ·                                                              | ÷ |                        |           |           | <u> </u> |

| f <sub>SCL</sub>           | Serial Clock Frequency (Note 10)                                                                              |                                                                | • | 10                     |           | 400       | kHz      |

| t <sub>LOW</sub>           | Serial Clock Low Period (Note 10)                                                                             |                                                                | • | 1.3                    |           |           | μs       |

| t <sub>HIGH</sub>          | Serial Clock High Period (Note 10)                                                                            |                                                                | • | 0.6                    |           |           | μs       |

| t <sub>BUF</sub>           | Bus Free Time Between Stop and Start (Note 10)                                                                |                                                                | • | 1.3                    |           |           | μs       |

| t <sub>hd,sta</sub>        | Start Condition Hold Time (Note 10)                                                                           |                                                                | • | 600                    |           |           | ns       |

| t <sub>SU,STA</sub>        | Start Condition Setup Time (Note 10)                                                                          |                                                                | • | 600                    |           |           | ns       |

| t <sub>SU,STO</sub>        | Stop Condition Setup Time (Note 10)                                                                           |                                                                | • | 600                    |           |           | ns       |

| t <sub>hd,dat</sub>        | Data Hold Time (LTC2978 Receiving<br>Data) (Note 10)                                                          |                                                                | • | 0                      |           |           | ns       |

|                            | Data Hold Time (LTC2978 Transmitting<br>Data) (Note 10)                                                       |                                                                | • | 300                    |           | 900       | ns       |

| t <sub>SU,DAT</sub>        | Data Setup Time (Note 10)                                                                                     |                                                                | • | 100                    |           |           | ns       |

| t <sub>SP</sub>            | Pulse Width of Spike Suppressed (Note 10)                                                                     |                                                                |   |                        | 98        |           | ns       |

| t <sub>timeout_bus</sub>   | Time Allowed to Complete any PMBus<br>Command After Which Time SDA Will<br>Be Released and Command Terminated | Longer Timeout = 0<br>Longer Timeout = 1                       | • |                        | 25<br>200 | 35<br>280 | ms<br>ms |

LINEAR

# **ELECTRICAL CHARACTERISTICS**

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating for extended periods may affect device reliability and lifetime.

**Note 2:** All currents into device pins are positive. All currents out of device pins are negative. All voltages are referenced to ground unless otherwise specified. If power is supplied to the chip via the  $V_{DD33}$  pin only, connect  $V_{PWR}$  and  $V_{DD33}$  pins together.

**Note 3:** Hysteresis in the output voltage is created by package stress that differs depending on whether the IC was previously at a higher or lower temperature. Output voltage is always measured at 25°C, but the IC is cycled to 85°C or -40°C before successive measurements. Hysteresis is roughly proportional to the square of the temperature change.

Note 4: TUE(%) is defined as:

Gain Error (%) + 100 • (INL + V<sub>OS</sub>)/V<sub>IN</sub>.

**Note 5:** Integral nonlinearity (INL) is defined as the deviation of a code from a straight line passing through the actual endpoints of the transfer curve (OV and 6V). The deviation is measured from the center of the quantization band.

**Note 6:** The time between successive ADC conversions (latency of the ADC) for any given channel is given as: 36.9ms + (6.15ms • number of ADC channels configured in Low Resolution mode) + (24.6ms • number of ADC channels configured in High Resolution mode).

**Note 7:** Nonlinearity is defined from the first code that is greater than or equal to the maximum offset specification to full-scale code, 1023.

**Note 8:** EEPROM endurance and retention are guaranteed by design, characterization and correlation with statistical process controls. The minimum retention specification applies for devices whose EEPROM has been cycled less than the minimum endurance specification.

**Note 9:** The LTC2978 will not acknowledge any PMBus commands while a mass write operation is being executed. This includes the STORE\_USER\_ALL and MFR\_FAULT\_LOG\_STORE commands or a fault log store initiated by a channel faulting off.

**Note 10:** Maximum capacitive load, C<sub>B</sub>, for SCL and SDA is 400pF. Data and clock rise time (t<sub>r</sub>) and fall time (t<sub>f</sub>) are: (20 + 0.1 • C<sub>B</sub>) (ns) < t<sub>r</sub> < 300ns and (20 + 0.1 • C<sub>B</sub>) (ns) < t<sub>f</sub> < 300ns. C<sub>B</sub> = capacitance of one bus line in pF. SCL and SDA external pull-up voltage, V<sub>10</sub>, is 3.13V < V<sub>10</sub> < 5.5V.

Note 11: EEPROM endurance and retention will be degraded when  $T_J > 85^{\circ}C$ .

Note 12: Output enable pins are charge pumped from V<sub>DD33</sub>.

**Note 13:** The current sense resolution is determined by the L11 format and the mV units of the returned value. For example a full scale value of 170mV returns a L11 value of 0xF2A8 = 680 •  $2^{-2}$  = 170. This is the lowest range that can represent this value without overflowing the L11 mantissa and the resolution for 1LSB in this range is  $2^{-2}$  mV =  $250\mu$ V. Each successively lower range improves resolution by cutting the LSB size in half.

## PMBUS TIMING DIAGRAM

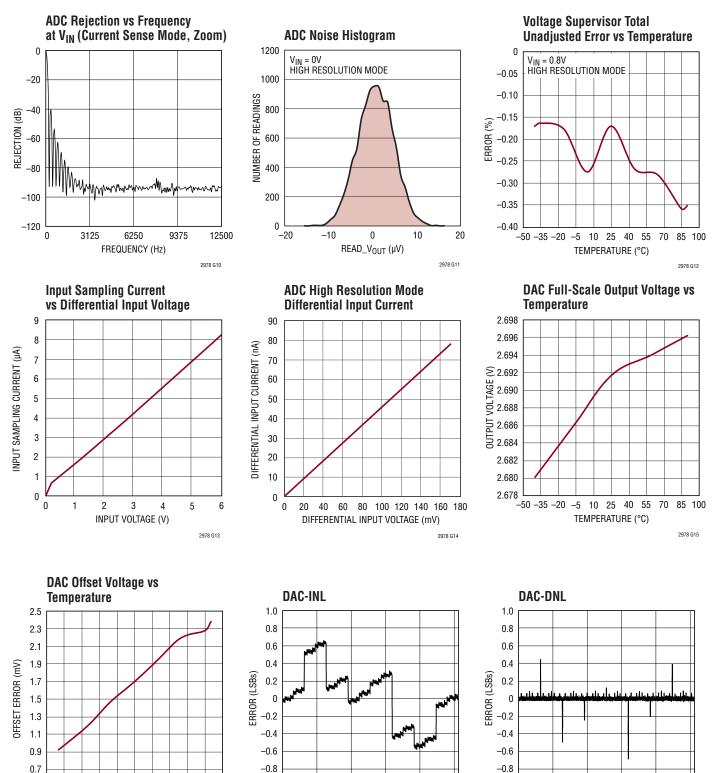

**ADC Total Unadjusted Error** vs Temperature ADC VIN = 1.8V

-50 -35 -20 -5 10 25 40 55 70 85 100 TEMPERATURE (°C) 2978 G03

ADC-DNL

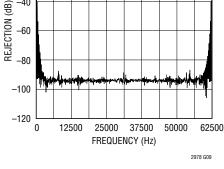

**ADC Rejection vs Frequency** at VIN (Current Sense Mode)

2978fd

-80

-100

-120

0

12500

25000

9375

12500

2978 G08

0.5

-50 -35 -20

10 25 40 55 70

TEMPERATURE (°C)

-5

400

600

DAC CODE

800

1000

2978 G17

-1.0

0

85 100

2978 G16

200

-1.0

0

200

400

600

DAC CODE

800

1000

2978fd

2978 G18

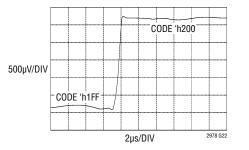

**DAC Transient Response to 1LSB DAC Code Change**

12

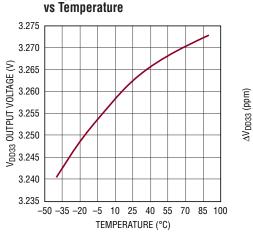

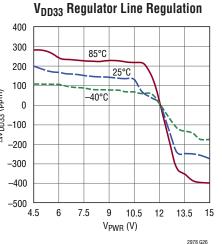

V<sub>DD33</sub> Regulator Output Voltage

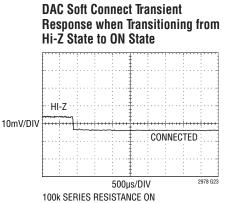

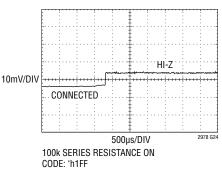

**DAC Soft Connect Transient** Response when Transitioning from **ON State to Hi-Z State**

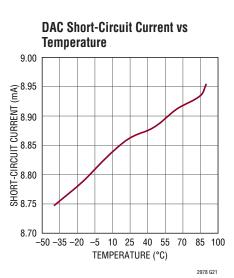

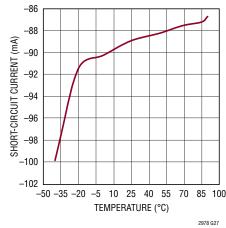

V<sub>DD33</sub> Regulator Short-Circuit Current vs Temperature

2978 G25

I<sub>SINK</sub> (mA)

2978 G34

I<sub>SINK</sub> (mA)

2978 G35

## **PIN FUNCTIONS**

| PIN NAME             | PIN NUMBER | PIN TYPE       | DESCRIPTION                                                                                                                                                                                                                                               |  |  |  |

|----------------------|------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V <sub>SENSEM6</sub> | 1*         | In             | DC/DC Converter Differential (-) Output Voltage-6 Sensing Pin                                                                                                                                                                                             |  |  |  |

| V <sub>SENSEP7</sub> | 2*         | In             | DC/DC Converter Differential (+) Output Voltage or Current-7 Sensing Pin                                                                                                                                                                                  |  |  |  |

| V <sub>SENSEM7</sub> | 3*         | In             | DC/DC Converter Differential (-) Output Voltage or Current-7 Sensing Pin                                                                                                                                                                                  |  |  |  |

| V <sub>OUT_EN0</sub> | 4          | Out            | DC/DC Converter Enable-0 Pin. Output High Voltage Optionally Pulled Up to 12V by 5µA                                                                                                                                                                      |  |  |  |

| V <sub>OUT_EN1</sub> | 5          | Out            | DC/DC Converter Enable-1 Pin. Output High Voltage Optionally Pulled Up to 12V by 5µA                                                                                                                                                                      |  |  |  |

| V <sub>OUT_EN2</sub> | 6          | Out            | DC/DC Converter Enable-2 Pin. Output High Voltage Optionally Pulled Up to 12V by 5µA                                                                                                                                                                      |  |  |  |

| V <sub>OUT_EN3</sub> | 7          | Out            | DC Converter Enable-3 Pin. Output High Voltage Optionally Pulled Up to 12V by 5µA                                                                                                                                                                         |  |  |  |

| V <sub>OUT_EN4</sub> | 8          | Out            | DC/DC Converter Open-Drain Pull-Down Output-4                                                                                                                                                                                                             |  |  |  |

| V <sub>OUT_EN5</sub> | 9          | Out            | DC/DC Converter Open-Drain Pull-Down Output-5                                                                                                                                                                                                             |  |  |  |

| V <sub>OUT_EN6</sub> | 10         | Out            | DC/DC Converter Open-Drain Pull-Down Output-6                                                                                                                                                                                                             |  |  |  |

| V <sub>OUT_EN7</sub> | 11         | Out            | DC/DC Converter Open-Drain Pull-Down Output-7                                                                                                                                                                                                             |  |  |  |

| V <sub>IN_EN</sub>   | 12         | Out            | DC/DC Converter V <sub>IN</sub> ENABLE Pin. Output High Voltage Optionally Pulled Up to 12V by 5µA                                                                                                                                                        |  |  |  |

| DNC                  | 13         | Do Not Connect | Do Not Connect to This Pin                                                                                                                                                                                                                                |  |  |  |

| V <sub>IN_SNS</sub>  | 14         | In             | V <sub>IN</sub> SENSE Input. This Voltage is Compared Against the V <sub>IN</sub> On and Off Voltage Thresholds in Order to Determine When to Enable and Disable, Respectively, the Downstream DC/DC Converters.                                          |  |  |  |

| V <sub>PWR</sub>     | 15         | In             | $V_{PWR}$ Serves as the Unregulated Power Supply Input to the Chip (4.5V to 15V). If a 4.5V to 15V Supply Voltage is Unavailable, Short $V_{PWR}$ to $V_{DD33}$ and Power the Chip Directly from a 3.3V Supply. Bypass to GND with 0.1 $\mu$ F Capacitor. |  |  |  |

| V <sub>DD33</sub>    | 16         | In/Out         | If Shorted to V <sub>PWR</sub> , it Serves as 3.13V to 3.47V Supply Input Pin. Otherwise, it is a 3.3V Internally Regulated Voltage Output (Use 0.1µF Decoupling Capacitor to GND).                                                                       |  |  |  |

| V <sub>DD33</sub>    | 17         | In             | Input for Internal 2.5V Sub-Regulator. Short This Pin to Pin 16                                                                                                                                                                                           |  |  |  |

| V <sub>DD25</sub>    | 18         | In/Out         | 2.5V Internally Regulated Voltage Output. Bypass to GND with a 0.1µF Capacitor.                                                                                                                                                                           |  |  |  |

| WP                   | 19         | In             | Digital Input. Write-Protect Input Pin, Active High                                                                                                                                                                                                       |  |  |  |

| PWRGD                | 20         | Out            | Power Good Open-Drain Output. Indicates When Outputs are Power Good. Can be Used as System Power-On Reset. The Latency of This Signal May Be as Long as the ADC Latency. See Note 6.                                                                      |  |  |  |

| SHARE_CLK            | 21         | In/Out         | Bidirectional Clock Sharing Pin. Connect a 5.49k Pull-Up Resistor to V <sub>DD33</sub> .                                                                                                                                                                  |  |  |  |

| WDI/RESETB           | 22         | In             | Watchdog Timer Interrupt and Chip Reset Input. Connect a 10k Pull-Up Resistor to V <sub>DD33</sub> . Rising Edge Resets Watchdog Counter. Holding This Pin Low for More Than t <sub>RESETB</sub> Resets the Chip.                                         |  |  |  |

| FAULTB00             | 23         | In/Out         | Open-Drain Output and Digital Input. Active Low Bidirectional Fault Indicator-00. Connect a 10k Pull-Up Resistor to V <sub>DD33</sub> .                                                                                                                   |  |  |  |

| FAULTB01             | 24         | In/Out         | Open-Drain Output and Digital Input. Active Low Bidirectional Fault Indicator-01. Connect a 10k Pull-Up Resistor to V <sub>DD33</sub> .                                                                                                                   |  |  |  |

| FAULTB10             | 25         | In/Out         | Open-Drain Output and Digital Input. Active Low Bidirectional Fault Indicator-10. Connect a 10k Pull-Up Resistor to V <sub>DD33</sub> .                                                                                                                   |  |  |  |

| FAULTB11             | 26         | In/Out         | Open-Drain Output and Digital Input. Active Low Bidirectional Fault Indicator-11. Connect a 10k Pull-Up Resistor to V <sub>DD33</sub> .                                                                                                                   |  |  |  |

| SDA                  | 27         | In/Out         | PMBus Bidirectional Serial Data Pin                                                                                                                                                                                                                       |  |  |  |

| SCL                  | 28         | In             | PMBus Serial Clock Input Pin (400kHz Maximum)                                                                                                                                                                                                             |  |  |  |

| ALERTB               | 29         | Out            | Open-Drain Output. Generates an Interrupt Request in a Fault/Warning Situation                                                                                                                                                                            |  |  |  |

| CONTROLO             | 30         | In             | Control Pin 0 Input                                                                                                                                                                                                                                       |  |  |  |

| CONTROL1             | 31         | In             | Control Pin 1 Input                                                                                                                                                                                                                                       |  |  |  |