# TS4604

# Stereo headset driver and analog audio line driver with integrated reference to ground

## Features

- Operating from V<sub>CC</sub> = 3 V up to 4.8 V single supply operation

- Line driver stereo differential inputs

- External gain setting resistors

- Space-saving package: TSSOP28 pitch 0.65 mm

- Dedicated shutdown control per function

- 100 mW headset drive into a 16  $\Omega$  load

- 90 dB high PSRR on headset drive

- Two internal negative supplies to ensure ground-referenced, headset and line driver capless outputs

- Internal undervoltage mute

- Line driver 2 Vrms typ. Output voltage across entire supply voltage range

- Pop-&-click reduction circuitry, thermal shutdown and output short-circuit protection

# Applications

- PDP/LCD TV

- Set-top boxes

# Description

The TS4604 is a stereo ground-referenced output analog line driver and stereo headset driver whose design allows the output DC-blocking capacitors to be removed, thus reducing component count. The TS4604 drives 2 Vrms into a 5 k $\Omega$  load or more. The device has differential inputs and uses external gain setting resistors.

The TS4604 delivers up to 100 mW per channel into a 16  $\Omega$  load. All outputs of the TS4604 include ±8 kV human body model ESD protection cells.

# Contents

| 1   | Abso  | lute maximum ratings and operating conditions              | . 3  |

|-----|-------|------------------------------------------------------------|------|

| 2   | Туріс | al application                                             | . 4  |

| 3   | Elect | rical characteristics                                      | . 6  |

| 4   |       | acteristics of the line driver                             |      |

| 5   | Chara | acteristics of the headset driver                          | 11   |

| 6   | Appli | cation information                                         | . 17 |

|     | 6.1   | General description                                        | . 17 |

|     | 6.2   | Use of ceramic capacitors                                  | 18   |

|     | 6.3   | Flying and tank capacitor for the internal negative supply | 18   |

|     | 6.4   | Power supply decoupling capacitor (Cs)                     | 18   |

|     | 6.5   | Input coupling capacitor (Cin)                             | 19   |

|     | 6.6   | Range of the gain setting resistors                        | 19   |

|     | 6.7   | Performance of CMRR                                        | 21   |

|     | 6.8   | Internal and external undervoltage detection               | 21   |

|     |       | 6.8.1 Internal UVLO                                        |      |

|     |       | 6.8.2 External UVLO                                        |      |

|     | 6.9   | 2nd order Butterworth low-pass filter                      |      |

|     | 6.10  | ESD protection and compliance                              |      |

| 105 | 6.11  | Pop-&-click circuitry                                      |      |

| )•  | 6.12  | Start-up phase                                             |      |

|     | 6.13  | Layout recommendations                                     | 26   |

| 7   | Pack  | age information                                            | 27   |

|     | 7.1   | TSSOP28 package                                            | 28   |

| 8   | Orde  | ring information                                           | 29   |

| 9   | Revis | sion history                                               | 30   |

# 1 Absolute maximum ratings and operating conditions

| <u> </u>          |                                                                                      |                                   |      |

|-------------------|--------------------------------------------------------------------------------------|-----------------------------------|------|

| Symbol            | Parameter                                                                            | Value                             | Unit |

| V <sub>CC</sub>   | Supply voltage <sup>(1)</sup>                                                        | 5.5                               | V    |

| V <sub>in</sub>   | Input voltage enable & standby pin <sup>(2)</sup>                                    | GND to V <sub>CC</sub>            | V    |

| V <sub>in</sub>   | Input signal voltage                                                                 | -2.5 to +2.5                      | V    |

| T <sub>oper</sub> | Operating free-air temperature range                                                 | -40 to + 85                       | °C   |

| T <sub>stg</sub>  | Storage temperature                                                                  | -65 to +150                       | °C   |

| Тj                | Maximum junction temperature                                                         | 150                               | O°C  |

| R <sub>thja</sub> | Thermal resistance junction to ambient <sup>(3)</sup>                                | 200                               | °C/W |

| Pd                | Power dissipation                                                                    | Internally limited <sup>(4)</sup> |      |

|                   | Human body model for all pins except outputs<br>Human body model for all output pins | <b>P</b> <sup>2</sup><br>8        | kV   |

| ESD               | Machine model                                                                        | 200                               | V    |

|                   | Charge device model                                                                  | 1500                              | V    |

| Latch-up          | Latch-up immunity                                                                    | 200                               | mA   |

|                   | Lead temperature (soldering, 10sec)                                                  | 260                               | °C   |

| Table 1. | Absolute maximum | ratings | (AMR)               |

|----------|------------------|---------|---------------------|

|          |                  |         | <b>(</b> <i>/</i> , |

1. All voltage values are measured with respect to the ground pin.

2. The magnitude of the input signal must never exceed V<sub>CC</sub> + 0.3 V/GND - 0.3 V.

3. The device is protected from overheating by a thermal shutdown mechanism active at 150° C.

4. Exceeding the power derating curves during a long period provokes abnormal operating conditions.

#### Table 2.Operating conditions

|     | Symbol            | Parameter                                             | Value            | Unit |

|-----|-------------------|-------------------------------------------------------|------------------|------|

|     | V <sub>CC</sub>   | Supply voltage                                        | 3 to 4.8         | V    |

| 26  | Vicm              | Common-mode input voltage range                       | From -1.4 to 1.4 | V    |

| SO  | R <sub>LD</sub>   | Line drive load resistor                              | ≥ 5              | kΩ   |

| 005 | R <sub>HD</sub>   | Headset drive load resistor                           | ≥ 16             | Ω    |

|     | R <sub>thja</sub> | Thermal resistance junction-to-ambient <sup>(1)</sup> | 80               | °C/W |

1. With heatsink surface =  $125 \text{ mm}^2$ .

# 2 Typical application

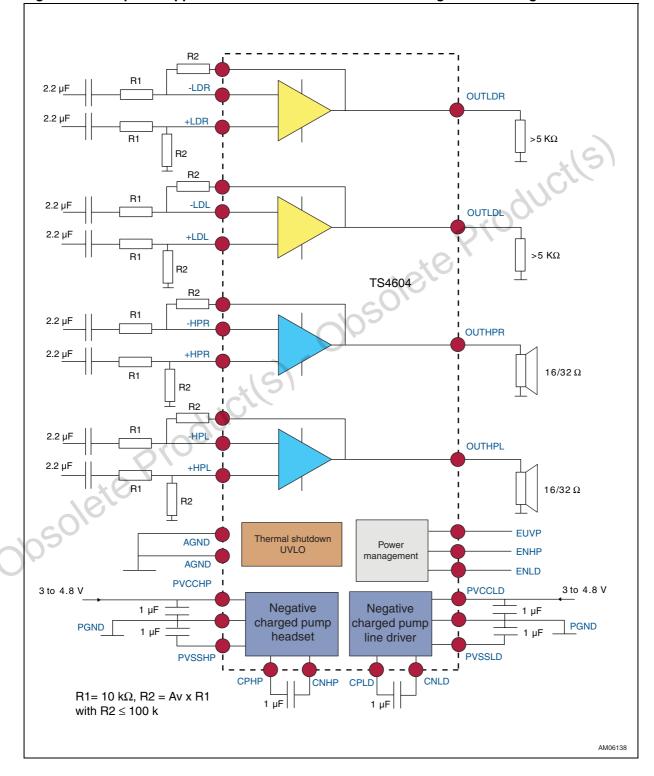

#### Figure 1. Simplified application schematics in differential configuration setting

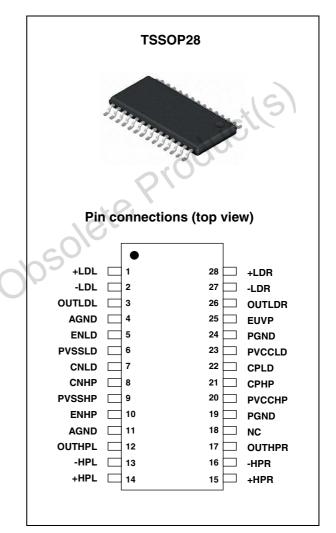

| Pin number | I/O <sup>(1)</sup> | Pin name | Pin description                                            |  |  |

|------------|--------------------|----------|------------------------------------------------------------|--|--|

| 1          | I                  | +LDL     | Left line driver positive input channel                    |  |  |

| 2          | I                  | -LDL     | Left line driver negative input channel                    |  |  |

| 3          | 0                  | OUTLDL   | Left line driver output channel                            |  |  |

| 4          | Р                  | AGND     | Analog line driver power ground                            |  |  |

| 5          | I                  | ENLD     | Line driver enable input pin (active high)                 |  |  |

| 6          | 0                  | PVSSLD   | Output from line drive charge pump                         |  |  |

| 7          | I/O                | CNLD     | Line driver charge pump flying capacitor negative terminal |  |  |

| 8          | I/O                | CNHP     | Headset charge pump flying capacitor negative terminal     |  |  |

| 9          | I/O                | PVSSHP   | Output from headset drive charge pump                      |  |  |

| 10         | I                  | ENHP     | Headset driver enable input pin (active high)              |  |  |

| 11         | Р                  | AGND     | Headphone analog input power ground                        |  |  |

| 12         | 0                  | OUTHPL   | Left headset driver output channel                         |  |  |

| 13         | I                  | -HPL     | Left headset driver negative input channel                 |  |  |

| 14         | I                  | +HPL     | Left headset driver positive input channel                 |  |  |

| 15         | I                  | +HPR     | Right headset driver positive input channel                |  |  |

| 16         | I                  | -HPR     | Right headset driver negative input channel                |  |  |

| 17         | 0                  | OUTHPR   | Right headset driver output channel                        |  |  |

| 18         |                    | NC       | Not connected                                              |  |  |

| 19         | Р                  | PGND     | Headset driver power ground                                |  |  |

| 20         | Р                  | PVCCHP   | Headset driver power supply voltage <sup>(2)</sup>         |  |  |

| 21         | I/O                | СРНР     | Headset charge pump flying capacitor positive terminal     |  |  |

| 22         | I/O                | CPLD     | Line driver charge pump flying capacitor positive terminal |  |  |

| 23         | Р                  | PVCCLD   | Line driver power supply voltage <sup>(2)</sup>            |  |  |

| 24         | Р                  | PGND     | Line driver power ground                                   |  |  |

| 25         | I                  | EUVP     | External undervoltage protection input pin                 |  |  |

| 26         | 0                  | OUTLDR   | Right line driver output channel                           |  |  |

| 27         | I                  | -LDR     | Right line driver negative input channel                   |  |  |

| 28         | I                  | +LDR     | Right line driver positive input channel                   |  |  |

Table 3. Pin descriptions

1. I = input, O = output, P = power

2. PVccHP and PVccLD are internally connected, so PVccHP must be equal to PVccLD.

# 3 Electrical characteristics

# Table 4.Common part: $V_{CC} = +3.3 V$ , GND = 0 V, CPhp = CPld = 1 $\mu$ F, $T_{amb} = 25^{\circ}$ C<br/>(unless otherwise specified)

| VIL       VENHP and VENLD Input voltage low         VIH       VENHP and VENLD Input voltage high         IIH       High level input current (ENHP and ENLD)         IIL       Low level input current (ENHP and ENLD)         Fosc       Internal negative voltage switching frequency, all temperaturange         Vup       External undervoltage detection threshold         Ihyst       External undervoltage detection hysteresis current | 38<br>57<br>-1<br>-1<br>ure 400<br>1.15 | 40<br>60<br>550 | 43<br>66<br>1<br>1 | % Vcc<br>% Vcc<br>μΑ<br>μΑ |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------|--------------------|----------------------------|

| I <sub>IH</sub> High level input current (ENHP and ENLD)         I <sub>IL</sub> Low level input current (ENHP and ENLD)         F <sub>osc</sub> Internal negative voltage switching frequency, all temperaturange         Vup       External undervoltage detection threshold         Ihyst       External undervoltage detection hysteresis current                                                                                        | -1<br>-1<br>Ire 400                     |                 | 1                  | μA                         |

| IL       Low level input current (ENHP and ENLD)         Fosc       Internal negative voltage switching frequency, all temperaturange         Vup       External undervoltage detection threshold         Ihyst       External undervoltage detection hysteresis current                                                                                                                                                                      | -1<br>Ire 400                           | 550             | 1                  | -                          |

| Fosc       Internal negative voltage switching frequency, all temperaturange         Vup       External undervoltage detection threshold         Ihyst       External undervoltage detection hysteresis current                                                                                                                                                                                                                               | <sup>1re</sup> 400                      | 550             |                    | μΑ                         |

| Fosc       range         Vup       External undervoltage detection threshold         Ihyst       External undervoltage detection hysteresis current                                                                                                                                                                                                                                                                                           | 400                                     | 550             |                    |                            |

| Ihyst         External undervoltage detection hysteresis current                                                                                                                                                                                                                                                                                                                                                                              | 1.15                                    |                 | 800                | <b>k</b> Hz                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         | 1.25            | 1.35               | v                          |

| V/byst Dyss UD/LD Internal undervioltage detection bysterratio                                                                                                                                                                                                                                                                                                                                                                                |                                         | 5               |                    | μA                         |

| Vhyst Pvcc_HP/LD Internal undervoltage detection hysteresis                                                                                                                                                                                                                                                                                                                                                                                   | 0                                       | 200             |                    | mV                         |

| Vuvl       – power up         – power down                                                                                                                                                                                                                                                                                                                                                                                                    | SIG                                     | 2.8<br>2.6      |                    | v                          |

| Av Overall external gain (R2 ≤100 kΩ R1 = R2/Av)                                                                                                                                                                                                                                                                                                                                                                                              | 0<br>1                                  |                 | 20<br>10           | dB<br>V/V                  |

| solete Product(S)                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         |                 |                    |                            |

| Symbol            | Parameters and test conditions                                                                                            | Min. | Тур. | Max.       | Unit              |

|-------------------|---------------------------------------------------------------------------------------------------------------------------|------|------|------------|-------------------|

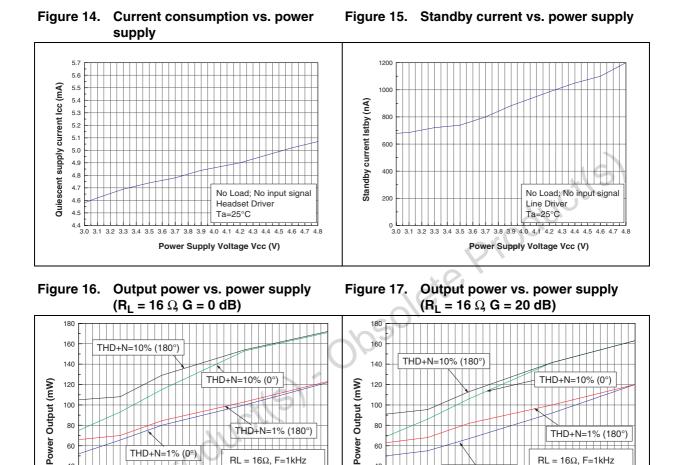

| I <sub>cc</sub>   | Supply current (no input signal, no load)                                                                                 |      | 5    | 6.5        | mA                |

| I <sub>ENHP</sub> | Headset overall standby current (no input signal):<br>$V_{ENHP} = GND$<br>$V_{ENHP} = 38\% V_{CC}$                        |      | 1    | 5<br>100   | μA                |

| V <sub>io</sub>   | Input offset voltage                                                                                                      | -7   | 0    | 7          | mV                |

| Po                | Headphone output power:<br>THD + N = 1% max, f = 1 kHz, BW = 22 kHz, R <sub>L</sub> = 16 $\Omega$                         | 45   | 65   |            | mW                |

| Po                | Headphone output power:<br>THD + N = 1% max, f = 1 kHz, BW = 22 kHz, R <sub>L</sub> = 32 $\Omega$                         | 30   | 45   | .ct        | SmW               |

| THD + N           | Total harmonic distortion + noise:<br>$R_L = 16 \Omega$ , $P_o = 60$ mW, f = 20 Hz to 20 kHz, BW = 22 kHz                 |      | 0.05 | 00         | %                 |

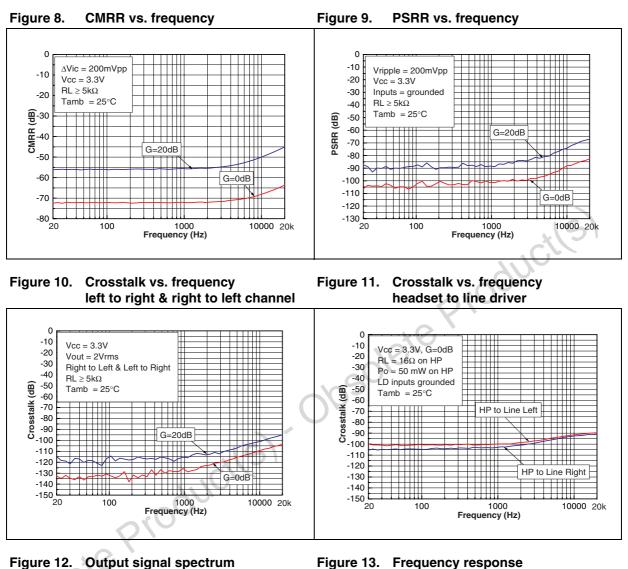

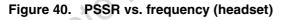

| PSRR              | Headphone power supply rejection ratio with AC inputs grounded: $f = 217 \text{ Hz}$ , $V_{ripple} = 200 \text{ mV}_{pp}$ | 2    | 90   |            | dB                |

| t <sub>WU</sub>   | Total wake-up time                                                                                                        | 0    | 30   |            | ms                |

| t <sub>STBY</sub> | Standby time                                                                                                              |      | 20   |            | μs                |

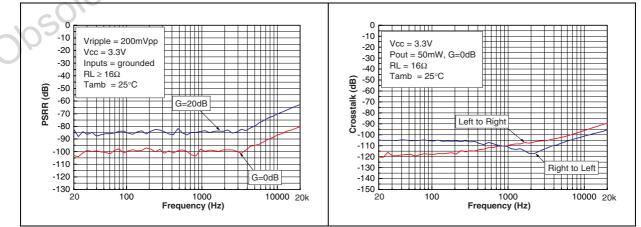

| Xtalk             | Crosstalk headphone to line:<br>Pout = 50 mW, $R_L = 16 \Omega$ , f = 20 Hz to 20 kHz                                     |      | -100 |            | dB                |

| SNR               | Signal-to-noise ratio (A-weighting): $R_L = 16 \Omega$ , $P_o = 60$ mW                                                    |      | 102  |            | dB                |

| CMRR              | Common-mode rejection ratio:<br>f = 20 Hz to 20 kHz, Vic = 200 mVpp                                                       |      | -70  |            | dB                |

| V <sub>N</sub>    | Output voltage noise: f = 20 Hz to 20 kHz, A-weighted                                                                     |      | 7.6  |            | μV <sub>RMS</sub> |

| CL <sup>(1)</sup> | Capacitive load:<br>$R_L = 16 \Omega \text{ to } 100 \Omega$<br>$R_L > 100 \Omega$                                        |      |      | 400<br>100 | pF                |

# Headset driver part: V<sub>CC</sub> = +3.3 V, GND = 0 V, Table 5.

1. Higher capacitive loads are possible by adding a serial resistor of 47  $\Omega$  in the line driver output. Josol

| Symbol             | Parameters and test conditions                                                                                    | Min. | Тур.  | Max.     | Unit              |

|--------------------|-------------------------------------------------------------------------------------------------------------------|------|-------|----------|-------------------|

| I <sub>cc</sub>    | Supply current (no input signal, no load)                                                                         |      | 5     | 6.5      | mA                |

| I <sub>ENLD</sub>  | Line drive standby current (no input signal)<br>$V_{ENLD} = GND$<br>$V_{ENLD} = 38\% V_{CC}$                      |      |       | 5<br>100 | μΑ                |

| V <sub>io</sub>    | Input offset voltage                                                                                              | -7   | 0     | +7       | mV                |

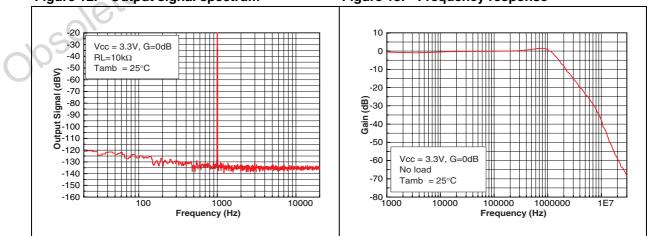

| V <sub>SWING</sub> | Output voltage swing:<br>$R_L = 10 \text{ k}\Omega$ , $C_L = 100 \text{ pF}$ , THD+N = 0.1%                       |      | 2.1   |          | Vrms              |

| PSRR               | Line driver power supply rejection ratio with AC inputs grounded: f = 217 Hz, $V_{ripple}$ = 200 mV <sub>pp</sub> |      | 90    |          | dB                |

| t <sub>WU</sub>    | Wake-up time from shutdown                                                                                        |      | 30    | 5        | ms                |

| t <sub>STBY</sub>  | Standby time                                                                                                      |      | 20    | •        | μs                |

| SNR                | Signal-to-noise ratio (A-weighting): Vin = 1.7 Vrms                                                               | X    | 102   |          | dB                |

| V <sub>N</sub>     | Output voltage noise: f = 20 Hz to 20 kHz, A-weighted                                                             | e .  | 8     |          | μV <sub>RMS</sub> |

| GBw                | Gain bandwidth product                                                                                            |      | 1     |          | MHz               |

| Sr                 | Slew rate                                                                                                         |      | 0.5   |          | V / µs            |

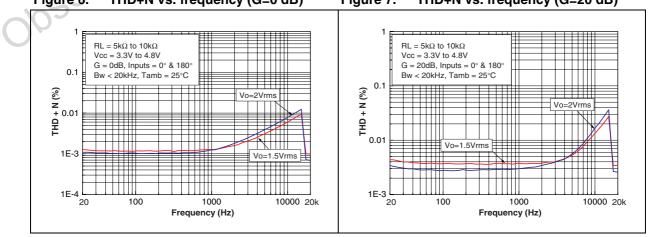

| THD+N              | BW = 22 kHz, R <sub>L</sub> = 10 k $\Omega$ , V <sub>O</sub> = 1.5 Vrms, Av = 1, f = 20 Hz to 20 kHz              |      | 0.001 |          | %                 |

| CMRR               | f = 20 Hz to 20 kHz, Vic = 200 mVpp                                                                               |      | -70   |          | dB                |

| Xtalk              | Crosstalk channel: f = 20 Hz to 20 kHz, Vo = 1.5 Vrms, $R_L = 5 k\Omega$                                          |      | -120  |          | dB                |

| CL <sup>(1)</sup>  | Capacitive load: $R_L > 5 k\Omega$                                                                                |      |       | 400      | pF                |

1. Higher capacitive loads are possible by adding a serial resistor of 47  $\Omega$  in the line driver output.

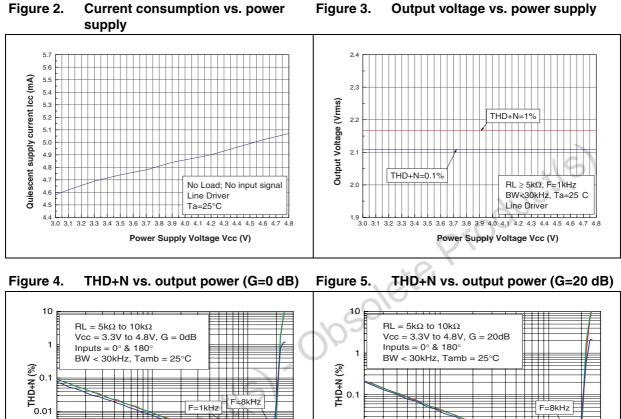

# 4 Characteristics of the line driver

57

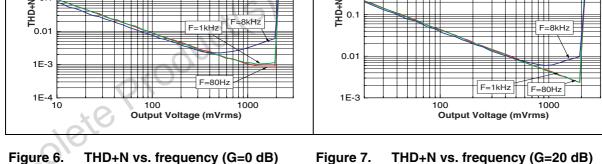

#### Characteristics of the headset driver 5

100

80

60

40

20

THD+N=1% (180°)

$RL = 16\Omega$ , F=1kHz

Headset Driver

BW<30kHz, Ta=25 C

G=0dB

3.0 3.1 3.2 3.3 3.4 3.5 3.6 3.7 3.8 3.9 4.0 4.1 4.2 4.3 4.4 4.5 4.6 4.7 4.8

Power Supply Voltage Vcc (V)

100

80

60

40

20

THD+N=1% (0°)

THD+N=1% (180°)

BW<30kHz, Ta=25 C

$RL = 16\Omega$ , F=1kHz

Headset Driver

G=20dB

THD+N=1% (0°)

0 4.1 4.2 4.3 4.4 4.5 4.6 4.7 4.8 3.0 3.1 3.2 3.3 3.4 3.5 3.6 3.7 3.8 3.9 4.0 4.1 4.2 4.3 4.4 4.5 4.6 4.7 4.8

Power Supply Voltage Vcc (V)

F=1kHz

100

1111

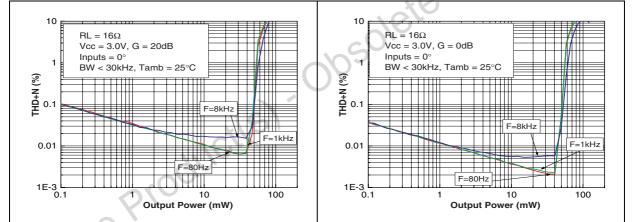

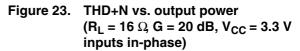

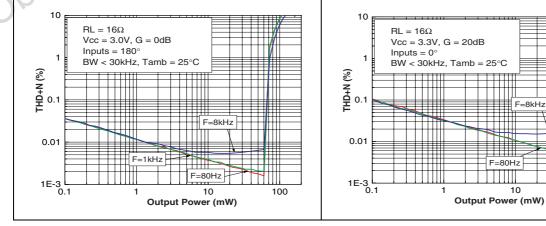

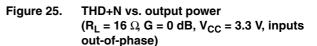

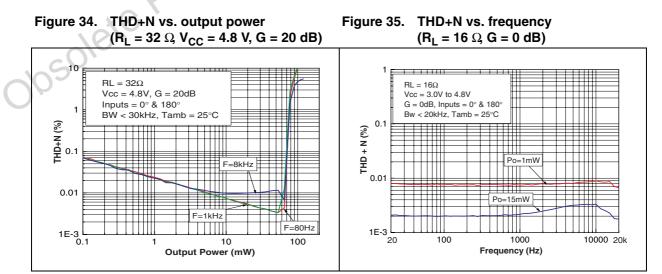

#### Figure 24. THD+N vs. output power ( $R_L = 16 \Omega$ , G = 0 dB, $V_{CC} = 3.3 V$ inputs in-phase)

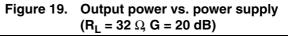

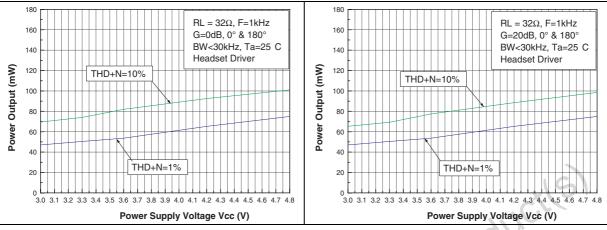

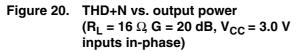

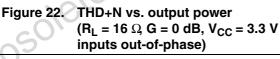

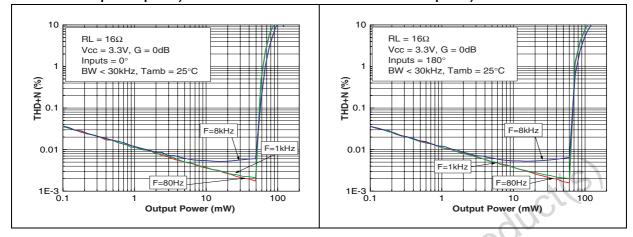

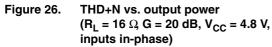

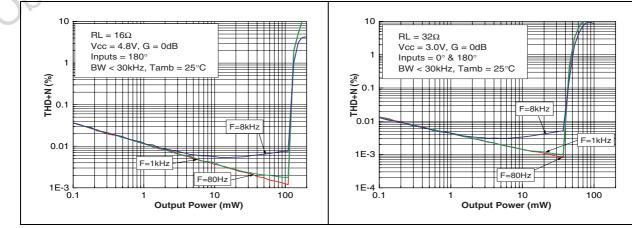

Figure 27. THD+N vs. output power ( $R_L = 16 \Omega$ , G = 0 dB, V<sub>CC</sub> = 4.8 V inputs in-phase)

Figure 28. THD+N vs. output power ( $R_L = 16 \Omega$ , G = 0 dB, V<sub>CC</sub> = 4.8 V inputs out-of-phase)

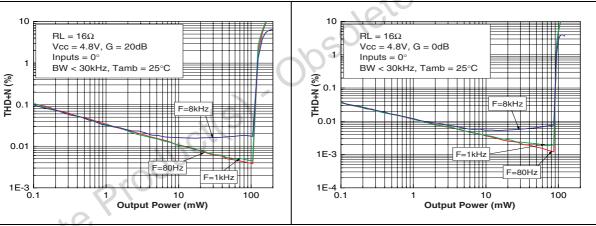

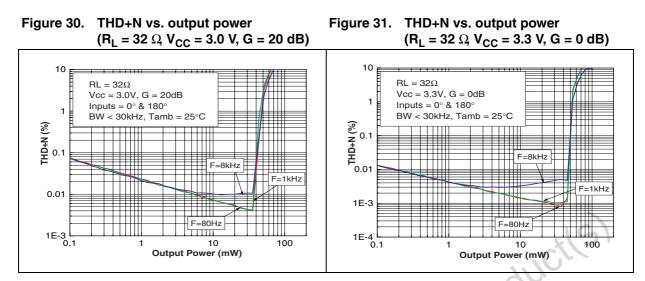

Figure 29. THD+N vs. output power ( $R_L = 32 \ \Omega$ ,  $V_{CC} = 3.0 \ V$ ,  $G = 0 \ dB$ )

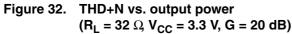

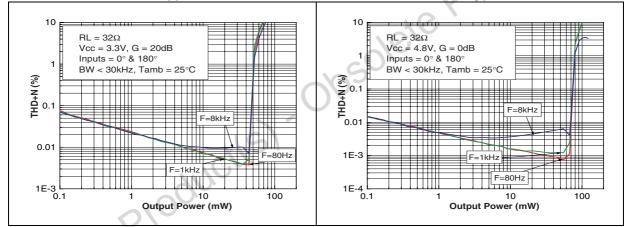

Figure 33. THD+N vs. output power ( $R_L = 32 \Omega$ ,  $V_{CC} = 4.8 V$ , G = 0 dB)

14/31

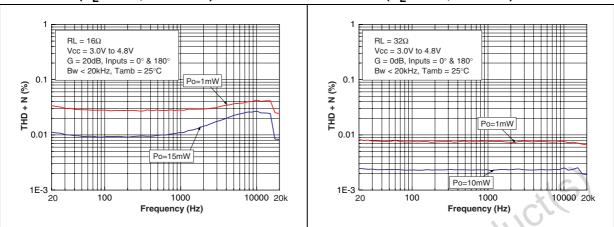

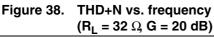

#### Figure 36. THD+N vs. frequency Fig ( $R_L = 16 \Omega, G = 20 \text{ dB}$ )

#### Figure 37. THD+N vs. frequency ( $R_1 = 32 \Omega_1 G = 0 dB$ )

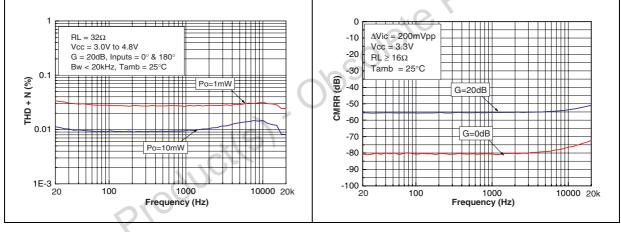

Figure 41. Crosstalk vs. frequency (left to right, Pout = 50 mW)

Figure 39. CMRR vs. frequency (headset)

57

1E7

100000 1000000 Frequency (Hz)

# Figure 43. Crosstalk vs. frequency

04-ai

-50

-60

-70

-80 L\_\_\_\_\_ 1000

Obsolete

Tamb =  $25^{\circ}C$

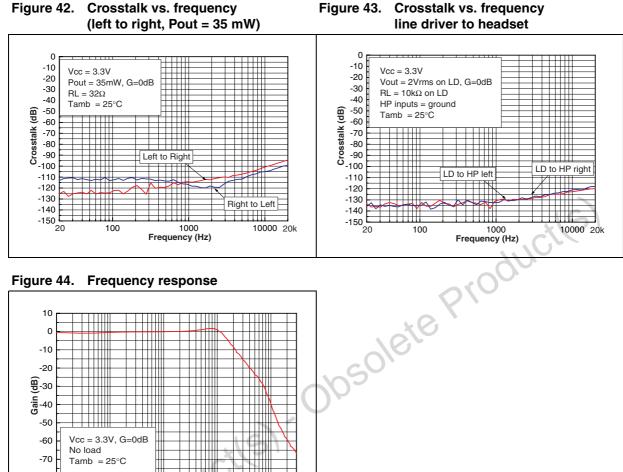

10000

No load

Vcc = 3.3V, G=0dB

# 6 Application information

# 6.1 General description

The TS4604 is a stereo headset driver and a ground-referenced stereo audio line driver. To save energy, each audio path, line driver or headphone can be independently set to standby mode.

The headphone delivers up to 100 mW into a 16  $\Omega$  load, and the line driver drives up to 2 Vrms into 5k or more. The gain can be set up to 20 dB by changing the values of the external gain resistors.

The outputs of the headphone and line driver are protected against overloads. Overloads can occur when the outputs are short-circuited between them or to Gnd or to  $V_{CC}$ . There is also an internal thermal shutdown activated at 150°C (typical) and deactivated at 120°C (typical).

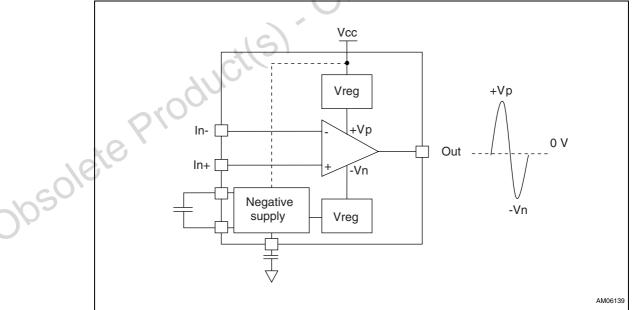

To remove the bulky output DC blocking capacitor and maximize the output swing of the amplifier, the TS4604 embeds a low noise internal negative supply. All amplifiers are supplied between a positive voltage +Vp and a negative voltage -Vn. With this architecture, the output voltage is centered on 0 V, allowing the swing of the output voltage between the positive rail, as depicted in *Figure 45*.

Both the line driver and headset driver use this architecture.

#### Figure 45. TS4604 voltage for one channel

Note:

The PVSSHP and PVSSLD voltages are generated internally by the internal negative supply. **To avoid damage to the TS4604, do not connect an external power supply on the PVSSHP and PVSSLD pins**.

## 6.2 Use of ceramic capacitors

We advise using ceramic capacitors for the decoupling, flying or tank capacitors because of their low ESR properties. The rated voltage of the ceramic capacitor, however, is an important parameter to take into consideration.

A 1  $\mu$ F/6.3 V capacitor used at 4.8 V DC typically loses about 40% of its value. In fact, with a 4.8 V power supply voltage, the decoupling value is about 0.6  $\mu$ F instead of 1  $\mu$ F. Because the decoupling capacitor influences the THD+N in the medium-to-high frequency region, this capacitor variation becomes decisive. In addition, less decoupling means higher overshoots, which can be problematic if they reach the power supply's AMR value (5.5 V).

This is why it is recommend to use a 1  $\mu$ F/10 V/X5R or a 2.2  $\mu$ F/6.3 V/X5R, or a new kind of ceramic capacitor with a low DC bias variation rated at 6.3 V.

If a 1  $\mu$ F/10 V ceramic capacitor is used, at 4.8 V the capacitance will be 0.82  $\mu$ F, C

If a 2.2  $\mu$ F/6.3 V ceramic capacitor is used, at 4.8 V the capacitance will be 1.1  $\mu$ F.

## 6.3 Flying and tank capacitor for the internal negative supply

The TS4604 embeds two independent internal negative supplies as shown in *Figure 1*. Each of them requires two capacitors to work properly (a flying and a tank capacitor). The internal negative supply capacitor must be correctly selected to generate an efficient negative voltage.

Two flying capacitors (CHP and CLD) of 1  $\mu$ F each with low ESR are recommended for internal negative power supply operation.

- CHP between pins 8 and 21.

- CLD between pins 7 and 22.

Two tank capacitors (CPvss\_HP and CPvss\_LD) of 1 µF each with low ESR are recommended for internal negative power supply energy storage.

- CPvss\_HP between pin 9 and ground.

- CPvss\_LD between pin 6 and ground.

An X5R dielectric for capacitor tolerance should be used. In order to take into consideration the  $\Delta C/\Delta V$  variation of this type of dielectric (see *Section 6.2* above), we also recommend:

- a 10 V DC rating voltage for 4.8 V power supply operation.

- a 6.3 V DC rating operation for 3.3 V power supply operation.

These capacitors must be placed as close as possible to the TS4604 to minimize parasitic inductance and resistance that have a negative impact on the audio performance.

## 6.4 Power supply decoupling capacitor (Cs)

A 1  $\mu$ F decoupling capacitor (Cs) with low ESR is mandatory for the positive power supply X5R dielectric for capacitor tolerance behavior. In order to take into consideration the  $\Delta$ C/ $\Delta$ V variation of this type of dielectric (see *Section 6.2* above), it is also recommended to use:

- a 10 V DC rating voltage for 4.8 V power supply operation.

- a 6.3 V DC rating operation for 3.3 V power supply operation.

These capacitors must be placed as close as possible to the TS4604 to minimize parasitic inductance and resistance that have a negative impact on the audio performance.

## 6.5 Input coupling capacitor (Cin)

An input coupling capacitor (Cin) might be used for TS4604 operation to block any DC component of the audio signal.

Cin starts to have an effect in the low frequency region. Cin forms with Rin a high-pass filter with a -3 dB cut-off frequency.

$$Fc(-3dB) = \frac{1}{2.\pi \cdot Rin \cdot Cin}(Hz)$$

#### **Example**

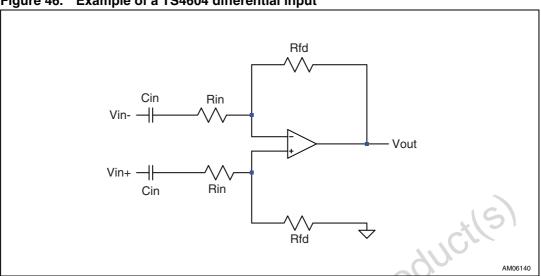

A differential input gain as shown in *Figure 46 on page 20* with the gain equalling 0 dB (Rin = 10 k $\Omega$ , Rfd = 10 k $\Omega$ ) and an input capacitor of 2.2 µF gives:

$$Fc = \frac{1}{2.\pi \cdot 10000 \cdot 2.2e10^{-6}} = 7.2Hz$$

The high-pass filter has a -3 dB cut-off frequency at 7.2 Hz in this case.

#### 6.6 Range of the gain setting resistors

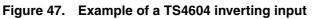

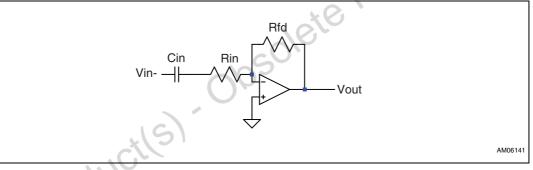

The TS4604 can be use in different configurations, as shown in figures 46, 47 and 48.

The gain is given by the external resistors Rfd divided by Rin. The feedback resistor Rfd does not exceed 100 k $\Omega$  for closed-loop stability reasons.

*Table 7* gives the recommended resistor values and the gain for different types of application.

|            | Rin           | Rfd           | Differential gain | Inverting gain | Non-inverting gain |

|------------|---------------|---------------|-------------------|----------------|--------------------|

| $\bigcirc$ | <b>1</b> 0 kΩ | 10 kΩ         | 0 dB              | 0 dB           | 6 dB               |

|            | 10 kΩ         | 20 kΩ         | 6 dB              | 6 dB           | 10 dB              |

|            | 10 kΩ         | 50 k $\Omega$ | 14 dB             | 14 dB          | 16 dB              |

|            | 4.7 kΩ        | 47 kΩ         | 20 dB             | 20 dB          | 21 dB              |

|            | 10 kΩ         | 100 kΩ        | 20 dB             | 20 dB          | 21 dB              |

Table 7. Recommended resistors values

Figure 46. Example of a TS4604 differential input

## 6.7 Performance of CMRR

When the TS4604 is used in differential mode (*Figure 46*), because of the resistor matching the CMRR can have important variations.

To minimize these variations, we recommend using the same kind of resistor (same tolerance).

The following equation is valid for frequencies ranging from DC to about kHz. The equation is simplified by neglecting the  $\Delta R^2$  terms.  $\Delta R$  is the tolerance value as a percentage.

$$CMRR \approx 20 \cdot log \left[\frac{100}{4\Delta R} \left(1 + \frac{Rfd}{Rin}\right)\right] (dB)$$

It is extremely important to correctly match the resistors to obtain a good CMRR.

All the tests have been performed with resistors with a tolerance value of 0.1%.

Example:

With  $\Delta R = 1\%$  the minimum CMRR would be 34 dB.

With  $\Delta R = 0.1\%$  the minimum CMRR would be 54 dB.

### 6.8 Internal and external undervoltage detection

The TS4604 embeds two UVLOs: one internal and one external.

#### 6.8.1 Internal UVLO

The internal UVLO monitors the power supply via pins PVCC\_HP (20) and PVCC\_LD(23). The threshold is set to 2.8 V with a 200 mV hysteresis. If the power supply decreases to 2.6 V, the TS4604 switches to standby mode. To switch the device on again, the power supply voltage must increase to above 2.8 V.

Refer to *Table 4* for the tolerance of the UVLO voltage.

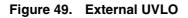

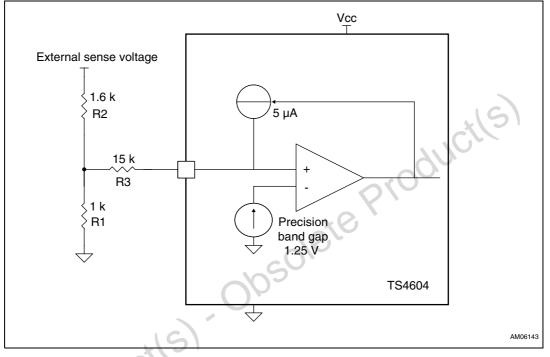

### 6.8.2 External UVLO

The Ex\_UVP pin (25) is an external undervoltage detection input that can be used to start up or shutdown the TS4604 by applying the correct voltage value. A 1.25 V internal precision voltage is used as a reference to monitor the voltage applied to the Ex\_UPVP pin.

To set a desired shutdown threshold and hysteresis for the application, a resistor divider can be calculated as follows.

$$Vuvp = 1.25V \cdot \frac{(R1 + R2)}{R1}$$

Vhyst

$$\approx 5\mu A \cdot R3 \cdot \left(\frac{R2}{R1} + 1\right)$$

with the condition R3>>R1//R2.

For example, to obtain Vuvp = 3.3 V with a hysteresis of 200 mV:

- R1 = 1 kΩ

- R2 = 1.6 kΩ

- R3 = 15 kΩ

When the external sense voltage (ESV) increases, the TS4604 stays in standby mode until the EUVP pin reaches 1.25 V (voltage across the divider R1, R2). At this point, the TS4604 starts, as does the internal 5  $\mu$ A current source connected to the EUVP pin. Thanks to this 5  $\mu$ A current, a voltage drop is created across the R3 resistor.

To switch the TS4604 back to standby, the voltage across the divider R1, R2 has to be lower than 1.25 V - VHyst  $\times$  R1/(R1 + R2). The ESV can be an external voltage or simply the power supply voltage PVcc\_LD/HD.

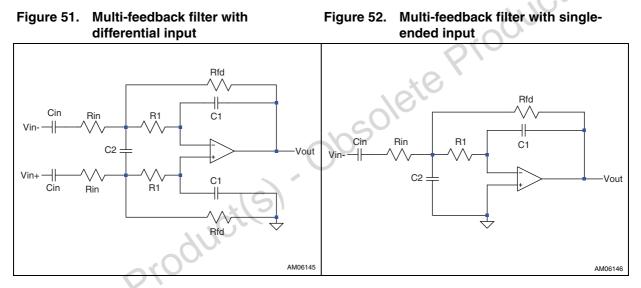

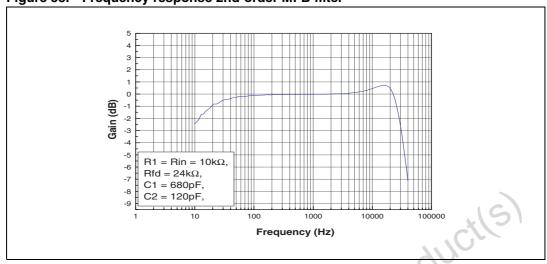

## 6.9 2nd order Butterworth low-pass filter

The TS4604 can also be configured as a low-pass filter to be driven directly by a DAC output. It can be used, for example, as a 2nd order low-pass filter, with either a differential input or a single-ended input.

*Figure 51* and *Figure 52* depict these two kinds of application and represent a multiple feedback 2nd order low-pass filter.

An AC-coupling capacitor should be added to block any DC component from the source, which helps to reduce the output DC offset to a minimum.

#### Example 2nd-order multi-feedback filter in differential mode

*Figure 53* shows a filter in differential mode with a cut-off frequency at 30 kHz (configured as per the values in *Table 8*, which proposes various filter options using a differential input).

ns

Figure 53. Frequency response 2nd-order MFB filter

| Table 8. | Recommended values for 2nd order low-pass filter |

|----------|--------------------------------------------------|

|          |                                                  |

| Low-pass filter | Rin           | R1    | Rfd   | C1     | C2     |

|-----------------|---------------|-------|-------|--------|--------|

| 25 kHz          | 10 k $\Omega$ | 10 kΩ | 15 kΩ | 1 nF   | 200 pF |

| 30 kHz          | 10 k $\Omega$ | 10 kΩ | 24 kΩ | 680 pF | 120 pF |

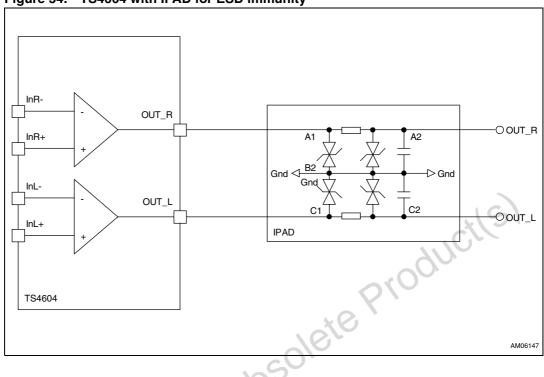

## 6.10 ESD protection and compliance

To provide excellent ESD immunity, an audio line IPAD<sup>(a)</sup> (STMicroelectronics reference EMIF04-EAR02M8) can be added at the output of the TS4604 (*Figure 54*).

By adding the IPAD, the TS4604 complies with the standard IEC 61000-4-2 level 4 on the external pins.

- OUT\_HPL and OUT\_HPR for the headphone driver.

- OUT\_LDL and OUT\_LDR for the Line driver.

a. Copyright ST Microelectronics.

Figure 54. TS4604 with IPAD for ESD immunity

## 6.11 Pop-&-click circuitry

Thanks to the internal negative supply the headphone and line driver outputs are referred to ground without the need for bulky in-series capacitors. As a result, the pop created by these bulky capacitors is eliminated. In addition, the TS4604 includes a pop-&-click circuitry that suppresses any residual pop on the outputs, thus enabling the outputs to be virtually pop-&-click-free.

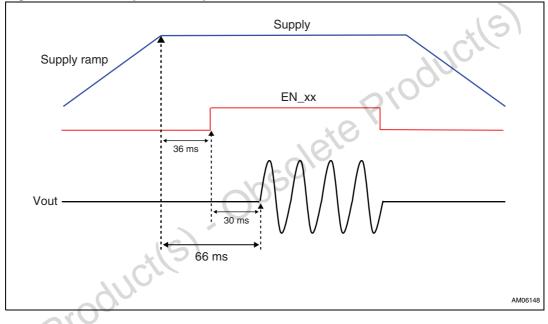

## 6.12 Start-up phase

To further improve the pop-&-click performance, two important points must be taken into account during the start-up phase.

#### Input capacitor

During the start up phase, as long as the AC input coupling capacitors are not fully charged, we suggested to remain the EN\_LD and En\_HP and/or Ext\_UVP pin low.

The constant time for an RC filter is given by:

$\tau = Rin \cdot Cin$

We can consider that the input capacitor Cin will be charged at 95% of its maximum value at:

$T = 3\tau$

With a gain set at G = 0 dB, a Rin = 10 k $\Omega$  and Cin = 2.2  $\mu$ F, to charge Cin to 95% of its final value, 66 ms are necessary.

#### Wake-up time of the TS4604

The TS4604 needs 30 ms to become fully operational (see *Table 5* and *Table 6*).

The total startup sequence with the settings described being 66 ms, and since the TS4604 needs 30 ms to wake up, the Enable pin for the line driver and/or headphone can be set high 36 ms after the power supply has reached its normal value (*Figure 55*).

With a lower input capacitance, the startup phase is quicker.

Figure 55. Power-up/down sequence

### 6.13 Layout recommendations

Particular attention must be given to the correct layout of the PCB traces and wires between the amplifier, load and power supply.

The power and ground traces are critical since they must provide adequate energy and grounding for all circuits. Good practice is to use short and wide PCB traces to minimize voltage drops and parasitic inductance.

Proper grounding guidelines help improve audio performances, minimize crosstalk between channels, and prevent switching noise from coupling into the audio signal. It is also recommended to use a large-area and multi-via ground plane to minimize parasitic impedance.

Connect all the V<sub>CC</sub> tracks (PVCCLD and PVCCHP) to one point one the board.

The copper traces that connect the output pins to the load and supply pins should be as wide as possible to minimize the trace resistances.

The gain setting resistors must be placed as close as possible to the input in order to minimize the parasitic capacitors on these inputs pins.

#### TS4604

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

obsolete Product(s). Obsolete Product(s)

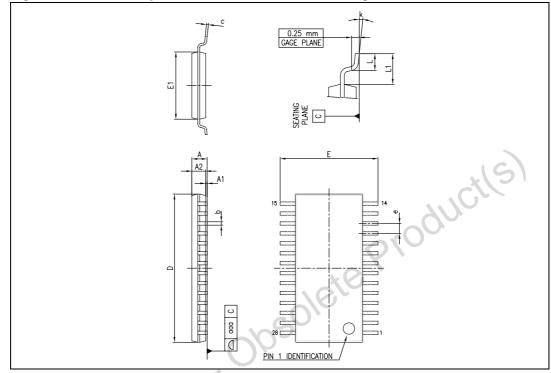

# 7.1 TSSOP28 package

#### Figure 56. TSSOP28 pitch 0.65 mm mechanical drawing

#### Table 9. TSSOP28 pitch 0.65 mm mechanical data

|     |      | , C  |             | Dime | nsions |        |       |  |

|-----|------|------|-------------|------|--------|--------|-------|--|

|     | Ref. | -90- | Millimeters |      |        | Inches |       |  |

|     | 20   | Min. | Тур.        | Max. | Min.   | Тур.   | Max.  |  |

|     | A    |      |             | 1.20 |        |        | 0.047 |  |

| 10  | A1   | 0.05 |             | 0.15 | 0.002  |        | 0.006 |  |

| c01 | A2   | 0.80 | 1.00        | 1.05 | 0.031  | 0.039  | 0.041 |  |

| 05  | b    | 0.19 |             | 0.30 | 0.007  |        | 0.011 |  |

| U.  | с    | 0.09 |             | 0.20 | 0.003  |        | 0.008 |  |

|     | D    | 9.60 | 9.70        | 9.80 | 0.378  | 0.382  | 0.386 |  |

|     | E    | 6.20 | 6.40        | 6.60 | 0.244  | 0.252  | 0.260 |  |

|     | E1   | 4.30 | 4.40        | 4.50 | 0.170  | 0.173  | 0.177 |  |

|     | е    |      | 0.65        |      |        | 0.026  |       |  |

|     | L    | 0.45 | 0.60        | 0.75 | 0.018  | 0.024  | 0.030 |  |

|     | L1   |      | 1.00        |      |        | 0.040  |       |  |

|     | k    | 0    |             | 8    |        |        |       |  |

|     | aaa  |      |             | 0.10 |        |        | 0.004 |  |

# 8 Ordering information

#### Table 10. Order codes

| Part number | Temperature<br>range | Gain     | Package | Marking |

|-------------|----------------------|----------|---------|---------|

| TS4604IPT   | -40°C, +85°C         | External | TSSOP28 | 4604    |

obsolete Product(s). Obsolete Product(s)

# 9 Revision history

#### Table 11. Document revision history

| Date        | Revision | Changes          |  |

|-------------|----------|------------------|--|

| 27-Oct-2010 | 1        | Initial release. |  |

obsolete Product(s). Obsolete Product(s)

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2010 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com