Document Number: SGTL5000

Rev. 6.0, 11/2013

# Low Power Stereo Codec with Headphone Amp

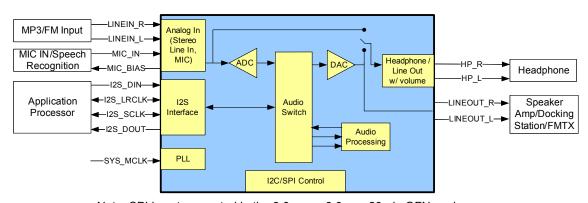

The SGTL5000 is a Low Power Stereo Codec with Headphone Amp from Freescale, and is designed to provide a complete audio solution for products needing LINEIN, MIC\_IN, LINEOUT, headphone-out, and digital I/O. Deriving it's architecture from best in class, Freescale integrated products that are currently on the market. The SGTL5000 is able to achieve ultra low power with very high performance and functionality, all in one of the smallest footprints available. Target markets include media players, navigation devices, smart phones, tablets, medical equipment, exercise equipment, consumer audio equipment, etc. Features such as capless headphone design and an internal PLL help lower overall system cost.

## **Features**

## **Analog Inputs**

- · Stereo LINEIN Support for external analog input

- · Stereo LINEIN Codec bypass for low power

- · MIC bias provided

- · Programmable MIC gain

- ADC 85 dB SNR (-60 dB input) and -73 dB THD+N (VDDA = 1.8 V)

## **Analog Outputs**

- · HP Output Capless design

- HP Output 62.5 mW max, 1.02 kHz sine into 16  $\Omega$  load at 3.3 V

- HP Output 100 dB SNR (-60 dB input) and -80 dB THD+N (V<sub>DDA</sub> = 1.8 V, 16 Ω load, DAC to headphone)

- LINEOUT 100 dB SNR (-60 dB input) and -85 dB THD+N (V<sub>DDIO</sub> = 3.3 V)

## Digital I/O

I<sup>2</sup>S port to allow routing to Application Processor

## **Integrated Digital Processing**

- Freescale surround, Freescale bass, tone control/ parametric equalizer/graphic equalizer clocking/control

- PLL allows input of an 8.0 MHz to 27 MHz system clock standard audio clocks are derived from PLL

## **Power Supplies**

Designed to operate from 1.62 to 3.6 volts

# **SGTL5000**

#### **AUDIO CODEC**

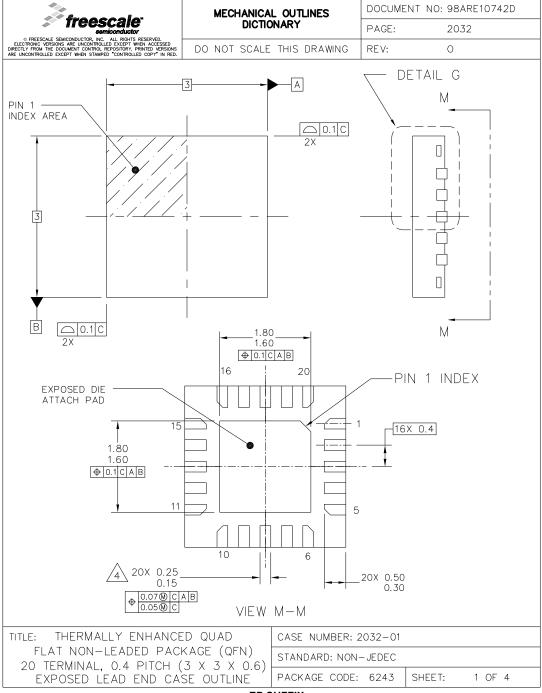

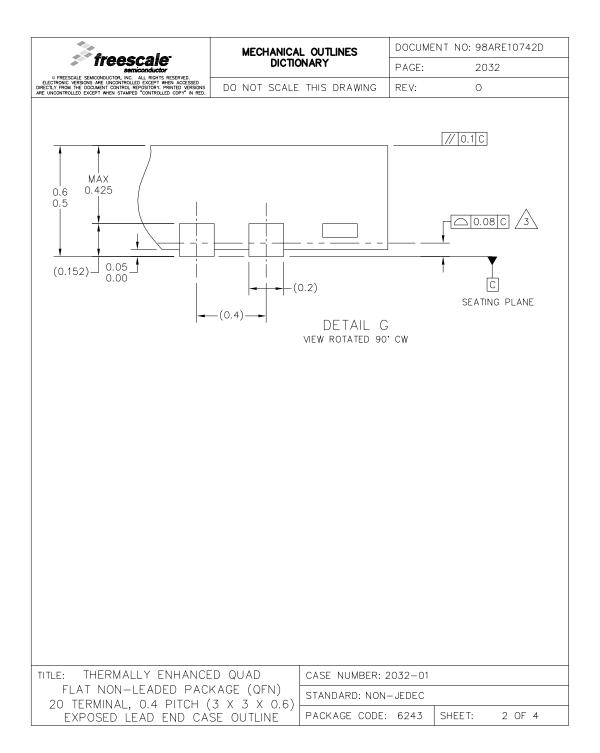

| ORDERING INFORMATION                               |              |        |  |  |  |

|----------------------------------------------------|--------------|--------|--|--|--|

| Device Temperature Range (T <sub>A</sub> ) Package |              |        |  |  |  |

| SGTL5000XNLA3/R2                                   | -40 to 85 °C | 20 QFN |  |  |  |

| SGTL5000XNAA3/R2                                   | -40 to 65 C  | 32 QFN |  |  |  |

Note: SPI is not supported in the 3.0 mm x 3.0 mm 20-pin QFN package

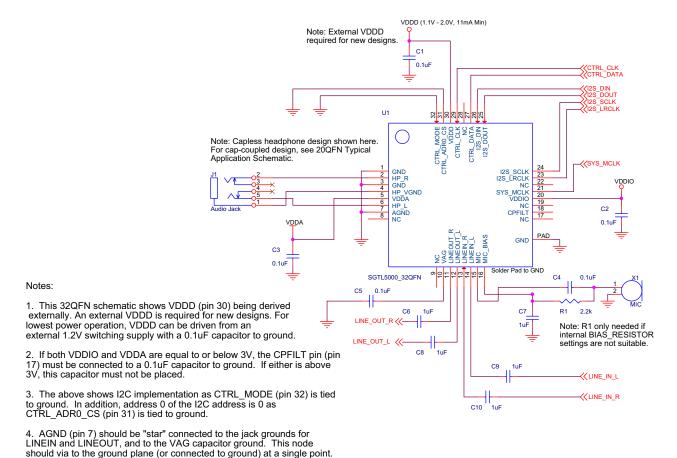

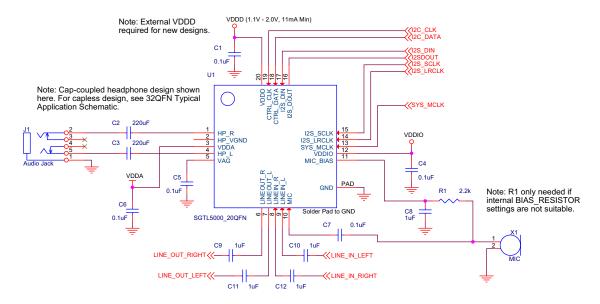

Figure 1. SGTL5000 Simplified Application Diagram

Freescale Semiconductor, Inc. reserves the right to change the detail specifications, as may be required, to permit improvements in the design of its products.

# INTERNAL BLOCK DIAGRAM

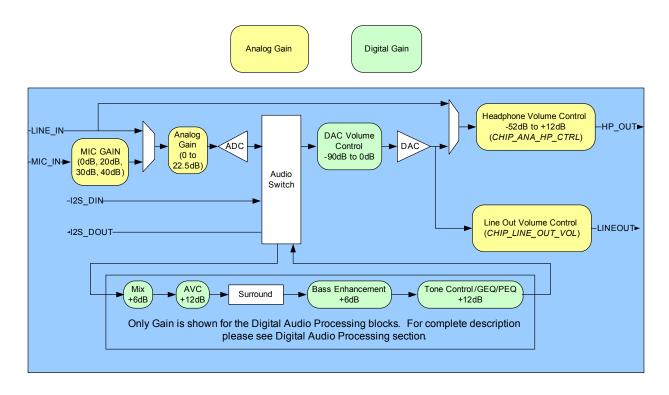

Figure 2. SGTL5000 Simplified Internal Block Diagram

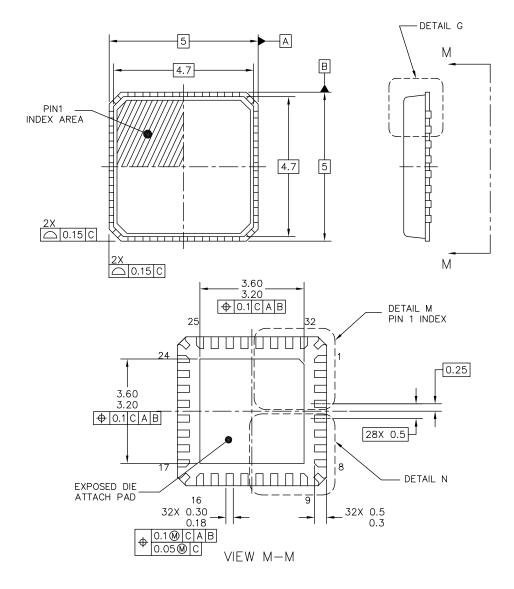

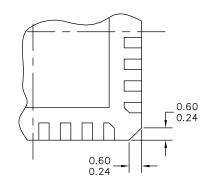

## **PIN CONNECTIONS**

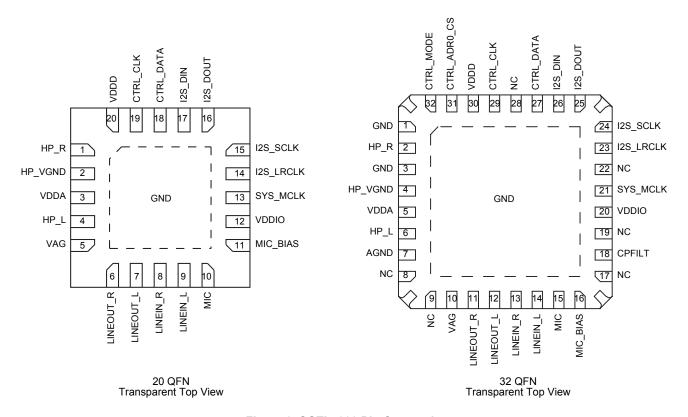

Figure 3. SGTL5000 Pin Connections

A functional description can be found in Functional Description, beginning on page 12.

Table 1. SGTL5000 Pin Definitions

| 20 Pin QFN | 32 Pin QFN              | Pin Name  | Pin<br>Function  | Formal Name              | Definition                                                                                                                                                                                                        |

|------------|-------------------------|-----------|------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | 2                       | HP_R      | Analog           | Right headphone output   |                                                                                                                                                                                                                   |

| 2          | 4                       | HP_VGND   | Analog           | Headphone virtual ground | Do not connect HP_VGND to system ground, even when unused. This is a virtual ground (DC voltage) that should never connect to an actual "0 Volt ground". Use the widest, shortest trace possible for the HP_VGND. |

| 3          | 5                       | VDDA      | Power            | Analog voltage           |                                                                                                                                                                                                                   |

| 4          | 6                       | HP_L      | Analog           | Left headphone output    |                                                                                                                                                                                                                   |

| -          | 7                       | AGND      | Analog<br>Ground | Ground                   |                                                                                                                                                                                                                   |

| -          | 8, 9, 17, 19,<br>22, 28 | NC        | No Connect       |                          |                                                                                                                                                                                                                   |

| 5          | 10                      | VAG       | Analog           | DAC VAG filter           |                                                                                                                                                                                                                   |

| 6          | 11                      | LINEOUT_R | Analog           | Right LINEOUT            |                                                                                                                                                                                                                   |

| 7          | 12                      | LINEOUT_L | Analog           | Left LINEOUT             |                                                                                                                                                                                                                   |

| 8          | 13                      | LINEIN_R  | Analog           | Right LINEIN             |                                                                                                                                                                                                                   |

| 9          | 14                      | LINEIN_L  | Analog           | Left LINEIN              |                                                                                                                                                                                                                   |

Table 1. SGTL5000 Pin Definitions (continued)

| 20 Pin QFN | 32 Pin QFN   | Pin Name     | Pin<br>Function | Formal Name                                                                                                                                         | Definition                                                                                                                                                                                           |

|------------|--------------|--------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10         | 15           | MIC          | Analog          | Microphone input                                                                                                                                    |                                                                                                                                                                                                      |

| 11         | 16           | MIC_BIAS     | Analog          | Mic bias                                                                                                                                            |                                                                                                                                                                                                      |

| _          | 18           | CPFILT       | Analog          | Charge Pump Filter                                                                                                                                  | The CPFILT cap value is 0.1 $\mu$ F. If both VDDIO and VDDA are $\leq$ 3.0 V, the CPFILT pin must be connected to a 0.1 $\mu$ F cap to GND. If either is > 3.0 V, the CPFILT cap MUST NOT be placed. |

| 12         | 20           | VDDIO        | Power           | Digital I/O voltage                                                                                                                                 |                                                                                                                                                                                                      |

| 13         | 21           | SYS_MCLK     | Digital         | System master clock                                                                                                                                 |                                                                                                                                                                                                      |

| 14         | 23           | I2S_LRCLK    | Digital         | I <sup>2</sup> S frame clock                                                                                                                        |                                                                                                                                                                                                      |

| 15         | 24           | I2S_SCLK     | Digital         | I <sup>2</sup> S bit clock                                                                                                                          |                                                                                                                                                                                                      |

| 16         | 25           | I2S_DOUT     | Digital         | I <sup>2</sup> S data output                                                                                                                        |                                                                                                                                                                                                      |

| 17         | 26           | I2S_DIN      | Digital         | I <sup>2</sup> S data input                                                                                                                         |                                                                                                                                                                                                      |

| 18         | 27           | CTRL_DATA    | Digital         | I <sup>2</sup> C Mode: Serial Data<br>(SDA); SPI Mode: Serial<br>Data Input (MOSI)                                                                  |                                                                                                                                                                                                      |

| 19         | 29           | CTRL_CLK     | Digital         | I <sup>2</sup> C Mode: Serial Clock<br>(SCL); SPI Mode: Serial<br>Clock (SCK)                                                                       |                                                                                                                                                                                                      |

| 20         | 30           | VDDD         | Digital         | Digital voltage                                                                                                                                     | For new designs, connect VDDD to an external voltage source and to a 0.1 µF capacitor to GND.                                                                                                        |

| -          | 31           | CTRL_ADR0_CS | Digital         | I <sup>2</sup> C Mode: I <sup>2</sup> C Address<br>Select 0; SPI Mode: SPI<br>Chip Select                                                           |                                                                                                                                                                                                      |

| -          | 32           | CTRL_MODE    | Digital         | Mode select for I <sup>2</sup> C or<br>SPI; When pulled low the<br>control mode is I <sup>2</sup> C, when<br>pulled high the control<br>mode is SPI |                                                                                                                                                                                                      |

| PAD        | 1, 3, 4, PAD | GND          | Ground          | Ground                                                                                                                                              | The PAD must be soldered to ground.  Star the ground pins of the chip, VAG ground, and all analog inputs/outputs to a single point, then to the ground plane.                                        |

# **ELECTRICAL CHARACTERISTICS**

## **MAXIMUM RATINGS**

## **Table 2. Maximum Ratings**

Exceeding the absolute maximum ratings shown in the following table could cause permanent damage to the part and is not recommended. Normal operation is not guaranteed at the absolute maximum ratings, and extended exposure could affect long term reliability.

| Ratings                              | Symbol            | Value                             | Unit |

|--------------------------------------|-------------------|-----------------------------------|------|

| ELECTRICAL RATINGS                   | 1                 |                                   |      |

| Maximum Digital Voltage              | V <sub>DDD</sub>  | 1.98                              | V    |

| Maximum Digital I/O Voltage          | V <sub>DDIO</sub> | 3.6                               | V    |

| Maximum Analog Supply Voltage        | V <sub>DDA</sub>  | 3.6                               | V    |

| Maximum voltage on any digital input |                   | GND-0.3 to V <sub>DDIO</sub> +0.3 | V    |

| Maximum voltage on any analog input  |                   | GND-0.3 to V <sub>DDA</sub> +0.3  | V    |

| THERMAL RATINGS                      |                   |                                   |      |

| Storage Temperature                  | T <sub>STG</sub>  | - 55 to 125                       | °C   |

| Operating Temperature                |                   |                                   | °C   |

| Ambient                              | T <sub>A</sub>    | -40 to 85                         |      |

## **Table 3. Recommended Operating Conditions**

| Ratings                                                                                      | Symbol           | Value       | Unit |

|----------------------------------------------------------------------------------------------|------------------|-------------|------|

| Digital Voltage (If supplied externally). External VDDD connection required for new designs. | V <sub>DDD</sub> | 1.1 to 2.0  | V    |

| Digital I/O Voltage                                                                          | $V_{DDIO}$       | 1.62 to 3.6 | V    |

| Analog Supply Voltage                                                                        | $V_{DDA}$        | 1.62 to 3.6 | V    |

# **Table 4. Input/Output Electrical Characteristics**

Test Conditions unless otherwise noted:  $V_{DDIO}$  = 3.3 V,  $V_{DDA}$  = 3.3 V,  $T_A$  = 25 °C, Slave mode,  $f_S$  = 48 kHz, MCLK = 256  $f_S$ , 24 bit input, 1.02 kHz sine.

| Characteristic                                                                          | Symbol | Min  | Тур        | Max                    | Unit            |

|-----------------------------------------------------------------------------------------|--------|------|------------|------------------------|-----------------|

| LINEIN Input Level (3.3 V VDDA)                                                         |        | -    | -          | 2.83                   | $V_{PP}$        |

| LINEIN Input Level (1.8 V VDDA)                                                         |        | -    | -          | 1.60                   | V <sub>PP</sub> |

| MIC Input Level (3.3 V VDDA)                                                            |        | -    | -          | 2.83                   | V <sub>PP</sub> |

| MIC Input Level (1.8 V VDDA)                                                            |        | -    | -          | 1.60                   | V <sub>PP</sub> |

| LINEOUT Output level                                                                    |        |      |            |                        | V <sub>PP</sub> |

| 0 dBFS at 1.031 kHz 12S input, 1.8 V LINEOUT supply (normally VDDIO), 10 kΩ load        |        | 1.46 | 1.52       | 1.68                   |                 |

| LINEOUT Output level                                                                    |        |      |            |                        | V <sub>PP</sub> |

| 0 dBFS at 1.031 kHz 12S input, 3.3 V LINEOUT supply (normally VDDIO), 10 $k\Omega$ load |        | 2.53 | 2.61       | 3.11                   |                 |

| LINEIN Input Impedance                                                                  |        | -    | 29         | -                      | kΩ              |

| MIC Input Impedance                                                                     |        | -    | 2.9        | -                      | kΩ              |

| LINEOUT Output Impedance                                                                |        | -    | 320        | -                      | Ω               |

| LINEOUT Load                                                                            |        | 10   | -          | -                      | kΩ              |

| HP (headphone) Load                                                                     |        | 16   | -          | -                      | Ω               |

| SYS_MCLK Input Voltage swing                                                            |        | -0.3 | $V_{DDIO}$ | V <sub>DDIO</sub> +0.3 | V               |

| SYS_MCLK Rise/Fall Time                                                                 |        | 0.5  | -          | 10                     | ns              |

## STATIC ELECTRICAL CHARACTERISTICS

Table 5. Audio Performance 1

Test Conditions unless otherwise noted:  $V_{DDIO}$  = 1.8 V,  $V_{DDA}$  = 1.8 V,  $T_A$  = 25 °C, Slave mode,  $f_S$  = 48 kHz, MCLK = 256  $f_S$ , 24 bit input

| Characteristic                                                 | Symbol                                         | Min | Тур   | Max | Unit             |

|----------------------------------------------------------------|------------------------------------------------|-----|-------|-----|------------------|

| AUDIO PERFORMANCE                                              | <u>,                                      </u> | •   | •     | •   | •                |

| LINEIN Input Level                                             |                                                | -   | 0.57  | -   | V <sub>RMS</sub> |

| LINEIN Input Impedance (at 1.02 kHz)                           |                                                | -   | 29    | -   | kΩ               |

| LINEIN -> ADC -> I <sup>2</sup> S OUT                          |                                                | -   | -1    |     | •                |

| SNR (-60 dB input)                                             |                                                | -   | 85    | -   | dB               |

| THD+N                                                          |                                                | -   | -70   | -   | dB               |

| Frequency Response                                             |                                                | -   | ±0.11 | -   | dB               |

| Channel Separation                                             |                                                | -   | 79    | -   | dB               |

| LINEIN -> HEADPHONE_LINEOUT (CODEC BYPASS MODE)                |                                                | -   | -1    |     | •                |

| SNR (-60 dB input)                                             |                                                | -   | 98    | -   | dB               |

| THD+N (10 kΩ load)                                             |                                                | -   | -87   | -   | dB               |

| THD+N (16 $\Omega$ load)                                       |                                                | -   | -87   | -   | dB               |

| Frequency Response                                             |                                                | -   | ±0.05 | -   | dB               |

| Channel Separation (at 1.0 kHz)                                |                                                |     | 82    |     | dB               |

| I <sup>2</sup> S IN -> DAC -> LINEOUT                          | •                                              |     |       |     |                  |

| Output Level                                                   |                                                | -   | 0.6   | -   | V <sub>RMS</sub> |

| SNR (-60 dB input)                                             |                                                | -   | 95    | -   | dB               |

| THD+N                                                          |                                                | -   | -85   | -   | dB               |

| Frequency Response                                             |                                                | -   | ±0.12 | -   | dB               |

| I <sup>2</sup> S IN -> DAC -> HEADPHONE OUT - 16 $\Omega$ LOAD | •                                              |     |       |     |                  |

| Output Power                                                   |                                                | -   | 17    | -   | mW               |

| SNR (-60 dB input)                                             |                                                | -   | 100   | -   | dB               |

| THD+N                                                          |                                                | -   | -80   | -   | dB               |

| Frequency Response                                             |                                                | -   | ±0.12 | -   | dB               |

| I <sup>2</sup> S IN -> DAC -> HEADPHONE OUT - 32 $\Omega$ LOAD |                                                |     |       |     |                  |

| Output Power                                                   |                                                | -   | 10    | -   | mW               |

| SNR (-60 dB input)                                             |                                                | -   | 95    | -   | dB               |

| THD+N                                                          |                                                | -   | -86   | -   | dB               |

| Frequency Response                                             |                                                | -   | ±0.11 | -   | dB               |

| I <sup>2</sup> S IN -> DAC -> HEADPHONE OUT - 10 KΩ LOAD       |                                                |     |       |     |                  |

| SNR (-60 dB input)                                             |                                                | -   | 96    | -   | dB               |

| THD+N                                                          |                                                | -   | -84   | -   | dB               |

| Frequency Response                                             |                                                | -   | ±0.11 | -   | dB               |

| PSRR (200 mVp-p at 1.0 kHz on VDDA)                            |                                                | -   | 85    | -   | dB               |

|                                                                |                                                | •   | •     | •   | •                |

Table 6. Audio Performance 2

Test Conditions unless otherwise noted:  $V_{DDIO}$  = 3.3 V,  $V_{DDA}$  = 3.3 V,  $T_{A}$  = 25°C, Slave mode,  $f_{S}$  = 48 kHz, MCLK = 256  $f_{S}$ , 24 bit input. ADC tests were conducted with BIAS\_CTRL = -37.5%, all other tests conducted with BIAS\_CTRL = -50%.

| Characteristic                                           | Symbol   | Min | Тур   | Max | Unit             |

|----------------------------------------------------------|----------|-----|-------|-----|------------------|

| AUDIO PERFORMANCE                                        | 1        |     |       |     | •                |

| LINEIN Input Level                                       |          | -   | 1.0   | -   | V <sub>RMS</sub> |

| LINEIN Input Impedance (at 1.02 kHz)                     |          | -   | 29    | -   | kΩ               |

| LINEIN -> ADC -> I <sup>2</sup> S OUT                    |          | II. | II.   | l   |                  |

| SNR (-60 dB input)                                       |          | -   | 90    | -   | dB               |

| THD+N                                                    |          | -   | -72   | -   | dB               |

| Frequency Response                                       |          | -   | ±0.11 | -   | dB               |

| Channel Separation                                       |          | -   | 80    | -   | dB               |

| LINEIN -> HEADPHONE_LINEOUT (CODEC BYPASS MOD            | DE)      | 1   | 1     |     | •                |

| SNR (-60 dB input)                                       |          | -   | 102   | -   | dB               |

| THD+N (10 kΩ load)                                       |          | -   | -89   | -   | dB               |

| THD+N (16 Ω load)                                        |          | -   | -87   | -   | dB               |

| Frequency Response                                       |          | -   | ±0.05 | -   | dB               |

| Channel Separation (at 1.0 kHz)                          |          |     | 81    |     | dB               |

| I <sup>2</sup> S IN -> DAC -> LINEOUT                    | <u> </u> |     |       |     |                  |

| Output Level                                             |          | -   | 1.0   | -   | V <sub>RMS</sub> |

| SNR (-60 dB input)                                       |          | -   | 100   | -   | dB               |

| THD+N                                                    |          | -   | -85   | -   | dB               |

| Frequency Response                                       |          | -   | ±0.12 | -   | dB               |

| I $^2$ S IN -> DAC -> HEADPHONE OUT - 16 $\Omega$ LOAD   |          |     |       |     |                  |

| Output Power                                             |          | -   | 58    | -   | mW               |

| SNR (-60 dB input)                                       |          | -   | 98    | -   | dB               |

| THD+N                                                    |          | -   | -86   | -   | dB               |

| Frequency Response                                       |          | -   | ±0.12 | -   | dB               |

| I $^2$ S IN -> DAC -> HEADPHONE OUT - 32 $\Omega$ LOAD   |          |     |       |     |                  |

| Output Power                                             |          | -   | 30    | -   | mW               |

| SNR (-60 dB input)                                       |          | -   | 100   | -   | dB               |

| THD+N                                                    |          | -   | -88   | -   | dB               |

| Frequency Response                                       |          | -   | ±0.11 | -   | dB               |

| I <sup>2</sup> S IN -> DAC -> HEADPHONE OUT - 10 KΩ LOAD |          |     |       |     |                  |

| SNR (-60 dB input)                                       |          | -   | 97    | -   | dB               |

| THD+N                                                    |          | -   | -85   | -   | dB               |

| Frequency Response                                       |          | -   | ±0.11 | -   | dB               |

| PSRR (200 mVp-p at 1.0 kHz on VDDA)                      |          | -   | 89    | -   | dB               |

## **DYNAMIC ELECTRICAL CHARACTERISTICS**

**Table 7. Dynamic Electrical Characteristics**

| Characteristic                                                                                 | Symbol               | Min                | Тур                                            | Max | Unit |

|------------------------------------------------------------------------------------------------|----------------------|--------------------|------------------------------------------------|-----|------|

| POWER UP TIMING                                                                                |                      | l.                 |                                                |     |      |

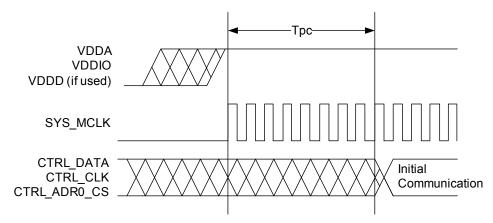

| Time from all supplies powered up and SYS_MCLK present to initial communication. See Figure 4. | t <sub>PC</sub>      | 1.0 <sup>(2)</sup> | -                                              | -   | μS   |

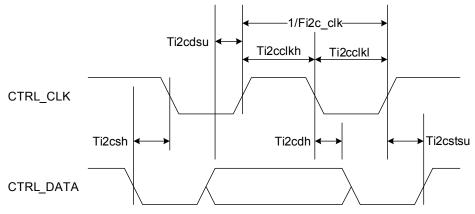

| I2C BUS TIMING <sup>(3)</sup> See <u>Figure 5</u> .                                            | -1                   | 1                  |                                                |     | •    |

| I <sup>2</sup> C Serial Clock Frequency                                                        | f <sub>I2C_CLK</sub> | -                  | -                                              | 400 | kHz  |

| I <sup>2</sup> C Start condition hold time                                                     | t <sub>I2CSH</sub>   | 150                | -                                              | -   | ns   |

| I <sup>2</sup> C Stop condition setup time                                                     | t <sub>I2CSTSU</sub> | 150                | -                                              | -   | ns   |

| I <sup>2</sup> C Data input setup time to rising edge of CTRL_CLK                              | t <sub>I2CDSU</sub>  | 125                | -                                              | -   | ns   |

| I <sup>2</sup> C Data input hold time from falling edge of CTRL_CLK (receiving data)           | t <sub>I2CDH</sub>   | 5.0                | -                                              | -   | ns   |

| I <sup>2</sup> C Data input hold time from falling edge of CTRL_CLK (driving data)             | t <sub>I2CDH</sub>   | 360                | -                                              | -   | ns   |

| I <sup>2</sup> C CTRL_CLK low time                                                             | t <sub>I2CCLKL</sub> | 300                | -                                              | -   | ns   |

| I <sup>2</sup> C CTRL_CLK high time                                                            | t <sub>I2CCLKH</sub> | 100                | -                                              | -   | ns   |

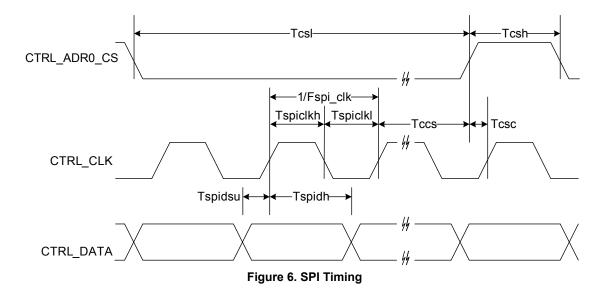

| SPI BUS TIMING <sup>(4)</sup> See <u>Figure 6</u> .                                            |                      |                    |                                                |     |      |

| SPI Serial Clock Frequency                                                                     | f <sub>SPI_CLK</sub> | -                  | -                                              | TBD | MHz  |

| SPI data input setup time                                                                      | t <sub>SPIDSU</sub>  | 10                 | -                                              | -   | ns   |

| SPI data input hold time                                                                       | t <sub>SPIDH</sub>   | 10                 | -                                              | -   | ns   |

| SPI CTRL_CLK low time                                                                          | t <sub>SPICLKL</sub> | TBD                | -                                              | -   | ns   |

| SPI CTRL_CLK high time                                                                         | t <sub>SPICLKH</sub> | TBD                | -                                              | -   | ns   |

| SPI clock to chip select                                                                       | t <sub>CCS</sub>     | 60                 | -                                              | -   | ns   |

| SPI chip select to clock                                                                       | t <sub>CSC</sub>     | 20                 | -                                              | -   | ns   |

| SPI chip select low                                                                            | t <sub>CSL</sub>     | 20                 | -                                              | -   | ns   |

| SPI chip select high                                                                           | t <sub>CSH</sub>     | 20                 |                                                |     | ns   |

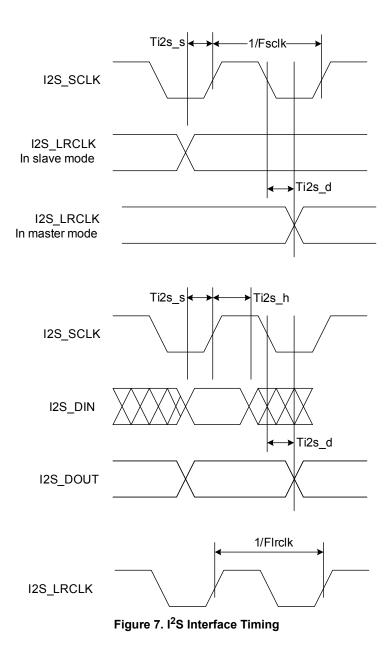

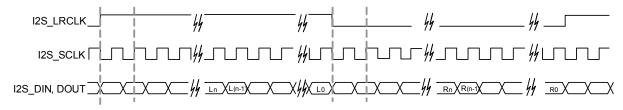

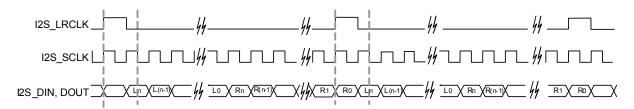

| SPECIFICATIONS AND TIMING FOR THE I <sup>2</sup> S PORT <sup>(5)</sup> See Figure 7.           |                      | 1                  | <u>'</u>                                       |     | 1    |

| Frequency of I <sup>2</sup> S_LRCLK                                                            | f <sub>LRCLK</sub>   | 8.0                | -                                              | 96  | kHz  |

| Frequency of I <sup>2</sup> S_SCLK                                                             | f <sub>SCLK</sub>    | -                  | 32*f <sub>LRCLK</sub><br>64*f <sub>LRCLK</sub> | -   | kHz  |

| I <sup>2</sup> S delay                                                                         | t <sub>I2S_D</sub>   | -                  | -                                              | 10  | ns   |

| I <sup>2</sup> S setup time                                                                    | t <sub>I2S_S</sub>   | 10                 | -                                              | -   | ns   |

| I <sup>2</sup> S hold time                                                                     | t <sub>I2S_H</sub>   | 10                 | -                                              | -   | ns   |

## Notes

- 1. The SGTL5000 has an internal reset that is deasserted 8 SYS\_MCLK cycles after all power rails have been brought up. After this time, communication can start.

- 2.  $1.0\mu s$  represents 8 SYS\_MCLK cycles at the minimum 8.0 MHz SYS\_MCLK.

- 3. This section provides timing for the SGTL5000 while in  $I^2C$  mode (CTRL\_MODE = 0).

- 4. This section provides timing for the SGTL5000 while in SPI mode (CTRL\_MODE = 1)

- 5. The following are the specifications and timing for I<sup>2</sup>S port. The timing applies to all formats.

## **TIMING DIAGRAMS**

Figure 4. Power Up Timing

Figure 5. I<sup>2</sup>C Timing (CTRL\_MODE == 0)

## **FUNCTIONAL DESCRIPTION**

## **INTRODUCTION**

The SGTL5000 is a low power stereo codec with integrated headphone amplifier. It is designed to provide a complete audio solution for portable products needing LINEIN, mic-in, LINEOUT, headphone-out, and digital I/O. Deriving it's architecture from best in class Freescale integrated products that are currently on the market, the SGTL5000 is able to achieve ultra low power with very high performance and functionality, all in one of the smallest footprints available. Target markets include portable media players, GPS units and smart phones. Features such as capless headphone design and USB clocking mode (12 MHz SYS MCLK input) help lower overall system cost.

In summary, the SGTL5000 accepts the following inputs:

- · Line input

- · Microphone input, with mic bias

- Digital I<sup>2</sup>S input

In addition, the SGTL5000 supports the following outputs:

- · Line output

- · Headphone output

- Digital I<sup>2</sup>S output

The following digital audio processing is included to allow for product differentiation:

- · Digital mixer

- Freescale Surround

- Freescale Bass Enhancement

- Tone Control, parametric equalizer, or graphic equalizer

The SGTL5000 can accept an external standard master

clock at a multiple of the sampling frequency (i.e. 256\*Fs, 385\*Fs, 512\*Fs). In addition it can take non-standard frequencies and use the internal PLL to derive the audio clocks. The device supports 8.0 kHz, 11.025 kHz, 12 kHz, 16 kHz, 22.05 kHz, 24 kHz, 32 kHz, 44.1kHz, 48 kHz, 96 kHz sampling frequencies.

## FUNCTIONAL INTERNAL BLOCK DESCRIPTION

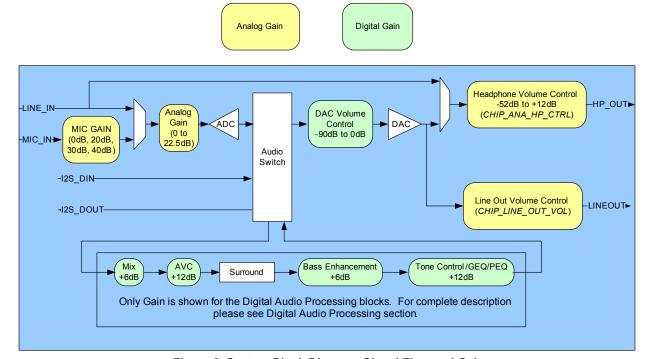

# SYSTEM BLOCK DIAGRAM W/ SIGNAL FLOW AND GAIN MAP

<u>Figure 8</u> shows a block diagram that highlights the signal flow and gain map for the SGTL5000.

To guarantee against clipping, it is important that the gain in a signal path in addition to the signal level does not exceed 0 dB at any point.

Figure 8. System Block Diagram, Signal Flow and Gain

## **POWER**

The SGTL5000 has a flexible power architecture to allow the system designer to minimize power consumption and maximize performance at the lowest cost.

## **External Power Supplies**

The SGTL5000 requires 2 external power supplies: VDDA and VDDIO. An optional third external power supply VDDD may be provided externally to achieve lower power. This external VDDD power supply is required for new designs. A description for the different power supplies is as follows:

- VDDA: This external power supply is used for the internal analog circuitry including ADC, DAC, LINE inputs, MIC inputs, headphone outputs and reference voltages. VDDA supply ranges are shown in Maximum Ratings. A decoupling cap should be used on VDDA, as shown in the typical application diagrams in Typical Applications.

- VDDIO: This external power supply controls the digital I/O levels as well as the output level of LINE outputs. VDDIO supply ranges are shown in Maximum Ratings. A decoupling cap should be used on VDDIO as shown in the typical application diagrams in Typical Applications.

Note that if VDDA and VDDIO are derived from the same voltage, a single decoupling capacitor can be used to minimize cost. This capacitor should be placed closest to VDDA.

VDDD: This is a digital power supply that is used for internal digital circuitry. An external VDDD power supply is required for new designs. For lowest power, this supply can be driven at the lowest specified voltage given in Maximum Ratings. If an external supply is used for VDDD, a decoupling capacitor is recommended, as shown in the typical applications diagram. VDDD supply ranges are shown in Maximum Ratings for when externally driven. If the system drives VDDD externally, an efficient switching supply should be used or no system power savings is realized.

## **Internal Power Supplies**

The SGTL5000 has two exposed internal power supplies, VAG and charge pump.

- VAG is the internal voltage reference for the ADC and DAC. After startup the voltage of VAG should be set to VDDA/2 by writing CHIP\_REF\_CTRL->VAG\_VAL. Refer to programming Chip Powerup and Supply Configurations. The VAG pin should have an external filter capacitor as shown in the typical application diagram.

- Chargepump: This power supply is used for internal analog switches. If VDDA or VDDIO is greater than 2.7 V, this supply is automatically driven from the highest of

VDDIO and VDDA. If both VDDIO and VDDA are less than 3.1 V, then the user should turn on the charge pump function to create the charge pump rail from VDDIO by writing CHIP\_ANA\_POWER-> VDDC\_CHRGPMP\_POWERUP register. Refer to programming Chip Powerup and Supply Configurations.

LINE\_OUT\_VAG is the line output voltage reference. It should be set to VDDIO/2 by writing CHIP\_LINE\_OUT\_CTRL->LO\_VAGCNTRL.

#### **Power Schemes**

The SGTL5000 supports a flexible architecture and allows the system designer to minimize power or maximize BOM savings.

- For maximum cost savings, all supplies can be run at the same voltage.

- Alternatively for minimum power, the analog and digital supplies can be run at minimum voltage while driving the digital I/O voltage at the voltage needed by the system.

- To save power, independent supplies are provided for line outputs and headphone outputs. This allows for 1VRMS line outputs while using minimal headphone power.

- For best power, VDDA should be run at the lowest possible voltage required for the maximum headphone output level. For highest performance, VDDA should be run at 3.3 V. For most applications a lower voltage can be used for the best performance/power combination.

## **RESET**

The SGTL5000 has an internal reset that is deasserted 8 SYS\_MCLKs after all power rails have been brought up. After this time communication can start. See Dynamic Electrical Characteristics.

### **CLOCKING**

Clocking for the SGTL5000 is provided by a system master clock input (SYS\_MCLK). SYS\_MCLK should be synchronous to the sampling rate (Fs) of the I<sup>2</sup>S port. Alternatively any clock between 8.0 and 27 MHz can be provided on SYS\_MCLK and the SGTL5000 can use an internal PLL to derive all internal and I<sup>2</sup>S clocks. This allows the system to use an available clock such as 12 MHz (common USB clock) for SYS\_MCLK to reduce overall system costs.

## Synchronous SYS\_MCLK input

The SGTL5000 supports various combinations of SYS\_MCLK frequency and sampling frequency as shown in Table 8. Using a synchronous SYS\_MCLK allows for lower power as the internal PLL is not used.

Table 8. Synchronous MCLK Rates and Sampling Frequencies

| CLOCK                          | SUPPORTED RATES                                               | UNITS |

|--------------------------------|---------------------------------------------------------------|-------|

| System Master Clock (SYS_MCLK) | 256, 384, 512                                                 | Fs    |

| Sampling Frequency (Fs)        | 8, 11.025, 12, 16, 22.05, 24, 32, 44.1, 48, 96 <sup>(6)</sup> | kHz   |

#### Notes

6. For a sampling frequency of 96 kHz, only 256 Fs SYS MCLK is supported

## Using the PLL - Asynchronous SYS\_MCLK input

An integrated PLL is provided in the SGTL5000 that allows any clock from 8.0 to 27 MHz to be connected to SYS\_MCLK. This can help save system costs, as a clock available elsewhere in the system can be used to derive all audio clocks using the internal PLL. In this case, the clock input to SYS\_MCLK can be asynchronous with the sampling frequency needed in the system. For example, a 12 MHz

clock from the system processor could be used as the clock input to the SGTL5000.

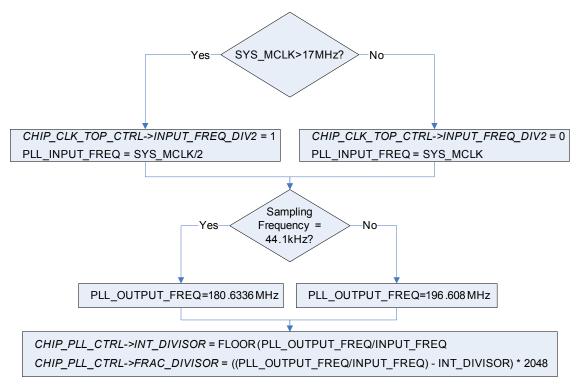

Three register fields need to be configured to properly use the PLL. They are CHIP\_PLL\_CTRL->INT\_DIVISOR, CHIP\_PLL\_CTRL->FRAC\_DIVISOR and CHIP\_CLK\_TOP\_CTRL->INPUT\_FREQ\_DIV2. Figure 9 shows a flowchart that shows how to determine the values to program in the register fields.

Figure 9. PLL Programming Flowchart

For example, when a 12 MHz digital signal is placed on MCLK, for a 48 kHz frame clock

CHIP\_CLK\_TOP\_CTRL->INPUT\_FREQ\_DIV2 = 0 // SYS\_MCLK < 17 MHz

CHIP\_PLL\_CTRL->INT\_DIVISOR = FLOOR (196.608 MHz/12 MHz) = 16 (decimal)

CHIP\_PLL\_CTRL->FRAC\_DIVISOR = ((196.608 MHz/ 12 MHz) - 16) \* 2048 = 786 (decimal)

Refer to PLL programming PLL Configuration.

## **AUDIO SWITCH (SOURCE SELECT SWITCH)**

The audio switch is the central routing block that controls the signal flow from input to output. Any single input can be routed to any single or multiple outputs.

Any signal can be routed to the Digital Audio Processor (DAP). The output of the DAP (an input to the audio switch) can in turn be routed to any physical output. The output of the DAP can not be routed into itself. Refer to Digital Audio Processing, for DAP information and configuration.

It should be noted that the analog bypass from Line input to headphone output does not go through the audio switch.

To configure a route, the *CHIP\_SSS\_CTRL* register is used. Each output from the source select switch has its own register field that is used to select what input is routed to that output.

For example, to route the I<sup>2</sup>S digital input through the DAP and then out to the DAC (headphone) outputs write SSS\_CTRL->DAP\_SELECT to 0x1 (selects I2S\_IN) and SSS\_CTRL->DAC\_SELECT to 0x3 (selects DAP output).

## **ANALOG INPUT BLOCK**

The analog input block contains a stereo line input and a microphone input with mic bias. Either input can be routed to the ADC. The line input can also be configured to bypass the CODEC and be routed directly to the headphone output.

## **Line Inputs**

One stereo line input is provided for connection to line sources such as an FM radio or MP3 input.

The source should be connected to the left and right line inputs through series coupling capacitors. The suggested value is shown in the typical application diagram in Typical Applications.

As detailed in ADC, the line input can be routed to the ADC.

The line input can also be routed to the headphone output by writing CHIP\_ANA\_CTRL->SELECT\_HP. This selection bypasses the ADC and audio switch and routes the line input directly to the headphone output to enable a very low power pass through.

## **Microphone Input**

One mono microphone input is provided for uses such as voice recording.

Mic bias is provided. The mic bias is programmed with the CHIP\_MIC\_CTRL->BIAS\_VOLT register field. Values from 1.25 V to 3.00 V are supported in 0.25 V steps. Mic bias should be set less than 200 mV from VDDA, e.g. with VDDA at 1.70 V, Mic bias should be set no greater than 1.50 V.

The microphone should be connected through a series coupling capacitor. The suggested value is shown in the typical connection diagram.

The microphone has programmable gain through the *CHIP\_MIC\_CTRL->GAIN* register field. Values of 0 dB, +20 dB, +30 dB and +40 dB are available.

## **ADC**

The SGTL5000 contains an ADC, which takes its input from either the line input or a microphone. The register field CHIP\_ANA\_CTRL->SELECT\_ADC controls this selection. The output of the ADC feeds the audio switch.

The ADC has its own analog gain stage that provides 0 to +22.5 dB of gain in 1.5 dB steps. A bit is available that shifts this range down by 6.0 dB to effectively provide -6.0 dB to

+16.5 dB of gain. The ADC gain is controlled in the CHIP\_ANA\_ADC\_CTRL register.

The ADC has an available zero cross detect (ZCD) that prevents any volume change until a zero-volt crossing of the audio signal is detected. This helps in eliminating pop or other audio anomalies. If the ADC is to be used, the chip reference bias current should not be set to -50% when in 3.0 V mode.

## **ANALOG OUTPUTS**

The SGTL5000 contains a single stereo DAC that can be used to drive a headphone output and a line output. The DAC receives its input from the audio switch. The headphone output and the line output can be driven at the same time from the DAC.

The headphone output can also be driven directly by the line input bypassing the ADC and DAC for a very low power mode of operation.

The headphone output is powered by VDDA while the line output is powered by VDDIO. This allows the headphone output to be run at the lowest possible voltage while the line output can still meet line output level requirements.

#### DAC

The DAC output is routed to the headphone and the dedicated line output.

The DAC output has a digital volume control from -90 dB to 0 dB in ~0.5 dB step sizes. This volume is shared among headphone output and line output. The register CHIP\_DAC\_VOL controls the DAC volume.

## Headphone

Stereo headphone outputs are provided which can be used to drive a headphone load or a line level output. The headphone output has its own independent analog volume control with a volume range of -52 dB to +12 dB in 0.5 dB step sizes. This volume control can be used in addition to the DAC volume control. For best performance the DAC volume control should be left at 0 dB until the headphone is brought to its lowest setting of -52 dB. The register CHIP\_ANA\_HP\_CTRL is used to control the headphone volume.

The headphone output has an independent mute that is controlled by the register field CHIP\_ANA\_CTRL->MUTE\_HP.

The line input is routed to the headphone output by writing CHIP\_ANA\_CTRL->SELECT\_HP. This selection bypasses the ADC and audio switch and routes the line input directly to the headphone output to enable a very low power pass through. When the line input is routed to the headphone output, only the headphone analog volume and mute affects the headphone output.

The headphone has an available zero cross detect (ZCD) which, as previously described, prevents any volume change until a zero-volt crossing of the audio signal is detected. This helps in eliminating pop or other audio anomalies.

# FUNCTIONAL DESCRIPTION FUNCTIONAL INTERNAL BLOCK DESCRIPTION

## **Line Outputs**

The SGTL5000 contains a stereo line output. The line output has a dedicated gain stage that can be used to adjust the output level. The CHIP\_LINE\_OUT\_VOL controls the line level output gain.

The line outputs also have a dedicated mute that is controlled by the register field CHIP\_ANA\_CTRL->MUTE\_LO.

The line out volume is intended as maximum output level adjustment. It is intended to be used to set the maximum output swing. It does not have the range of a typical volume control and does not have a zero cross detect (ZCD). However the DAC digital volume could be used if volume control is desired.

## **FUNCTIONAL DEVICE OPERATION**

## **POWER CONSUMPTION**

Table 9. Power Consumption: V<sub>DDA</sub>=1.8 V, V<sub>DDIO</sub>=1.8 V

| MODE                                                                      | CURR             | DOMED (MIM)      |                   |            |

|---------------------------------------------------------------------------|------------------|------------------|-------------------|------------|

| MODE                                                                      | V <sub>DDD</sub> | V <sub>DDA</sub> | V <sub>DDIO</sub> | POWER (MW) |

| Playback (I <sup>2</sup> S->DAC->Headphone)                               | -                | 2.54             | 0.9               | 6.19       |

| Playback with DAP ((I <sup>2</sup> S->DAP->DAC->Headphone)                | -                | 3.59             | 0.9               | 8.08       |

| Playback/Record (I <sup>2</sup> S->DAC->Headphone, ADC->I <sup>2</sup> S) | -                | 3.71             | 1.10              | 8.67       |

| Record (ADC->I <sup>2</sup> S)                                            | -                | 2.29             | 1.06              | 6.02       |

| Analog playback, CODEC bypassed (LINEIN->HP)                              | -                | 1.48             | 0.89              | 4.27       |

| Standby, all analog power off                                             | -                | 0.019            | 0.002             | 0.038      |

| Playback with PLL (I <sup>2</sup> S->DAC->HP)                             | -                | 3.01             | 2.17              | 9.31       |

$V_{DDD}$  derived internally at 1.2 V, slave mode except for PLL case, 32  $\Omega$  load on HP, Conditions: -100 dBFs signal

input, slave mode unless otherwise noted, paths tested as indicated, unused paths turned off.

Table 10. Power Consumption: V<sub>DDA</sub>=3.3 V, V<sub>DDIO</sub>=3.3 V

| MODE                                                                      | CURR             | DOWED/MW/        |                   |           |

|---------------------------------------------------------------------------|------------------|------------------|-------------------|-----------|

| MODE                                                                      | V <sub>DDD</sub> | V <sub>DDA</sub> | V <sub>DDIO</sub> | POWER(MW) |

| Playback (I <sup>2</sup> S->DAC->Headphone)                               | -                | 3.45             | 0.067             | 11.60     |

| Playback with DAP ((I <sup>2</sup> S->DAP->DAC->Headphone)                | -                | 4.49             | 0.067             | 15.03     |

| Playback/Record (I <sup>2</sup> S->DAC->Headphone, ADC->I <sup>2</sup> S) | -                | 4.67             | 0.343             | 16.53     |

| Record (ADC->I <sup>2</sup> S)                                            | -                | 2.90             | 0.296             | 10.56     |

| Analog playback, CODEC bypassed (LINEIN->HP)                              | -                | 1.91             | 0.039             | 6.43      |

| Standby, all analog power off                                             | -                | 0.04             | 0.002             | 0.139     |

| Playback with PLL (I <sup>2</sup> S->DAC->HP)                             | -                | 3.92             | 2.76              | 22.05     |

## **DIGITAL INPUT & OUTPUT**

One I<sup>2</sup>S (Digital Audio) Port is provided which supports the following formats: I<sup>2</sup>S, Left Justified, Right Justified, and PCM mode.

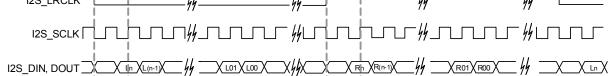

## I<sup>2</sup>S, Left Justified, and Right Justified Modes

I<sup>2</sup>S, Left Justified and Right Justified modes are stereo interface formats. The I2S\_SCLK frequency, I2S\_SCLK polarity, I2S\_DIN/DOUT data length, and I2S\_LRCLK polarity can all be changed through the *CHIP\_I2S\_CTRL* register. For I2S, Left Justified and Right Justified formats,

the left subframe should always be presented first regardless of the CHIP\_I2S\_CTRL->LRPOL setting.

The I2S\_LRCLK and I2S\_SCLK can be programmed as master (driven to an external target) or slave (driven from an external source). When the clocks are in slave mode, they must be synchronous to SYS\_MCLK. For this reason the SGTL5000 can only operate in synchronous mode (see Clocking) while in I<sup>2</sup>S slave mode.

In master mode, the clocks are synchronous to SYS\_MCLK or the output of the PLL when the part is running in asynchronous mode.

<u>Figure 10</u> shows functional examples of different common digital interface formats and their associated register settings.

# I2S Format (n = bit length)

# Left Justified Format (n = bit length)

CHIP\_I2S0\_CTRL field values: (SCLKFREQ = 0; SCLK\_INV = 0; DLEN = 1; I2S\_MODE = 0; LRALIGN = 1; LRPOL = 0)

# Right Justified Format (n = bit length)

CHIP\_I2S0\_CTRL field values: SCLKFREQ = 0; SCLK INV = 0; DLEN = 1; I2S MODE = 1; LRALIGN = 1; LRPOL = 0)

Figure 10. I<sup>2</sup>S Port Supported Formats

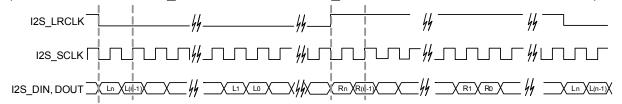

## **PCM Mode**

The I<sup>2</sup>S port can also be configured in PCM mode (also known as DSP mode). This mode is provided to allow connectivity to external devices such as Bluetooth modules. PCM mode differs from other interface formats presented in I2S, Left Justified, and Right Justified Modes, in that the frame clock (I2S\_LRCLK) does not represent a different channel when high or low. Instead, it is a bit-wide pulse that marks the start of a frame. Data is aligned such that the left channel data is immediately followed by right channel data. Zero padding is filled in for the remaining bits. The data and

frame clock may be configured to clock in on the rising or falling edge of Bit Clock.

PCM Format A is a format in which the data word begins one SCLK bit following the I2S\_LRCLK transition, as in I<sup>2</sup>S Mode. PCM Format B is a format in which the data word begins after the I2S\_LRCLK transition, as in Left Justified.

In slave mode, the pulse width of the I2S\_LRCLK does not matter. The pulse can range from one cycle high to all but one cycle high. In master mode, it is driven one cycle high.

<u>Figures 11</u> shows a functional drawing of the different formats in master mode.

# **PCM** Format A

$CHIP\_I2S0\_CTRL = 0x01F4 \\ (SCLKFREQ = 1; MS = 1; SCLK\_INV = 1; DLEN = 3; I2S\_MODE = 2; LRALIGN = 0)$

# PCM Format B

CHIP\_I2S0\_CTRL = 0x01F6 (SCLKFREQ = 1; MS = 1; SCLK INV = 1; DLEN = 3; I2S MODE = 2; LRALIGN = 1)

Figure 11. PCM Formats

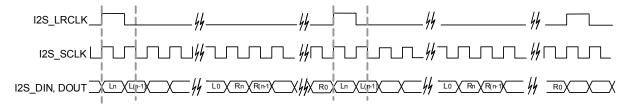

## **DIGITAL AUDIO PROCESSING**

The SGTL5000 contains a digital audio processing block (DAP) connected to the source select switch. The digitized signal from the source select switch can be routed into the DAP block for audio processing. The DAP has the following 5 sub blocks:

· Dual Input Mixer

- Freescale Surround

- Freescale Bass Enhancement

- 7-Band Parameter EQ / 5-Band Graphic EQ / Tone Control (only one can be used at a time)

- Automatic Volume Control (AVC)

The block diagram in Figure 12 shows the sequence in which the signal passes through these blocks.

Figure 12. Digital Audio Processing Block Diagram

When the DAP block is added in the route, it must be enabled separately to get audio through. It is recommended to mute the outputs before enabling/disabling the DAP block to avoid any pops or clicks due to discontinuities in the output.

Refer to Digital Audio Processor Configuration for programming examples on how to enable/disable the DAP block.

Each sub-block of the DAP can be individually disabled if its processing is not required. The following sections describe the DAP sub-blocks and how to configure them.

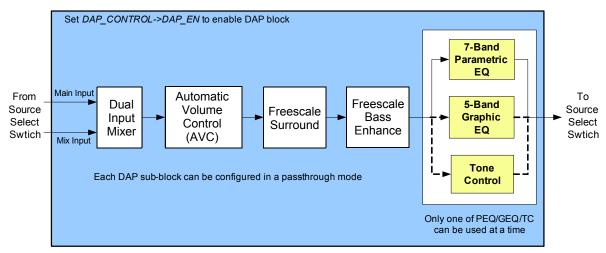

## **Dual Input Mixer**

The dual input digital mixer allows for two incoming streams from the source select switch as shown in DAP - Dual Input Mixer.

Figure 13. DAP - Dual Input Mixer

The Dual Input Mixer can be enabled or configured in a pass-through mode (Main channel is passed through without any mixing). When enabled, the volume of the main and mix channels can be independently controlled before they are mixed together.

The volume range allowed on each channel is 0% to 200% of the incoming signal level. The default is 100% (same as input signal level) volume on the main input and 0% (muted) on the mix input.

Refer to <u>Dual Input Mixer</u> for programming examples on how to enable/disable the mixer and also to set the main and mix channel volume.

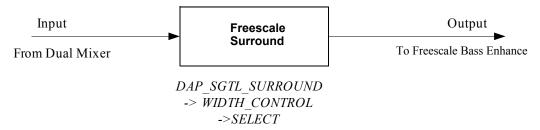

## **Freescale Surround**

Freescale Surround is a royalty free virtual surround algorithm for stereo or mono inputs. It widens and deepens the sound stage of the music input.

The Freescale Surround can be enabled or configured in pass-through mode (input is passed through without any processing). When enabling the Surround, mono or stereo input type must be selected based on the input signal. Surround width may be adjusted for the size of the sound stage.

Refer to Freescale Surround and Freescale Surround On/ Off for a programming example on how to configure Surround width and how to enable/disable Surround.

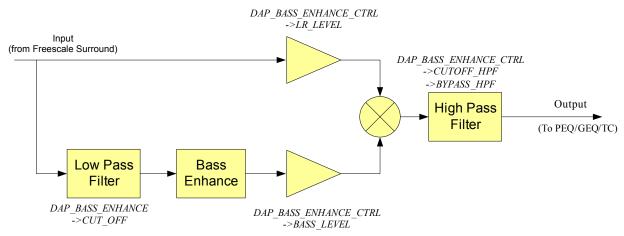

## Freescale Bass Enhance

Freescale Bass Enhance is a royalty-free algorithm that enhances natural bass response of the audio. Bass Enhance extracts bass content from right and left channels, adds bass and mixes this back up with the original signal. An optional complementary high pass filter is provided after the mixer.

Figure 14. DAP- Freescale Bass Enhance

The Freescale Bass Enhance can be enabled or configured in pass-through mode (input is passed through without any processing).

The cutoff frequency of the low-pass filter (LPF) can be selected based on the speakers frequency response. The cutoff frequency of the low-pass and high-pass filters are selectable between 80 to 225 Hz. Also, the input signal and bass enhanced signal can be individually adjusted for level before the two signals are mixed.

Refer to Freescale Bass Enhance and Bass Enhance On/ Off for a programming example on how to configure Bass Enhance and how to enable/disable this feature.

# 7-Band Parametric EQ / 5-Band Graphic EQ / Tone Control

One 7-band parametric equalizer (PEQ), one 5-band graphic equalizer (GEQ), and Tone Control (Bass and Treble

control) blocks are implemented as mutually exclusive blocks. Only one block can be used at a given time.

Refer to 7-Band Parametric EQ / 5-Band Graphic EQ / Tone Control for a programming example that shows how to select the desired EQ mode.

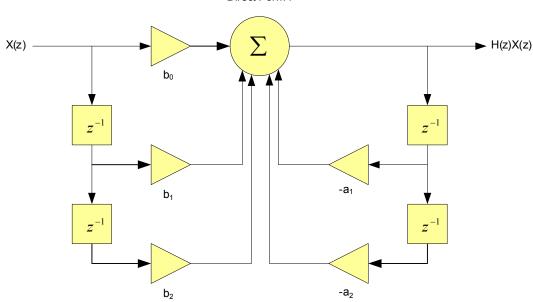

## 7-Band Parametric EQ

The 7-band PEQ allows the designer to compensate for speaker response and to provide the ability to filter out resonant frequencies caused by the physical system design. The system designer can create custom EQ presets such as Rock, Speech, Classical, etc, which allows users the flexibility to customize their audio.

The 7-band PEQ is implemented using 7 cascaded second order IIR filters. All filters are implemented using programmable bi-quad filters. Figure 15 shows the transfer function and Direct Form 1 of the five coefficient biquadratic filter.

$$H(z) = \frac{b_0 + b_1 z^{-1} + b_2 z^{-2}}{1 + a_1 z^{-1} + a_2 z^{-2}}$$

Direct Form 1

Figure 15. 5-Coefficient Biquad Filter and Transfer Function

If a band is enabled but is not being used (flat response), then a value of 0.5 should be put in  $b_0$  and all other coefficients should be set to 0.0. Note that the coefficients must be converted to hex values before writing to the registers. By default, all the filters are loaded with coefficients to give a flat response.

In order to create EQ presets such as Rock, Speech, Classical, etc, the coefficients must be calculated, converted to 20-bit hex values and written to the registers. Note that coefficients are sample-rate dependent and separate coefficients must be generated for different sample rates. Please contact Freescale for assistance with generating the coefficients.

Refer to 7-Band PEQ Preset Selection for a programming example that shows how load the filter coefficients when the end-user changes the preset.

PEQ can be disabled (pass-through mode) by writing 0 to DAP AUDIO EQ->EN bits.

## 5-Band Graphic EQ

The 5-band graphic equalizer is implemented using 5 parallel second order IIR filters. All filters are implemented using biquad filters whose coefficients are programmed to set the bands at a specific frequency. The GEQ bands are fixed

at 115 Hz, 330 Hz, 990 Hz, 3000 Hz, and 9900 Hz. The volume on each band is independently adjustable in the range of +12 dB to -11.75 dB in 0.25 dB steps.

Refer to 5-Band GEQ Volume Change for a programming example that shows how to change the GEQ volume.

#### **Tone Control**

Tone control comprises treble and bass controls. The tone control is implemented as one 2nd order low pass filter (bass) and one 2nd order high pass filter (treble).

Refer to Tone Control - Bass and Treble Change for a programming example that shows how to change Bass and Treble values.

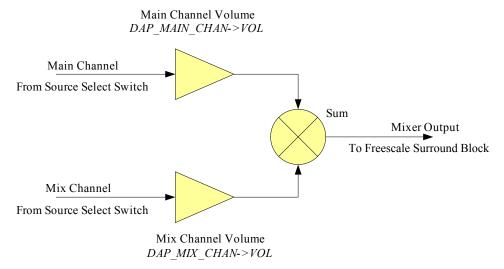

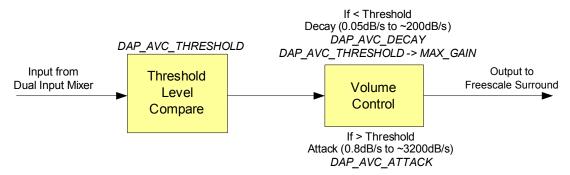

## **Automatic Volume Control (AVC)**

An Automatic Volume Control (AVC) block is provided to reduce loud signals and amplify low level signals for easier listening. The AVC is designed to compress audio when the measured level is above the programmed threshold or to expand the audio to the programmed threshold when the measured audio is below the threshold. The threshold level is programmable with an allowed range of 0 to -96 dB. Figure 16 shows the AVC block diagram and controls.

Figure 16. DAP AVC Block Diagram

When the measured audio level is below threshold, the AVC can apply a maximum gain of up to 12 dB. The maximum gain can be selected, either 0, 6, or 12 dB. When the maximum gain is set to 0 dB the AVC acts as a limiter. In this case the AVC only takes effect when the signal level is above the threshold.

The rate at which the incoming signal is attenuated down to the threshold is called the attack rate. Too high of an attack causes an unnatural sound as the input signal may be distorted. Too low of an attack may cause saturation of the output as the incoming signal is not compressed quickly enough. The attack rate is programmable with allowed range of 0.05 dB/s to 200 dB/s.

When the signal is below the threshold, AVC adjusts the volume up until either the threshold or the maximum gain is reached. The rate at which this volume is changed is called the decay rate. The decay rate is programmable with allowed range of 0.8 dB/s to 3200 dB/s. It is desirable to use very slow decay rate to avoid any distortion in the signal and prevent the AVC from entering a continuous attack-decay loop.

Refer to Automatic Volume Control (AVC) and Automatic Volume Control (AVC) On/Off for a programming example that shows how to configure AVC and how to enable/disable AVC respectively.

## CONTROL

The SGTL5000 supports both I<sup>2</sup>C and SPI control modes (note that SPI is not supported in the 20 QFN part). The CTRL\_MODE pin chooses which mode is used. When CTRL\_MODE is tied to ground, the control mode is I<sup>2</sup>C. When CTRL\_MODE is tied to VDDIO, the control mode is SPI

Regardless of the mode, the control interface is used for all communication with the SGTL5000 including startup configuration, routing, volume, etc.

## ı<sup>2</sup>C

The I<sup>2</sup>C port is implemented according to the I<sup>2</sup>C specification v2.0. The I<sup>2</sup>C interface is used to read and write all registers.

For the 32 QFN version of the SGTL5000, the  $I^2C$  device address is 0n01010(R/W) where n is determined by CTRL\_ADR0\_CS and R/W is the read/write bit from the  $I^2C$  protocol.

For the 20 QFN version of the SGTL5000 the  $I^2C$  address is always 0001010(R/W).

The SGTL5000 is always the slave on all transactions, which means that an external master always drives CTRL CLK.

In general, an I<sup>2</sup>C transaction looks like the following. All locations are accessed with a 16 bit address. Each

# location is 16 bits wide. Example I<sup>2</sup>C write

- · Start condition

- · Device address with the R/W bit cleared to indicate write

- Send two bytes for the 16 bit register address (most significant byte first)

- Send two bytes for the 16 bits of data to be written to the register (most significant byte first)

- · Stop condition

## Example I<sup>2</sup>C read

- · Start condition

- · Device address with the R/W bit cleared to indicate write

- Send two bytes for the 16 bit register address (most significant byte first)

- Stop Condition followed by start condition (or a single restart condition)

- · Device address with the R/W bit set to indicate read

- Read two bytes from the addressed register (most significant byte first)

- · Stop condition

Figure 17 shows the functional I<sup>2</sup>C timing diagram.

# Figure 17. Functional I<sup>2</sup>C Diagram

The protocol has an auto increment feature. Instead of sending the stop condition after two bytes of data, the master may continue to send data byte pairs for writing, or it may send extra clocks for reading data byte pairs. In either case, the access address is incremented after every two bytes of data. A start or stop condition from the I<sup>2</sup>C master interrupts the current command. For reads, unless a new address is written, a new start condition with R/W=0 reads from the current address and continues to auto increment.

The following diagrams describe the different access formats. The gray fields are from the  $I^2C$  master, and the white fields are the SGTL5000 responses. Data [n] corresponds to the data read from the address sent, data[n+1] is the data from the next register, and so on.

S = Start Condition

Sr = Restart Condition

A = Ack

N = Nack

P = Stop Condition

**Table 11. Write Single Location**

| S | Device  | W   | Α | ADDR   | Α | ADDR   | Α | DATA   | Α | DATA   | Α | Р |

|---|---------|-----|---|--------|---|--------|---|--------|---|--------|---|---|

|   | Address | (0) |   | byte 1 |   | byte 0 |   | byte 1 |   | byte 0 |   |   |

#### Table 12. Write Auto increment

| S | Device  | W   | Α | start  | Α | start  | Α | DATA   | Α | DATA   | Α | DATA   | Α | DATA   | Α | Р |

|---|---------|-----|---|--------|---|--------|---|--------|---|--------|---|--------|---|--------|---|---|

|   | Address | (0) |   | ADDR   |   | ADDR   |   | [n]    |   | [n]    |   | [n+1]  |   | [n+1]  |   |   |

|   |         |     |   | byte 1 |   | byte 0 |   | byte 1 |   | byte 0 |   | byte 1 |   | byte 0 |   |   |

## Table 13. Read Single Location

| S | Device  | W   | Α | ADDR   | Α | ADDR   | Α | Sr | Device  | R   | Α | DATA   | Α | DATA   | Ν | Р |

|---|---------|-----|---|--------|---|--------|---|----|---------|-----|---|--------|---|--------|---|---|

|   | Address | (0) |   | byte 1 |   | byte 0 |   |    | Address | (1) |   | byte 1 |   | byte 0 |   |   |

## Table 14. Read Auto increment

| S | Device  | W   | Α | start  | Α | start  | Α | Sr | Device  | R   | Α | DATA   | Α | DATA   | Α | DATA   | Α | DATA   | Ν | Р |

|---|---------|-----|---|--------|---|--------|---|----|---------|-----|---|--------|---|--------|---|--------|---|--------|---|---|

|   | Address | (0) |   | ADDR   |   | ADDR   |   |    | Address | (1) |   | [n]    |   | [n]    |   | [n+1]  |   | [n+1]  |   |   |

|   |         |     |   | byte 1 |   | byte 0 |   |    |         |     |   | byte 1 |   | byte 0 |   | byte 1 |   | byte 0 |   |   |

## Table 15. Read Continuing Auto increment

| S | Device  | R | Α | DATA   | Α | DATA   | Α | DATA   | Α | DATA   | N | Р |

|---|---------|---|---|--------|---|--------|---|--------|---|--------|---|---|

|   | Address |   |   | [n+2]  |   | [n+2]  |   | [n+3]  |   | [n+3]  |   |   |

|   |         |   |   | byte 1 |   | byte 0 |   | byte 1 |   | byte 0 |   |   |

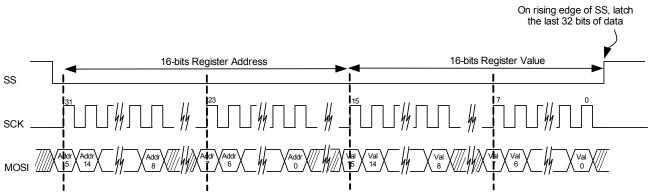

## SPI

Serial Peripheral Interface (SPI) is a communications protocol supported by the SGTL5000 (not supported in the 20 QFN package). The SGTL5000 is always a slave. The CTRL\_ADR0\_CS is used as the slave select (SS) when the master wants to select the SGTL5000 for communication. CTRL\_CLK is connected to master's SCLK and CTRL\_DATA

is connected to master's MOSI line. The part only supports SPI write operations and does not support read operations.

Figure 18 shows the functional timing diagram of the SPI communication protocol as supported by the SGTL5000 chip. Note that on the rising edge of the SS, the chip latches to the previous 32 bits of data. It interprets the latest 16-bits as register value and the 16-bits preceding it as register address.

Figure 18. Functional Timing Diagram of SPI Protocol

## **PROGRAMMING EXAMPLES**

This section provides programming examples showing how to configure the chip. The registers can be written/read by using I<sup>2</sup>C communication protocol. The chip also supports

SPI communication protocol (not supported in the 20 QFN package), but only register write operation is supported.

## PROTOTYPE FOR READING AND WRITING A REGISTER

```

The generic register read write prototype is used throughout this section, as shown by the following. The I^2C or SPI implementation is specific to the I^2C/SPI hardware used in the system.

```

```

// This prototype writes a value to the entire register. All // bit-fields of the register will be written.

```

## Write REGISTER REGISTERVALUE

```

// In the actual implementation, the other bit-fields should be // masked to prevent them from being written. Also, the // actual implementation should left-shift the BITFIELDVALUE // by appropriate number to match the starting bit location of // the BITFIELD.

```

// This prototype writes a value only to the bit-field specified.

# Modify REGISTER -> BITFIELD, BITFIELDVALUE //Bitfield Location

```

// Example implementation

// Modify DAP_EN (bit 0) bit to value 1 to enable DAP block

Modify(DAP_CONTROL_REG, 0xFFFE, 1 <<

DAP_EN_STARTBIT);

// Example Implementation of Modify

```

```

void Modify(unsigned short usRegister,

unsigned short usClearMask,

unsigned short usSetValue)

{

```

unsigned short usData;

// 1) Read current value

ReadRegister(usRegister, &usData);

// 2) Clear out old bits

usData = usData & usClearMask;

// 3) set new bit values

usData = usData | usSetValue;

// 4) Write out new value created

Write Register (us Register, us Data);

}

## **CHIP CONFIGURATION**

All outputs (LINEOUT, HP\_OUT, I2S\_OUT) are muted by default on power up. To avoid any pops/clicks, the outputs should remain muted during these chip configuration steps. Refer to Volume Control for volume and mute control.

## Initialization

## Chip Powerup and Supply Configurations

After the power supplies for the chip are turned on, the following initialization sequence should be followed. Please note that certain steps may be optional or different values may need to be written based on the power supply voltage

```

used and desired configuration. The initialization sequence below assumes VDDIO = 3.3 V and VDDA = 1.8 V.

```

```

elow assumes VDDIO = 3.3 V and VDDA = 1.8 V.

//----- Power Supply Configuration----

// NOTE: This next 2 Write calls is needed ONLY if VDDD is

```

// Configure VDDD level to 1.2V (bits 3:0)

// internally driven by the chip

Write CHIP\_LINREG\_CTRL 0x0008

// Power up internal linear regulator (Set bit 9)

Write CHIP\_ANA\_POWER 0x7260

// NOTE: This next Write call is needed ONLY if VDDD is

// externally driven

// Turn off startup power supplies to save power (Clear bit 12 and 13)

## Write CHIP\_ANA\_POWER 0x4260

// NOTE: The next Write calls is needed only if both VDDA and

// VDDIO power supplies are less than 3.1V.

// Enable the internal oscillator for the charge pump (Set bit 11)

## Write CHIP\_CLK\_TOP\_CTRL 0x0800

// Enable charge pump (Set bit 11)

#### Write CHIP ANA POWER 0x4A60

// NOTE: The next modify call is only needed if both VDDA and

// VDDIO are greater than 3.1 V

// Configure the charge pump to use the VDDIO rail (set bit 5 and bit 6)

## Write CHIP\_LINREG\_CTRL 0x006C

//---- Reference Voltage and Bias Current Configuration----

// NOTE: The value written in the next 2 Write calls is dependent // on the VDDA voltage value.

// Set ground, ADC, DAC reference voltage (bits 8:4). The value should

// be set to VDDA/2. This example assumes VDDA = 1.8 V. VDDA/2 = 0.9 V.

// The bias current should be set to 50% of the nominal value (bits 3:1)

## Write CHIP\_REF\_CTRL 0x004E

// Set LINEOUT reference voltage to VDDIO/2 (1.65 V) (bits 5:0) and bias current (bits 11:8) to the recommended value of 0.36 mA for 10 kOhm load with 1.0 nF capacitance

## Write CHIP\_LINE\_OUT\_CTRL 0x0322

//-----Other Analog Block Configurations-----

// Configure slow ramp up rate to minimize pop (bit 0)

## Write CHIP\_REF\_CTRL 0x004F

// Enable short detect mode for headphone left/right

// and center channel and set short detect current trip level // to 75 mA

## Write CHIP SHORT CTRL 0x1106

// Enable Zero-cross detect if needed for HP\_OUT (bit 5) and ADC (bit 1)

Write CHIP ANA CTRL 0x0133 //-----Power up Inputs/Outputs/Digital Blocks--// Power up LINEOUT, HP, ADC, DAC Write CHIP\_ANA\_POWER 0x6AFF // Power up desired digital blocks // I2S IN (bit 0), I2S OUT (bit 1), DAP (bit 4), DAC (bit 5), // ADC (bit 6) are powered on Write CHIP DIG POWER -----Set LINEOUT Volume Level---// Set the LINEOUT volume level based on voltage reference (VAG) // values using this formula // Value = (int)(40\*log(VAG VAL/LO VAGCNTRL) + 15) // Assuming VAG\_VAL and LO\_VAGCNTRL is set to 0.9 V and 1.65 V respectively, the // left LO vol (bits 12:8) and right LO volume (bits 4:0) value should be set // to 5 Write CHIP LINE OUT VOL 0x0505

## System MCLK and Sample Clock

// Configure SYS\_FS clock to 48 kHz

// Configure MCLK\_FREQ to 256\*Fs

Modify CHIP\_CLK\_CTRL->SYS\_FS 0x0002 // bits 3:2

Modify CHIP\_CLK\_CTRL->MCLK\_FREQ 0x0000 // bits 1:0

// Configure the I<sup>2</sup>S clocks in master mode

// NOTE: I<sup>2</sup>S LRCLK is same as the system sample clock

Modify CHIP\_I2S\_CTRL->MS 0x0001 // bit 7

## **PLL Configuration**

These programming steps are needed only when the PLL is used. Refer to Using the PLL - Asynchronous SYS\_MCLK input for details on when to use the PLL.