# dsPICDEM<sup>TM</sup> MC1 Motor Control Development Board User's Guide

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, MPLAB, PIC, PICmicro, PICSTART, PRO MATE and PowerSmart are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, microID, MXDEV, MXLAB, PICMASTER, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Accuron, Application Maestro, dsPICDEM, dsPICDEM.net, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, PICC, PICkit, PICDEM, PICDEM.net, PowerCal, PowerInfo, PowerMate, PowerTool, rfLAB, rfPIC, Select Mode, SmartSensor, SmartShunt, SmartTel and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2003, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999 and Mountain View, California in March 2002. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELog® code hopping devices, Serial EEPROMs, microperipherals, non-volatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

## dsPICDEM™ MC1 MOTOR CONTROL DEVELOPMENT BOARD

#### **Table of Contents**

| Preface    |       |                                                  |     |

|------------|-------|--------------------------------------------------|-----|

|            | Highl | lights                                           | 1   |

|            | Abou  | ıt This Guide                                    | 1   |

|            | Warr  | anty Registration                                | 2   |

|            | Reco  | ommended Reading                                 | 2   |

|            | The I | Microchip Web Site                               | 2   |

|            | Deve  | elopment Systems Customer Notification Service . | 3   |

|            | Custo | omer Support                                     | 3   |

| Chapter 1. | Se    | tup and Operation                                |     |

|            | 1.1   | Introduction                                     | 5   |

|            | 1.2   | About The System                                 | 6   |

|            | 1.3   | Interface via the 37-Pin Connector - J1          | 9   |

|            | 1.4   | Port Allocations                                 | 12  |

|            | 1.5   | Test Points                                      | 14  |

|            | 1.6   | Power Module Connector Pinout (j1)               | 15  |

|            | 1.7   | Errata                                           | 16  |

| Appendix   | Α. (  | Circuit Diagrams                                 |     |

| Worldwide  | Sale  | es and Service                                   | .22 |

## dsPICDEM™ MC1 MOTOR CONTROL DEVELOPMENT BOARD

#### **Preface**

This chapter contains general information about this manual and contacting customer support.

#### **HIGHLIGHTS**

Topics covered in this chapter:

- · About this Guide

- Warranty Registration

- · Recommended Reading

- The Microchip Web Site

- Development Systems Customer Notification Service

- Customer Support

#### **ABOUT THIS GUIDE**

#### **Document Layout**

This document describes how to use the Microchip dsPICDEM™ MC1 Motor Control Development Board. The manual layout is as follows:

- Chapter 1: Introduction This chapter introduces the dsPICDEM™ MC1 Motor Control Development Board and provides a brief description of the hardware.

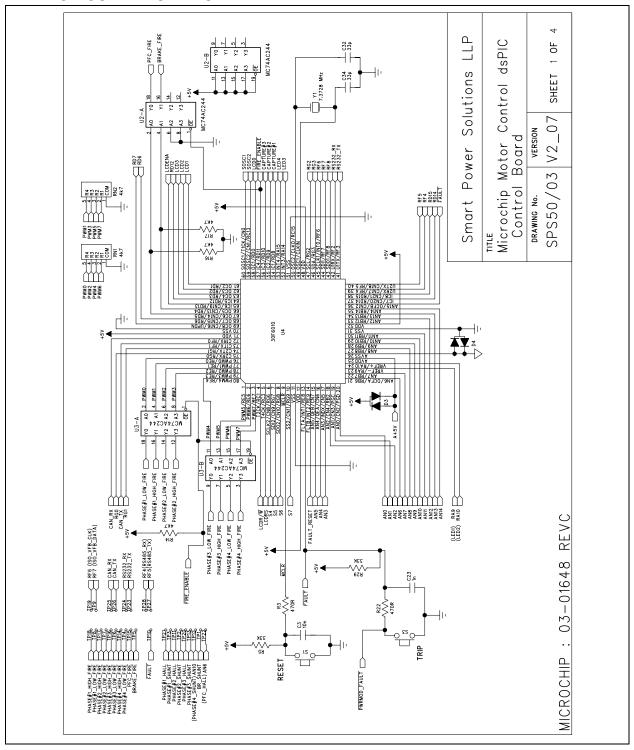

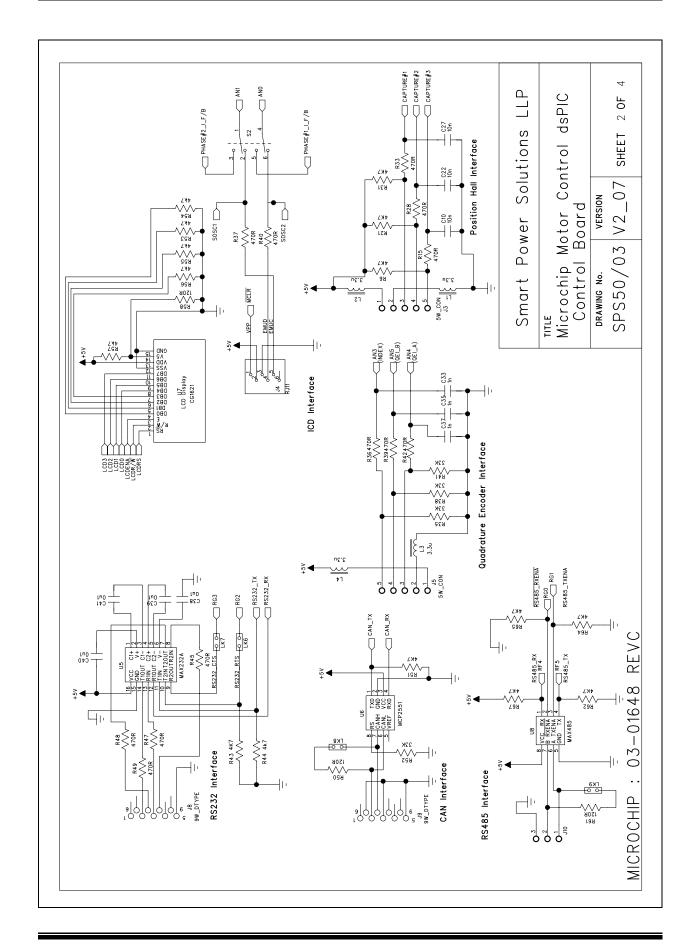

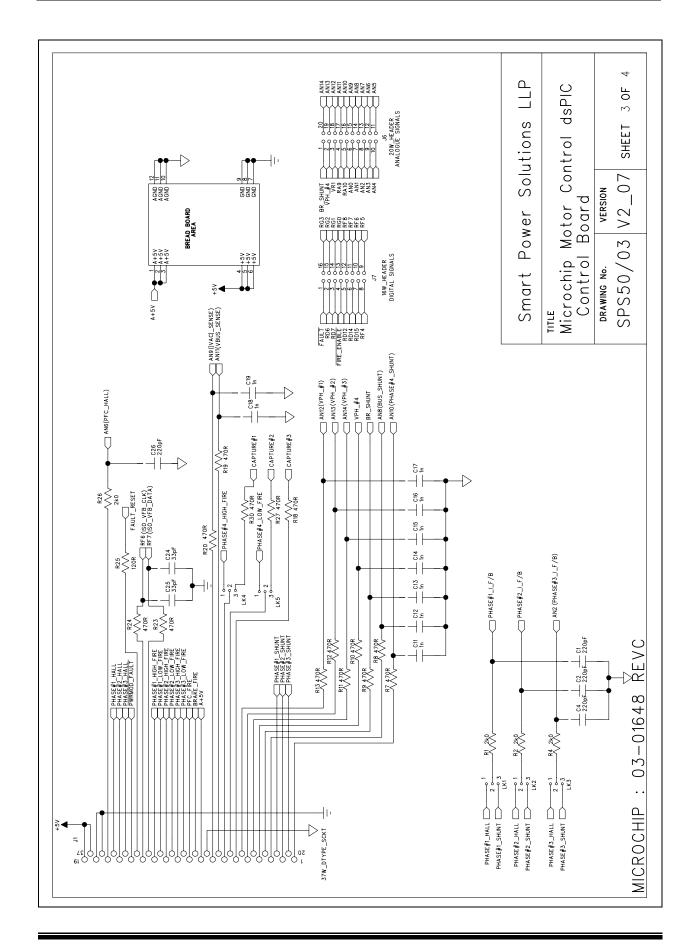

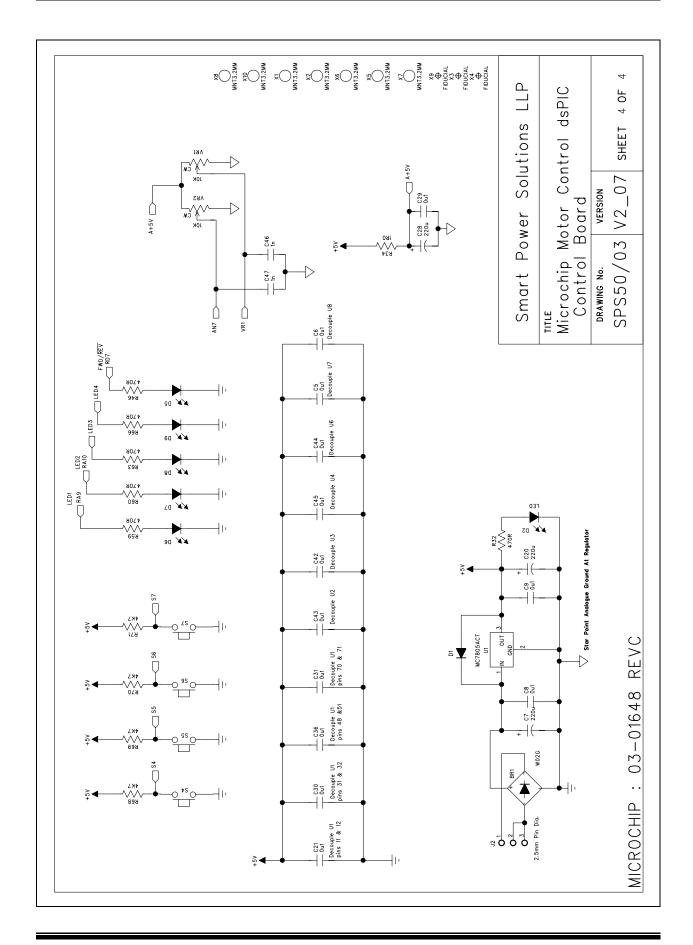

- Appendix A: Circuit Diagrams This Appendix illustrates the dsPICDEM™ MC1 Motor Control Development Board layout and hardware schematic diagrams.

- Worldwide Sales and Service Lists Microchip sales and service locations and telephone numbers worldwide.

#### **Documentation Updates**

All documentation becomes dated and this user's guide is no exception. Since MPLAB® IDE, MPLAB C1X and other Microchip tools are constantly evolving to meet customer needs, some actual dialogs and/or tool descriptions may differ from those in this document. Please refer to our web site to obtain the latest documentation available.

#### **Documentation Numbering Conventions**

Documents are numbered with a "DS" number. The number is located on the bottom of each page, in front of the page number. The numbering convention for the DS Number is: DSXXXXXA;

where:

XXXXX = The document number.

A = The revision level of the document.

#### WARRANTY REGISTRATION

Please complete the enclosed Warranty Registration Card and mail it promptly. Sending in your Warranty Registration Card entitles you to receive new product updates. Interim software releases are available at the Microchip web site.

#### RECOMMENDED READING

This user's guide describes how to use the dsPICDEM™ MC1 Motor Control Development Board. The data sheets contain current information on programming the specific microcontroller devices.

#### THE MICROCHIP WEB SITE

Microchip provides online support on the Microchip World Wide Web (WWW) site. The web site is used by Microchip as a means to make files and information easily available to customers. To view the site, you must have access to the Internet and a web browser such as Netscape Navigator® or Microsoft® Internet Explorer.

The Microchip web site is available by using your favorite internet browser to attach to: http://www.microchip.com

The web site provides a variety of services. Users may download files for the latest development tools, data sheets, application notes, user guides, articles and sample programs. A variety of information specific to the business of Microchip is also available, including listings of Microchip sales offices, distributors and factory representatives.

#### **Technical Support**

- Frequently Asked Questions (FAQ)

- Online Discussion Groups Conferences for products, Development Systems, technical information and more

- Microchip Consultant Program Member Listing

- Links to other useful web sites related to Microchip products

#### **Engineer's Toolbox**

- Design Tips

- Device Errata

#### Other Available Information

- Latest Microchip Press Releases

- Listing of Seminars and Events

- Job Postings

#### **DEVELOPMENT SYSTEMS CUSTOMER NOTIFICATION SERVICE**

Microchip started the customer notification service to help our customers keep current on Microchip products with the least amount of effort. Once you subscribe, you will receive email notification whenever we change, update, revise or have errata related to your specified product family or development tool of interest.

Go to the Microchip web site at (http://www.microchip.com) and click on Customer Change Notification. Follow the instructions to register.

The Development Systems product group categories are:

- Compilers

- Emulators

- In-Circuit Debuggers

- MPLAB<sup>®</sup> IDE

- Programmers

Here is a description of these categories:

**Compilers** – The latest information on Microchip C compilers and other language tools. These include the MPLAB C17, MPLAB C18 and MPLAB C30 C compilers; MPASM™ and MPLAB ASM30 assemblers; MPLINK™ and MPLAB LINK30 object linkers; MPLIB™ and MPLAB LIB30 object librarians.

**Emulators** – The latest information on Microchip in-circuit emulators. This includes the MPLAB<sup>®</sup> ICE 2000 and MPLAB<sup>®</sup> ICE 4000.

**In-Circuit Debuggers** – The latest information on Microchip in-circuit debuggers. These include the MPLAB® ICD and MPLAB ICD 2.

**MPLAB IDE** – The latest information on Microchip MPLAB<sup>®</sup> IDE, the Windows<sup>®</sup> Integrated Development Environment for development systems tools. This list is focused on the MPLAB<sup>®</sup> IDE, MPLAB SIM and MPLAB SIM30 simulators, MPLAB IDE Project Manager and general editing and debugging features.

**Programmers** – The latest information on Microchip device programmers. These include the PRO MATE<sup>®</sup> II device programmer and PICSTART<sup>®</sup> Plus development programmer.

#### CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Corporate Applications Engineer (CAE)

- Hotline

Customers should call their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. See the back cover for a list of sales offices and locations.

Corporate Applications Engineers (CAEs) may be contacted at (480) 792-7627.

In addition, there is a Systems Information and Upgrade Line. This line provides system users a list of the latest versions of all of Microchip's development systems software products. Plus, this line provides information on how customers can receive any currently available upgrade kits.

The Hotline Numbers are:

1-800-755-2345 for U.S. and most of Canada.

1-480-792-7302 for the rest of the world.

| NOTES: |  |  |  |

|--------|--|--|--|

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

## dsPICDEM™ MC1 MOTOR CONTROL DEVELOPMENT BOARD

#### **Chapter 1. Setup and Operation**

#### 1.1 INTRODUCTION

The Microchip dsPIC30F Motor Control Development Board has been designed to aid the user in the rapid evaluation and development of motor control applications using the Motor Control parts of the dsPIC<sup>®</sup> family. To maximize flexibility, the largest device variant in the dsPIC family has been designed in.

The board may be used in two different ways. First is to interface to one of the custom power modules that have been developed to complement the control board. The interface is via the 37-pin, D-type connector J1. In this way, all the user has to supply is a motor and they are ready to go without having to worry about the power stage and signal conditioning. The power module has its own FAULT protection and signal isolation circuitry. There are many different feedback signals that the user can select between to customize the system to their intended application. These are selected internally within the power module.

The second use of the board is for customers who already have their own power stage but are interested in evaluating the dsPIC MCU in their application. In this instance, the user can easily interface to their own system via the connectors provided on the board.

Although targeted primarily at motor control applications, the board is also well suited to static power conversion applications, such as Uninterruptible Power Supplies (UPS), Power Factor Correctors (PFC) and Switch Mode Power Supplies (SMPS).

#### 1.2 ABOUT THE SYSTEM

#### 1.2.1 Introduction

This chapter describes the features of the system.

#### 1.2.2 Processor

The system has the dsPIC30F6010 80-pin TQFP part fitted as standard (U4).

An array of pins around the device allows the appropriate MPLAB ICE device adapter to plug directly into the board without the need for the transition socket.

#### 1.2.3 Power Supply

The main supply input to the system is via J2. Any power supply with a 2.1 mm plug capable of delivering 9V, up to 1A with an unregulated AC or DC output, may be used. After rectification and filtering, the digital +5V is created by U1, a 1A 2% tolerance linear regulator. The tighter than standard tolerance is used to ensure correct optoisolator drive and FAULT trip levels when using one of the power modules. The digital +5V is available in the prototyping area (VDD) as well as on several of the interface connectors

A low current analog supply (AVDD) is created from the digital supply via a passive RC filter. This is used for the ADC in the dsPIC<sup>®</sup> device and for the analog feedback signals via J1. It is also available in the prototyping area.

### 1.2.4 In-Circuit Debugging and In-Circuit Serial Programming™ (ICSP™)

In-circuit debugging and serial programming of the FLASH memory contained within the dsPIC device is supported via J4. This allows direct connection to the MPLAB<sup>®</sup> ICD 2 or the PRO MATE<sup>®</sup> II via the appropriate ICSP module.

The default pins used for dsPIC emulator communication and device programming are AN1 and AN0. In order to maximize the number of ADC channels for use in motor control, provision has been made to switch the emulator and programming pins to the alternative pins of 59 and 60. These pins are shared with the low power secondary oscillator module that is not used in the design. Switching between the two sets of programming pins should be done using S2 and the appropriate configuration bit settings within the MPLAB environment. See the MPLAB IDE User's Guide (DS51025) for details.

When S2 is switched to the 'ICD' position, the analog feedback signals are disconnected from the AN0 and AN1 pins. The programming lines on J4 are connected. When S2 is switched to the 'Analog' position, the programming lines are disconnected and the analog signals are connected to AN0 and AN1.

#### 1.2.5 Motor Position Feedback Interface

Interface to two different types of commonly used motor position feedback devices is provided.

Note that no electrical isolation is provided on the board. The user must ensure that the motor frame is correctly earthed (grounded) and that the position feedback devices are isolated from the motor windings.

J3 (Halls) is intended for electrical commutation signals from (typically) Hall effect devices. These signals are used for BLDC and SR motors and have edge transitions aligned to the electrical cycle of the motor phases. The three inputs (A, B, C) are connected to 3 input capture channels (IC1 - IC3) of the dsPIC device. Pull-up resistors and a small amount of filtering are provided on the board. The inputs are therefore, suitable for either open-collector or driven use. Clearly, the inputs can be used for any input capture or I/O requirements the user may have.

J5 (QEI) is intended for a Quadrature (or Incremental) Encoder Interface. These devices produce two position related pulse train outputs, 90° apart (A and B) and an optionally index output (Z) that pulses once per revolution. A typical device will produce many hundreds of pulses per revolution allowing high resolution position feedback and high bandwidth speed measurement. The inputs have a very small amount of filtering. Weak pull-down resistors are also fitted. The three inputs are connected through to the dedicated inputs of the QEI module of the dsPIC device.

The digital power supply (+5V and 0V-"G") is brought out to the connectors for powering the transducers. Series inductors are used to reduce electrical noise entering the board. The user should ensure there is adequate local decoupling of the power supply at the position transducer end of the cable. The maximum current that may be drawn from the +5V supply is 200 mA. If the user wishes to use a transducer that requires more current, then an external power supply should be used with a common connection between the grounds made on the G pin.

To minimize electrical noise, a shielded cable should be used.

#### 1.2.6 Oscillator

A 7.3728 MHz, low profile crystal (Y1) is provided on the board. In combination with the internal PLL and programmable postscaler of the dsPIC device, this allows a wide range of system clock frequencies to be generated. A low profile component is used to clear the emulator device adapter.

#### 1.2.7 RS-232 Serial Port

One of the dsPIC UARTs is connected to J8 via an RS-232 level shifting interface implemented by U5 (MAX232A). Using RG2 and RG3 as port pins also provides optional hardware handshaking using CTS and RTS. To use the handshaking, the user must install links LK6 and LK7. As RG2 and RG3 are multiplexed with the I<sup>2</sup>C<sup>™</sup> clock and data lines available on the digital prototyping header J7, both features can not be used at once.

#### 1.2.8 RS-485 Serial Bus

The second dsPIC UART is connected to J10 via an RS-485 level shifting interface implemented by U8 (MAX485). A 120R terminating resistor may be connected across the bus lines (A, B) by installing LK9. The user may (optionally) control the RX and TX enable lines by driving RG0 and RG1. Pull-down resistors are used to ensure the RX is enabled and the TX is disabled by default.

#### 1.2.9 CAN bus

One of the CAN modules is connected to J9 via a Microchip MCP2551 CAN Transceiver IC. A 120R terminating resistor may be connected across the bus lines by installing LK8. A pull-down resistor ensures the TX stays inactive during RESET or if the CAN module is not being used.

The second CAN module is available on the digital prototyping header on RG0 and RG1. As these pins are used for the RS-485 RX and TX control, the RS-485 and the second CAN module may not be used at the same time.

#### 1.2.10 LCD Display

A 16x2 LCD display (U7) is included on the board. Communication to the display is via the standard 4-bit interface method based on the well known Hitachi style communication standard.

- The LCD data lines are on RD0-RD3.

- The Enable line is on RD13.

- The Read/Write is on RC1.

- The Data/Command Select (LCDRS) is on RC3.

#### 1.2.11 LEDs

Four general purpose LEDs (D6-D9) are provided on the board. These are connected to RA9, RA10, RA14 and RA15, respectively.

A single LED (D2) is provided to indicate the +5V supply is on.

A single LED (D5) is provided to indicate direction of rotation. This is connected to RD7. When using a quadrature encoder via J5, RD7 may be automatically driven by the QEI module to indicate direction. Otherwise, this line must be driven as a port pin.

#### 1.2.12 Push Button Switches

Four general purpose push button switches are provided (S4-S7). These are connected to RG6-RG9, respectively.

A RESET switch is also provided (S1) and connected to the MCLR line of the dsPIC device.

A TRIP switch (S3) is provided which is wire ORed with an active low FAULT signal from J1. The resulting signal (FAULT) is connected to the FLTA input of the PWM module and the OCFB input of the Output Compare module. When correctly configured in software, the TRIP switch will therefore, cause all the PWM channels to be driven to their inactive state and OC channels 5-8 to be tri-stated. Thus, the power stage may be shut down independent of software intervention. To configure the OC channels to use this feature, the OCM bits of OCxCON (x = 5-8) should all be set. To configure the PWM module to use this feature, the appropriate bits in the FLTACON register should be set.

#### 1.2.13 Potentiometers

Two potentiometers (VR1 and VR2) are provided on the board.

VR2 is permanently connected to the AN7 input of the ADC.

VR1 is only brought to the analog prototyping header J6 as POT1 owing to analog channel constraints. If the user is not using the VPH\_#1 analog feedback signal from J1, then VR2 may be easily connected to AN12 by placing a 0.1" jumper across J6. Alternatively, VR2 may be connected to any other spare analog channel by soldering a wire link between the appropriate pins of J6.

#### 1.2.14 Prototyping Area

A 0.1" pitch prototyping area is provided on the board.

Digital (VDD/VSS) and analog (AVDD/AVSS) power supplies are provided in the four corners.

J6 provides access to all the ADC channels as well as having unassigned analog signals on it.

J7 provides access to any optional or unassigned digital I/O pins.

#### 1.3 INTERFACE VIA THE 37-PIN CONNECTOR - J1

#### 1.3.1 Introduction

The 37-pin, D-type connector (J1) and the associated signal routing and circuitry have been designed to directly interface with one of the custom power modules that are available. These complement this board by removing the need for the user to have their own power stage. The power modules contain all the necessary driving circuitry, have robust FAULT protection and many different feedback signals. For details as to the interfacing requirements, feedback scaling and power capabilities for the particular power module, the user should consult the power module documentation.

Due to the finite number of ADC channels and the fact that some of the pins are shared with other modules, it is not possible to connect all of the power module feedback signals to the ADC module at the same time.

In general, up to four phase motors have been allowed for in terms of firing signals and feedback information. Given that 4-phase motors are not all that common, where compromises were needed owing to ADC or input pin restriction, 3-phase motors have been given preference.

A small amount of RC filtering is used on all the analog feedback signals for ESD protection and noise suppression. The resistors have been chosen to have minimal impact on ADC acquisition time.

#### 1.3.2 Switch Firing Commands

A total of ten PWM signals are routed to the 37-pin connector via high current 74AC244 buffers. The output of the buffers directly drives the LEDs of the optocouplers, as well as LEDs that are visible through the front of the enclosure of the power module.

**Note:** The 74AC244 buffers are not required in most designs. The dsPIC PWM pins can drive most gate drive circuitry directly. Refer to the device data sheet for further details. The buffers provide protection of the dsPIC I/O pins in a development environment and provide drive strength for the loads presented by the power module interface circuitry.

In order to ensure correct operation of the firing signal outputs via J1 when the inputs to the buffers are tri-stated, an overall active low FIRE\_ENABLE control line is used via RD11. The FIRE\_ENABLE line is pulled up via R14 and must be pulled low by the user's software to enable the buffers.

Eight of the firing commands come from the Motor Control PWM module. Of these eight, two are optional owing to the limited number of pins on the connector. These are the Phase#4 firing commands. They are shared with two of the back EMF crossing signals. As delivered, the board is configured to use the back EMF crossing signals – LK4 and LK5 are fitted in position 2-3.

Two of the firing commands used for the brake chopper and PFC come from output compare channels 5 and 6. These channels should be configured in the PWM mode with the FAULT pin enabled.

#### 1.3.3 Current Feedback from the Power Modules

#### 1.3.3.1 PFC

When an active power factor corrector is used, a Hall effect isolated current transducer is included on the power module design to measure the input current. This signal is assigned to AN6.

#### 1.3.3.2 BRAKE CHOPPER

Although not strictly required for correct control of a brake chopper, feedback of the amplified shunt voltage is provided. This signal is brought to the analog prototyping header J6 as BR\_SHUNT. If AN14 is not already in use, then a 0.1" jumper may be used to easily connect BR\_SHUNT to AN14. Alternatively, a wire link may be soldered into J6 to assign BR\_SHUNT to any other available channel.

#### 1.3.3.3 MOTOR POWER STAGE

Owing to phase symmetry of motors and the connection to their phases, a separate current transducer is not necessarily required per phase. This has been taken advantage of to reduce the number of feedback signals as is done in commercial applications.

Two alternative sets of current feedback signals have been allowed. The two sets represent signals from transducers measuring output current to the motor or those measuring switch currents referenced to the -DC bus. A given application tends to use one type or the other depending on isolation, accuracy and cost requirements.

A maximum of 3 output transducers is allowed along with up to 4 switch shunts.

LK1-LK3 are used to change over between the two sets of signals for Phase#1-Phase#3. In this instance, the isolated signals come from Hall effect transducers. As delivered, the isolated signals are selected to match the (default) isolated configuration of the power module. The Phase#1-Phase#3 current feedback signals are allocated to AN0, AN1 and AN2. This has been done so that simultaneous sampling may be carried out on all three phases. This is especially important for certain motor control algorithms.

The fourth shunt (if used) is allocated to AN10.

Note that the ICD/ICSP data and clock lines must be reallocated before the Phase#1 and Phase#2 current feedback channels may be used. See Section 1.2.4 for details.

#### 1.3.3.4 DC BUS SHUNT FEEDBACK

Feedback of the current in the -DC bus shunt is provided.

This signal (BUS\_SHUNT) is assigned to AN8

#### 1.3.4 Voltage Feedback

#### 1.3.4.1 ISOLATED VOLTAGE FEEDBACK

Isolated voltage feedback signals are accommodated through the use of a PIC12C671 located within the power module. This device has its own ADC and communicates with the dsPIC device via a simple 2-wire (clock and data) serial communications interface. These signals are assigned to SCLK1 and SDI1 via RF6 and RF7.

Re-synchronization of the serial link is achieved by asserting the FAULT\_RESET line on RE9 for a minimum of 2  $\mu s$  provided a FAULT does not already exist. For details of the serial communication protocol, refer to the power module documentation.

The two signals passed back are the DC bus voltage and, for AC input power modules with PFC, the rectified AC voltage.

A small amount of passive filtering is used on the clock and data lines to remove noise spikes.

#### 1.3.4.2 POWER MODULE OUTPUT VOLTAGE FEEDBACK

Up to 4 power module output voltage feedback signals are accommodated. These signals may be useful for detection of position or speed (i.e., so called sensorless operation). Alternatively, they may be used to correct for output voltage distortion which occurs due to power device voltage drops and dead-time.

The signals are referred to as VPH\_#1 - VPH\_#4. VPH\_#1 - VPH\_#3 are assigned to AN12-AN14, respectively. VPH\_#4 is only brought to the analog prototyping header J6 and must be manually assigned if required.

#### 1.3.4.3 DC BUS VOLTAGE AND RECTIFIED AC VOLTAGE FEEDBACK

The DC bus voltage and, for AC input power modules with PFC, the rectified AC voltage is accommodated.

The DC bus voltage is assigned to AN11.

The rectified AC voltage, if used, is assigned to AN9.

#### 1.3.5 Back EMF Crossing Detection

One method of operating a brushless DC motor without a position sensor has been included in the design of certain power modules. This method relies on detecting when the voltage of an inactive phase's output lead, due to it's back EMF, crosses the nominal center point of the DC bus. Comparators are included within the power module which detect the crossover points.

Three such crossover signals are accommodated in the design. Two of these signals can not be used at the same time as the Phase#4 firing signals (which are not required by the power modules that provide the back EMF crossing signals).

If the user wishes to use the back EMF crossing signals then they must do the following:

- Make sure LK4 and LK5 are in position 2-3.

- Make sure that no Hall commutation transducer is connected to J3. This is because the three input capture channels are common.

#### 1.4 PORT ALLOCATIONS

The following table shows the primary port allocations for the dsPIC30F6010 as required for interfacing to one of the custom power modules via J1. Where a primary assignment and use is not shown, the pin is available on one of the prototyping headers.

The pin headers give access to all pins. In addition, certain other pins are routed to the analog (J6) and digital (J7) prototyping headers.

| Pin No.         Port No.         Port No.         Assignment Assignment         Pri Use         Suggested Alternative Use           23         A         9         RA9         LED1 (D6)         VREF- via J6 (RA9) (D6-NF)           25         A         10         RA10         LED2 (D7)         VREF+ via J6 (R10) (D7-NF)           52         A         114         RA14         LED3 (D8)         —           53         A         115         RA15         LED4 (D9)         —           20         B         0         AN0         PHASE#3 L F/B via J1         ICSP **Data if S2 in PRI Position           19         B         1         AN1         PHASE#3 L F/B via J1         ICSP **Data if S2 in PRI Position           18         B         2         AN2         PHASE#3 L F/B via J1         ICSP **Data if S2 in PRI Position           18         B         2         AN2         PHASE#3 L F/B via J1         ICSP **Data if S2 in PRI Position           19         B         3         INDX         INDEX for Cell via J5 (Z)         ADC input via J6 (AN3) or Pin3 J5           16         B         4         QEA         QEI Channel B via J5 (B)         ADC input via J6 (AN14) or Pin3 J5           15         B         5         | analog (60) and digital (67) prototyping neadors. |      |          |      |                                  |                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|------|----------|------|----------------------------------|-----------------------------------|

| 25         A         10         RA10         LED2 (D7)         VREF+ via J6 (R10) (D7-NF)           52         A         14         RA14         LED3 (D8)         —           53         A         15         RA15         LED4 (D9)         —           20         B         0         AN0         PHASE#1_F/B via J1         ICSP™ Data if S2 in PRI Position           19         B         1         AN1         PHASE#2_F/B via J1         ICSP™ Data if S2 in PRI Position           18         B         2         AN2         PHASE#3_F/B via J1         ICSP™ Data if S2 in PRI Position           18         B         2         AN2         PHASE#3_F/B via J1         ICSP Clock is S2 in PRI Position           18         B         2         AN2         PHASE#3_F/B via J1         ADC input via J6 (AN3) (K13-NF)           16         B         4         QEA         QEI Channel A via J5 (2)         ADC input via J6 (AN4) or Pin3 J5           16         B         4         QEA         QEI Channel B via J5 (B)         ADC input via J6 (AN4) or Pin3 J5           15         B         5         QEB         QEI Channel B via J5 (B)         ADC input via J6 (AN4) or Pin3 J5           15         CB         AN6         PEL HA      | Pin No.                                           | Port | Port No. |      | Pri Use                          | Suggested Alternative Use         |

| 52         A         14         RA14         LED3 (D8)         —           53         A         15         RA15         LED4 (D9)         —           20         B         0         AN0         PHASE#1_F/B via J1         ICSP™ Data if S2 in PRI Position           19         B         1         AN1         PHASE#2_F/B via J1         ICSP Clock is S2 in PRI Position           18         B         2         AN2         PHASE#3_F/B via J1         ADC input via J6 (AN2) (LK3-NF)           17         B         3         INDX         INDEX for OEI via J5 (2)         ADC input via J6 (AN4) or Pin3 J5           16         B         4         QEA         QEI Channel B via J5 (B)         ADC input via J6 (AN4) or Pin3 J5           15         B         5         QEB         QEI Channel B via J5 (B)         ADC input via J6 (AN5) or Pin4 J5           21         B         6         AN6         PFC HALL via J1         ADC input via J6 (AN5) or Pin4 J5           21         B         6         AN6         PFC HALL via J1         ADC input via J6 (AN5) or Pin4 J5           22         B         7         —         —         AN7/RB7 via J6 (AN7)           27         B         8         AN8         BUS_SHUNT               | 23                                                | Α    | 9        | RA9  | LED1 (D6)                        | VREF- via J6 (RA9) (D6-NF)        |

| S3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25                                                | Α    | 10       | RA10 | LED2 (D7)                        | VREF+ via J6 (R10) (D7-NF)        |

| 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 52                                                | Α    | 14       | RA14 | LED3 (D8)                        |                                   |

| 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53                                                | Α    | 15       | RA15 | LED4 (D9)                        | _                                 |

| 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20                                                | В    | 0        | AN0  | PHASE#1_I_F/B via J1             | ICSP™ Data if S2 in PRI Position  |

| 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19                                                | В    | 1        | AN1  | PHASE#2_I_F/B via J1             | ICSP Clock is S2 in PRI Position  |

| 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18                                                | В    | 2        | AN2  | PHASE#3_I_F/B via J1             | ADC input via J6 (AN2) (LK3-NF)   |

| 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17                                                | В    | 3        | INDX | INDEX for QEI via J5 (Z)         | ADC input via J6 (AN3) or Pin5 J5 |

| 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16                                                | В    | 4        | QEA  | QEI Channel A via J5 (A)         | ADC input via J6 (AN4) or Pin3 J5 |

| ANT/RB7 via J6 (ANT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                | В    | 5        | QEB  | QEI Channel B via J5 (B)         | ADC input via J6 (AN5) or Pin4 J5 |

| 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 21                                                | В    | 6        | AN6  | PFC HALL via J1                  | ADC input via J6 (AN6)            |

| 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22                                                | В    | 7        | _    | _                                | AN7/RB7 via J6 (AN7)              |

| 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27                                                | В    | 8        | AN8  | BUS_SHUNT via J1                 | ADC input via J6 (AN8)            |

| 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28                                                | В    | 9        | AN9  | VAC   SENSE                      | ADC input via J6 (AN9)            |

| 33         B         12         AN12         VPH_#1         ADC input via J6 (AN12)           34         B         13         AN13         VPH_#2         ADC input via J6 (AN13)           35         B         14         AN14         VPH_#3         ADC input via J6 (AN14)           36         B         15         OCFB         Active Low FAULT from power module of TRIP switch         —           4         C         1         RC1         LCD R/W Line         —           5         C         3         RC3         LCD R/W Line         —           59         C         13         —         ICSP Data if S2 in ALT Position         —           60         C         14         —         ICSP Clock if S2 in ALT Position         —           60         C         14         —         ICSP Clock if S2 in ALT Position         —           58         D         0         RD0         LCD0 (LSB)         —           61         D         1         RD1         LCD1         —           62         D         2         RD2         LCD2         —           63         D         3         RD3         LCD8 (MSB)         — <t< td=""><td>29</td><td>В</td><td>10</td><td>AN10</td><td>PHASE#4_SHUNT</td><td>ADC input via J6 (AN10)</td></t<> | 29                                                | В    | 10       | AN10 | PHASE#4_SHUNT                    | ADC input via J6 (AN10)           |

| 34         B         13         AN13         VPH_#2         ADC input via J6 (AN13)           35         B         14         AN14         VPH_#3         ADC input via J6 (AN14)           36         B         15         OCFB         Active Low FAULT from power module of TRIP switch         —           4         C         1         RC1         LCD RS Line         —           5         C         3         RC3         LCD RS Line         —           60         C         14         —         ICSP Data if S2 in ALT Position         —           60         C         14         —         ICSP Clock if S2 in ALT Position         —           61         D         1         RD1         LCD0 (LSB)         —           61         D         1         RD1         LCD1         —           62         D         2         RD2         LCD2         —           63         D         3         RD3         LCD3 (MSB)         —           66         D         4         OC5         BRAKE_FIRE via J1         —           67         D         5         OC6         PFC_FIRE via J1         —           68                                                                                                                                      | 30                                                | В    | 11       | AN11 | VLINK_SENSE                      | ADC input via J6 (AN11)           |

| S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 33                                                | В    | 12       | AN12 | VPH_#1                           | ADC input via J6 (AN12)           |

| 36         B         15         OCFB         Active Low FAULT from power module of TRIP switch         —           4         C         1         RC1         LCD R/W Line         —           5         C         3         RC3         LCD RS Line         —           59         C         13         —         ICSP Data if S2 in ALT Position         —           60         C         14         —         ICSP Clock if S2 in ALT Position         —           60         C         14         —         ICSP Clock if S2 in ALT Position         —           60         C         14         —         ICSP Clock if S2 in ALT Position         —           61         D         0         RD0         LCD0 (LSB)         —           61         D         1         RD1         LCD1         —           62         D         2         RD2         LCD2         —           63         D         3         RD3         LCD3 (MSB)         —           66         D         4         OC5         BRAKE_FIRE via J1         —           67         D         5         OC6         PFC_FIRE via J1         RD7 output to Direction LED (D5)                                                                                                                 | 34                                                | В    | 13       | AN13 | VPH_#2                           | ADC input via J6 (AN13)           |

| Module of TRIP switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 35                                                | В    | 14       | AN14 | VPH_#3                           | ADC input via J6 (AN14)           |

| 5         C         3         RC3         LCD RS Line         —           59         C         13         —         ICSP Data if S2 in ALT Position         —           60         C         14         —         ICSP Clock if S2 in ALT Position         —           58         D         0         RD0         LCD0 (LSB)         —           61         D         1         RD1         LCD1         —           62         D         2         RD2         LCD2         —           63         D         3         RD3         LCD3 (MSB)         —           66         D         4         OC5         BRAKE_FIRE via J1         —           67         D         5         OC6         PFC_FIRE via J1         —           68         D         6         —         —         OC7/CN15/RD6 via J7 (RD6)           69         D         7         UPDN         QEI UP/DOWN Output to Direction LED (D5)         RD7 output to Direction LED (D5)           54         D         8         IC1         Phase A Position Hall via J3 (A)         Back EMF Crossing #1 via J1 if LK4 in Position 2-3           55         D         9         IC2         Phase B Position                                                                                      | 36                                                | В    | 15       | OCFB |                                  | _                                 |

| 59         C         13         —         ICSP Data if S2 in ALT Position         —           60         C         14         —         ICSP Clock if S2 in ALT Position         —           58         D         0         RD0         LCD0 (LSB)         —           61         D         1         RD1         LCD1         —           62         D         2         RD2         LCD2         —           63         D         3         RD3         LCD3 (MSB)         —           66         D         4         OC5         BRAKE_FIRE via J1         —           67         D         5         OC6         PFC_FIRE via J1         —           68         D         6         —         —         OC7/CN15/RD6 via J7 (RD6)           69         D         7         UPDN         QEI UP/DOWN Output to Direction LED (D5)         RD7 output to Direction LED (D5)           54         D         8         IC1         Phase A Position Hall via J3 (A)         Back EMF Crossing #1 via J1 if LK4 in Position 2-3           55         D         9         IC2         Phase B Position Hall via J3 (B)         Back EMF Crossing #3 via J1           57         D         11                                                                          | 4                                                 | С    | 1        | RC1  | LCD R/W Line                     | _                                 |

| 60         C         14         —         ICSP Clock if S2 in ALT Position         —           58         D         0         RD0         LCD0 (LSB)         —           61         D         1         RD1         LCD1         —           62         D         2         RD2         LCD2         —           63         D         3         RD3         LCD3 (MSB)         —           66         D         4         OC5         BRAKE_FIRE via J1         —           67         D         5         OC6         PFC_FIRE via J1         —           68         D         6         —         —         OC7/CN15/RD6 via J7 (RD6)           69         D         7         UPDN         QEI UP/DOWN Output to Direction LED (D5)         RD7 output to Direction LED (D5)           54         D         8         IC1         Phase A Position Hall via J3 (A)         Back EMF Crossing #1 via J1 if LK4 in Position 2-3           55         D         9         IC2         Phase B Position Hall via J3 (B)         Back EMF Crossing #3 via J1 if LK5 in Position 2-3           56         D         10         IC3         Phase C Position Hall via J3 (B)         Back EMF Crossing #3 via J1                                                        | 5                                                 | С    | 3        | RC3  | LCD RS Line                      | _                                 |

| 58         D         0         RD0         LCD0 (LSB)         —           61         D         1         RD1         LCD1         —           62         D         2         RD2         LCD2         —           63         D         3         RD3         LCD3 (MSB)         —           66         D         4         OC5         BRAKE_FIRE via J1         —           67         D         5         OC6         PFC_FIRE via J1         —           68         D         6         —         —         OC7/CN15/RD6 via J7 (RD6)           69         D         7         UPDN         QEI UP/DOWN Output to Direction LED (D5)           54         D         8         IC1         Phase A Position Hall via J3 (A)         Back EMF Crossing #1 via J1 if LK4 in Position 2-3           55         D         9         IC2         Phase B Position Hall via J3 (B)         Back EMF Crossing #2 via J1 if LK5 in Position 2-3           56         D         10         IC3         Phase C Position Hall via J3 (B)         Back EMF Crossing #3 via J1           57         D         11         RD11         Active Low FIRE_ENABLE         —           64         D         12                                                                      | 59                                                | С    | 13       | _    | ICSP Data if S2 in ALT Position  | _                                 |

| 61         D         1         RD1         LCD1         —           62         D         2         RD2         LCD2         —           63         D         3         RD3         LCD3 (MSB)         —           66         D         4         OC5         BRAKE_FIRE via J1         —           67         D         5         OC6         PFC_FIRE via J1         —           68         D         6         —         —         OC7/CN15/RD6 via J7 (RD6)           69         D         7         UPDN         QEI UP/DOWN Output to Direction LED (D5)           54         D         8         IC1         Phase A Position Hall via J3 (A)         Back EMF Crossing #1 via J1 if LK4 in Position 2-3           55         D         9         IC2         Phase B Position Hall via J3 (B)         Back EMF Crossing #2 via J1 if LK5 in Position 2-3           56         D         10         IC3         Phase C Position Hall via J3 (B)         Back EMF Crossing #3 via J1           57         D         11         RD11         Active Low FIRE_ENABLE         —           64         D         12         —         —         IC5/RD12 via J7 (RD12)                                                                                             | 60                                                | С    | 14       | _    | ICSP Clock if S2 in ALT Position | _                                 |

| 62         D         2         RD2         LCD2         —           63         D         3         RD3         LCD3 (MSB)         —           66         D         4         OC5         BRAKE_FIRE via J1         —           67         D         5         OC6         PFC_FIRE via J1         —           68         D         6         —         —         OC7/CN15/RD6 via J7 (RD6)           69         D         7         UPDN         QEI UP/DOWN Output to Direction LED (D5)         RD7 output to Direction LED (D5)           54         D         8         IC1         Phase A Position Hall via J3 (A)         Back EMF Crossing #1 via J1 if LK4 in Position 2-3           55         D         9         IC2         Phase B Position Hall via J3 (B)         Back EMF Crossing #2 via J1 if LK5 in Position 2-3           56         D         10         IC3         Phase C Position Hall via J3 (B)         Back EMF Crossing #3 via J1           57         D         11         RD11         Active Low FIRE_ENABLE         —           64         D         12         —         —         IC5/RD12 via J7 (RD12)                                                                                                                        | 58                                                | D    | 0        | RD0  | LCD0 (LSB)                       | _                                 |

| 63         D         3         RD3         LCD3 (MSB)         —           66         D         4         OC5         BRAKE_FIRE via J1         —           67         D         5         OC6         PFC_FIRE via J1         —           68         D         6         —         —         OC7/CN15/RD6 via J7 (RD6)           69         D         7         UPDN         QEI UP/DOWN Output to Direction LED (D5)         RD7 output to Direction LED (D5)           54         D         8         IC1         Phase A Position Hall via J3 (A)         Back EMF Crossing #1 via J1 if LK4 in Position 2-3           55         D         9         IC2         Phase B Position Hall via J3 (B)         Back EMF Crossing #2 via J1 if LK5 in Position 2-3           56         D         10         IC3         Phase C Position Hall via J3 (B)         Back EMF Crossing #3 via J1           57         D         11         RD11         Active Low FIRE_ENABLE         —           64         D         12         —         —         IC5/RD12 via J7 (RD12)                                                                                                                                                                                            | 61                                                | D    | 1        | RD1  | LCD1                             | _                                 |

| 66         D         4         OC5         BRAKE_FIRE via J1         —           67         D         5         OC6         PFC_FIRE via J1         —           68         D         6         —         —         OC7/CN15/RD6 via J7 (RD6)           69         D         7         UPDN         QEI UP/DOWN Output to Direction LED (D5)           54         D         8         IC1         Phase A Position Hall via J3 (A)         Back EMF Crossing #1 via J1 if LK4 in Position 2-3           55         D         9         IC2         Phase B Position Hall via J3 (B)         Back EMF Crossing #2 via J1 if LK5 in Position 2-3           56         D         10         IC3         Phase C Position Hall via J3 (B)         Back EMF Crossing #3 via J1           57         D         11         RD11         Active Low FIRE_ENABLE         —           64         D         12         —         —         IC5/RD12 via J7 (RD12)                                                                                                                                                                                                                                                                                                               | 62                                                | D    | 2        | RD2  | LCD2                             | _                                 |

| 67         D         5         OC6         PFC_FIRE via J1         —           68         D         6         —         —         OC7/CN15/RD6 via J7 (RD6)           69         D         7         UPDN         QEI UP/DOWN Output to Direction LED (D5)         RD7 output to Direction LED (D5)           54         D         8         IC1         Phase A Position Hall via J3 (A)         Back EMF Crossing #1 via J1 if LK4 in Position 2-3           55         D         9         IC2         Phase B Position Hall via J3 (B)         Back EMF Crossing #2 via J1 if LK5 in Position 2-3           56         D         10         IC3         Phase C Position Hall via J3 (B)         Back EMF Crossing #3 via J1           57         D         11         RD11         Active Low FIRE_ENABLE         —           64         D         12         —         —         IC5/RD12 via J7 (RD12)                                                                                                                                                                                                                                                                                                                                                       | 63                                                | D    | 3        | RD3  | LCD3 (MSB)                       | _                                 |

| 68         D         6         —         —         OC7/CN15/RD6 via J7 (RD6)           69         D         7         UPDN         QEI UP/DOWN Output to Direction LED (D5)         RD7 output to Direction LED (D5)           54         D         8         IC1         Phase A Position Hall via J3 (A)         Back EMF Crossing #1 via J1 if LK4 in Position 2-3           55         D         9         IC2         Phase B Position Hall via J3 (B)         Back EMF Crossing #2 via J1 if LK5 in Position 2-3           56         D         10         IC3         Phase C Position Hall via J3 (B)         Back EMF Crossing #3 via J1           57         D         11         RD11         Active Low FIRE_ENABLE         —           64         D         12         —         —         IC5/RD12 via J7 (RD12)                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66                                                | D    | 4        | OC5  | BRAKE_FIRE via J1                | _                                 |

| 69D7UPDNQEI UP/DOWN Output to Direction LED (D5)54D8IC1Phase A Position Hall via J3 (A)Back EMF Crossing #1 via J1 if LK4 in Position 2-355D9IC2Phase B Position Hall via J3 (B)Back EMF Crossing #2 via J1 if LK5 in Position 2-356D10IC3Phase C Position Hall via J3 (B)Back EMF Crossing #3 via J157D11RD11Active Low FIRE_ENABLE—64D12—IC5/RD12 via J7 (RD12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 67                                                | D    | 5        | OC6  | PFC_FIRE via J1                  | _                                 |

| Direction LED (D5)           54         D         8         IC1         Phase A Position Hall via J3 (A)         Back EMF Crossing #1 via J1 if LK4 in Position 2-3           55         D         9         IC2         Phase B Position Hall via J3 (B)         Back EMF Crossing #2 via J1 if LK5 in Position 2-3           56         D         10         IC3         Phase C Position Hall via J3 (B)         Back EMF Crossing #3 via J1           57         D         11         RD11         Active Low FIRE_ENABLE         —           64         D         12         —         IC5/RD12 via J7 (RD12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 68                                                | D    | 6        | _    | _                                | OC7/CN15/RD6 via J7 (RD6)         |

| 54         D         8         IC1         Phase A Position Hall via J3 (A)         Back EMF Crossing #1 via J1 if LK4 in Position 2-3           55         D         9         IC2         Phase B Position Hall via J3 (B)         Back EMF Crossing #2 via J1 if LK5 in Position 2-3           56         D         10         IC3         Phase C Position Hall via J3 (B)         Back EMF Crossing #3 via J1           57         D         11         RD11         Active Low FIRE_ENABLE         —           64         D         12         —         IC5/RD12 via J7 (RD12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 69                                                | D    | 7        | UPDN |                                  | RD7 output to Direction LED (D5)  |