Single 8 bits ADC, up to 40 MHz Rev. 02 — 18 August 2008

Product data sheet

#### 1. **General description**

The ADC0801S040 is an 8-bit universal analog-to-digital converter (ADC) for video and general purpose applications. It converts the analog input signal from 2.7 V to 5.5 V into 8-bit binary-coded digital words at a maximum sampling rate of 40 MHz. All digital inputs and outputs are CMOS/Transistor-Transistor Logic (TTL) compatible. A sleep mode allows reduction of the device power consumption to 4 mW.

#### **Features** 2.

- 8-bit resolution

- Operation between 2.7 V and 5.5 V

- Sampling rate up to 40 MHz

- DC sampling allowed

- High signal-to-noise ratio over a large analog input frequency range (7.3 effective bits at 4.43 MHz full-scale input at f<sub>clk</sub> = 40 MHz)

- CMOS/TTL compatible digital inputs and outputs

- External reference voltage regulator

- Power dissipation only 30 mW (typical value)

- Low analog input capacitance, no buffer amplifier required

- Sleep mode (4 mW)

- No sample-and-hold circuit required

#### **Applications** 3.

- Video data digitizing

- Camera

- Camcorder

- Radio communication

- Car alarm system

### 4. Quick reference data

#### Table 1. Quick reference data

$V_{DDA} = V5$  to V6 = 3.3 V;  $V_{DDD} = V3$  to V4 = 3.3 V;  $V_{DDO} = V20$  to V11 = 3.3 V;  $V_{SSA}$ ,  $V_{SSD}$  and  $V_{SSO}$  shorted together;  $V_{i(a)(p-p)} = 1.84$  V;  $C_L = 20$  pF;  $T_{amb} = 0$  °C to 70 °C; typical values measured at  $T_{amb} = 25$  °C unless otherwise specified.

| Symbol                | Parameter                     | Conditions                                                        | Min  | Тур   | Max   | Unit |

|-----------------------|-------------------------------|-------------------------------------------------------------------|------|-------|-------|------|

| V <sub>DDA</sub>      | analog supply<br>voltage      |                                                                   | 2.7  | 3.3   | 5.5   | V    |

| V <sub>DDD</sub>      | digital supply<br>voltage     |                                                                   | 2.7  | 3.3   | 5.5   | V    |

| V <sub>DDO</sub>      | output supply voltage         |                                                                   | 2.5  | 3.3   | 5.5   | V    |

| $\Delta V_{DD}$       | supply voltage                | $V_{DDA} - V_{DDD}$                                               | -0.2 | -     | +0.2  | V    |

| difference            | difference                    | $V_{DDD} - V_{DDO}$                                               | -0.2 | -     | +2.25 | V    |

| I <sub>DDA</sub>      | analog supply current         |                                                                   | -    | 4     | 6     | mA   |

| I <sub>DDD</sub>      | digital supply current        |                                                                   | -    | 5     | 8     | mA   |

| I <sub>DDO</sub>      | output supply current         | $f_{clk} = 40 \text{ MHz}$ ; ramp input;<br>$C_L = 20 \text{ pF}$ | -    | 1     | 2     | mA   |

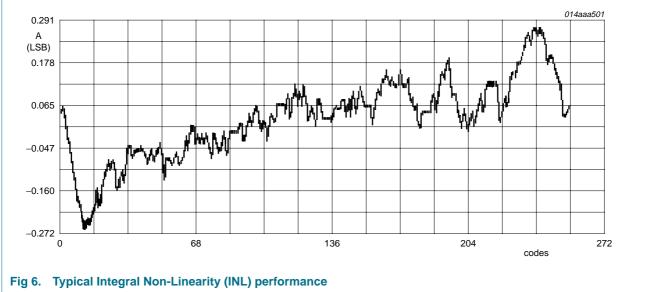

| INL                   | integral<br>non-linearity     | ramp input; see <u>Figure 6</u>                                   | -    | ±0.5  | ±0.75 | LSB  |

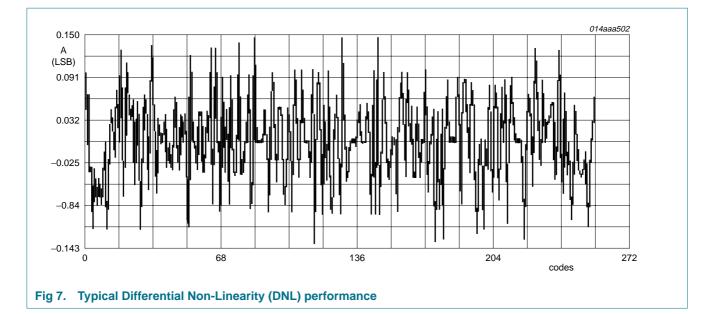

| DNL                   | differential<br>non-linearity | ramp input; see Figure 7                                          | -    | ±0.25 | ±0.5  | LSB  |

| f <sub>clk(max)</sub> | maximum<br>clock<br>frequency |                                                                   | 40   | -     | -     | MHz  |

| P <sub>tot</sub>      | total power dissipation       | $V_{DDA} = V_{DDD} = V_{DDO} = 3.3 V$                             | -    | 30    | 53    | mW   |

|                       |                               |                                                                   |      |       |       |      |

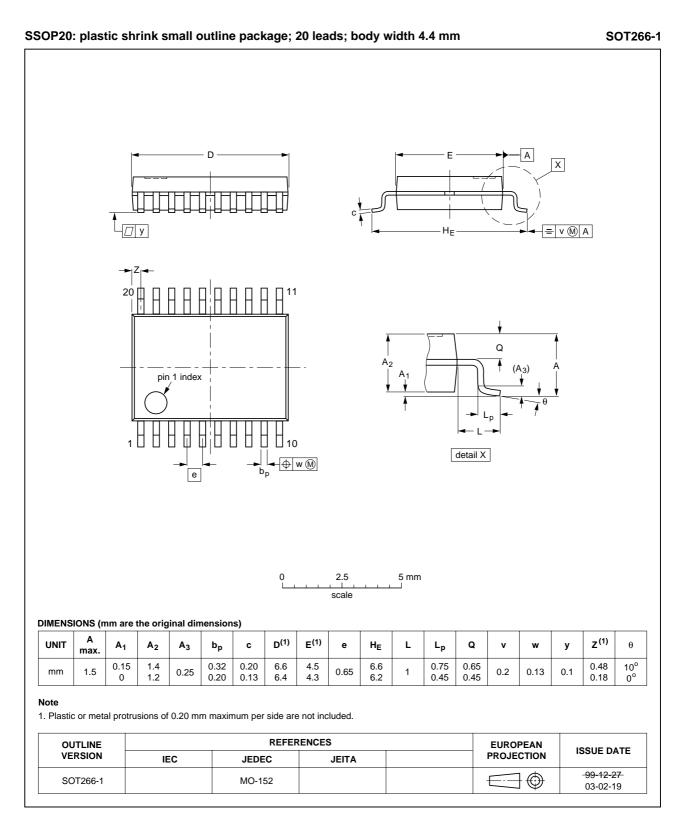

### 5. Ordering information

#### Table 2.Ordering information

| Type number   | Package |                                                                   |          |  |

|---------------|---------|-------------------------------------------------------------------|----------|--|

|               | Name    | Description                                                       | Version  |  |

| ADC0801S040TS | SSOP20  | plastic shrink small outline package; 20 leads; body width 4.4 mm | SOT266-1 |  |

Single 8 bits ADC, up to 40 MHz

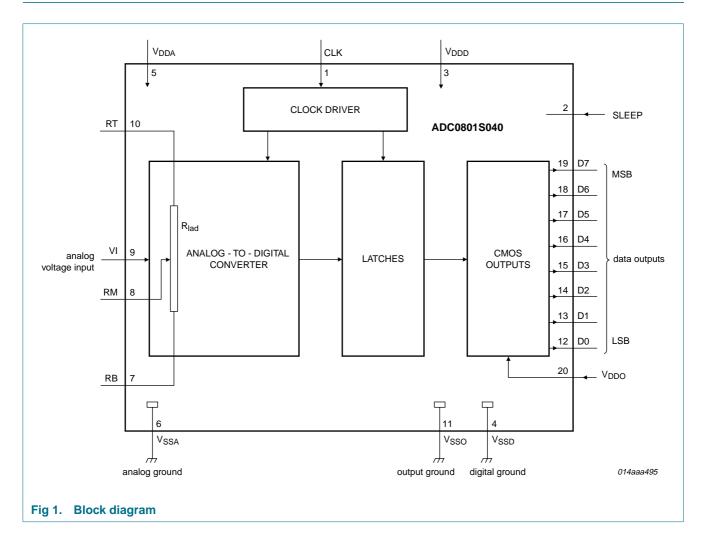

### 6. Block diagram

ADC0801S040\_2

Single 8 bits ADC, up to 40 MHz

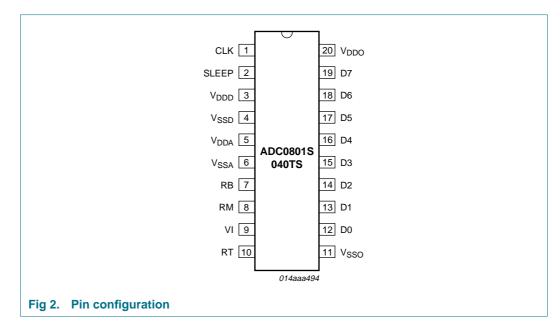

## 7. Pinning information

### 7.1 Pinning

#### 7.2 Pin description

| Table 3.         | Pin description |                                                  |

|------------------|-----------------|--------------------------------------------------|

| Symbol           | Pin             | Description                                      |

| CLK              | 1               | clock input                                      |

| SLEEP            | 2               | sleep mode input                                 |

| V <sub>DDD</sub> | 3               | digital supply voltage (2.7 V to 5.5 V)          |

| $V_{SSD}$        | 4               | digital ground                                   |

| $V_{DDA}$        | 5               | analog supply voltage (2.7 V to 5.5 V)           |

| $V_{SSA}$        | 6               | analog ground                                    |

| RB               | 7               | reference voltage BOTTOM input                   |

| RM               | 8               | reference voltage MIDDLE                         |

| VI               | 9               | analog input voltage                             |

| RT               | 10              | reference voltage TOP input                      |

| V <sub>SSO</sub> | 11              | output stage ground                              |

| D0               | 12              | data output; bit 0 (Least Significant Bit (LSB)) |

| D1               | 13              | data output; bit 1                               |

| D2               | 14              | data output; bit 2                               |

| D3               | 15              | data output; bit 3                               |

| D4               | 16              | data output; bit 4                               |

| D5               | 17              | data output; bit 5                               |

ADC0801S040\_2

Product data sheet

| Table 3.         | Pin description | continued                                                 |

|------------------|-----------------|-----------------------------------------------------------|

| Symbol           | Pin             | Description                                               |

| D6               | 18              | data output; bit 6                                        |

| D7               | 19              | data output; bit 7 (Most Significant Bit (MSB))           |

| V <sub>DDO</sub> | 20              | positive supply voltage for output stage (2.7 V to 5.5 V) |

### 8. Limiting values

#### Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                   | Parameter                        | Conditions                                                                           | Min             | Мах       | Unit |

|--------------------------|----------------------------------|--------------------------------------------------------------------------------------|-----------------|-----------|------|

| V <sub>DDA</sub>         | analog supply voltage            |                                                                                      | <u>[1]</u> –0.3 | +7.0      | V    |

| V <sub>DDD</sub>         | digital supply voltage           |                                                                                      | <u>[1]</u> –0.3 | +7.0      | V    |

| V <sub>DDO</sub>         | output supply voltage            |                                                                                      | <u>[1]</u> –0.3 | +7.0      | V    |

| $\Delta V_{DD}$          | supply voltage difference        | $\begin{array}{l} V_{DDA}-V_{DDD};\\ V_{DDD}-V_{DDO};\\ V_{DDA}-V_{DDO} \end{array}$ | -0.1            | +4.0      | V    |

| VI                       | input voltage                    | referenced to<br>V <sub>SSA</sub>                                                    | -0.3            | +7.0      | V    |

| V <sub>i(clk)(p-p)</sub> | peak-to-peak clock input voltage | referenced to<br>V <sub>SSD</sub>                                                    | -               | $V_{DDD}$ | V    |

| lo                       | output current                   |                                                                                      | -               | 10        | mA   |

| T <sub>stg</sub>         | storage temperature              |                                                                                      | -55             | +150      | °C   |

| T <sub>amb</sub>         | ambient temperature              |                                                                                      | -20             | +75       | °C   |

| Tj                       | junction temperature             |                                                                                      | -               | 150       | °C   |

[1] The supply voltages  $V_{DDA}$ ,  $V_{DDD}$  and  $V_{DDO}$  may have any value between -0.3 V and +7.0 V provided that the supply voltage  $\Delta V_{DD}$  remains as indicated.

### 9. Thermal characteristics

| Table 5.             | Thermal characteristics                     |             |       |      |

|----------------------|---------------------------------------------|-------------|-------|------|

| Symbol               | Parameter                                   | Condition   | Value | Unit |

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air | 120   | K/W  |

### **10. Characteristics**

#### Table 6. Characteristics

$V_{DDA} = V5$  to V6 = 3.3 V;  $V_{DDD} = V3$  to V4 = 3.3 V;  $V_{DDO} = V20$  to V11 = 3.3 V;  $V_{SSA}$ ,  $V_{SSD}$  and  $V_{SSO}$  shorted together;  $V_{i(a)(p-p)} = 1.84$  V;  $C_L = 20$  pF;  $T_{amb} = 0$  °C to 70 °C; typical values measured at  $T_{amb} = 25$  °C unless otherwise specified.

| Symbol           | Parameter              | Conditions | Min | Тур | Max | Unit |

|------------------|------------------------|------------|-----|-----|-----|------|

| Supplies         |                        |            |     |     |     |      |

| V <sub>DDA</sub> | analog supply voltage  |            | 2.7 | 3.3 | 5.5 | V    |

| V <sub>DDD</sub> | digital supply voltage |            | 2.7 | 3.3 | 5.5 | V    |

| V <sub>DDO</sub> | output supply voltage  |            | 2.5 | 3.3 | 5.5 |      |

ADC0801S040\_2

#### Single 8 bits ADC, up to 40 MHz

#### Table 6. Characteristics ...continued

$V_{DDA} = V5$  to V6 = 3.3 V;  $V_{DDD} = V3$  to V4 = 3.3 V;  $V_{DDO} = V20$  to V11 = 3.3 V;  $V_{SSA}$ ,  $V_{SSD}$  and  $V_{SSO}$  shorted together;  $V_{i(a)(p-p)} = 1.84$  V;  $C_L = 20$  pF;  $T_{amb} = 0$  °C to 70 °C; typical values measured at  $T_{amb} = 25$  °C unless otherwise specified.

| Symbol                           | Parameter                                  | Conditions                                       | Min                | Тур  | Max                  | Unit |

|----------------------------------|--------------------------------------------|--------------------------------------------------|--------------------|------|----------------------|------|

| $\Delta V_{DD}$                  | supply voltage difference                  | $V_{DDA} - V_{DDD}$                              | -0.2               | -    | +0.2                 | V    |

|                                  |                                            | $V_{DDD} - V_{DDO}$                              | -0.2               | -    | +2.25                | V    |

| I <sub>DDA</sub>                 | analog supply current                      |                                                  | -                  | 4    | 6                    | mA   |

| I <sub>DDD</sub>                 | digital supply current                     |                                                  | -                  | 5    | 8                    | mA   |

| I <sub>DDO</sub>                 | output supply current                      | $f_{clk}$ = 40 MHz; ramp input;<br>$C_L$ = 20 pF | -                  | 1    | 2                    | mA   |

| P <sub>tot</sub>                 | total power dissipation                    | $V_{DDA} = V_{DDD} = V_{DDO} = 3.3 V$            | -                  | 30   | 53                   | mW   |

| Inputs                           |                                            |                                                  |                    |      |                      |      |

| Clock input                      | CLK (Referenced to V <sub>SSD</sub> )[     | 1]                                               |                    |      |                      |      |

| V <sub>IL</sub>                  | LOW-level input voltage                    |                                                  | 0                  | -    | $0.3 V_{DDD}$        | V    |

| VIH                              | HIGH-level input voltage                   | $V_{DDD} \le 3.6 \text{ V}$                      | $0.6 V_{DDD}$      | -    | V <sub>DDD</sub>     | V    |

|                                  |                                            | V <sub>DDD</sub> > 3.6 V                         | $0.7 V_{DDD}$      | -    | V <sub>DDD</sub>     | V    |

| I <sub>IL</sub>                  | LOW-level input current                    | $V_{clk} = 0.3 V_{DDD}$                          | -1                 | 0    | +1                   | μA   |

| I <sub>IH</sub>                  | HIGH-level input current                   | $V_{clk} = 0.7 V_{DDD}$                          | -                  | -    | 5                    | μA   |

| Zi                               | input impedance                            | f <sub>clk</sub> = 40 MHz                        | -                  | 4    | -                    | kΩ   |

| Ci                               | input capacitance                          | f <sub>clk</sub> = 40 MHz                        | -                  | 3    | -                    | pF   |

| Input SLEE                       | P (Referenced to V <sub>SSD</sub> ); see   | e <u>Table 8</u>                                 |                    |      |                      |      |

| VIL                              | LOW-level input voltage                    |                                                  | 0                  | -    | $0.3 V_{\text{DDD}}$ | V    |

| V <sub>IH</sub> HIGH-level input | HIGH-level input voltage                   | $V_{DDD} \le 3.6 \text{ V}$                      | $0.6 V_{DDD}$      | -    | V <sub>DDD</sub>     | V    |

|                                  |                                            | V <sub>DDD</sub> > 3.6 V                         | $0.7 V_{DDD}$      | -    | V <sub>DDD</sub>     | V    |

| IIL                              | LOW-level input current                    | $V_{IL} = 0.3 V_{DDD}$                           | -1                 | -    | -                    | μA   |

| I <sub>IH</sub>                  | HIGH-level input current                   | $V_{IH} = 0.7 V_{DDD}$                           | -                  | -    | +1                   | μA   |

| Analog inp                       | ut VI (Referenced to V <sub>SSA</sub> )    |                                                  |                    |      |                      |      |

| IIL                              | LOW-level input current                    | $V_I = V_{RB}$                                   | -                  | 0    | -                    | μA   |

| I <sub>IH</sub>                  | HIGH-level input current                   | $V_I = V_{RT}$                                   | -                  | 9    | -                    | μA   |

| Z <sub>i</sub>                   | input impedance                            | f <sub>i</sub> = 1 MHz                           | -                  | 20   | -                    | kΩ   |

| C <sub>i</sub>                   | input capacitance                          | f <sub>i</sub> = 1 MHz                           | -                  | 2    | -                    | pF   |

| Reference                        | voltages for the resistor la               | adder; see <u>Table 7</u>                        |                    |      |                      |      |

| V <sub>RB</sub>                  | voltage on pin RB                          |                                                  | 1.1                | 1.2  | -                    | V    |

| V <sub>RT</sub>                  | voltage on pin RT                          | $V_{RT} \leq V_{DDA}$                            | 2.7                | 3.3  | V <sub>DDA</sub>     | V    |

| V <sub>ref(dif)</sub>            | differential reference voltage             | $V_{RT} - V_{RB}$                                | 1.5                | 2.1  | 2.7                  | V    |

| I <sub>ref</sub>                 | reference current                          |                                                  | -                  | 0.95 | -                    | mA   |

| R <sub>lad</sub>                 | ladder resistance                          |                                                  | -                  | 2.2  | -                    | kΩ   |

| TC <sub>Rlad</sub>               | ladder resistor<br>temperature coefficient |                                                  | -                  | 4092 | -                    | mΩ/k |

| V <sub>offset</sub>              | offset voltage                             | BOTTOM                                           | [2] _              | 170  | -                    | mV   |

|                                  |                                            | ТОР                                              | [2] _              | 170  | -                    | mV   |

| V <sub>i(a)(p-p)</sub>           | peak-to-peak analog<br>input voltage       |                                                  | <sup>[3]</sup> 1.4 | 1.76 | 2.4                  | V    |

Single 8 bits ADC, up to 40 MHz

#### Table 6. Characteristics ...continued

$V_{DDA} = V5$  to V6 = 3.3 V;  $V_{DDD} = V3$  to V4 = 3.3 V;  $V_{DDO} = V20$  to V11 = 3.3 V;  $V_{SSA}$ ,  $V_{SSD}$  and  $V_{SSO}$  shorted together;  $V_{i(a)(p-p)} = 1.84$  V;  $C_L = 20$  pF;  $T_{amb} = 0$  °C to 70 °C; typical values measured at  $T_{amb} = 25$  °C unless otherwise specified.

| Symbol                | Parameter                                     | Conditions                                                    | Min           | Тур   | Max       | Unit |

|-----------------------|-----------------------------------------------|---------------------------------------------------------------|---------------|-------|-----------|------|

| Digital out           | puts D7 to D0 and IR (Refe                    | erenced to V <sub>SSD</sub> )                                 |               |       |           |      |

| V <sub>OL</sub>       | LOW-level output voltage                      | I <sub>O</sub> = 1 mA                                         | 0             | -     | 0.5       | V    |

| V <sub>OH</sub>       | HIGH-level output voltage                     | $I_0 = -1 \text{ mA}$                                         | $V_{DDO}-0.5$ | -     | $V_{DDO}$ | V    |

| I <sub>OZ</sub>       | OFF-state output current                      | $0.4 \text{ V} < \text{V}_{\text{O}} < \text{V}_{\text{DDO}}$ | -20           | -     | +20       | μΑ   |

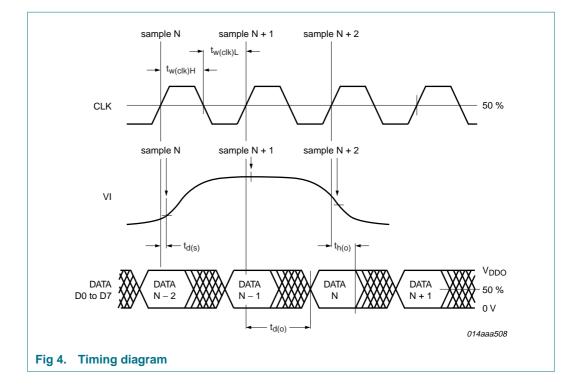

| Clock inpu            | t CLK; see <mark>Figure 4</mark> [1]          |                                                               |               |       |           |      |

| f <sub>clk(max)</sub> | maximum clock<br>frequency                    |                                                               | 40            | -     | -         | MHz  |

| t <sub>w(clk)H</sub>  | HIGH clock pulse width                        |                                                               | 9             | -     | -         | ns   |

| t <sub>w(clk)L</sub>  | LOW clock pulse width                         |                                                               | 9             | -     | -         | ns   |

| Analog sig            | nal processing (f <sub>clk</sub> = 40 M       | 1Hz)                                                          |               |       |           |      |

| Linearity             |                                               |                                                               |               |       |           |      |

| INL                   | integral non-linearity                        | ramp input; see Figure 6                                      | -             | ±0.5  | ±0.75     | LSB  |

| DNL                   | differential non-linearity                    | ramp input; see Figure 7                                      | -             | ±0.25 | ±0.5      | LSB  |

| Bandwidth             |                                               |                                                               |               |       |           |      |

| В                     | bandwidth                                     | full-scale sine wave                                          | [4] _         | 10    |           | MHz  |

|                       |                                               | 75 % full-scale sine wave                                     | -             | 13    |           | MHz  |

|                       |                                               | 50 % full-scale sine wave                                     | -             | 20    |           | MHz  |

|                       |                                               | small signal at mid scale; $V_i = \pm 10$ LSB at code 128     | -             | 350   |           | MHz  |

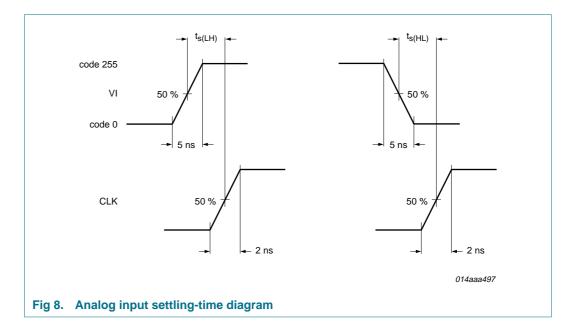

| Input set rea         | sponse; see <u>Figure 8<sup>[5]</sup></u>     |                                                               |               |       |           |      |

| t <sub>s(LH)</sub>    | LOW to HIGH settling time                     | full-scale square wave                                        | -             | 3     | 5         | ns   |

| t <sub>s(HL)</sub>    | HIGH to LOW settling time                     | full-scale square wave                                        | -             | 3     | 5         | ns   |

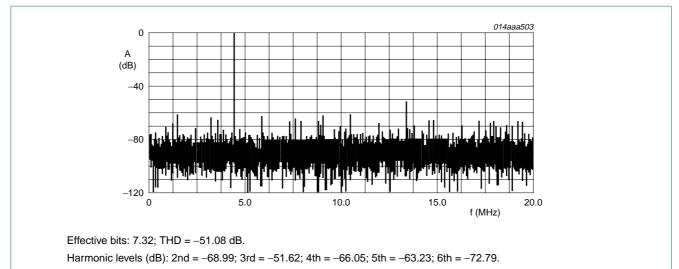

| Harmonics;            | see Figure 9 <sup>[6]</sup>                   |                                                               |               |       |           |      |

| THD                   | total harmonic distortion                     | f <sub>i</sub> = 4.43 MHz                                     | -             | -50   | -         | dB   |

| Signal-to-N           | oise ratio; see <u>Figure 9<sup>[6]</sup></u> |                                                               |               |       |           |      |

| S/N                   | signal-to-noise ratio                         | without harmonics;<br>f <sub>i</sub> = 4.43 MHz               | -             | 47    | -         | dB   |

| Effective bit         | s; see <u>Figure 9<sup>[6]</sup></u>          |                                                               |               |       |           |      |

| ENOB                  | effective number of bits                      | f <sub>i</sub> = 300 MHz                                      | -             | 7.8   | -         | bits |

|                       |                                               | f <sub>i</sub> = 4.43 MHz                                     | -             | 7.3   | -         | bits |

| Differential          | gain[ <u>7]</u>                               |                                                               |               |       |           |      |

| G <sub>dif</sub>      | differential gain                             | PAL modulated ramp                                            | -             | 1.5   | -         | %    |

#### Table 6. Characteristics ... continued

$V_{DDA} = V5$  to V6 = 3.3 V;  $V_{DDD} = V3$  to V4 = 3.3 V;  $V_{DDO} = V20$  to V11 = 3.3 V;  $V_{SSA}$ ,  $V_{SSD}$  and  $V_{SSO}$  shorted together;  $V_{i(a)(p-p)} = 1.84$  V;  $C_L = 20$  pF;  $T_{amb} = 0$  °C to 70 °C; typical values measured at  $T_{amb} = 25$  °C unless otherwise specified.

| Symbol                  | Parameter                                          | Conditions                              | Min | Тур  | Max | Unit |

|-------------------------|----------------------------------------------------|-----------------------------------------|-----|------|-----|------|

| Differential            | phase <sup>[7]</sup>                               |                                         |     |      |     |      |

| φdif                    | differential phase                                 | PAL modulated ramp                      | -   | 0.25 | -   | deg  |

| Timing (f <sub>cl</sub> | <sub>k</sub> = 40 MHz; C <sub>L</sub> = 20 pF); se | ee <mark>Figure 4</mark> <sup>[8]</sup> |     |      |     |      |

| t <sub>d(s)</sub>       | sampling delay time                                |                                         | -   | -    | 5   | ns   |

| t <sub>h(o)</sub>       | output hold time                                   |                                         | 5   | -    | -   | ns   |

| t <sub>d(o)</sub>       | output delay time                                  | V <sub>DDO</sub> = 4.75 V               | 8   | 12   | 15  | ns   |

|                         |                                                    | V <sub>DDO</sub> = 3.15 V               | 8   | 17   | 20  | ns   |

|                         |                                                    | $V_{DDO} = 2.7 V$                       | 8   | 18   | 21  | ns   |

| 3-state out             | tput delay times; see <mark>Figu</mark>            | re <u>5</u>                             |     |      |     |      |

| t <sub>dHZ</sub>        | active HIGH to float delay time                    |                                         | -   | 14   | 18  | ns   |

| t <sub>dZL</sub>        | float to active LOW delay time                     |                                         | -   | 16   | 20  | ns   |

| t <sub>dZH</sub>        | float to active HIGH delay time                    |                                         | -   | 16   | 20  | ns   |

| $t_{dLZ}$               | active LOW to float delay time                     |                                         | -   | 14   | 18  | ns   |

[1] In addition to a good layout of the digital and analog ground, it is recommended that the rise and fall times of the clock must not be less than 1 ns.

[2] Analog input voltages producing code 0 up to and including code 255:

a) V<sub>offset</sub> BOTTOM is the difference between the analog input which produces data equal to 00 and the reference voltage on pin RB (V<sub>RB</sub>) at T<sub>amb</sub> = 25 °C.

- b)  $V_{offset}$  TOP is the difference between the reference voltage on pin RT ( $V_{RT}$ ) and the analog input which produces data outputs equal to code 255 at  $T_{amb}$  = 25 °C.

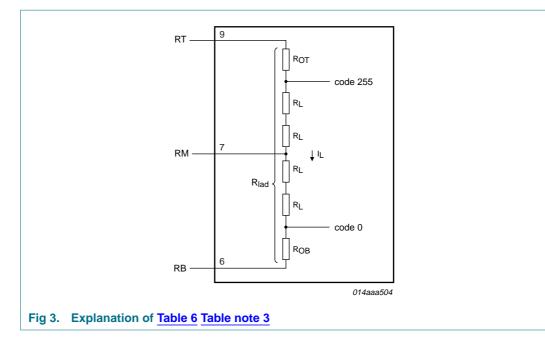

- [3] To ensure the optimum linearity performance of such a converter architecture the lower and upper extremities of the converter reference resistor ladder are connected to pins RB and RT via offset resistors R<sub>OB</sub> and R<sub>OT</sub> as shown in Figure 3.

a) The current flowing into the resistor ladder is  $I = \frac{V_{RT} - V_{RB}}{R_{OB} + R_L + R_{OT}}$  and the full-scale input range at the converter, to cover code 0

to 255 is

$$V_I = R_L \times I_L = \frac{R_L}{R_{OB} + R_L + R_{OT}} \times (V_{RT} + V_{RB}) = 0.838 \times (V_{RT} - V_{RB})$$

b) Since R<sub>L</sub>, R<sub>OB</sub> and R<sub>OT</sub> have similar behavior with respect to process and temperature variation, the ratio  $\frac{R_L}{R_{OB} + R_L + R_{OT}}$

will be kept reasonably constant from device to device. Consequently variation of the output codes at a given input voltage depends mainly on the difference  $V_{RT} - V_{RB}$  and its variation with temperature and supply voltage. When several ADCs are connected in parallel and fed with the same reference source, the matching between each of them is optimized.

- [4] The analog bandwidth is defined as the maximum input sine wave frequency which can be applied to the device. No glitches greater than 2 LSB, nor any significant attenuation is observed in the reconstructed signal.

- [5] The analog input settling time is the minimum time required for the input signal to be stabilized after a sharp full-scale input (square wave signal) in order to sample the signal and obtain correct output data.

- [6] Effective bits are obtained via a Fast Fourier Transform (FFT) treatment taking 8000 acquisition points per equivalent fundamental period. The calculation takes into account all harmonics and noise up to half of the clock frequency (Nyquist frequency). Conversion to signal-to-noise ratio: S/N = ENOB × 6.02 + 1.76 dB.

- [7] Measurement carried out using video analyzer VM700A, where video analog signal is reconstructed through a DAC.

- [8] Output data acquisition: the output data is available after the maximum delay time of  $t_{d(o)}$ .

ADC0801S040 2

Single 8 bits ADC, up to 40 MHz

## 11. Additional information relating to Table 6

#### Table 7. Output coding and input voltage (typical values; referenced to V<sub>SSA</sub>)

| -            | • •                        |                         |

|--------------|----------------------------|-------------------------|

| Code         | V <sub>i(a)(p-p)</sub> (V) | Binary outputs D7 to D0 |

| Underflow    | < 1.37                     | 00 0000 00              |

| 0            | 1.37                       | 00 0000 00              |

| 1            | -                          | 00 0000 01              |

| $\downarrow$ | -                          | $\downarrow$            |

| 254          | -                          | 11 11 11 10             |

| 255          | 3.13                       | 11 11 11 11             |

| Overflow     | > 3.13                     | 11 11 11 11             |

|              |                            |                         |

#### Table 8.Mode selection

| SLEEP | D7 to D0       | I <sub>DDA</sub> + I <sub>DDD</sub> (typ) |

|-------|----------------|-------------------------------------------|

| 1     | high impedance | 1.2 mA                                    |

| 0     | active         | 9 mA                                      |

#### **NXP Semiconductors**

## ADC0801S040

### **NXP Semiconductors**

## ADC0801S040

Single 8 bits ADC, up to 40 MHz

ADC0801S040\_2

#### **NXP Semiconductors**

## ADC0801S040

Single 8 bits ADC, up to 40 MHz

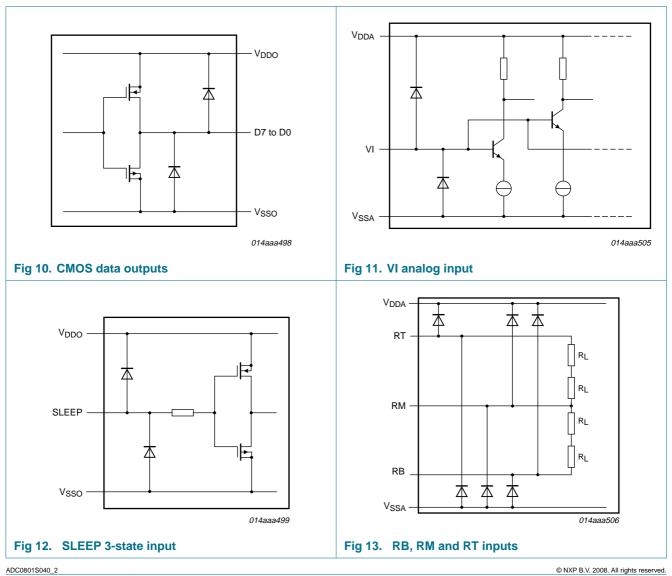

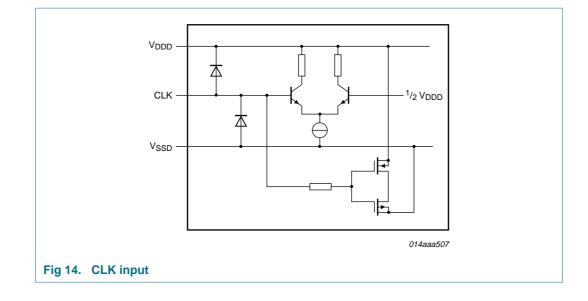

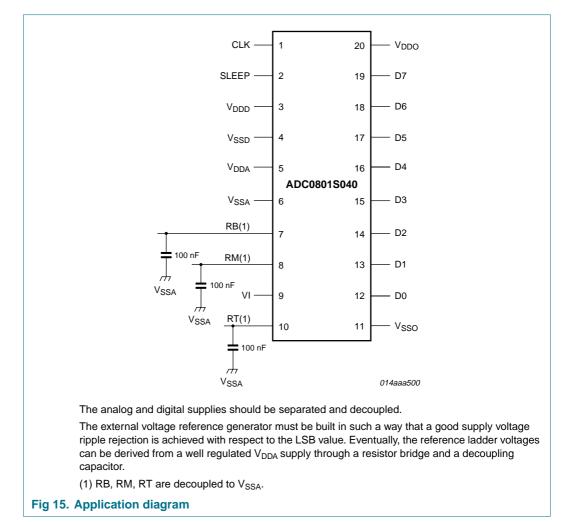

### **12.** Application information

### 12.1 Application diagrams

Single 8 bits ADC, up to 40 MHz

### 13. Package outline

#### Fig 16. Package outline SOT266-1 (SSOP20)

Single 8 bits ADC, up to 40 MHz

## 14. Revision history

| Document ID    | Release date                                                      | Data sheet status  | Change notice | Supersedes    |  |  |

|----------------|-------------------------------------------------------------------|--------------------|---------------|---------------|--|--|

| ADC0801S040_2  | 20080818                                                          | Product data sheet | -             | ADC0801S040_1 |  |  |

| Modifications: | <ul> <li>Corrections made to table notes in Figure 1.</li> </ul>  |                    |               |               |  |  |

|                | <ul> <li>Corrections made to <u>Table 3</u>.</li> </ul>           |                    |               |               |  |  |

|                | <ul> <li>Corrections made to symbol in <u>Table 4</u>.</li> </ul> |                    |               |               |  |  |

|                | • Corrections made to <u>Table 6</u> .                            |                    |               |               |  |  |

|                | <ul> <li>Corrections made to Figure 13</li> </ul>                 |                    |               |               |  |  |

| ADC0801S040_1  | 20080612                                                          | Product data sheet | -             | -             |  |  |

### **15. Legal information**

#### 15.1 Data sheet status

| Document status <sup>[1][2]</sup> | Product status <sup>[3]</sup> | Definition                                                                            |

|-----------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet      | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet    | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet        | Production                    | This document contains the product specification.                                     |

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term 'short data sheet' is explained in section "Definitions".

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

#### 15.2 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

#### 15.3 Disclaimers

**General** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.

Terms and conditions of sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

#### 15.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

### 16. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Single 8 bits ADC, up to 40 MHz

### **17. Contents**

founded by

**PHILIPS**

| 1    | General description 1                        |

|------|----------------------------------------------|

| 2    | Features 1                                   |

| 3    | Applications 1                               |

| 4    | Quick reference data 2                       |

| 5    | Ordering information 2                       |

| 6    | Block diagram 3                              |

| 7    | Pinning information 4                        |

| 7.1  | Pinning 4                                    |

| 7.2  | Pin description 4                            |

| 8    | Limiting values 5                            |

| 9    | Thermal characteristics 5                    |

| 10   | Characteristics 5                            |

| 11   | Additional information relating to Table 6 9 |

| 12   | Application information 15                   |

| 12.1 | Application diagrams 15                      |

| 13   | Package outline 16                           |

| 14   | Revision history 17                          |

| 15   | Legal information 18                         |

| 15.1 | Data sheet status 18                         |

| 15.2 | Definitions                                  |

| 15.3 | Disclaimers                                  |

| 15.4 | Trademarks 18                                |

| 16   | Contact information 18                       |

| 17   | Contents 19                                  |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP B.V. 2008.

All rights reserved.

Date of release: 18 August 2008 Document identifier: ADC0801S040\_2