# Variable Resolution, 10-Bit to 16-Bit R/D Converter with Reference Oscillator

AD2S1210-EP

## **FEATURES**

Complete monolithic resolver-to-digital converter 3125 rps maximum tracking rate (10-bit resolution) ±2.5 arc minutes of accuracy 10-/12-/14-/16-bit resolution, set by user Parallel and serial 10-bit to 16-bit data ports Absolute position and velocity outputs System fault detection **Programmable fault detection thresholds Differential inputs** Incremental encoder emulation Programmable sinusoidal oscillator on board Compatible with DSP and SPI interface standards 5 V supply with 2.3 V to 5 V logic interface Support defense and aerospace applications (AQEC) Military temperature range (-55°C to +125°C) Controlled manufacturing baseline One assembly/test site One fabrication site **Enhanced product change notification** Qualification data available upon request

### **APPLICATIONS**

DC and ac servo motor control

Encoder emulation

Electric power steering

Electric vehicles

Integrated starter generators/alternators

Automotive motion sensing and control

#### **GENERAL DESCRIPTION**

The AD2S1210-EP is a complete 10-bit to 16-bit resolution tracking resolver-to-digital converter, integrating an on-board programmable sinusoidal oscillator that provides sine wave excitation for resolvers.

The converter accepts 3.15 V p-p  $\pm$  27% input signals, in the range of 2 kHz to 20 kHz on the sine and cosine inputs. A Type II servo loop is employed to track the inputs and convert the input sine and cosine information into a digital representation of the input angle and velocity. The maximum tracking rate is 3125 rps.

Full details about this enhanced product, including theory of operation, registers details, and applications information, are available in the AD2S1210 data sheet, which should be concluded in conjunction with this data sheet.

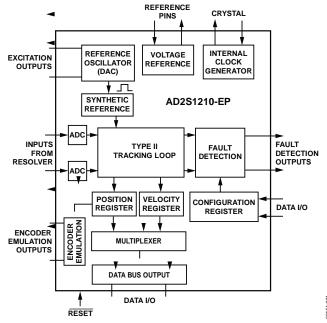

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

### **PRODUCT HIGHLIGHTS**

- Ratiometric tracking conversion. The Type II tracking loop provides continuous output position data without conversion delay. It also provides noise immunity and tolerance of harmonic distortion on the reference and input signals.

- System fault detection. A fault detection circuit can sense loss of resolver signals, out-of-range input signals, input signal mismatch, or loss of position tracking. The fault detection threshold levels can be individually programmed by the user for optimization within a particular application.

- 3. Input signal range. The sine and cosine inputs can accept differential input voltages of 3.15 V p-p  $\pm$  27%.

- 4. Programmable excitation frequency. Excitation frequency is easily programmable to a number of standard frequencies between 2 kHz and 20 kHz.

- Triple format position data. Absolute 10-bit to 16-bit angular position data is accessed via either a 16-bit parallel port or a 4-wire serial interface. Incremental encoder emulation is in standard A-quad-B format with direction output available.

- 6. Digital velocity output. 10-bit to 16-bit signed digital velocity accessed via either a 16-bit parallel port or a 4-wire serial interface.

#### Rev. 0

# **TABLE OF CONTENTS**

| Features                           | I |

|------------------------------------|---|

| Applications                       | 1 |

| Functional Block Diagram           |   |

| Product Highlights                 |   |

|                                    |   |

| Revision History<br>Specifications |   |

|                                    |   |

| Timing Specifications              | 5 |

| Absolute Maximum Ratings                    |    |

|---------------------------------------------|----|

| ESD Caution                                 |    |

| Pin Configuration and Function Descriptions |    |

| Typical Performance Characteristics         | 10 |

| Outline Dimensions                          | 14 |

| Ordering Guide                              | 14 |

## **REVISION HISTORY**

6/10—Revision 0: Initial Version

## **SPECIFICATIONS**

$AV_{\rm DD} = DV_{\rm DD} = 5.0~\rm V \pm 5\%, CLKIN = 8.192~\rm MHz \pm 25\%, EXC, \overline{EXC}~frequency = 10~\rm kHz~to~20~\rm kHz~(10-bit); 6~\rm kHz~to~20~\rm kHz~(12-bit); 3~\rm kHz~to~12~\rm kHz~(14-bit); 2~\rm kHz~to~10~\rm kHz~(16-bit); T_A = T_{\rm MIN}~to~T_{\rm MAX}; unless otherwise noted.$

Table 1.

| Parameter                        | Min  | Тур            | Max        | Unit        | Conditions/Comments                                           |

|----------------------------------|------|----------------|------------|-------------|---------------------------------------------------------------|

| SINE, COSINE INPUTS <sup>2</sup> |      |                |            |             |                                                               |

| Voltage Amplitude                | 2.3  | 3.15           | 4.0        | V p-p       | Sinusoidal waveforms, differential SIN to SINLO, COS to COSLO |

| Input Bias Current               |      |                | 8.25       | μΑ          | $V_{IN} = 4.0 \text{ V p-p, CLKIN} = 8.192 \text{ MHz}$       |

| Input Impedance                  | 485  |                |            | kΩ          | $V_{IN} = 4.0 \text{ V p-p, CLKIN} = 8.192 \text{ MHz}$       |

| Phase Lock Range                 | -44  |                | +44        | Degrees     | Sine/cosine vs. EXC output, Control Register D3 = $0$         |

| Common-Mode Rejection            |      | ±20            |            | arc sec/V   | 10 Hz to 1 MHz, Control Register D4 = 0                       |

| ANGULAR ACCURACY <sup>3</sup>    |      |                |            | a. c 500, t |                                                               |

| Angular Accuracy                 |      | ±2.5 + 1 LSB   | ±7 + 1 LSB | arc min     |                                                               |

| Resolution                       |      | 10, 12, 14, 16 | ±7 1 1 230 | Bits        | No missing codes                                              |

| Linearity INL                    |      | 10, 12, 11, 10 |            | Dits        | 140 missing codes                                             |

| 10-bit                           |      |                | ±1         | LSB         |                                                               |

| 12-bit                           |      |                | ±2         | LSB         |                                                               |

| 14-bit                           |      |                | ±4         | LSB         |                                                               |

| 16-bit                           |      |                | ±4<br>±16  | LSB         |                                                               |

|                                  |      |                |            |             |                                                               |

| Linearity DNL                    |      | . 1            | ±0.9       | LSB         |                                                               |

| Repeatability                    |      | ±1             |            | LSB         |                                                               |

| VELOCITY OUTPUT                  |      |                |            |             |                                                               |

| Velocity Accuracy <sup>4</sup>   |      |                | _          |             |                                                               |

| 10-bit                           |      |                | ±2         | LSB         | Zero acceleration                                             |

| 12-bit                           |      |                | ±2         | LSB         | Zero acceleration                                             |

| 14-bit                           |      |                | ±4         | LSB         | Zero acceleration                                             |

| 16-bit                           |      |                | ±16        | LSB         | Zero acceleration                                             |

| Resolution <sup>5</sup>          |      | 9, 11, 13, 15  |            | Bits        |                                                               |

| DYNAMNIC PERFORMANCE             |      |                |            |             |                                                               |

| Bandwidth                        |      |                |            |             |                                                               |

| 10-bit                           | 2000 |                | 6600       | Hz          |                                                               |

|                                  | 2900 |                | 5400       | Hz          | CLKIN = 8.192 MHz                                             |

| 12-bit                           | 900  |                | 2800       | Hz          |                                                               |

|                                  | 1200 |                | 2200       | Hz          | CLKIN = 8.192 MHz                                             |

| 14-bit                           | 400  |                | 1500       | Hz          |                                                               |

|                                  | 600  |                | 1200       | Hz          | CLKIN = 8.192 MHz                                             |

| 16-bit                           | 100  |                | 350        | Hz          |                                                               |

|                                  | 125  |                | 275        | Hz          | CLKIN = 8.192 MHz                                             |

| Tracking Rate                    |      |                |            |             |                                                               |

| 10-bit                           |      |                | 3125       | rps         | CLKIN = 10.24 MHz                                             |

|                                  |      |                | 2500       |             | CLKIN = 8.192 MHz                                             |

| 12-bit                           |      |                | 1250       | rps         | CLKIN = 10.24 MHz                                             |

|                                  |      |                | 1000       |             | CLKIN = 8.192 MHz                                             |

| 14-bit                           |      |                | 625        | rps         | CLKIN = 10.24 MHz                                             |

|                                  |      |                | 500        |             | CLKIN = 8.192 MHz                                             |

| 16-bit                           |      |                | 156.25     | rps         | CLKIN = 10.24 MHz                                             |

|                                  |      |                | 125        |             | CLKIN = 8.192 MHz                                             |

| Acceleration Error               |      |                |            |             |                                                               |

| 10-bit                           |      | 30             |            | arc min     | At 50,000 rps, <sup>2</sup> CLKIN = 8.192 MHz                 |

| 12-bit                           |      | 30             |            | arc min     | At 10,000 rps, <sup>2</sup> CLKIN = 8.192 MHz                 |

| 14-bit                           |      | 30             |            | arc min     | At 2500 rps, <sup>2</sup> CLKIN = 8.192 MHz                   |

| 16-bit                           |      | 30             |            | arc min     | At 125 rps, <sup>2</sup> CLKIN = 8.192 MHz                    |

| Parameter                                                 | Min  | Тур             | Max  | Unit   | Conditions/Comments                                                                           |

|-----------------------------------------------------------|------|-----------------|------|--------|-----------------------------------------------------------------------------------------------|

| Settling Time 10° Step Input                              |      |                 |      |        |                                                                                               |

| 10-bit                                                    |      | 0.6             | 0.9  | ms     | To settle to within $\pm 2$ LSB, CLKIN = 8.192 MHz                                            |

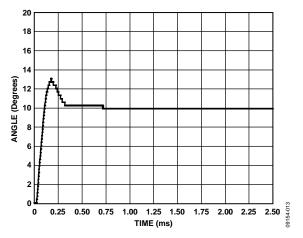

| 12-bit                                                    |      | 2.2             | 3.3  | ms     | To settle to within $\pm 2$ LSB, CLKIN = 8.192 MHz                                            |

| 14-bit                                                    |      | 6.5             | 9.8  | ms     | To settle to within $\pm 2$ LSB, CLKIN = 8.192 MHz                                            |

| 16-bit                                                    |      | 27.5            | 48   | ms     | To settle to within $\pm 2$ LSB, CLKIN = 8.192 MHz                                            |

| Settling Time 179° Step Input                             |      |                 |      |        |                                                                                               |

| 10-bit                                                    |      | 1.5             | 2.4  | ms     | To settle to within $\pm 2$ LSB, CLKIN = 8.192 MHz                                            |

| 12-bit                                                    |      | 4.75            | 6.1  | ms     | To settle to within $\pm 2$ LSB, CLKIN = 8.192 MHz                                            |

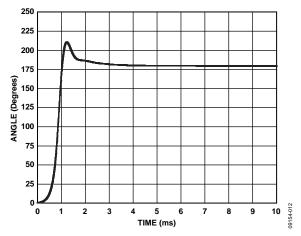

| 14-bit                                                    |      | 10.5            | 15.2 | ms     | To settle to within $\pm 2$ LSB, CLKIN = 8.192 MHz                                            |

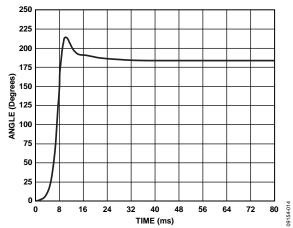

| 16-bit                                                    |      | 45              | 68   | ms     | To settle to within $\pm 2$ LSB, CLKIN = 8.192 MHz                                            |

| EXC, EXC OUTPUTS                                          |      |                 |      |        |                                                                                               |

| Voltage                                                   | 3.2  | 3.6             | 4.0  | V p-p  | Load $\pm 1\underline{00} \mu A$ , typical differential output (EXC to EXC) = 7.2 V p-p       |

| Center Voltage                                            | 2.40 | 2.47            | 2.53 | V      |                                                                                               |

| Frequency                                                 | 2    |                 | 20   | kHz    |                                                                                               |

| EXC/EXC DC Mismatch                                       |      |                 | 30   | mV     |                                                                                               |

| EXC/EXC AC Mismatch                                       |      |                 | 132  | mV     |                                                                                               |

| THD                                                       |      | -58             |      | dB     | First five harmonics                                                                          |

| VOLTAGE REFERENCE                                         |      | 30              |      | us us  | This tive namonies                                                                            |

| REFOUT                                                    | 2.40 | 2.47            | 2.53 | V      | ±I <sub>OUT</sub> = 100 μA                                                                    |

| Drift                                                     | 2.10 | 100             | 2.33 | ppm/°C | _1001 100 μ/τ                                                                                 |

| PSRR                                                      |      | <del>-</del> 60 |      | dB     |                                                                                               |

| CLKIN, XTALOUT <sup>6</sup>                               |      |                 |      | us us  |                                                                                               |

| V <sub>∥</sub> Voltage Input Low                          |      |                 | 0.8  | V      |                                                                                               |

| V <sub>II</sub> Voltage Input High                        | 2.0  |                 | 0.0  | V      |                                                                                               |

| LOGIC INPUTS                                              | 2.0  |                 |      |        |                                                                                               |

| V <sub>IL</sub> Voltage Input Low                         |      |                 | 0.8  | V      | $V_{DRIVE} = 2.7 \text{ V to } 5.25 \text{ V}$                                                |

| vi voltage input 2011                                     |      |                 | 0.7  | V      | $V_{DRIVE} = 2.3 \text{ V to } 2.7 \text{ V}$                                                 |

| V <sub>IH</sub> Voltage Input High                        | 2.0  |                 | 0.7  | V      | $V_{DRIVE} = 2.7 \text{ V to } 5.25 \text{ V}$                                                |

| v <sub>iii</sub> voltage inpactingii                      | 1.7  |                 |      | V      | $V_{DRIVE} = 2.3 \text{ V to } 2.7 \text{ V}$                                                 |

| I <sub>IL</sub> Low Level Input Current (Non-<br>Pull-Up) |      |                 | 10   | μΑ     | URIVE 213 V 80 2.17 V                                                                         |

| I <sub>II</sub> Low Level Input Current (Pull-Up)         |      |                 | 80   | μΑ     | RESO, RES1, RD, WR/FSYNC, A0, A1, and RESET pins                                              |

| I <sub>H</sub> High Level Input Current                   | -10  |                 |      | μA     | у така така така така така така така так                                                      |

| LOGIC OUTPUTS                                             | 10   |                 |      | μπ     |                                                                                               |

| V <sub>OL</sub> Voltage Output Low                        |      |                 | 0.4  | V      | $V_{DRIVE} = 2.3 \text{ V to } 5.25 \text{ V}$                                                |

| V <sub>OH</sub> Voltage Output High                       | 2.4  |                 | 0.1  | ľ      | $V_{DRIVE} = 2.7 \text{ V to } 5.25 \text{ V}$ $V_{DRIVE} = 2.7 \text{ V to } 5.25 \text{ V}$ |

| VOH VOITAGE Output riigii                                 | 2.0  |                 |      | ľ      | $V_{DRIVE} = 2.3 \text{ V to } 2.7 \text{ V}$ $V_{DRIVE} = 2.3 \text{ V to } 2.7 \text{ V}$   |

| I <sub>ozh</sub> High Level Three-State Leakage           | -10  |                 |      | μA     | - DRIVE 2.5 CO 2.7                                                                            |

| I <sub>OZL</sub> Low Level Three-State Leakage            | 10   |                 | 10   | μΑ     |                                                                                               |

| POWER REQUIREMENTS                                        |      |                 |      | ber ,  |                                                                                               |

| AV <sub>DD</sub>                                          | 4.75 |                 | 5.25 | V      |                                                                                               |

| DV <sub>DD</sub>                                          | 4.75 |                 | 5.25 | ľ      |                                                                                               |

| V <sub>DRIVE</sub>                                        | 2.3  |                 | 5.25 | ľ      |                                                                                               |

| POWER SUPPLY                                              | 2.5  |                 | 5.25 | •      |                                                                                               |

| I <sub>AVDD</sub>                                         |      |                 | 12   | mA     |                                                                                               |

| I <sub>DVDD</sub>                                         |      |                 | 35   | mA     |                                                                                               |

| 'טטעט                                                     | 1    |                 | 23   | 1      |                                                                                               |

$<sup>^1</sup>$  Temperature range is as follows: –55°C to +125°C.  $^2$  The voltages SIN, SINLO, COS, and COSLO, relative to AGND, must always be between 0.15 V and AV $_{DD}$  – 0.2 V.

All specifications within the angular accuracy parameter are tested at constant velocity, that is, zero acceleration.

The velocity accuracy specification includes velocity offset and dynamic ripple.

For example, when RESO = 0 and RES1 = 1, the position output has a resolution of 12 bits. The velocity output has a resolution of 11 bits with the MSB indicating the direction of rotation. In this example, with a CLKIN frequency of 8.192 MHz, the velocity LSB is 0.488 rps, that is, 1000 rps/(2<sup>11</sup>).

<sup>&</sup>lt;sup>6</sup> The clock frequency of the AD2S1210-EP can be supplied with a crystal, an oscillator, or directly from a DSP/microprocessor digital output. When using a single-ended clock signal directly from the DSP/microprocessor, the XTALOUT pin should remain open circuit and the logic levels outlined under the logic inputs parameter in Table 1 apply.

## **TIMING SPECIFICATIONS**

$AV_{\rm DD}$  = DV  $_{\rm DD}$  = 5.0 V  $\pm$  5%,  $T_{\rm A}$  =  $T_{\rm MIN}$  to  $T_{\rm MAX,}$  unless otherwise noted.  $^{1}$

Table 2.

| Parameter           | Description                                                                                  | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit    |

|---------------------|----------------------------------------------------------------------------------------------|----------------------------------------------|---------|

| f <sub>clkin</sub>  | Frequency of clock input                                                                     | 6.144                                        | MHz min |

|                     |                                                                                              | 10.24                                        | MHz max |

| ск                  | Clock period $(t_{CK} = 1/f_{CLKIN})$                                                        | 98                                           | ns min  |

|                     |                                                                                              | 163                                          | ns max  |

| t <sub>1</sub>      | A0 and A1 setup time before RD/CS low                                                        | 2                                            | ns min  |

| t <sub>2</sub>      | Delay CS falling edge to WR/FSYNC rising edge                                                | 22                                           | ns min  |

| t <sub>3</sub>      | Address/data setup time during a write cycle                                                 | 3                                            | ns min  |

| t <sub>4</sub>      | Address/data hold time during a write cycle                                                  | 2                                            | ns min  |

| t <sub>5</sub>      | Delay WR/FSYNC rising edge to CS rising edge                                                 | 2                                            | ns min  |

| t <sub>6</sub>      | Delay CS rising edge to CS falling edge                                                      | 10                                           | ns min  |

| t <sub>7</sub>      | Delay between writing address and writing data                                               | $2 \times t_{CK} + 20$                       | ns min  |

| ,<br>t <sub>8</sub> | A0 and A1 hold time after WR/FSYNC rising edge                                               | 2                                            | ns min  |

| t <sub>9</sub>      | Delay between successive write cycles                                                        | $6 \times t_{CK} + 20$                       | ns min  |

| t <sub>10</sub>     | Delay between rising edge of WR/FSYNC and falling edge of RD                                 | 2                                            | ns min  |

| t <sub>11</sub>     | Delay CS falling edge to RD falling edge                                                     | 2                                            | ns min  |

| t <sub>12</sub>     | Enable delay RD low to data valid in configuration mode                                      |                                              |         |

| *12                 | V <sub>DRIVE</sub> = 4.5 V to 5.25 V                                                         | 37                                           | ns min  |

|                     | $V_{DRIVE} = 4.5 \text{ V to } 3.25 \text{ V}$ $V_{DRIVE} = 2.7 \text{ V to } 3.6 \text{ V}$ | 25                                           | ns min  |

|                     | $V_{DRIVE} = 2.3 \text{ V to } 3.6 \text{ V}$ $V_{DRIVE} = 2.3 \text{ V to } 2.7 \text{ V}$  | 30                                           | ns min  |

| 13                  | RD rising edge to CS rising edge                                                             | 2                                            | ns min  |

|                     | Disable delay RD high to data high-Z                                                         | 16                                           | ns min  |

| 14A                 | Disable delay CS high to data high-Z                                                         | 16                                           |         |

| 1 <sub>4B</sub>     |                                                                                              |                                              | ns min  |

| t <sub>15</sub>     | Delay between rising edge of RD and falling edge of WR/FSYNC                                 | 2                                            | ns min  |

| 16                  | SAMPLE pulse width                                                                           | $2 \times t_{CK} + 20$                       | ns min  |

| t <sub>17</sub>     | Delay from SAMPLE before RD/CS low                                                           | $6 \times t_{CK} + 20$                       | ns min  |

| t <sub>18</sub>     | Hold time RD before RD low                                                                   | 2                                            | ns min  |

| 19                  | Enable delay RD/CS low to data valid                                                         |                                              |         |

|                     | $V_{DRIVE} = 4.5 \text{ V to } 5.25 \text{ V}$                                               | 17                                           | ns min  |

|                     | $V_{DRIVE} = 2.7 \text{ V to } 3.6 \text{ V}$                                                | 21                                           | ns min  |

|                     | $V_{DRIVE} = 2.3 \text{ V to } 2.7 \text{ V}$                                                | 33                                           | ns min  |

| t <sub>20</sub>     | RD pulse width                                                                               | 6                                            | ns min  |

| t <sub>21</sub>     | A0 and A1 set time to data valid when RD/CS low                                              |                                              |         |

|                     | $V_{DRIVE} = 4.5 \text{ V to } 5.25 \text{ V}$                                               | 36                                           | ns min  |

|                     | $V_{DRIVE} = 2.7 \text{ V to } 3.6 \text{ V}$                                                | 37                                           | ns min  |

|                     | $V_{DRIVE} = 2.3 \text{ V to } 2.7 \text{ V}$                                                | 29                                           | ns min  |

| t <sub>22</sub>     | Delay WR/FSYNC falling edge to SCLK rising edge                                              | 3                                            | ns min  |

| t <sub>23</sub>     | Delay WR/FSYNC falling edge to SDO release from high-Z                                       |                                              |         |

|                     | $V_{DRIVF} = 4.5 \text{ V to } 5.25 \text{ V}$                                               | 16                                           | ns min  |

|                     | $V_{DRIVE} = 2.7 \text{ V to } 3.6 \text{ V}$                                                | 26                                           | ns min  |

|                     | $V_{DRIVE} = 2.3 \text{ V to } 2.7 \text{ V}$                                                | 29                                           | ns min  |

| -<br>-24            | Delay SCLK rising edge to DBx valid                                                          |                                              |         |

|                     | $V_{DRIVE} = 4.5 \text{ V to } 5.25 \text{ V}$                                               | 24                                           | ns min  |

|                     | $V_{DRIVE} = 2.7 \text{ V to } 3.6 \text{ V}$                                                | 18                                           | ns min  |

|                     | $V_{DRIVE} = 2.3 \text{ V to } 2.7 \text{ V}$                                                | 32                                           | ns min  |

| 25                  | SCLK high time                                                                               | $0.4 \times t_{SCLK}$                        | ns min  |

| t <sub>26</sub>     | SCLK low time                                                                                | $0.4 \times t_{SCLK}$                        | ns min  |

| t <sub>27</sub>     | SDI setup time prior to SCLK falling edge                                                    | 3                                            | ns min  |

| t <sub>28</sub>     | SDI hold time after SCLK falling edge                                                        | 2                                            | ns min  |

| Parameter       | Description                                                   | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit   |

|-----------------|---------------------------------------------------------------|----------------------------------------------|--------|

| t <sub>29</sub> | Delay WR/FSYNC rising edge to SDO high-Z                      | 15                                           | ns min |

| t <sub>30</sub> | Delay from SAMPLE before WR/FSYNC falling edge                | $6 \times t_{CK} + 20 \text{ ns}$            | ns min |

| t <sub>31</sub> | Delay CS falling edge to WR/FSYNC falling edge in normal mode | 2                                            | ns min |

| t <sub>32</sub> | A0 and A1 setup time before WR/FSYNC falling edge             | 2                                            | ns min |

| t <sub>33</sub> | A0 and A1 hold time after WR/FSYNC falling edge <sup>2</sup>  |                                              |        |

|                 | In normal mode, $A0 = 0$ , $A1 = 0/1$                         | $24 \times t_{CK} + 5 \text{ ns}$            | ns min |

|                 | In configuration mode, $A0 = 1$ , $A1 = 1$                    | $8 \times t_{CK} + 5 \text{ ns}$             | ns min |

| t <sub>34</sub> | Delay WR/FSYNC rising edge to WR/FSYNC falling edge           | 10                                           | ns min |

| $f_{SCLK}$      | Frequency of SCLK input                                       |                                              |        |

|                 | $V_{DRIVE} = 4.5 \text{ V to } 5.25 \text{ V}$                | 20                                           | MHz    |

|                 | $V_{DRIVE} = 2.7 \text{ V to } 3.6 \text{ V}$                 | 25                                           | MHz    |

|                 | $V_{DRIVE} = 2.3 \text{ V to } 2.7 \text{ V}$                 | 15                                           | MHz    |

<sup>&</sup>lt;sup>1</sup> Temperature range is as follows: -55°C to +125°C.

<sup>2</sup> A0 and A1 should remain constant for the duration of the serial readback. This may require 24 clock periods to read back the 8-bit fault information in addition to the 16 bits of position/velocity data. If the fault information is not required, A0/A1 may be released after 16 clock cycles.

## **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Table 3.                                              |                                               |

|-------------------------------------------------------|-----------------------------------------------|

| Parameter                                             | Rating                                        |

| AV <sub>DD</sub> to AGND, DGND                        | −0.3 V to +7.0 V                              |

| DV <sub>DD</sub> to AGND, DGND                        | −0.3 V to +7.0 V                              |

| V <sub>DRIVE</sub> to AGND, DGND                      | $-0.3 \text{ V to AV}_{DD}$                   |

| $AV_{DD}$ to $DV_{DD}$                                | −0.3 V to +0.3 V                              |

| AGND to DGND                                          | −0.3 V to +0.3 V                              |

| Analog Input Voltage to AGND                          | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$   |

| Digital Input Voltage to DGND                         | $-0.3 \text{ V to V}_{DRIVE} + 0.3 \text{ V}$ |

| Digital Output Voltage to DGND                        | $-0.3 \text{ V to V}_{DRIVE} + 0.3 \text{ V}$ |

| Analog Output Voltage Swing                           | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$   |

| Input Current to Any Pin Except Supplies <sup>1</sup> | ±10 mA                                        |

| Operating Temperature Range (Ambient)                 |                                               |

| EP Grade                                              | −55°C to +125°C                               |

| Storage Temperature Range                             | −65°C to +150°C                               |

| $\theta_{JA}$ Thermal Impedance <sup>2</sup>          | 54°C/W                                        |

| $\theta_{JC}$ Thermal Impedance <sup>2</sup>          | 15°C/W                                        |

| RoHS-Compliant Temperature, Soldering<br>Reflow       | 260(-5/+0)°C                                  |

| ESD                                                   | 2 kV HBM                                      |

<sup>&</sup>lt;sup>1</sup> Transient currents of up to 100 mA do not cause latch-up.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> JEDEC 2S2P standard board.

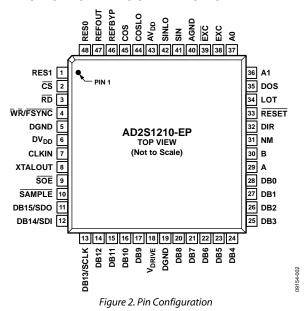

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

**Table 4. Pin Function Descriptions**

|       | Till Fulletio | ii Descriptions                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin   |               |                                                                                                                                                                                                                                                                                                                                                                                                    |

| No.   | Mnemonic      | Description                                                                                                                                                                                                                                                                                                                                                                                        |

| 1     | RES1          | Resolution Select 1. Logic input. RES1 in conjunction with RES0 allows the resolution of the AD2S1210-EP to be programmed.                                                                                                                                                                                                                                                                         |

| 2     | CS            | Chip Select. Active low logic input. The device is enabled when $\overline{CS}$ is held low.                                                                                                                                                                                                                                                                                                       |

| 3     | RD            | Edge-Triggered Logic Input. When the SOE pin is high, this pin acts as a frame synchronization signal and output enable for the parallel data outputs, DB15 to DB0. The output buffer is enabled when CS and RD are held low. When the SOE pin is low, the RD pin should be held high.                                                                                                             |

| 4     | WR/FSYNC      | Edge-Triggered Logic Input. When the SOE pin is high, this pin acts as a frame synchronization signal and input enable for the parallel data inputs, DB7 to DB0. The input buffer is enabled when CS and WR/FSYNC are held low.  When the SOE pin is low, the WR/FSYNC pin acts as a frame synchronization signal and enable for the serial data bus.                                              |

| 5, 19 | DGND          | Digital Ground. These pins are ground reference points for digital circuitry on the AD2S1210-EP. Refer all digital input signals to this DGND voltage. Both of these pins can be connected to the AGND plane of a system. The DGND and AGND voltages should ideally be at the same potential and must not be more than 0.3 V apart, even on a transient basis.                                     |

| 6     | $DV_{DD}$     | Digital Supply Voltage, 4.75 V to 5.25 V. This is the supply voltage for all digital circuitry on the AD2S1210-EP. The AV <sub>DD</sub> and DV <sub>DD</sub> voltages should ideally be at the same potential and must not be more than 0.3 V apart, even on a transient basis.                                                                                                                    |

| 7     | CLKIN         | Clock Input. A crystal or oscillator can be used at the CLKIN and XTALOUT pins to supply the required clock frequency of the AD2S1210-EP. Alternatively, a single-ended clock can be applied to the CLKIN pin. The input frequency of the AD2S1210-EP is specified from 6.144 MHz to 10.24 MHz.                                                                                                    |

| 8     | XTALOUT       | Crystal Output. When using a crystal or oscillator to supply the clock frequency to the AD2S1210-EP, apply the crystal across the CLKIN and XTALOUT pins. When using a single-ended clock source, the XTALOUT pin should be considered a no connect pin.                                                                                                                                           |

| 9     | SOE           | Serial Output Enable. Logic input. This pin enables either the parallel or serial interface. The serial interface is selected by holding the SOE pin low, and the parallel interface is selected by holding the SOE pin high.                                                                                                                                                                      |

| 10    | SAMPLE        | Sample Result. Logic input. Data is transferred from the position and velocity integrators to the position and velocity registers after a high-to-low transition on the SAMPLE signal. The fault register is also updated after a high-to-low transition on the SAMPLE signal.                                                                                                                     |

| 11    | DB15/SDO      | Data Bit 15/Serial Data Output Bus. When the SOE pin is high, this pin acts as DB15, a three-state data output pin controlled by CS and RD. When the SOE pin is low, this pin acts as SDO, the serial data output bus controlled by CS and WR/FSYNC. The bits are clocked out on the rising edge of SCLK.                                                                                          |

| 12    | DB14/SDI      | Data Bit 14/Serial Data Input Bus. When the $\overline{SOE}$ pin is high, this pin acts as DB14, a three-state data output pin controlled by $\overline{CS}$ and $\overline{RD}$ . When the $\overline{SOE}$ pin is low, this pin acts as SDI, the serial data input bus controlled by $\overline{CS}$ and $\overline{WR}/\overline{FSYNC}$ . The bits are clocked in on the falling edge of SCLK. |

| Pin<br>No.  | Mnemonic           | Description                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|-------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 13          | DB13/SCLK          | Data Bit 13/Serial Clock. In parallel mode, this pin acts as DB13, a three-state data output pin controlled by $\overline{\text{CS}}$ and $\overline{\text{RD}}$ . In serial mode, this pin acts as the serial clock input.                                                                                                                                                     |  |  |  |  |

| 14 to<br>17 | DB12 to<br>DB9     | Data Bit 12 to Data Bit 9. Three-state data output pins controlled by $\overline{\text{CS}}$ and $\overline{\text{RD}}$ .                                                                                                                                                                                                                                                       |  |  |  |  |

| 18          | V <sub>DRIVE</sub> | Logic Power Supply Input. The voltage supplied at this pin determines at what voltage the interface operates. Decouple this pin to DGND. The voltage range on this pin is 2.3 V to 5.25 V and may be different from the voltage range at $AV_{DD}$ and $DV_{DD}$ but should never exceed either by more than 0.3 V.                                                             |  |  |  |  |

| 20          | DB8                | Data Bit 8. Three-state data output pin controlled by $\overline{\text{CS}}$ and $\overline{\text{RD}}$ .                                                                                                                                                                                                                                                                       |  |  |  |  |

| 21 to<br>28 | DB7 to DB0         | Data Bit 7 to Data Bit 0. Three-state data input/output pins controlled by $\overline{\text{CS}}$ , $\overline{\text{RD}}$ , and $\overline{\text{WR}}/\overline{\text{FSYNC}}$ .                                                                                                                                                                                               |  |  |  |  |

| 29          | A                  | Incremental Encoder Emulation Output A. Logic output. This output is free running and is valid if the resolver format input signals applied to the converter are valid.                                                                                                                                                                                                         |  |  |  |  |

| 30          | В                  | Incremental Encoder Emulation Output B. Logic output. This output is free running and is valid if the resolver format input signals applied to the converter are valid.                                                                                                                                                                                                         |  |  |  |  |

| 31          | NM                 | North Marker Incremental Encoder Emulation Output. Logic output. This output is free running and is valid if the resolver format input signals applied to the converter are valid.                                                                                                                                                                                              |  |  |  |  |

| 32          | DIR                | Direction. Logic output. This output is used in conjunction with the incremental encoder emulation outputs. The DIR output indicates the direction of the input rotation and is high for increasing angular rotation.                                                                                                                                                           |  |  |  |  |

| 33          | RESET              | Reset. Logic input. The AD2S1210-EP requires an external reset signal to hold the $\overline{\text{RESET}}$ input low until $V_{DD}$ is within the specified operating range of 4.75 V to 5.25 V.                                                                                                                                                                               |  |  |  |  |

| 34          | LOT                | Loss of Tracking. Logic output. Loss of tracking (LOT) is indicated by a logic low on the LOT pin and is not latched.                                                                                                                                                                                                                                                           |  |  |  |  |

| 35          | DOS                | Degradation of Signal. Logic output. Degradation of signal (DOS) is detected when either resolver input (sine or cosine) exceeds the specified DOS sine/cosine threshold or when an amplitude mismatch occurs between the sine and cosine input voltages. DOS is indicated by a logic low on the DOS pin.                                                                       |  |  |  |  |

| 36          | A1                 | Mode Select 1. Logic input. A1 in conjunction with A0 allows the mode of the AD2S1210-EP to be selected.                                                                                                                                                                                                                                                                        |  |  |  |  |

| 37          | A0                 | Mode Select 0. Logic input. A0 in conjunction with A1 allows the mode of the AD2S1210-EP to be selected.                                                                                                                                                                                                                                                                        |  |  |  |  |

| 38          | EXC                | Excitation Frequency. Analog output. An on-board oscillator provides the sinusoidal excitation signal (EXC) and its complement signal (EXC) to the resolver. The frequency of this reference signal is programmable via the excitation frequency register.                                                                                                                      |  |  |  |  |

| 39          | EXC                | Excitation Frequency Complement. Analog output. An on-board oscillator provides the sinusoidal excitation signal (EXC) and its complement signal (EXC) to the resolver. The frequency of this reference signal is programmable via the excitation frequency register.                                                                                                           |  |  |  |  |

| 40          | AGND               | Analog Ground. This pin is the ground reference points for analog circuitry on the AD2S1210-EP. Refer all analog input signals and any external reference signal to this AGND voltage. Connect the AGND pin to the AGND plane of a system. The AGND and DGND voltages should ideally be at the same potential and must not be more than 0.3 V apart, even on a transient basis. |  |  |  |  |

| 41          | SIN                | Positive Analog Input of Differential SIN/SINLO Pair. The input range is 2.3 V p-p to 4.0 V p-p.                                                                                                                                                                                                                                                                                |  |  |  |  |

| 42          | SINLO              | Negative Analog Input of Differential SIN/SINLO Pair. The input range is 2.3 V p-p to 4.0 V p-p.                                                                                                                                                                                                                                                                                |  |  |  |  |

| 43          | AV <sub>DD</sub>   | Analog Supply Voltage, 4.75 V to 5.25 V. This pin is the supply voltage for all analog circuitry on the AD2S1210-EP. The $AV_{DD}$ and $DV_{DD}$ voltages ideally should be at the same potential and must not be more than 0.3 V apart, even on a transient basis.                                                                                                             |  |  |  |  |

| 44          | COSLO              | Negative Analog Input of Differential COS/COSLO Pair. The input range is 2.3 V p-p to 4.0 V p-p.                                                                                                                                                                                                                                                                                |  |  |  |  |

| 45          | cos                | Positive Analog Input of Differential COS/COSLO Pair. The input range is 2.3 V p-p to 4.0 V p-p.                                                                                                                                                                                                                                                                                |  |  |  |  |

| 46          | REFBYP             | Reference Bypass. Connect reference decoupling capacitors at this pin. Typical recommended values are 10 $\mu$ F and 0.01 $\mu$ F.                                                                                                                                                                                                                                              |  |  |  |  |

| 47          | REFOUT             | Voltage Reference Output.                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 48          | RES0               | Resolution Select 0. Logic input. RES0 in conjunction with RES1 allows the resolution of the AD2S1210-EP to be programmed.                                                                                                                                                                                                                                                      |  |  |  |  |

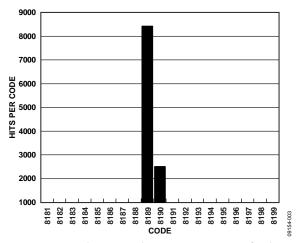

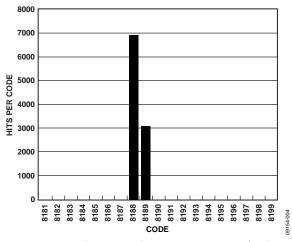

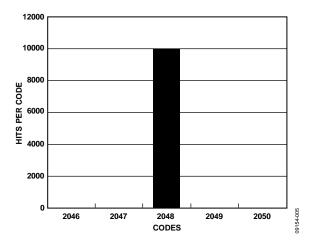

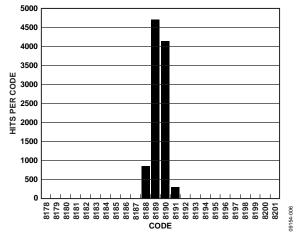

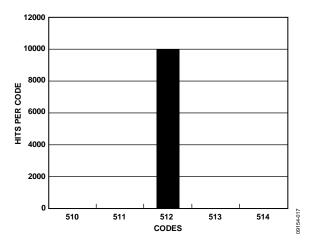

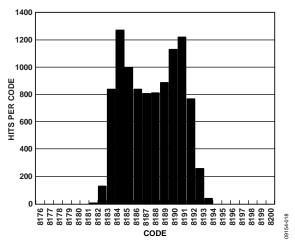

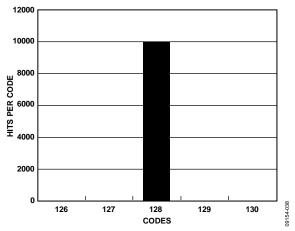

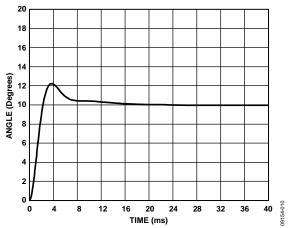

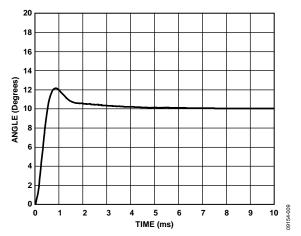

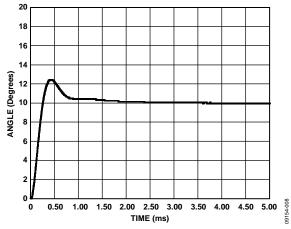

## TYPICAL PERFORMANCE CHARACTERISTICS

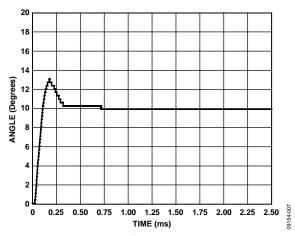

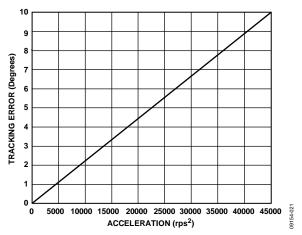

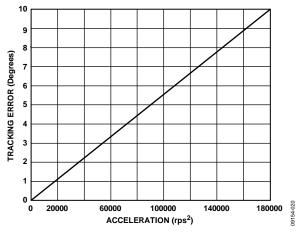

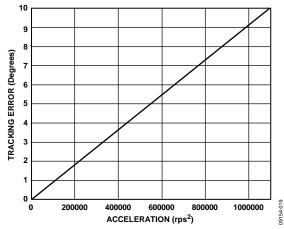

$T_{A} = 25^{\circ}\text{C}, \text{ AV}_{DD} = DV_{DD} = V_{DRIVE} = 5 \text{ V}, \text{SIN/SINLO} = 3.15 \text{ V p-p}, \text{COS/COSLO} = 3.15 \text{ V p-p}, \text{CLKIN} = 8.192 \text{ MHz}, \text{ unless otherwise noted}.$

Figure 3. Typical 16-Bit Angular Accuracy Histogram Of Codes, 10,000 Samples

Figure 4. Typical 14-Bit Angular Accuracy Histogram of Codes, 10,000 Samples, Hysteresis Disabled

Figure 5. Typical 14-Bit Angular Accuracy Histogram of Codes, 10,000 Samples, Hysteresis Enabled

Figure 6. Typical 12-Bit Angular Accuracy Histogram of Codes, 10,000 Samples, Hysteresis Disabled

Figure 7. Typical 12-Bit Angular Accuracy Histogram of Codes, 10,000 Samples, Hysteresis Enabled

Figure 8. Typical 10-Bit Angular Accuracy Histogram of Codes, 10,000 Samples, Hysteresis Disabled

Figure 9. Typical 10-Bit Angular Accuracy Histogram of Codes, 10,000 Samples, Hysteresis Enabled

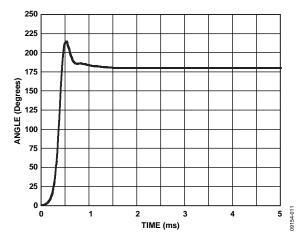

Figure 10. Typical 16-Bit 10° Step Response

Figure 11. Typical 14-Bit 10° Step Response

Figure 12. Typical 12-Bit 10° Step Response

Figure 13. Typical 10-Bit 10° Step Response

Figure 14. Typical 16-Bit 179° Step Response

Figure 15. Typical 14-Bit 179° Step Response

Figure 16. Typical 12-Bit 179° Step Response

Figure 17. Typical 10-Bit 179° Step Response

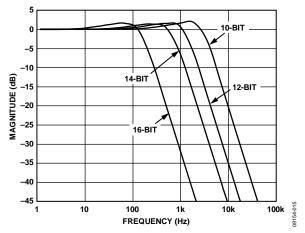

Figure 18. Typical System Magnitude Response

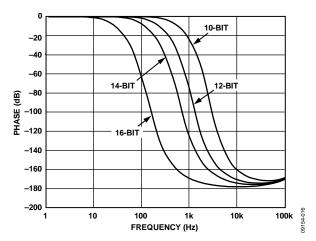

Figure 19. Typical System Phase Response

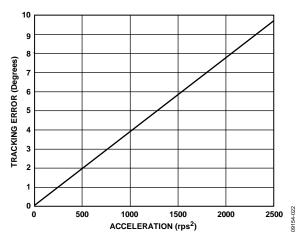

Figure 20. Typical 16-Bit Tracking Error vs. Acceleration

Figure 21. Typical 14-Bit Tracking Error vs. Acceleration

Figure 22. Typical 12-Bit Tracking Error vs. Acceleration

Figure 23. Typical 10-Bit Tracking Error vs. Acceleration

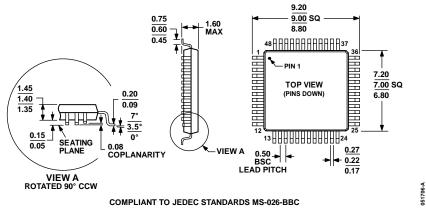

## **OUTLINE DIMENSIONS**

Figure 24. 48-Lead Low Profile Quad Flat Package [LQFP] (ST-48) Dimensions shown in millimeters

## **ORDERING GUIDE**

| Model              | Temperature Range | Package Description | Package Option |

|--------------------|-------------------|---------------------|----------------|

| AD2S1210SST-EP-RL7 | −55°C to +125°C   | 48-Lead LQFP        | ST-48          |

# **NOTES**

| AD2S1210-EP |  |  |

|-------------|--|--|

|-------------|--|--|

NOTES