# Supervisory IC for Desktop Power Supply Monitoring

The NCP4350 provides all the necessary functions to monitor and control a multi-output power supply providing fault protection shutdown signals, and On/Off control. The NCP4350 provides the ability to monitor the status of the +5 Vdc, +12 Vdc (A and B outputs), and +3.3 Vdc output (voltage and current). The controller has built in delay to prevent tripping during transient conditions to eliminate false shutdowns.

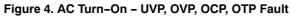

OVP/UVP (OverVoltage/UnderVoltage Protection) monitors 3.3 V, 5 V, and dual 12 V to protect the power supply, FPOB output goes high when one of these supply voltages exceed their limits.

OCP (OverCurrent Protection) monitors 3.3 V, 5 V, and dual 12 V output current. Overcurrent limit is adjustable by  $I_{REF}$  and current protection resistor.

The PGI (Power Good Input) and OTP (OverTemperature Protection) input pin provides the flexibility for design protection circuit.

The PGO (Power Good Output) signal gives personal computer notice when the output supplies are ready or power supply is going to shutdown or fail, therefore it can provide a reliable power supply environment.

# Features

- Individual Overvoltage and Undervoltage Monitoring for +3.3 V, +5 V, +12 VA, +12 VB Outputs and Lockout

- Individual Overcurrent Monitoring for +3.3 V, +5 V, +12 VA, +12 VB Outputs and Lockout

- Fault Output with 5 mA of Sink Capability

- Remote On/Off

- Power Good Output Signal with 5 mA of Sink Capability

- Built-in Delays for OVP, UVP, and Overload to avoid False Tripping

- Low Power Consumption 10 mW at  $V_{CC} = 5 V$  Typical

- Overtemperature Input

- Wide Power Supply Range (4 V 16 V)

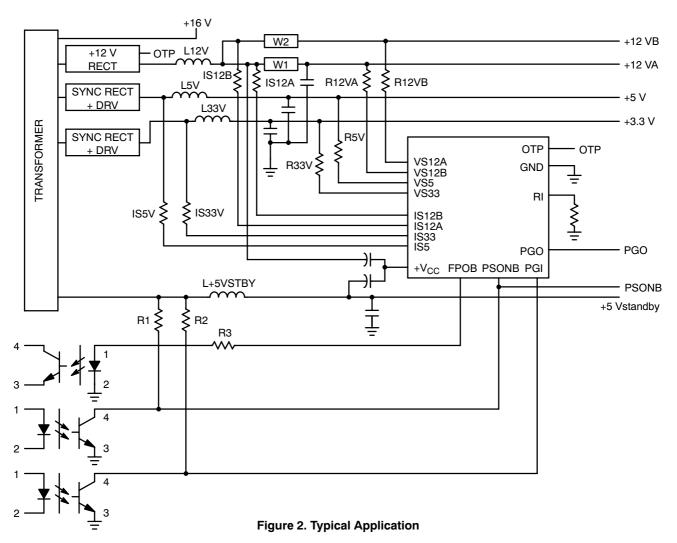

# **Typical Applications**

• ATX Computers

# **ON Semiconductor®**

http://onsemi.com

WW = Work Week

G = Pb-Free Device

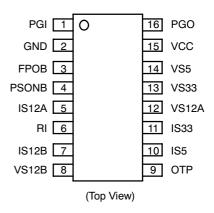

# **PIN CONNECTIONS**

# **ORDERING INFORMATION**

| Device      | Package              | Shipping $^{\dagger}$ |

|-------------|----------------------|-----------------------|

| NCP4350DR2G | SOIC-16<br>(Pb-Free) | 3000/Tape & Reel      |

+ For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

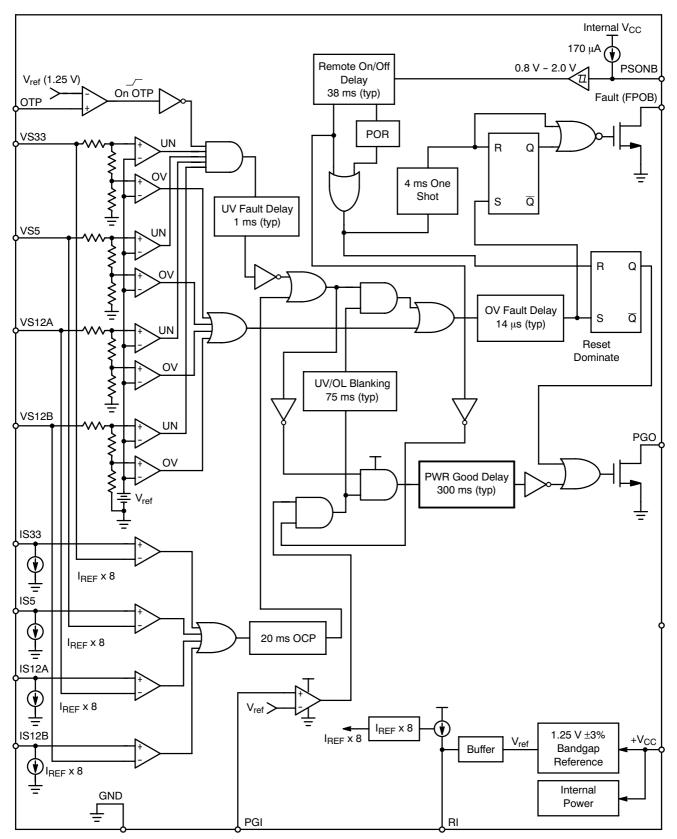

Figure 1. Detailed Block Diagram

# **PIN DESCRIPTION**

| Pin              | Pin# | Description                                                                                           |

|------------------|------|-------------------------------------------------------------------------------------------------------|

| PGI              | 1    | The pin is used for a power good input signal.                                                        |

| GND              | 2    | Ground                                                                                                |

| FPOB             | 3    | This is an open drain output for Fault protection shutdown.                                           |

| PSONB            | 4    | This pin is used for a REMOTE on/off switch input and acts as a reset signal after a fault condition. |

| IS12A            | 5    | This pin is an input to the +12 VA output current monitoring comparator.                              |

| RI               | 6    | A resistor to ground sets the I <sub>REF</sub> current for overcurrent monitoring.                    |

| IS12B            | 7    | This pin is an input to the +12 VB output current monitoring comparator.                              |

| VS12B            | 8    | This pin is an input to the +12 VB output voltage monitoring comparator.                              |

| OTP              | 9    | Overtemperature or external protection input.                                                         |

| IS5              | 10   | This pin is an input to the +5 V output current monitoring comparator.                                |

| IS33             | 11   | This pin is an input to the +3.3 V output current monitoring comparator.                              |

| VS12A            | 12   | This pin is an input to the +12 VA output voltage monitoring comparator.                              |

| VS33             | 13   | This pin is an input to the +3.3 V output voltage monitoring comparator.                              |

| VS5              | 14   | This pin is an input to the +5 V output voltage monitoring comparator.                                |

| +V <sub>CC</sub> | 15   | This is the input pin for $V_{CC}$ .                                                                  |

| PGO              | 16   | This pin provides an open drain power good output signal.                                             |

# **MAXIMUM RATINGS**

| Rating                                  | Symbol                                                  | Value              | Unit    |

|-----------------------------------------|---------------------------------------------------------|--------------------|---------|

| Power Supply Input<br>Current           | V <sub>CC</sub>                                         | -0.3 to 16<br>100  | V<br>mA |

| Maximum Voltage<br>Current              | VS12A<br>VS12B<br>IS12A<br>IS12B                        | -0.3 to 16<br>100  | V<br>mA |

| Maximum Voltage<br>Current              | PGI<br>PSONB<br>OTP<br>VS33<br>IS33                     | -0.3 to 5.5<br>100 | V<br>mA |

| Maximum Voltage                         | V <sub>RI</sub>                                         | 2.0                | V       |

| Power Good Output and FPOB Sink Current | IPGO<br>IFPOB                                           | 5.0                | mA      |

| Maximum Voltage                         | V <sub>OH</sub> PGO, V <sub>OH</sub> FPOB<br>VS5<br>IS5 | 7.5                | V       |

| Output Current from RI                  | I <sub>REF</sub>                                        | 100                | μΑ      |

| Maximum Junction Temperature            | T <sub>JMAX</sub>                                       | 150                | °C      |

| Storage Temperature Range               | T <sub>SMAX</sub>                                       | -65 to 150         | °C      |

| Lead Temperature (Soldering, 10s)       | T <sub>LMAX</sub>                                       | 300                | °C      |

| Total Power Dissipation                 | PD                                                      | TBD                | W       |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. This device series contains ESD protection and exceeds the following tests:

Pins 1–16: Human Body Model 2000V per Mil–Std–883, Method 3015. Machine Model Method 200V

2. This device contains Latch-up protection and exceeds ±100ma per JEDEC Standard JESD78.

### **RECOMMENDED OPERATING CONDITIONS**

| Symbol                                              | Rating                   | Min  | Тур | Max  | Unit |

|-----------------------------------------------------|--------------------------|------|-----|------|------|

| V <sub>CC</sub>                                     | Operating Supply Voltage | 4.0  |     | 16   | V    |

| I <sub>REF</sub>                                    | Output Current from RI   | 12.5 |     | 62.5 | μΑ   |

| T <sub>J</sub> Operating Junction Temperature Range |                          | 0    |     | 105  | °C   |

| <b>ELECTRICAL CHARACTERISTICS</b> ( $V_{CC}$ = 12V, for typical values $T_J$ = 25°C, for min/max values, $T_J$ = 0°C to +105°C, | , |

|---------------------------------------------------------------------------------------------------------------------------------|---|

| Max T <sub>J</sub> = 150°C, R <sub>J</sub> =33 k $\Omega$ , unless otherwise noted.)                                            |   |

| Symbol                             | Rating                                                                                                                                                            | Min  | Тур   | Мах  | Unit |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|------|

| I <sub>CC</sub>                    | Operating Supply Current (VCC = 16V, FPOB $\downarrow$ and PGO <sup>↑</sup> )                                                                                     | -    | 1.5   | 2.0  | mA   |

| Overvoltage/U                      | ndervoltage Protection                                                                                                                                            |      |       |      |      |

| V33OVP                             | $\begin{array}{l} \mbox{VP} \\ \mbox{+3.3V Output Overvoltage Threshold (includes V_{IO})} \\ \mbox{T}_{J} = 0^{\circ} C \mbox{ to } + 105^{\circ} C \end{array}$ |      | 3.9   | 4.0  | V    |

| V33OVP <sub>HYS</sub>              | Hysteresis (Note 3)                                                                                                                                               | -    | 40    | -    | mV   |

| V5OVP                              | +5 V Output Overvoltage Threshold (includes $V_{IO})$ $T_J$ =0°C to +105°C                                                                                        | 5.6  | 5.8   | 6.0  | V    |

| V5OVP <sub>HYS</sub>               | Hysteresis (Note 3)                                                                                                                                               | -    | 60    | -    | mV   |

| V12OVP<br>(A and B)                | +12V Output Overvoltage Threshold (includes $V_{IO}$ )<br>T <sub>J</sub> =0°C to +105°C                                                                           | 13.5 | 13.85 | 14.2 | V    |

| V12OVP <sub>HYS</sub><br>(A and B) | Hysteresis (Note 3)                                                                                                                                               | -    | 130   | -    | mV   |

| V33UVP                             | +3.3V Output Undervoltage Threshold (includes $V_{IO})$ $T_J$ =0°C to +105°C                                                                                      | 2.8  | 2.9   | 3.0  | V    |

| V33UVP <sub>HYS</sub>              | Hysteresis (Note 3)                                                                                                                                               | -    | 30    | -    | mV   |

| V5UVP                              | +5 V Output Undervoltage Threshold (includes $V_{IO}$ )<br>T <sub>J</sub> =0°C to +105°C                                                                          | 4.2  | 4.4   | 4.6  | V    |

| V5UVP <sub>HYS</sub>               | Hysteresis (Note 3)                                                                                                                                               | -    | 45    | -    | mV   |

| V12UVP<br>(A and B)                |                                                                                                                                                                   |      | 10.65 | 11.0 | V    |

| V12UVP <sub>HYS</sub><br>(A and B) | Hysteresis (Note 3)                                                                                                                                               | -    | 100   | -    | mV   |

| Interface I/O                      |                                                                                                                                                                   |      |       |      | •    |

| V <sub>OLFPOB</sub>                | Low Level Output Voltage Fault (I <sub>Sink</sub> = 5 mA)                                                                                                         |      |       | 0.4  | V    |

| I <sub>LFAULT</sub>                | Leakage Current (V <sub>DS</sub> = 5V)                                                                                                                            |      |       | 10   | μA   |

| V <sub>THPGI</sub>                 | Input Voltage Threshold                                                                                                                                           | 1.18 | 1.25  | 1.32 | V    |

| V <sub>OLPGO</sub>                 | Low Level Output Voltage (I <sub>Sink</sub> = 5 mA)                                                                                                               |      |       | 0.4  | V    |

| I <sub>LPGO</sub>                  | Leakage Current (V <sub>DS</sub> = 5V)                                                                                                                            |      |       | 10   | μA   |

| VOLPSONB                           | Low Level Input Voltage                                                                                                                                           |      |       | 0.8  | V    |

| V <sub>OHPSONB</sub>               | High Level Input Voltage                                                                                                                                          | 2.0  |       |      | V    |

| V <sub>PSONBHYS</sub>              | PSONB Input Hysteresis                                                                                                                                            | 300  | -     | -    | mV   |

| PSONBVIH                           | Open Circuit Voltage (I <sub>IN</sub> = 0 mA)                                                                                                                     | 2.5  |       | 5.25 | V    |

| I <sub>LPSONB</sub>                | Input Pull-up Current (V <sub>PSONB</sub> = 0V)                                                                                                                   | 120  | 170   | 220  | μA   |

| Current Monito                     | bring Comparators                                                                                                                                                 |      |       |      |      |

| IS12AV <sub>IO</sub>               | Input Offset Voltage 12VA Comparator, T <sub>J</sub> = +25°C                                                                                                      | -4.0 |       | 4.0  | mV   |

| IS12BV <sub>IO</sub>               | Input Offset Voltage 12VB Comparator, T <sub>J</sub> = +25°C                                                                                                      | -4.0 |       | 4.0  | mV   |

| IS33V <sub>IO</sub>                | Input Offset Voltage 33V Comparator, T <sub>J</sub> = +25°C                                                                                                       | -4.0 | 1     | 4.0  | mV   |

| IS5V <sub>IO</sub>                 | Input Offset Voltage 5V Comparator, $T_J = +25^{\circ}C$                                                                                                          | -4.0 |       | 4.0  | mV   |

| A <sub>VOL</sub>                   | Voltage Gain (Note 3)                                                                                                                                             | 50   | 200   |      | V/mV |

| I <sub>IB</sub>                    | Input Bias Current (V <sub>IS12x</sub> = 12V, V <sub>IS5</sub> = 5V, V <sub>IS33</sub> = 3.3V)                                                                    |      | 300   | 500  | nA   |

| IREFGAIN                           | The Gain of the I_{REF} signal, R_I=33 k $\pm 0.1\%,$ I_{REF} = 1.25/R_I, T_J=+25^{\circ}C                                                                        | 7.68 | 8.0   | 8.32 |      |

| <b>ELECTRICAL CHARACTERISTICS</b> ( $V_{CC}$ = 12V, for typical values $T_J$ = 25°C, for min/max values, $T_J$ = 0°C to +105°C, |  |

|---------------------------------------------------------------------------------------------------------------------------------|--|

| Max T <sub>J</sub> = 150°C, R <sub>I</sub> =33 k $\Omega$ , unless otherwise noted.)                                            |  |

| Symbol                 | Rating                                                                                                                                                                                                                        | Min  | Тур  | Max  | Unit |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Delay Charact          | eristics                                                                                                                                                                                                                      | •    |      |      |      |

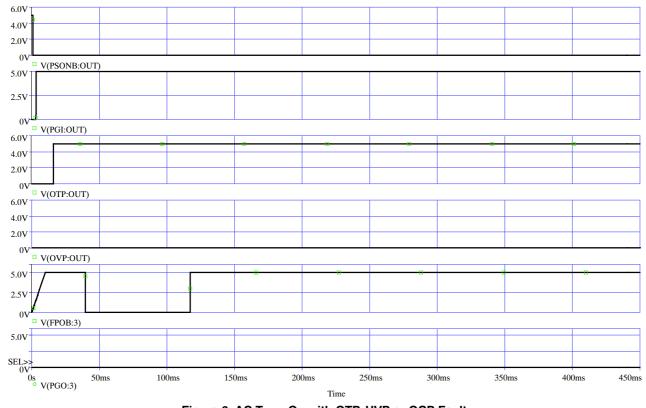

| Tdly <sub>PSONB</sub>  | Time delay On/Off PSONB (PGO↓) 50% of the pull up voltage (PSONB>V <sub>OHPSONB</sub> , R <sub>pull-up</sub> FPOB =1k, V <sub>pull-up</sub> = +5 V)                                                                           | 24   | 38   | 62   | msec |

| Tdly <sub>FOP</sub>    | Time delay between PGO↓ and FPOB↑                                                                                                                                                                                             | 2.0  | 4.0  | 8.0  | msec |

| Tdly <sub>OV</sub>     | Time delay from an OV to FPOB <sup><math>\uparrow</math></sup> and PGO <sup><math>\downarrow</math></sup> 50% of the pull up voltage (PSONB <v<sub>OLPSONB, R<sub>pull-up</sub> FPOB =1k, V<sub>pull-up</sub> = +5 V)</v<sub> | 9.0  | 14   | 19   | μsec |

| Tdly <sub>UV</sub>     | Time delay from an UV to FPOB <sup>↑</sup> and PGO <sup>↓</sup> 50% of the pull up voltage (PSONB <v<sub>OLPSONB, R<sub>pull-up</sub> FPOB =1k, V<sub>pull-up</sub> = +5 V)</v<sub>                                           | 0.5  | 1.0  | 2.0  | msec |

| Tdly <sub>PGO</sub>    | Time delay PGI↑ to PGO↓<br>(PSONB <v<sub>OLPSONB, R<sub>pull-up</sub> PGO =1k, V<sub>pull-up</sub> = +5 V)</v<sub>                                                                                                            | 100  | 300  | 438  | msec |

| Tdlly <sub>START</sub> | Time delay on start-up UV, OC, OTP lockout                                                                                                                                                                                    | 45   | 75   | 130  | msec |

| Tdelay <sub>OTP</sub>  | Time delay from an OTP <sup>↑</sup> to FPOB <sup>↑</sup> and PGO <sup>↓</sup> 50% of the pull up voltage (PSONB <v<sub>OLPSONB, R<sub>pull-up</sub> FPOB and PGO =1k, V<sub>pull-up</sub> = +5 V) OTP<sup>↓</sup></v<sub>     |      | 1.0  | 2.0  | msec |

| Tdly <sub>OCP</sub>    | Time delay from an OCP to FPOB <sup>↑</sup> and PGO <sup>↓</sup> 50% of the pull up voltage (PSONB <v<sub>OLPSONB, R<sub>pull</sub><math>\boxtimes_{up}</math> FPOB and PGO =1k, V<sub>pull-up</sub> = +5 V)</v<sub>          | 11   | 20   | 32   | msec |

| Tdly <sub>PGI</sub>    | Time delay from PSONB↓ to PGO↑ 10–90% of the pull up voltage (PGI>V <sub>THPGI,</sub> R <sub>pull-up</sub> PGO=1k, V <sub>pull-up</sub> = +5V)                                                                                | 124  | 338  | 500  | msec |

| Overtemperate          | ure Input                                                                                                                                                                                                                     |      |      |      |      |

| V <sub>OTP</sub>       | Voltage threshold for OTP $\downarrow$ (PGO $\downarrow$ , FPOB $\uparrow$ , PSONB < V <sub>OL</sub> PSONB, R <sub>pull-up</sub> FPOB and PGO =1k, V <sub>pull-up</sub> = +5 V)                                               | 1.18 | 1.25 | 1.32 | V    |

50

mV

3. Guaranteed by design.

V<sub>OTPHYS</sub>

Overtemperature Comparator Hysteresis (Note 3)

| PGI       | PSONB (REMOTE) | UVP,OVP,OCP | FPOB (FAULT) | PGO |

|-----------|----------------|-------------|--------------|-----|

| <1.25V(L) | L              | No          | L            | L   |

| <1.25V(L) | L              | Yes         | L            | L   |

| >1.25V(H) | L              | No          | L            | Н   |

| >1.25V(H) | L              | Yes         | Н            | L   |

#### **TABLE 1: ASIC TRUTH TABLE**

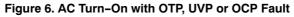

#### **Overload Current Monitoring**

In ATX power supplies the output power must be monitored and limited. In the present ATX specification the +3.3 V and +5 V outputs have a very relaxed tolerance for the over current limit set point. As a result customers typically use the dc resistance in the output filter inductor. If very accuracy current sensing is required, as is the case for the +12 V outputs, a precision current shunt is used.

The circuit operates as shown, when the load current increases the voltage drop across the inductor, or current shunt,- in series (the dc resistance) with the output increases reducing the voltage at the negative input of the overcurrent comparator. The voltage at the positive input to the comparator is set by the I<sub>REF</sub> current source, if the voltage at the negative input to the comparator output goes high indicating an overload condition. The overload trip level can be determined by the following relationships:

$$V_{R} = 8 \times I_{REF} \times R$$

$$R = \frac{RL \cdot IL}{IREF \cdot 8}$$

Example:

$R_{I} = 33 \text{ k}\Omega$  $R_{L} = 0.002 \Omega$  $R = 150 \Omega$

$$I_{\text{REF}} = \frac{V_{\text{REF}}}{R_1} = \frac{1.25 \text{ V}}{33 \text{k}}$$

$$I_{L} = I_{REF} \cdot 8 \cdot \frac{R}{R_{L}} = 37.87 \mu A \cdot 8 \cdot \frac{150}{0.002} = 22.72 \text{ Adc}$$

This calculation neglects input voltage offset, biases currents, and other tolerances.

#### **Output Voltage Sensing**

Four output voltage sense lines are provided +3.3V, +5.0V, +12VA, +12VB. Each of the sensed input signals is inputted into an undervoltage (UVP) and overvoltage (OVP) comparators. In the event of an output fault (OVP or UVP) the fault trigger signal is delayed and then latch. The delay has been added to prevent the Latch from being set during output transient conditions. During start-up the UVP, OTP and OCP comparators output are ignored.

#### Power Good Input

The Power Good input (PGI) can be used to monitor an additional logic event, for example the temperature inside an ATX power supply. When the input voltage at the PGI is below the threshold 1.25 V, the Power Good Output (PGO) signal remains in a low state, even if all of the voltage and current sensed inputs are within the voltage and current limits.

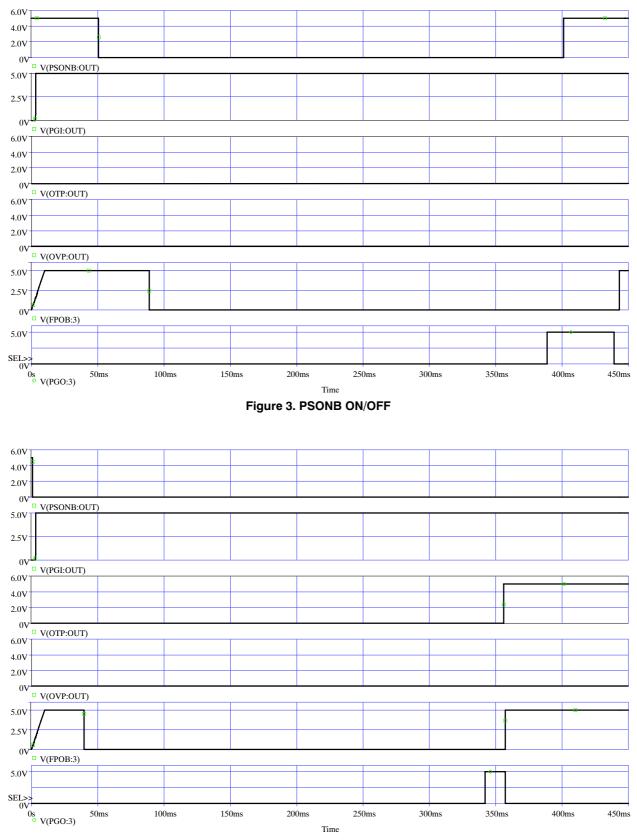

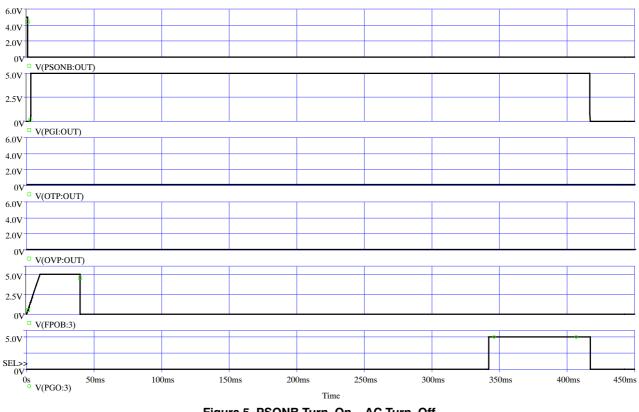

### PSONB

The PSONB input is active low and is used to turn on/off the primary side controller. The PSONB signal can also be used to reset the PGO output after a fault a condition has occurred. When the PSONB signal is low (the external connection), the Fault signal between the monitoring controller and the power supply is enabled (FAULT will be low, no Fault). In order to reset the Fault latch a minimum width pulse should be applied to the PSONB input, the pulse should be greater than 38 msec (typical).

#### **Power Good Output**

The Power Good (PGO) signal is intended to warn the motherboard that the output voltage or current of at least one of the four outputs is out of tolerance. The PGO signal is delayed by 300 msec (typical) to avoid false tripping due to transient conditions. The PGO output is capable of sinking 5 mA of current.

#### **FPOB Output**

In a typical application (refer to Figure 2) the Fault pin is activated (high level) when any one of four outputs is out of range, or there is an output overload condition. The Fault output is the link between the output monitoring circuits and the primary PWM. The Fault output is capable of sinking 5 mA of current.

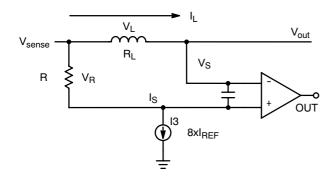

### PACKAGE DIMENSIONS

SOIC-16 D SUFFIX CASE 751B-05 ISSUE J

NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

- 2. CONTROLLING DIMENSION: MILLIMETER. 3. DIMENSIONS A AND B DO NOT INCLUDE

- MOLD PROTRUSION. 4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIN | IETERS   | INC     | HES   |

|-----|--------|----------|---------|-------|

| DIM | MIN    | MAX      | MIN MAX |       |

| Α   | 9.80   | 10.00    | 0.386   | 0.393 |

| В   | 3.80   | 4.00     | 0.150   | 0.157 |

| С   | 1.35   | 1.75     | 0.054   | 0.068 |

| D   | 0.35   | 0.49     | 0.014   | 0.019 |

| F   | 0.40   | 1.25     | 0.016   | 0.049 |

| G   | 1.27   | 1.27 BSC |         | BSC   |

| J   | 0.19   | 0.25     | 0.008   | 0.009 |

| K   | 0.10   | 0.25     | 0.004   | 0.009 |

| М   | 0 °    | 7°       | 0 °     | 7°    |

| Ρ   | 5.80   | 6.20     | 0.229   | 0.244 |

| R   | 0.25   | 0.50     | 0.010   | 0.019 |

The product described herein (NCP4350), may be covered by U.S. patents including 6,373,734. There may be other patents pending.

ON Semiconductor and use registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use payes that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative