The revision list can be viewed directly by clicking the title page. The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

# SH7080 Group

User's Manual: Hardware

Renesas 32-Bit RISC Microcomputer

SuperH<sup>™</sup> RISC engine Family

| SH7083 | R5F7083 |

|--------|---------|

|        | R5M7083 |

|        | R5S7083 |

| SH7084 | R5F7084 |

|        | R5M7084 |

|        | R5S7084 |

| SH7085 | R5F7085 |

|        | R5M7085 |

|        | R5S7085 |

| SH7086 | R5F7086 |

#### Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- 2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com)

- Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

- (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

- Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

# General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

### 1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions may occur due to the false recognition of the pin state as an input signal. Unused pins should be handled as described under Handling of Unused Pins in the manual.

### 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

- The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

- In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

### 3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

The reserved addresses are provided for the possible future expansion of functions. Do not access these addresses; the correct operation of LSI is not guaranteed if they are accessed.

### 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

— When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

#### 5. Differences between Products

Before changing from one product to another, i.e. to one with a different type number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different type numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different type numbers, implement a system-evaluation test for each of the products.

# Configuration of This Manual

This manual comprises the following items:

- 1. General Precautions in the Handling of MPU/MCU Products

- 2. Configuration of This Manual

- 3. Preface

- 4. Contents

- 5 Overview

- 6. Description of Functional Modules

- CPU and System-Control Modules

- On-Chip Peripheral Modules

The configuration of the functional description of each module differs according to the module. However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. Each section includes notes in relation to the descriptions given, and usage notes are given, as required, as the final part of each section.

- 7. List of Registers

- 8. Electrical Characteristics

- 9. Appendix

- 10. Main Revisions for This Edition (only for revised versions)

The list of revisions is a summary of points that have been revised or added to earlier versions. This does not include all of the revised contents. For details, see the actual locations in this manual.

11. Index

## **Preface**

The SH7083, SH7084, SH7085, and SH7086 Group RISC (Reduced Instruction Set Computer) microcomputers include a Renesas original RISC CPU as its core, and the peripheral functions required to configure a system.

Target Users: This manual was written for users who will be using the SH7083, SH7084, SH7085,

and SH7086 Group in the design of application systems. Target users are expected

to understand the fundamentals of electrical circuits, logical circuits, and

microcomputers.

Objective: This manual was written to explain the hardware functions and electrical

characteristics of the SH7083, SH7084, SH7085, and SH7086 Group to the target

users.

Refer to the SH-1/SH-2/SH-DSP Software Manual for a detailed description of the

instruction set.

### Notes on reading this manual:

• In order to understand the overall functions of the chip

Read the manual according to the contents. This manual can be roughly categorized into parts

on the CPU, system control functions, peripheral functions and electrical characteristics.

• In order to understand the details of the CPU's functions

Read the SH-1/SH-2/SH-DSP Software Manual.

• In order to understand the details of a register when its name is known

Read the index that is the final part of the manual to find the page number of the entry on the register. The addresses, bits, and initial values of the registers are summarized in section 27, List of Registers.

Examples: Register name: The following notation is used for cases when the same or a

similar function, e.g. serial communication interface, is

implemented on more than one channel:

XXX\_N (XXX is the register name and N is the channel

number)

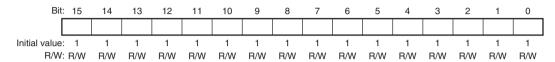

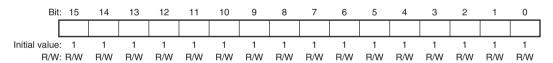

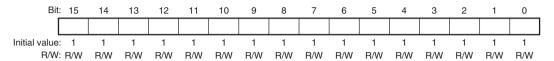

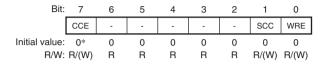

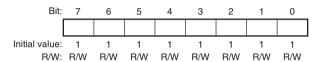

Bit order: The MSB is on the left and the LSB is on the right.

Number notation: Binary is B'xxxx, hexadecimal is H'xxxx, decimal is xxxx.

Signal notation: An overbar is added to a low-active signal: xxxx

Related Manuals: The latest versions of all related manuals are available from our web site.

Please ensure you have the latest versions of all documents you require.

http://www.renesas.com/

SH7083, SH7084, SH7085, and SH7086 Group Manuals:

| Document Title                   | Document No. |

|----------------------------------|--------------|

| SH7080 Group Hardware Manual     | This manual  |

| SH-1/SH-2/SH-DSP Software Manual | REJ09B0171   |

### User's Manuals for Development Tools:

| Document Title                                                                                                                | Document No. |

|-------------------------------------------------------------------------------------------------------------------------------|--------------|

| SuperH <sup>™</sup> RISC engine C/C++ Compiler, Assembler,<br>Optimizing Linkage Editor Compiler Package V.9.04 User's Manual | REJ10J2202   |

| High-performance Embedded Workshop User's Manual                                                                              | REJ10J2169   |

### Application Note:

| Document Title                                             | Document No. |

|------------------------------------------------------------|--------------|

| SuperH RISC engine C/C++ Compiler Package Application Note | REJ05B0463   |

All trademarks and registered trademarks are the property of their respective owners.

# Contents

| Sect | tion 1 C                 | Overview                                 | 1  |

|------|--------------------------|------------------------------------------|----|

| 1.1  | Feature                  | es of SH7083, SH7084, SH7085, and SH7086 | 1  |

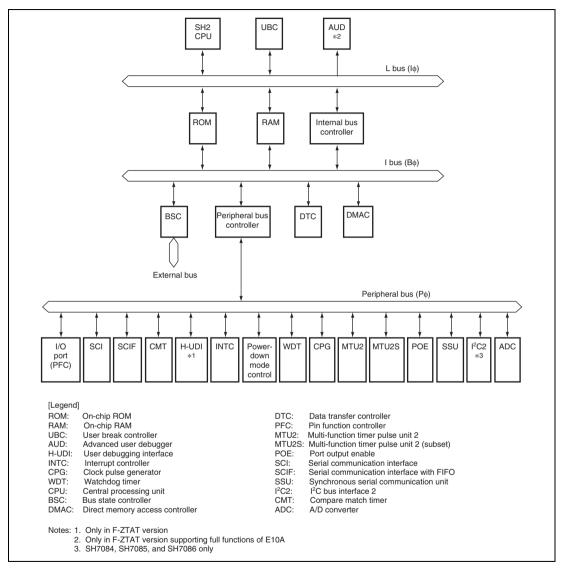

| 1.2  | Block I                  | Diagram                                  | 7  |

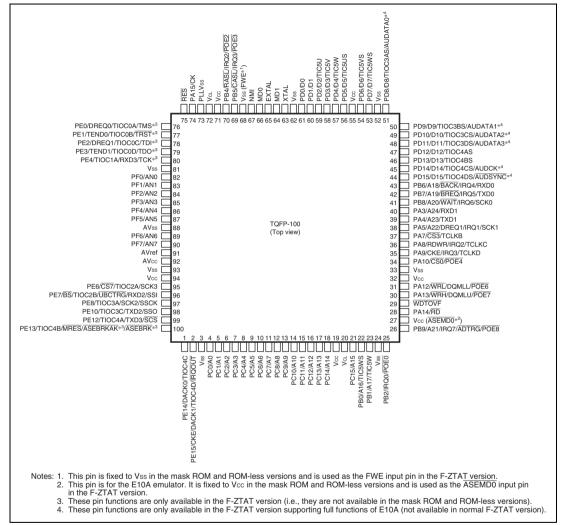

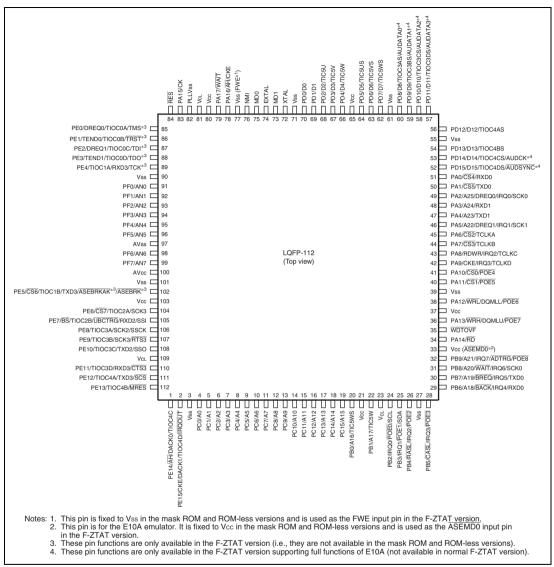

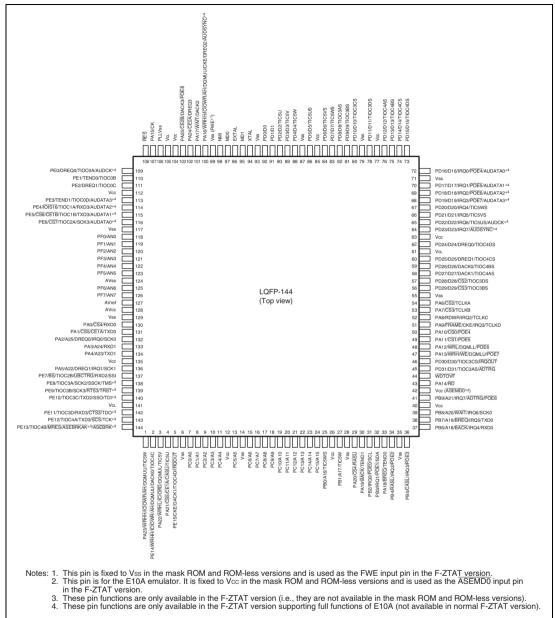

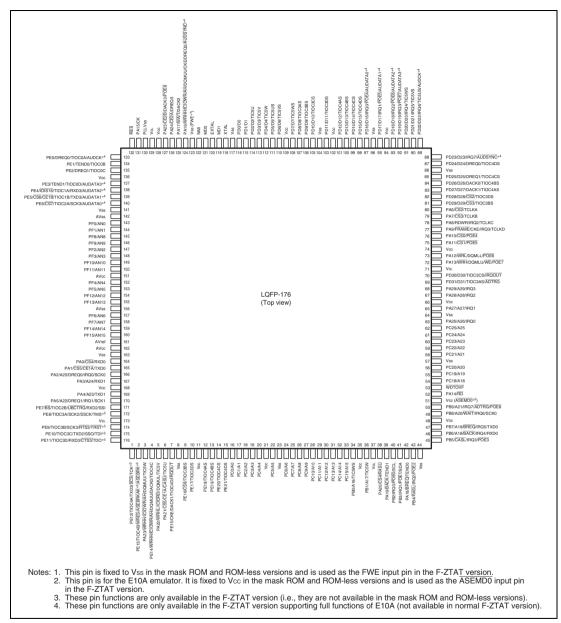

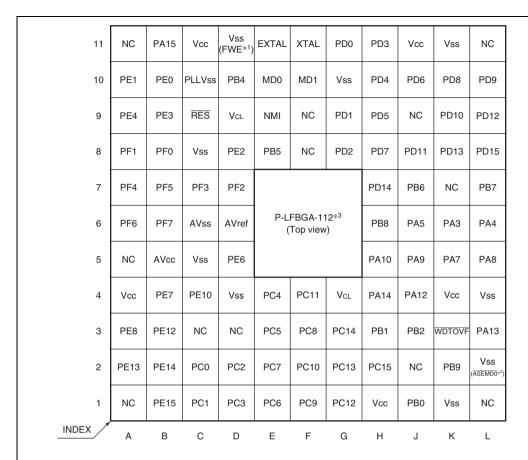

| 1.3  | Pin Ass                  | signments                                | 8  |

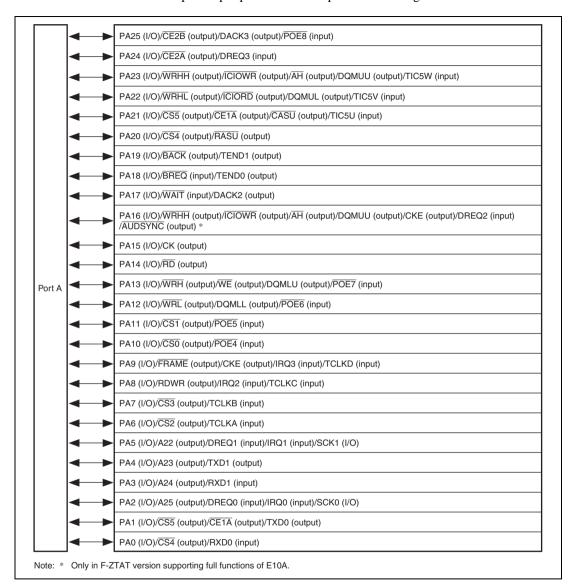

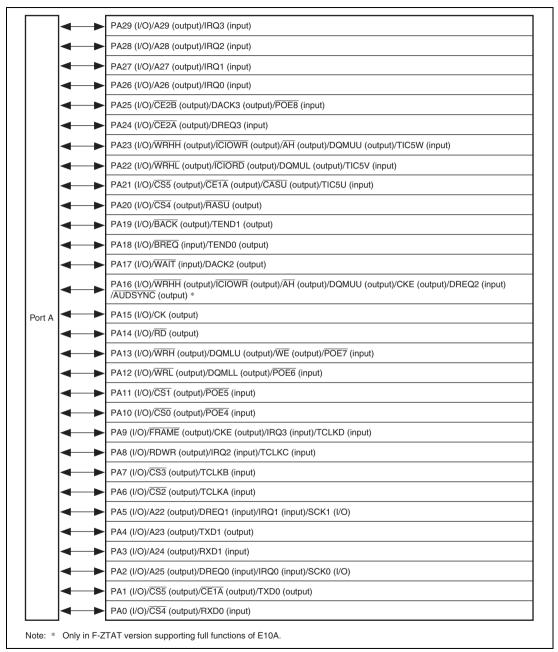

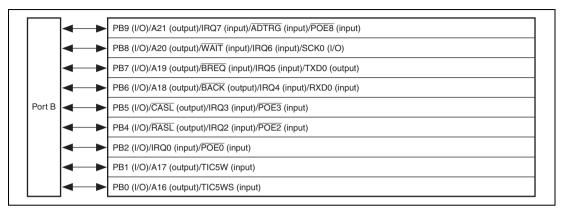

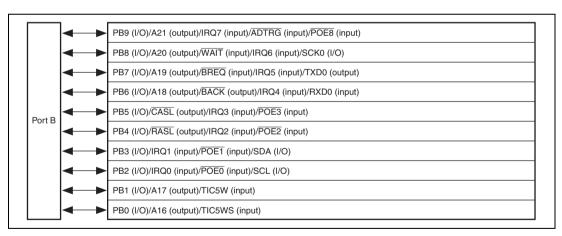

| 1.4  | Pin Fur                  | nctions                                  | 13 |

|      |                          |                                          |    |

| Sect | ion 2 C                  | CPU                                      | 23 |

| 2.1  | Feature                  | es                                       | 23 |

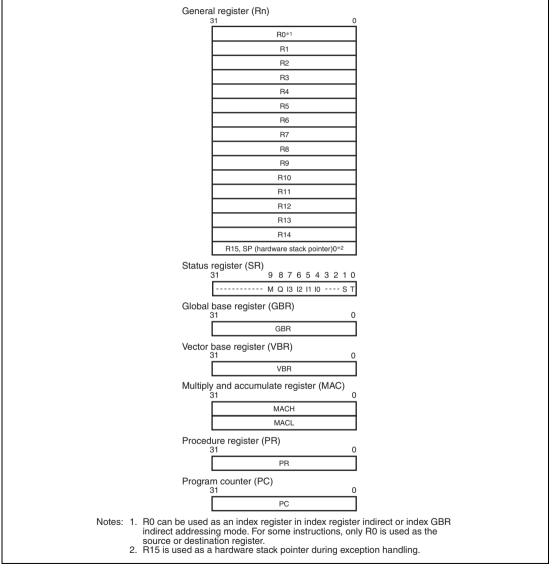

| 2.2  | Registe                  | er Configuration                         | 24 |

|      | 2.2.1                    | General Registers (Rn)                   | 25 |

|      | 2.2.2                    | Control Registers                        | 25 |

|      | 2.2.3                    | System Registers                         | 27 |

|      | 2.2.4                    | Initial Values of Registers              | 27 |

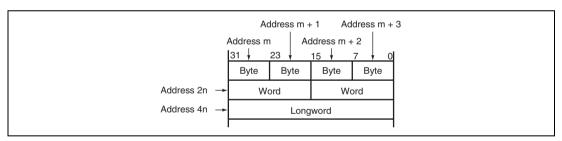

| 2.3  | Data Fo                  | ormats                                   | 28 |

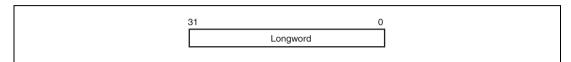

|      | 2.3.1                    | Register Data Format                     | 28 |

|      | 2.3.2                    | Memory Data Formats                      | 28 |

|      | 2.3.3                    | Immediate Data Formats                   | 29 |

| 2.4  | Features of Instructions |                                          | 29 |

|      | 2.4.1                    | RISC Type                                | 29 |

|      | 2.4.2                    | Addressing Modes                         | 32 |

|      | 2.4.3                    | Instruction Formats                      | 35 |

| 2.5  | Instruct                 | tion Set                                 | 39 |

|      | 2.5.1                    | Instruction Set by Type                  | 39 |

|      | 2.5.2                    | Data Transfer Instructions               |    |

|      | 2.5.3                    | Arithmetic Operation Instructions        | 45 |

|      | 2.5.4                    | Logic Operation Instructions             | 47 |

|      | 2.5.5                    | Shift Instructions                       | 48 |

|      | 2.5.6                    | Branch Instructions                      | 49 |

|      | 2.5.7                    | System Control Instructions              | 50 |

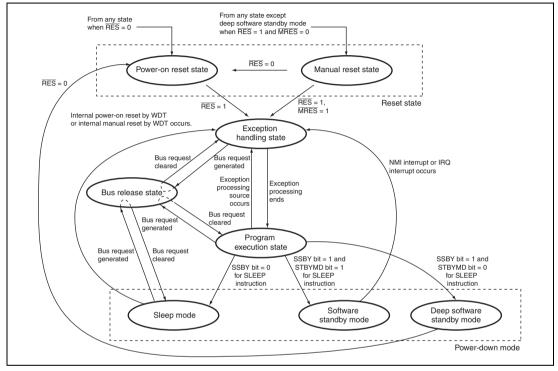

| 2.6  | Process                  | sing States                              | 52 |

|      |                          |                                          |    |

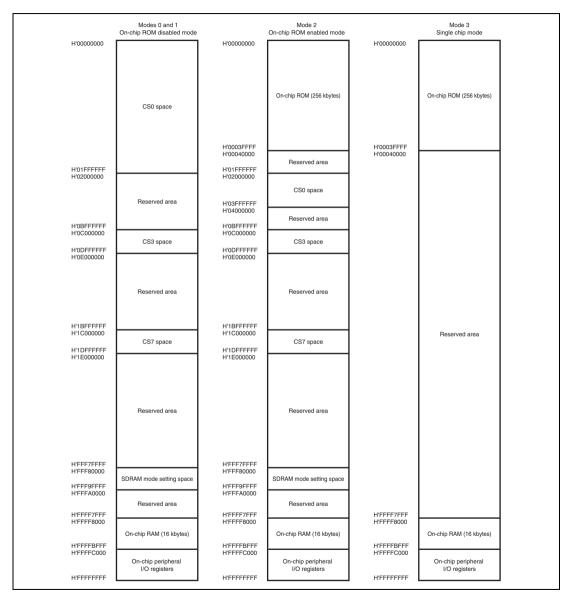

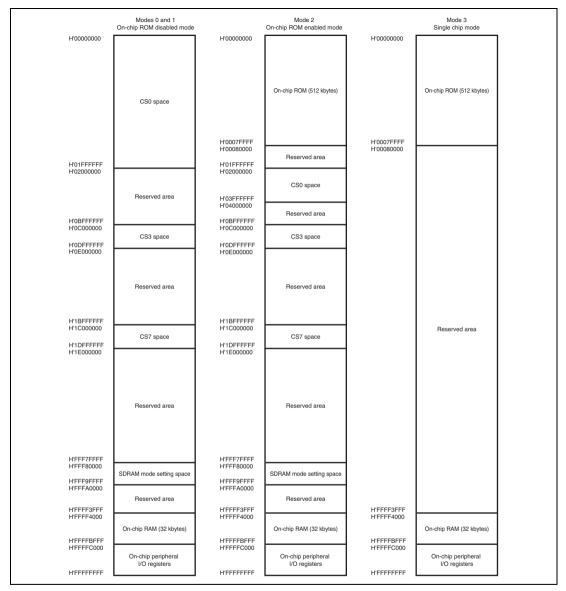

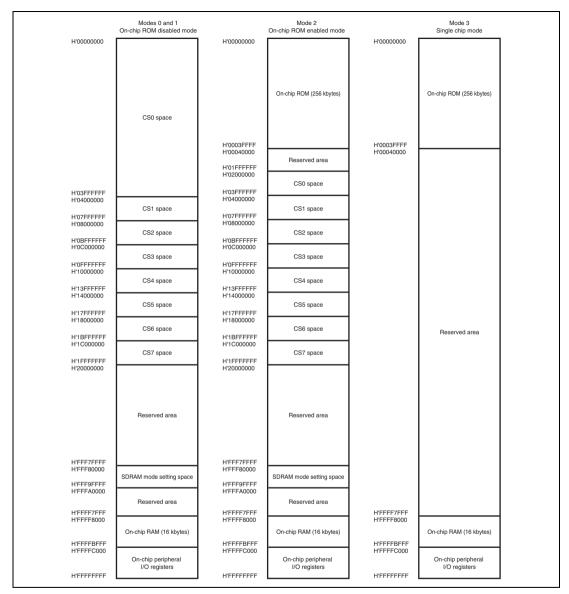

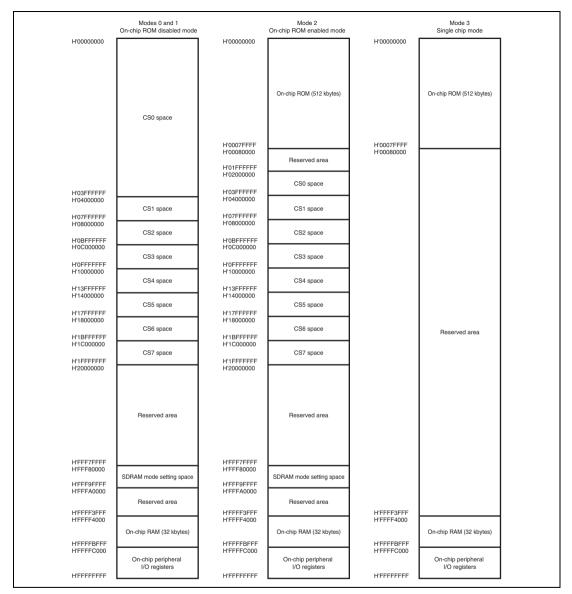

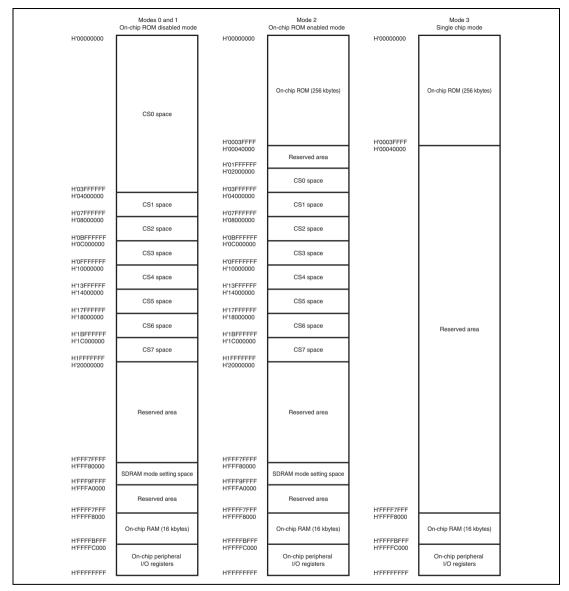

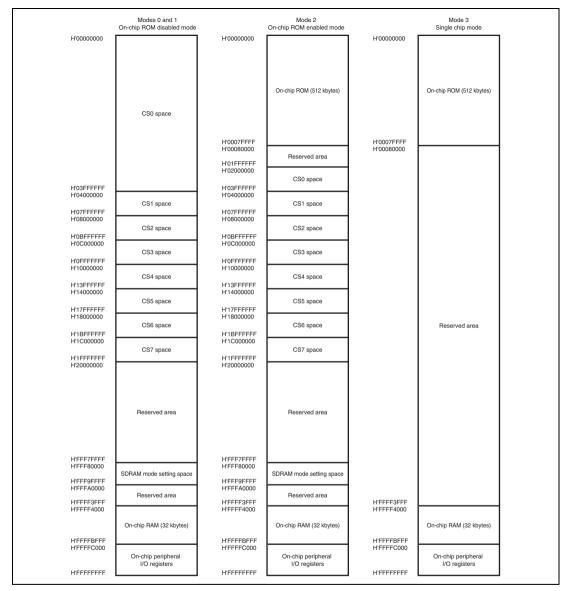

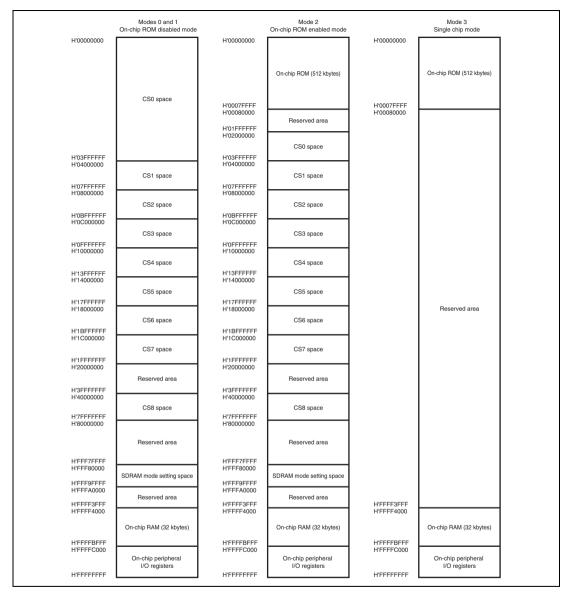

| Sect | ion 3 N                  | MCU Operating Modes                      | 55 |

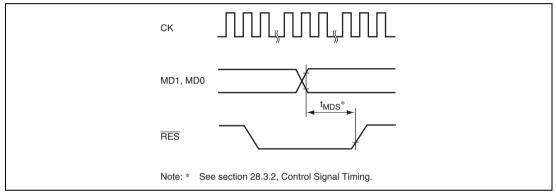

| 3.1  | Selection                | on of Operating Modes                    | 55 |

| 3.2  | Input/C                  | Output Pins                              | 56 |

| 3.3  | Operati                  | ing Modes                                | 57 |

|      | 3.3.1                    | Mode 0 (MCU Extension Mode 0)            | 57 |

|      | 3.3.2                    | Mode 1 (MCU Extension Mode 1)            | 57 |

|      |                          |                                          |    |

|      | 3.3.3                     | Mode 2 (MCU Extension Mode 2)                       | 57 |  |

|------|---------------------------|-----------------------------------------------------|----|--|

|      | 3.3.4                     | Mode 3 (Single Chip Mode)                           | 57 |  |

| 3.4  | Addres                    | s Map                                               | 58 |  |

| 3.5  | Initial State in This LSI |                                                     |    |  |

| 3.6  | Note or                   | n Changing Operating Mode                           | 65 |  |

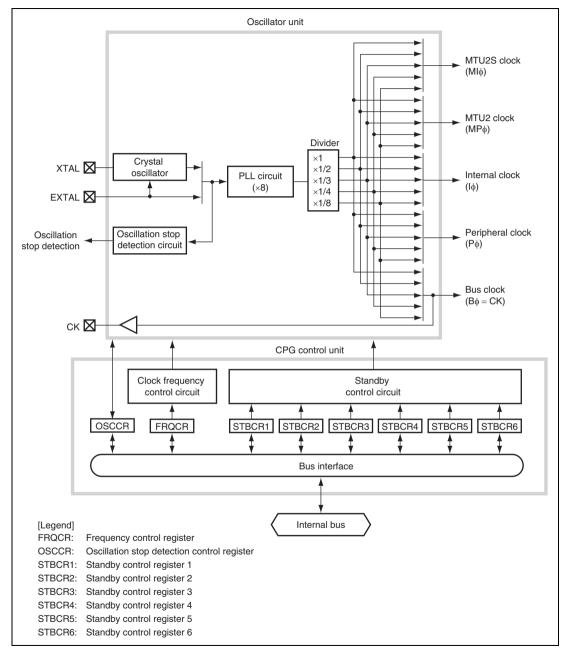

| Sect | ion 4 C                   | Clock Pulse Generator (CPG)                         | 67 |  |

| 4.1  | Feature                   | S                                                   | 67 |  |

| 4.2  | Input/C                   | Output Pins                                         | 71 |  |

| 4.3  | Clock (                   | Operating Mode                                      | 72 |  |

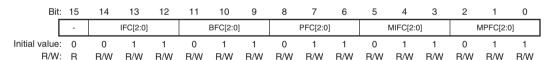

| 4.4  | Registe                   | r Descriptions                                      | 77 |  |

|      | 4.4.1                     | Frequency Control Register (FRQCR)                  | 77 |  |

|      | 4.4.2                     | Oscillation Stop Detection Control Register (OSCCR) | 80 |  |

| 4.5  | Changi                    | ng Frequency                                        | 81 |  |

| 4.6  | Oscillat                  | tor                                                 | 82 |  |

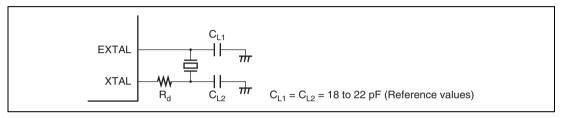

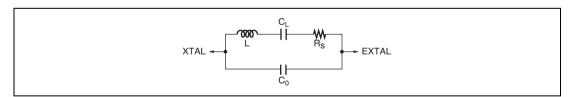

|      | 4.6.1                     | Connecting Crystal Resonator                        | 82 |  |

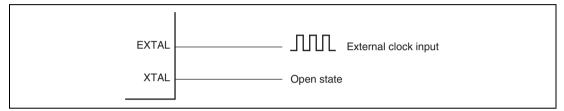

|      | 4.6.2                     | External Clock Input Method                         | 83 |  |

| 4.7  | Functio                   | on for Detecting Oscillator Stop                    | 84 |  |

| 4.8  | Usage l                   | Notes                                               | 85 |  |

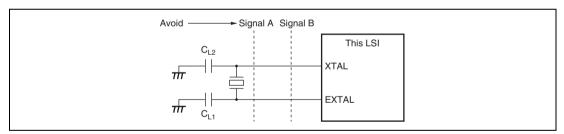

|      | 4.8.1                     | Note on Crystal Resonator                           | 85 |  |

|      | 4.8.2                     | Notes on Board Design                               | 85 |  |

| Sect | ion 5 E                   | Exception Handling                                  | 87 |  |

| 5.1  | Overvie                   | ew                                                  | 87 |  |

|      | 5.1.1                     | Types of Exception Handling and Priority            | 87 |  |

|      | 5.1.2                     | Exception Handling Operations                       | 88 |  |

|      | 5.1.3                     | Exception Handling Vector Table                     | 89 |  |

| 5.2  | Resets.                   |                                                     | 91 |  |

|      | 5.2.1                     | Types of Resets                                     | 91 |  |

|      | 5.2.2                     | Power-On Reset                                      | 91 |  |

|      | 5.2.3                     | Manual Reset                                        | 92 |  |

| 5.3  | Addres                    | s Errors                                            | 93 |  |

|      | 5.3.1                     | Address Error Sources                               | 93 |  |

|      | 5.3.2                     | Address Error Exception Source                      | 94 |  |

| 5.4  | Interrup                  | ots                                                 | 95 |  |

|      | 5.4.1                     | Interrupt Sources                                   | 95 |  |

|      | 5.4.2                     | Interrupt Priority                                  | 96 |  |

|      | 5.4.3                     | Interrupt Exception Handling                        | 96 |  |

| 5.5  | Excepti                   | ions Triggered by Instructions                      |    |  |

|      | 5.5.1                     | Types of Exceptions Triggered by Instructions       | 97 |  |

| 5.5.2                                        | Trap Instructions                                                                                                                                                                                                      | 97                                                                 |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 5.5.3                                        | Illegal Slot Instructions                                                                                                                                                                                              | 98                                                                 |

| 5.5.4                                        | General Illegal Instructions                                                                                                                                                                                           | 98                                                                 |

| Cases w                                      | when Exceptions Are Accepted                                                                                                                                                                                           | 99                                                                 |

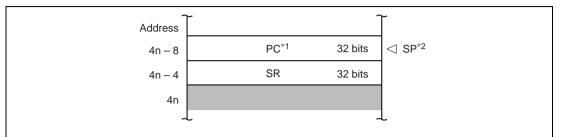

| Stack S                                      | tates after Exception Handling Ends                                                                                                                                                                                    | 100                                                                |

| Usage N                                      | Notes                                                                                                                                                                                                                  | 102                                                                |

| 5.8.1                                        | Value of Stack Pointer (SP)                                                                                                                                                                                            | 102                                                                |

| 5.8.2                                        | Value of Vector Base Register (VBR)                                                                                                                                                                                    | 102                                                                |

| 5.8.3                                        | Address Errors Caused by Stacking for Address Error Exception Handling.                                                                                                                                                | 102                                                                |

| 5.8.4                                        | Notes on Slot Illegal Instruction Exception Handling                                                                                                                                                                   | 103                                                                |

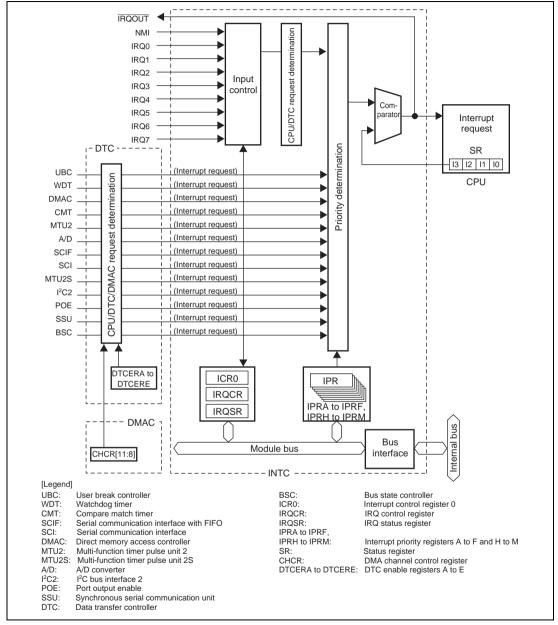

| ion 6 Iı                                     | nterrupt Controller (INTC)                                                                                                                                                                                             | 105                                                                |

|                                              |                                                                                                                                                                                                                        |                                                                    |

|                                              |                                                                                                                                                                                                                        |                                                                    |

| Registe                                      | r Descriptions                                                                                                                                                                                                         | 108                                                                |

| 6.3.1                                        | •                                                                                                                                                                                                                      |                                                                    |

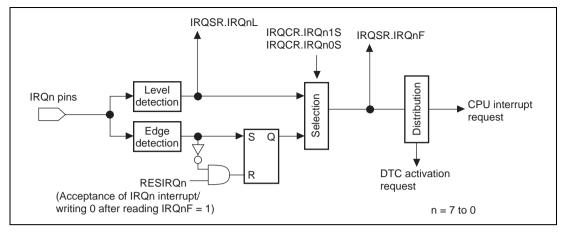

| 6.3.2                                        | IRQ Control Register (IRQCR)                                                                                                                                                                                           | 110                                                                |

| 6.3.3                                        | IRQ Status register (IRQSR)                                                                                                                                                                                            | 113                                                                |

| 6.3.4                                        | Interrupt Priority Registers A to F and H to M                                                                                                                                                                         |                                                                    |

|                                              | (IPRA to IPRF and IPRH to IPRM)                                                                                                                                                                                        | 118                                                                |

| Interrup                                     | ot Sources                                                                                                                                                                                                             | 121                                                                |

| 6.4.1                                        | External Interrupts                                                                                                                                                                                                    | 121                                                                |

| 6.4.2                                        | On-Chip Peripheral Module Interrupts                                                                                                                                                                                   | 122                                                                |

| 6.4.3                                        | User Break Interrupt                                                                                                                                                                                                   | 122                                                                |

| Interrup                                     | ot Exception Handling Vector Table                                                                                                                                                                                     | 123                                                                |

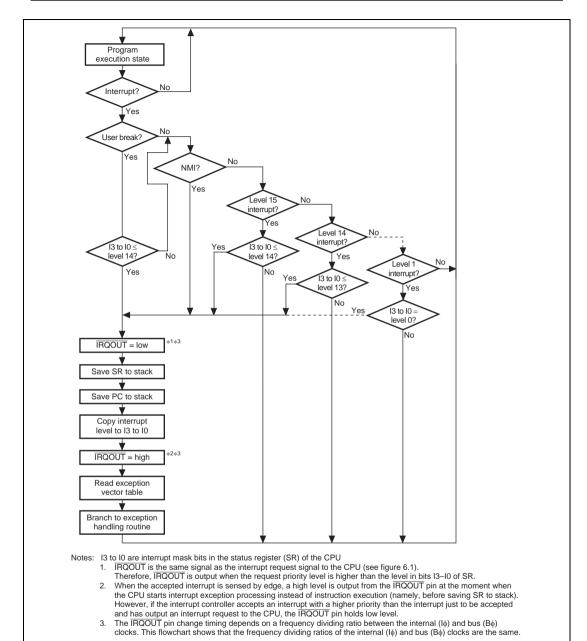

| Interrup                                     | ot Operation                                                                                                                                                                                                           | 127                                                                |

| 6.6.1                                        | Interrupt Sequence                                                                                                                                                                                                     | 127                                                                |

| 6.6.2                                        | Stack after Interrupt Exception Handling                                                                                                                                                                               | 130                                                                |

| Interrup                                     | ot Response Time                                                                                                                                                                                                       | 130                                                                |

| Data Transfer with Interrupt Request Signals |                                                                                                                                                                                                                        |                                                                    |

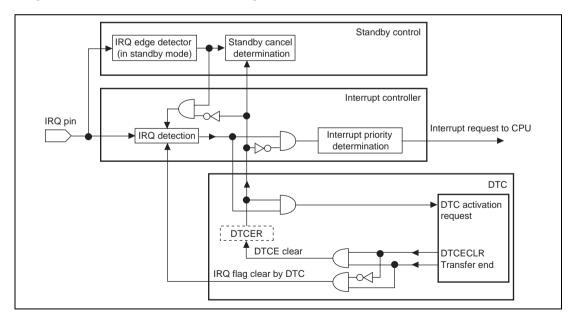

| 6.8.1                                        | Handling Interrupt Request Signals as Sources for DTC Activation and                                                                                                                                                   |                                                                    |

|                                              | CPU Interrupts, but Not DMAC Activation                                                                                                                                                                                | 133                                                                |

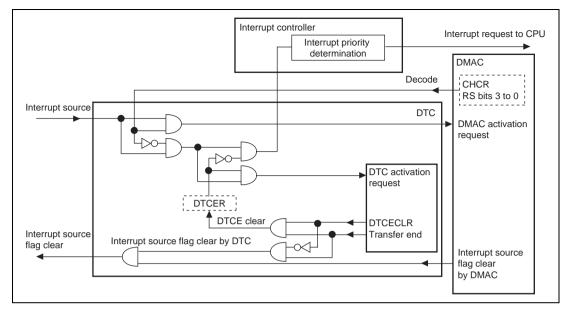

| 6.8.2                                        | Handling Interrupt Request Signals as Sources for DMAC Activation,                                                                                                                                                     |                                                                    |

|                                              | but Not CPU Interrupts and DTC Activation                                                                                                                                                                              | 134                                                                |

| 6.8.3                                        | Handling Interrupt Request Signals as Sources for DTC Activation,                                                                                                                                                      |                                                                    |

|                                              |                                                                                                                                                                                                                        | 134                                                                |

| 6.8.4                                        | Handling Interrupt Request Signals as Sources for CPU Interrupts,                                                                                                                                                      |                                                                    |

|                                              | but Not DTC and DMAC Activation                                                                                                                                                                                        | 134                                                                |

| Usage N                                      | Note                                                                                                                                                                                                                   | 134                                                                |

|                                              | 5.5.3 5.5.4 Cases w Stack S Usage N 5.8.1 5.8.2 5.8.3 5.8.4 ion 6 In Feature Input/O Registe 6.3.1 6.3.2 6.3.3 6.3.4 Interrup 6.4.1 6.4.2 6.4.3 Interrup Interrup 6.6.1 6.6.2 Interrup Data Tr 6.8.1 6.8.2 6.8.3 6.8.4 | 5.5.3 Illegal Slot Instructions 5.5.4 General Illegal Instructions |

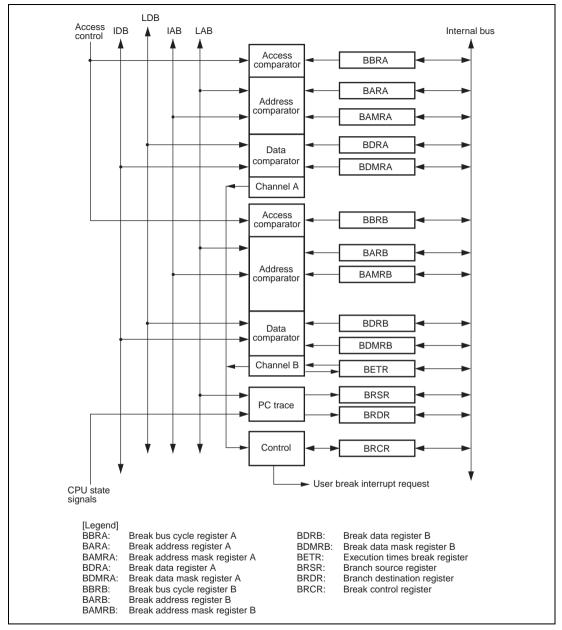

| Sect | ion 7 U   | ser Break Controller (UBC)                                     | 135 |  |

|------|-----------|----------------------------------------------------------------|-----|--|

| 7.1  | Features  | 3                                                              | 135 |  |

| 7.2  | Input/O   | utput Pins                                                     | 138 |  |

| 7.3  | Register  | Descriptions                                                   | 139 |  |

|      | 7.3.1     | Break Address Register A (BARA)                                | 140 |  |

|      | 7.3.2     | Break Address Mask Register A (BAMRA)                          | 140 |  |

|      | 7.3.3     | Break Bus Cycle Register A (BBRA)                              | 141 |  |

|      | 7.3.4     | Break Data Register A (BDRA) (Only in F-ZTAT Version)          | 143 |  |

|      | 7.3.5     | Break Data Mask Register A (BDMRA) (Only in F-ZTAT Version)    | 144 |  |

|      | 7.3.6     | Break Address Register B (BARB)                                | 145 |  |

|      | 7.3.7     | Break Address Mask Register B (BAMRB)                          | 146 |  |

|      | 7.3.8     | Break Data Register B (BDRB) (Only in F-ZTAT Version)          | 147 |  |

|      | 7.3.9     | Break Data Mask Register B (BDMRB) (Only in F-ZTAT Version)    | 148 |  |

|      | 7.3.10    | Break Bus Cycle Register B (BBRB)                              | 149 |  |

|      | 7.3.11    | Break Control Register (BRCR)                                  | 151 |  |

|      | 7.3.12    | Execution Times Break Register (BETR) (Only in F-ZTAT Version) | 156 |  |

|      | 7.3.13    | Branch Source Register (BRSR) (Only in F-ZTAT Version)         | 157 |  |

|      | 7.3.14    | Branch Destination Register (BRDR) (Only in F-ZTAT Version)    | 158 |  |

| 7.4  | Operation |                                                                |     |  |

|      | 7.4.1     | Flow of the User Break Operation                               | 159 |  |

|      | 7.4.2     | User Break on Instruction Fetch Cycle                          | 160 |  |

|      | 7.4.3     | User Break on Data Access Cycle                                | 161 |  |

|      | 7.4.4     | Sequential Break                                               | 162 |  |

|      | 7.4.5     | Value of Saved Program Counter                                 | 162 |  |

|      | 7.4.6     | PC Trace                                                       | 163 |  |

|      | 7.4.7     | Usage Examples                                                 | 164 |  |

| 7.5  | Usage N   | Notes                                                          | 169 |  |

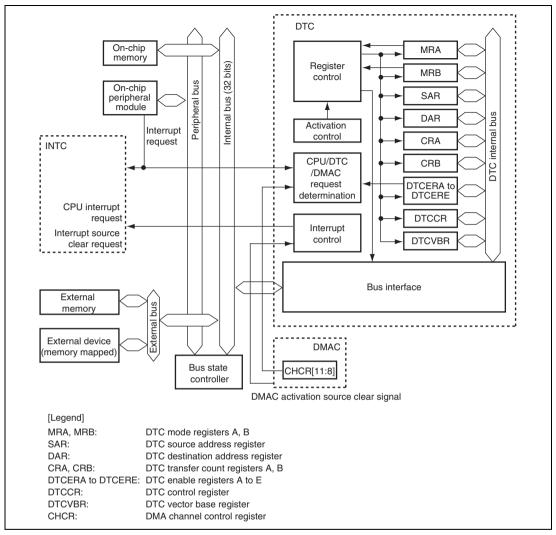

| Sect | ion 8 D   | eata Transfer Controller (DTC)                                 | 171 |  |

| 8.1  |           | S                                                              |     |  |

| 8.2  | Register  | Descriptions                                                   | 173 |  |

|      | 8.2.1     | DTC Mode Register A (MRA)                                      | 174 |  |

|      | 8.2.2     | DTC Mode Register B (MRB)                                      |     |  |

|      | 8.2.3     | DTC Source Address Register (SAR)                              | 177 |  |

|      | 8.2.4     | DTC Destination Address Register (DAR)                         | 177 |  |

|      | 8.2.5     | DTC Transfer Count Register A (CRA)                            | 178 |  |

|      | 8.2.6     | DTC Transfer Count Register B (CRB)                            | 179 |  |

|      | 8.2.7     | DTC Enable Registers A to E (DTCERA to DTCERE)                 |     |  |

|      | 8.2.8     | DTC Control Register (DTCCR)                                   | 181 |  |

|      | 8.2.9     | DTC Vector Base Register (DTCVBR)                              | 183 |  |

|      |           |                                                                |     |  |

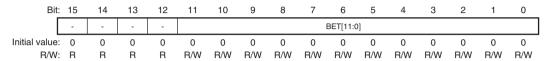

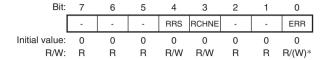

| 8.3       Activation Sources       184         8.4       Location of Transfer Information and DTC Vector Table       184         8.5       Operation       189         8.5.1       Transfer Information Read Skip Function       194         8.5.2       Transfer Information Writeback Skip Function       195         8.5.3       Normal Transfer Mode       195         8.5.4       Repeat Transfer Mode       198         8.5.5       Block Transfer Mode       198         8.5.6       Chain Transfer       199         8.5.7       Operation Timing       201         8.5.8       Number of DTC Execution Cycles       204         8.5.9       DTC Bus Release Timing       206         8.5.10       DTC Activation Priority Order       209         8.6       DTC Activation Priority Order       209         8.6       DTC Activation Priority Order       210         8.7       Normal Transfer Mode       211         8.7       Normal Transfer Mode <th></th> <th>8.2.10</th> <th>Bus Function Extending Register (BSCEHR)</th> <th> 183</th>                    |      | 8.2.10    | Bus Function Extending Register (BSCEHR)       | 183 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------|------------------------------------------------|-----|

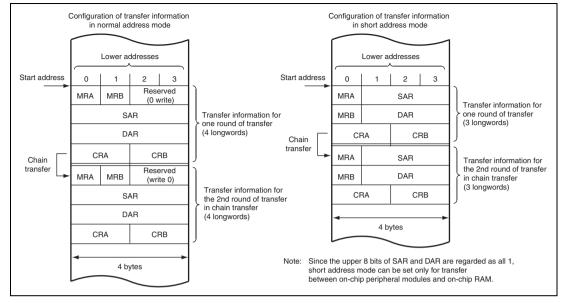

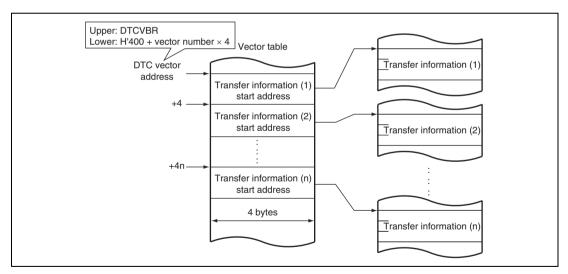

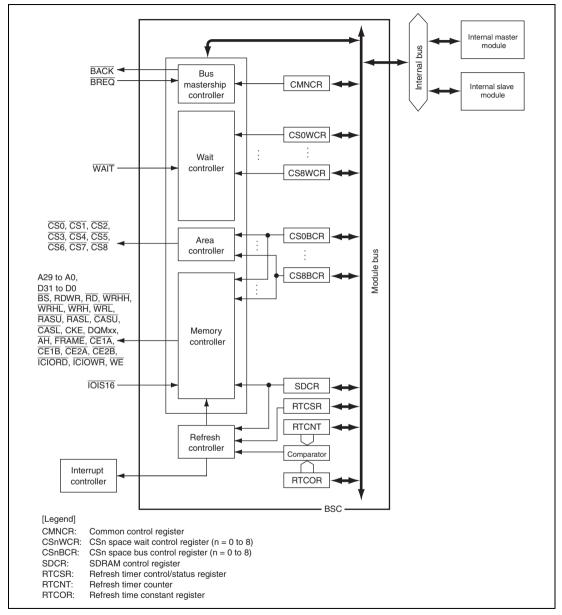

| 8.5       Operation       189         8.5.1       Transfer Information Read Skip Function       194         8.5.2       Transfer Information Writeback Skip Function       195         8.5.3       Normal Transfer Mode       196         8.5.4       Repeat Transfer Mode       198         8.5.5       Block Transfer Mode       198         8.5.6       Chain Transfer       199         8.5.7       Operation Timing       201         8.5.8       Number of DTC Execution Cycles       204         8.5.9       DTC Bus Release Timing       206         8.5.10       DTC Activation Priority Order       209         8.6       DTC Activation by Interrupt       210         8.7       Examples of Use of the DTC       211         8.7       Normal Transfer Mode       211         8.7       Normal Transfer when Counter = 0       211         8.8       Interrupt Sources       213         8.9       Usage Notes       213         8.9.1       Module Standby Mode Setting       213         8.9.2       On-Chip RAM       213         8.9.3       DTCE Bit Setting       213         8.9.4       Chain Transfer       214                                                                                                                                            | 8.3  | Activati  | on Sources                                     | 184 |

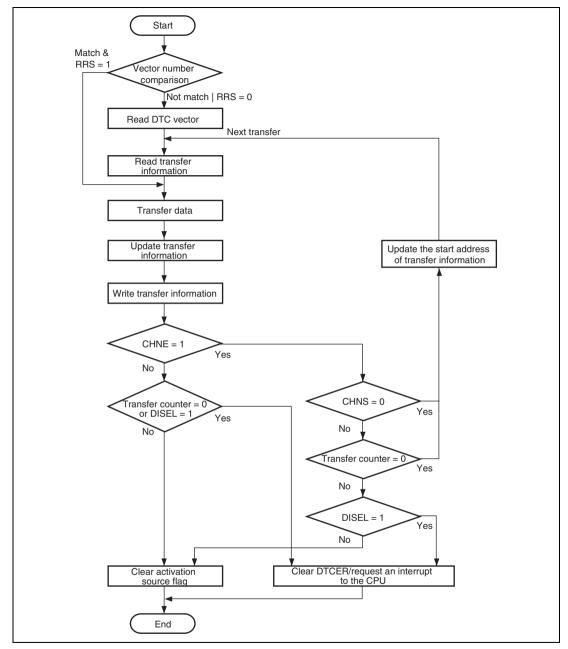

| 8.5.1       Transfer Information Read Skip Function       194         8.5.2       Transfer Information Writeback Skip Function       195         8.5.3       Normal Transfer Mode       195         8.5.4       Repeat Transfer Mode       196         8.5.5       Block Transfer Mode       198         8.5.6       Chain Transfer       199         8.5.7       Operation Timing       201         8.5.8       Number of DTC Execution Cycles       204         8.5.9       DTC Bus Release Timing       206         8.5.10       DTC Activation Priority Order       209         8.6       DTC Activation by Interrupt       210         8.7       Examples of Use of the DTC       211         8.7.1       Normal Transfer Mode       211         8.7.2       Chain Transfer Mode       211         8.8.1       Interrupt Sources       213         8.9       Usage Notes       213         8.9.1       Module Standby Mode Setting       213         8.9.2       On-Chip RAM       213         8.9.3       DTCE Bit Setting       213         8.9.4       Chain Transfer       213         8.9.5       Transfer Information Start Address, Source Address, and De                                                                                                          | 8.4  | Location  | n of Transfer Information and DTC Vector Table | 184 |

| 8.5.2       Transfer Information Writeback Skip Function       195         8.5.3       Normal Transfer Mode       196         8.5.4       Repeat Transfer Mode       196         8.5.5       Block Transfer Mode       198         8.5.6       Chain Transfer       199         8.5.7       Operation Timing       201         8.5.8       Number of DTC Execution Cycles       204         8.5.9       DTC Bus Release Timing       206         8.5.10       DTC Activation by Interrupt       209         8.6       DTC Activation by Interrupt       210         8.7       Examples of Use of the DTC       211         8.7       Normal Transfer Mode       211         8.7       Normal Transfer When Counter = 0       211         8.8       Interrupt Sources       213         8.9       Usage Notes       213         8.9.1       Module Standby Mode Setting       213         8.9.2       On-Chip RAM       213         8.9.3       DTCE Bit Setting       213         8.9.4       Chain Transfer       213         8.9.5       Transfer Information Start Address, Source Address, and Destination Address       214         8.9.6       Access to DMAC or                                                                                                          | 8.5  | Operation | on                                             | 189 |

| 8.5.3       Normal Transfer Mode       195         8.5.4       Repeat Transfer Mode       196         8.5.5       Block Transfer Mode       198         8.5.6       Chain Transfer       199         8.5.7       Operation Timing       201         8.5.8       Number of DTC Execution Cycles       204         8.5.9       DTC Bus Release Timing       206         8.5.10       DTC Activation by Interrupt       210         8.7       Examples of Use of the DTC       211         8.7       Examples of Use of the DTC       211         8.7       Normal Transfer Mode       211         8.7       Chain Transfer when Counter = 0       211         8.8       Interrupt Sources       213         8.9       Usage Notes       213         8.9       Usage Notes       213         8.9.1       Module Standby Mode Setting       213         8.9.2       On-Chip RAM       213         8.9.3       DTCE Bit Setting       213         8.9.4       Chain Transfer       213         8.9.5       Transfer Information Start Address, Source Address, and Destination       214         8.9.6       Access to DMAC or DTC Registers through DTC       214                                                                                                                   |      | 8.5.1     | Transfer Information Read Skip Function        | 194 |

| 8.5.4       Repeat Transfer Mode       196         8.5.5       Block Transfer Mode       198         8.5.6       Chain Transfer       199         8.5.7       Operation Timing       201         8.5.8       Number of DTC Execution Cycles       204         8.5.9       DTC Bus Release Timing       206         8.5.10       DTC Activation Priority Order       209         8.6       DTC Activation by Interrupt       210         8.7       Examples of Use of the DTC       211         8.7.1       Normal Transfer Mode       211         8.7.2       Chain Transfer Mode       211         8.8.1       Interrupt Sources       213         8.9       Usage Notes       213         8.9.1       Module Standby Mode Setting       213         8.9.2       On-Chip RAM       213         8.9.3       DTCE Bit Setting       213         8.9.5       Transfer Information Start Address, Source Address, and Destination         Address       214         8.9.6       Access to DMAC or DTC Registers through DTC       214         8.9.7       Notes on IRQ Interrupt as DTC Activation Source       214         8.9.9       Clearing Interrupt Source Flag       214 </td <td></td> <td>8.5.2</td> <td>Transfer Information Writeback Skip Function</td> <td> 195</td> |      | 8.5.2     | Transfer Information Writeback Skip Function   | 195 |

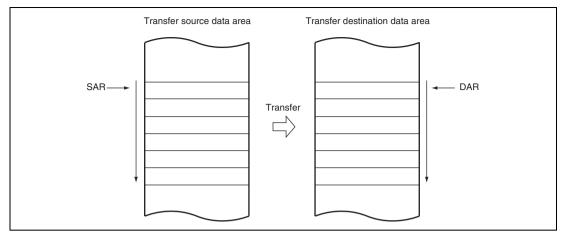

| 8.5.5       Block Transfer Mode       198         8.5.6       Chain Transfer       199         8.5.7       Operation Timing       201         8.5.8       Number of DTC Execution Cycles       204         8.5.9       DTC Bus Release Timing       206         8.5.10       DTC Activation Priority Order       209         8.6       DTC Activation by Interrupt       210         8.7       Examples of Use of the DTC       211         8.7       Examples of Use of the DTC       211         8.7       Chain Transfer Mode       211         8.7       Examples of Use of the DTC       211         8.7       Interrupt Sources       213         8.9       Usage Notes       213         8.9       Usage Notes       213         8.9.1       Module Standby Mode Setting       213         8.9.2       On-Chip RAM       213         8.9.3       DTCE Bit Setting       213         8.9.4       Chain Transfer       213         8.9.5       T                                                                                                                                                      |      | 8.5.3     | Normal Transfer Mode                           | 195 |

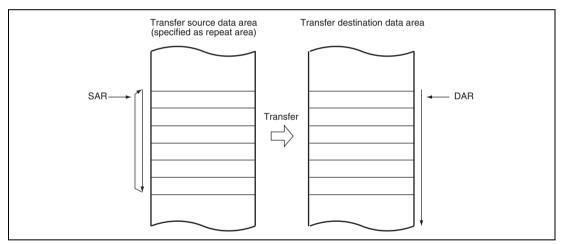

| 8.5.6       Chain Transfer       199         8.5.7       Operation Timing       201         8.5.8       Number of DTC Execution Cycles       204         8.5.9       DTC Bus Release Timing       206         8.5.10       DTC Activation Priority Order       209         8.6       DTC Activation by Interrupt       210         8.7       Examples of Use of the DTC       211         8.7       Interrupt Sources       213         8.8       Interrupt Sources       213         8.9       Usage Notes       213         8.9.1       Module Standby Mode Setting       213         8.9.2       On-Chip RAM       213         8.9.3       DTCE Bit Setting       213         8.9.4       Chain Transfer       213         8.9.5       Transfer Information Start Address, Source Address, and Destination Address       214         8.9.6       Access to DMAC or DTC Registers through DTC       214         8.9.7       Notes on IRQ Interrupt as DTC Activation Source       214         8.9.8       Notes on SCI and SCIF as DTC Activation Sources       214         8.9.9       Clearing Interrupt Source Flag       214         8.9.10       Conflict between NMI Interrupt and DTC Activation                                                                       |      | 8.5.4     | Repeat Transfer Mode                           | 196 |

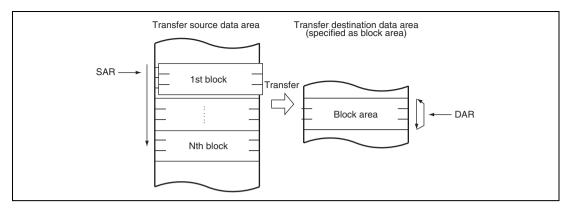

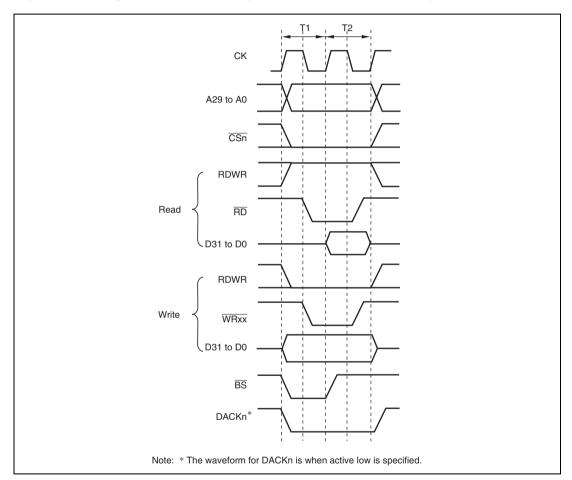

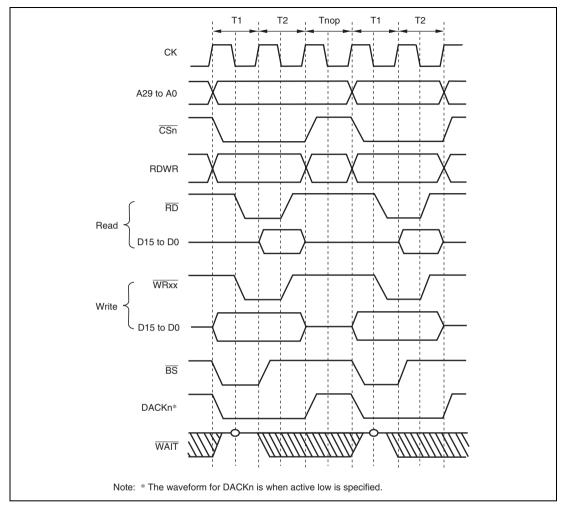

| 8.5.7       Operation Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      | 8.5.5     | Block Transfer Mode                            | 198 |

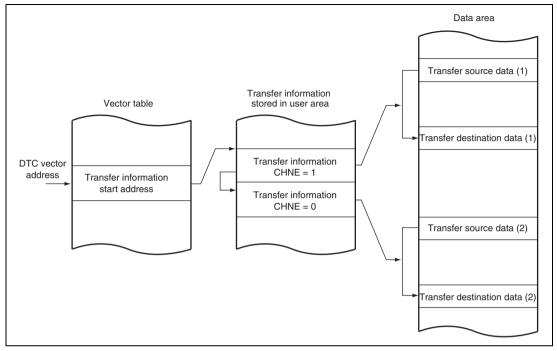

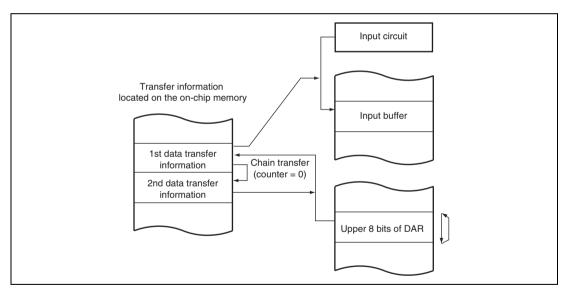

| 8.5.8       Number of DTC Execution Cycles       204         8.5.9       DTC Bus Release Timing       206         8.5.10       DTC Activation Priority Order       209         8.6       DTC Activation by Interrupt       210         8.7       Examples of Use of the DTC       211         8.7.1       Normal Transfer Mode       211         8.7.2       Chain Transfer When Counter = 0       211         8.8       Interrupt Sources       213         8.9       Usage Notes       213         8.9.1       Module Standby Mode Setting       213         8.9.2       On-Chip RAM       213         8.9.3       DTCE Bit Setting       213         8.9.4       Chain Transfer       213         8.9.5       Transfer Information Start Address, Source Address, and Destination         Address       214         8.9.6       Access to DMAC or DTC Registers through DTC       214         8.9.7       Notes on IRQ Interrupt as DTC Activation Source       214         8.9.8       Notes on SCI and SCIF as DTC Activation Sources       214         8.9.9       Clearing Interrupt Source Flag       214         8.9.10       Conflict between NMI Interrupt and DTC Activation       215                                                                              |      | 8.5.6     | Chain Transfer                                 | 199 |

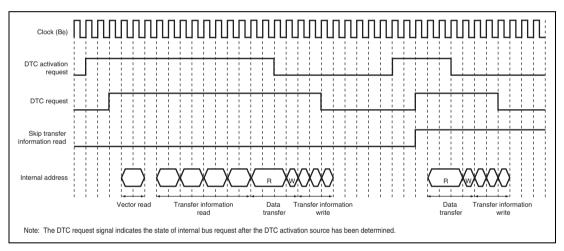

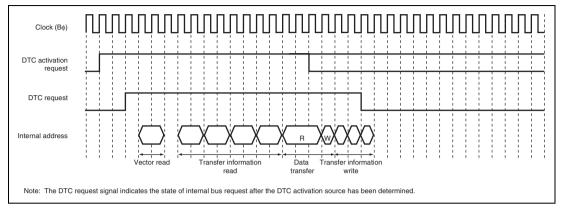

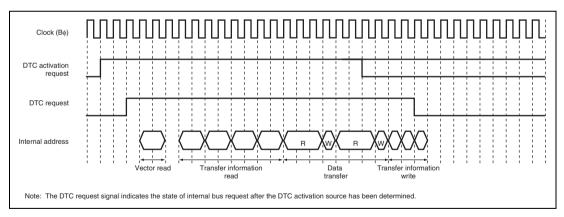

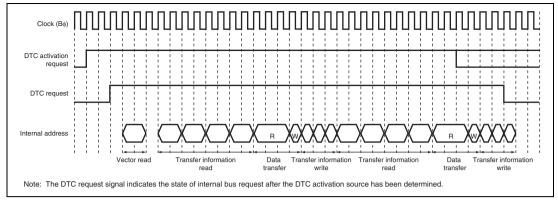

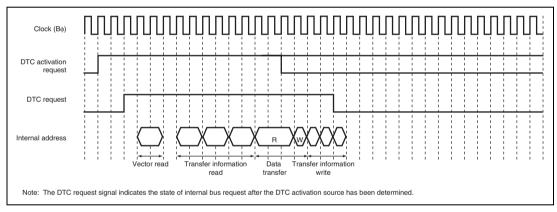

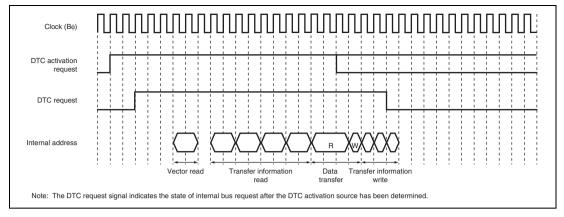

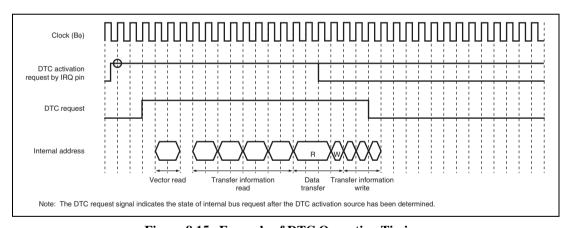

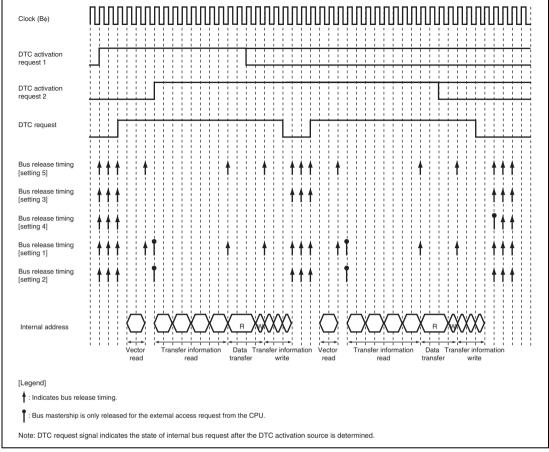

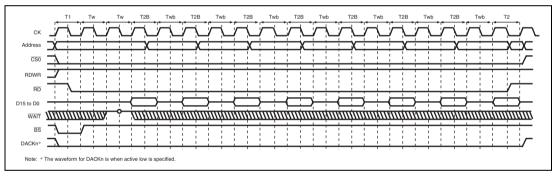

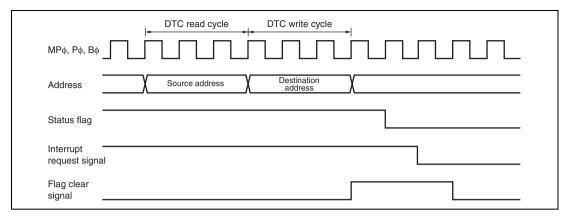

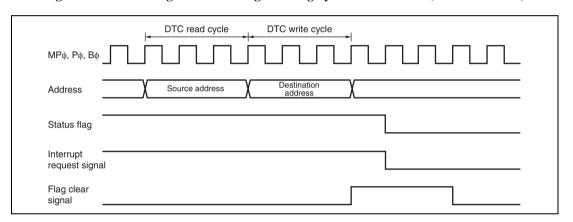

| 8.5.8       Number of DTC Execution Cycles       204         8.5.9       DTC Bus Release Timing       206         8.5.10       DTC Activation Priority Order       209         8.6       DTC Activation by Interrupt       210         8.7       Examples of Use of the DTC       211         8.7.1       Normal Transfer Mode       211         8.7.2       Chain Transfer When Counter = 0       211         8.8       Interrupt Sources       213         8.9       Usage Notes       213         8.9.1       Module Standby Mode Setting       213         8.9.2       On-Chip RAM       213         8.9.3       DTCE Bit Setting       213         8.9.4       Chain Transfer       213         8.9.5       Transfer Information Start Address, Source Address, and Destination         Address       214         8.9.6       Access to DMAC or DTC Registers through DTC       214         8.9.7       Notes on IRQ Interrupt as DTC Activation Source       214         8.9.8       Notes on SCI and SCIF as DTC Activation Sources       214         8.9.9       Clearing Interrupt Source Flag       214         8.9.10       Conflict between NMI Interrupt and DTC Activation       215                                                                              |      | 8.5.7     | Operation Timing                               | 201 |

| 8.5.10       DTC Activation Priority Order       209         8.6       DTC Activation by Interrupt       210         8.7       Examples of Use of the DTC       211         8.7.1       Normal Transfer Mode       211         8.7.2       Chain Transfer when Counter = 0       211         8.8       Interrupt Sources       213         8.9       Usage Notes       213         8.9.1       Module Standby Mode Setting       213         8.9.2       On-Chip RAM       213         8.9.3       DTCE Bit Setting       213         8.9.4       Chain Transfer       213         8.9.5       Transfer Information Start Address, Source Address, and Destination Address       214         8.9.6       Access to DMAC or DTC Registers through DTC       214         8.9.7       Notes on IRQ Interrupt as DTC Activation Source       214         8.9.8       Notes on SCI and SCIF as DTC Activation Sources       214         8.9.9       Clearing Interrupt Source Flag       214         8.9.10       Conflict between NMI Interrupt and DTC Activation       215         8.9.11       Operation when a DTC Activation Request Is Cancelled While in Progress       215         Section 9       Bus State Controller (BSC)       221                                     |      | 8.5.8     |                                                |     |

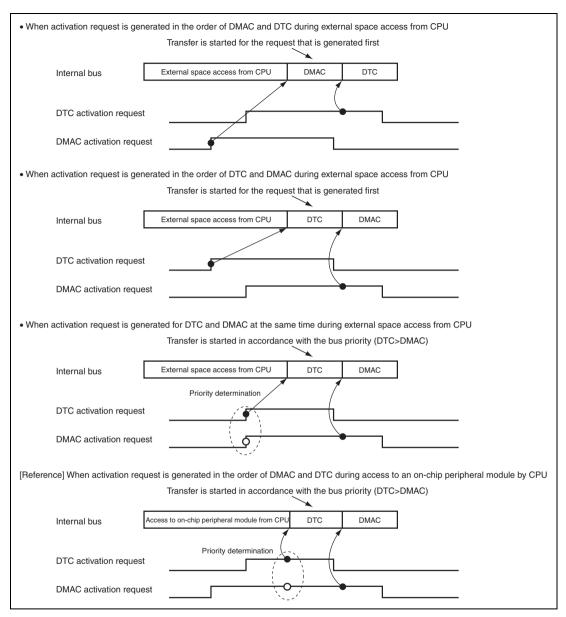

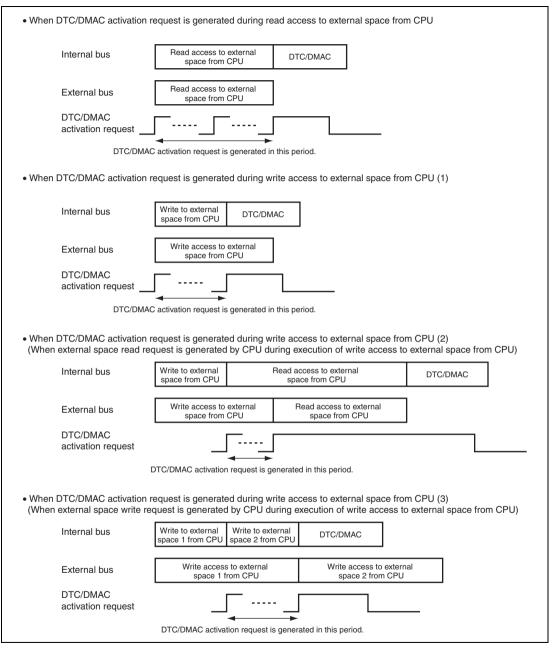

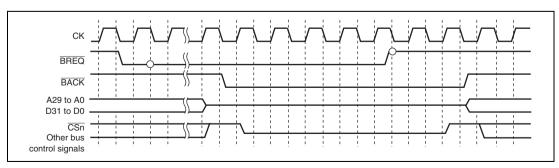

| 8.6       DTC Activation by Interrupt       210         8.7       Examples of Use of the DTC       211         8.7.1       Normal Transfer Mode       211         8.7.2       Chain Transfer when Counter = 0       213         8.9       Usage Notes       213         8.9.1       Module Standby Mode Setting       213         8.9.2       On-Chip RAM       213         8.9.3       DTCE Bit Setting       213         8.9.4       Chain Transfer       213         8.9.5       Transfer Information Start Address, Source Address, and Destination       Address         Address       214         8.9.6       Access to DMAC or DTC Registers through DTC       214         8.9.7       Notes on IRQ Interrupt as DTC Activation Source       214         8.9.8       Notes on SCI and SCIF as DTC Activation Sources       214         8.9.9       Clearing Interrupt Source Flag       214         8.9.10       Conflict between NMI Interrupt and DTC Activation       215         8.9.11       Operation when a DTC Activation Request Is Cancelled While in Progress       215         Section 9       Bus State Controller (BSC)       217         9.1       Features       220         9.3       Area Overview                                                     |      | 8.5.9     | DTC Bus Release Timing                         | 206 |

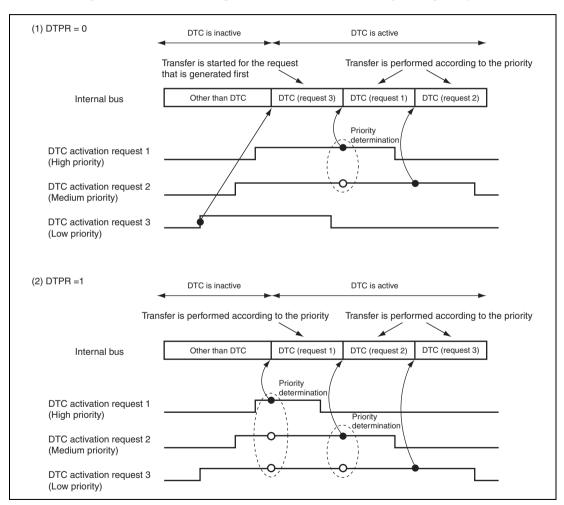

| 8.7       Examples of Use of the DTC       211         8.7.1       Normal Transfer Mode       211         8.7.2       Chain Transfer when Counter = 0       211         8.8       Interrupt Sources       213         8.9       Usage Notes       213         8.9.1       Module Standby Mode Setting       213         8.9.2       On-Chip RAM       213         8.9.3       DTCE Bit Setting       213         8.9.4       Chain Transfer       213         8.9.5       Transfer Information Start Address, Source Address, and Destination       Address         4       A.9.6       Access to DMAC or DTC Registers through DTC       214         8.9.7       Notes on IRQ Interrupt as DTC Activation Source       214         8.9.8       Notes on SCI and SCIF as DTC Activation Sources       214         8.9.9       Clearing Interrupt Source Flag       214         8.9.10       Conflict between NMI Interrupt and DTC Activation       215         Section 9       Bus State Controller (BSC)       217         9.1       Features       217         9.2       Input/Output Pins       220         9.3       Area Overview       222         9.3.1       Area Division       222 <td></td> <td>8.5.10</td> <td>DTC Activation Priority Order</td> <td> 209</td>    |      | 8.5.10    | DTC Activation Priority Order                  | 209 |

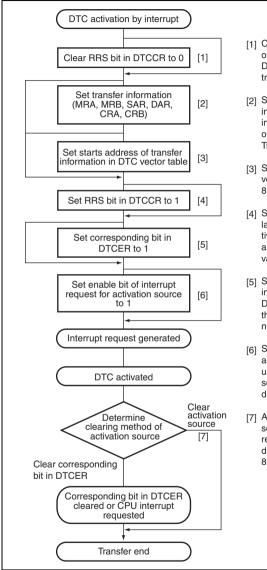

| 8.7       Examples of Use of the DTC       211         8.7.1       Normal Transfer Mode       211         8.7.2       Chain Transfer when Counter = 0       211         8.8       Interrupt Sources       213         8.9       Usage Notes       213         8.9.1       Module Standby Mode Setting       213         8.9.2       On-Chip RAM       213         8.9.3       DTCE Bit Setting       213         8.9.4       Chain Transfer       213         8.9.5       Transfer Information Start Address, Source Address, and Destination       Address         4       A.9.6       Access to DMAC or DTC Registers through DTC       214         8.9.7       Notes on IRQ Interrupt as DTC Activation Source       214         8.9.8       Notes on SCI and SCIF as DTC Activation Sources       214         8.9.9       Clearing Interrupt Source Flag       214         8.9.10       Conflict between NMI Interrupt and DTC Activation       215         Section 9       Bus State Controller (BSC)       217         9.1       Features       217         9.2       Input/Output Pins       220         9.3       Area Overview       222         9.3.1       Area Division       222 <td>8.6</td> <td>DTC Ac</td> <td>ctivation by Interrupt</td> <td> 210</td>        | 8.6  | DTC Ac    | ctivation by Interrupt                         | 210 |

| 8.7.2       Chain Transfer when Counter = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8.7  |           |                                                |     |

| 8.8       Interrupt Sources       213         8.9       Usage Notes       213         8.9.1       Module Standby Mode Setting       213         8.9.2       On-Chip RAM       213         8.9.3       DTCE Bit Setting       213         8.9.4       Chain Transfer       213         8.9.5       Transfer Information Start Address, Source Address, and Destination       214         8.9.6       Access to DMAC or DTC Registers through DTC       214         8.9.7       Notes on IRQ Interrupt as DTC Activation Source       214         8.9.8       Notes on SCI and SCIF as DTC Activation Sources       214         8.9.9       Clearing Interrupt Source Flag       214         8.9.10       Conflict between NMI Interrupt and DTC Activation       215         8.9.11       Operation when a DTC Activation Request Is Cancelled While in Progress       215         Section 9       Bus State Controller (BSC)       217         9.1       Features       217         9.2       Input/Output Pins       220         9.3       Area Overview       222         9.3.1       Area Division       222         9.3.2       Address Map       222                                                                                                                       |      | 8.7.1     | Normal Transfer Mode                           | 211 |

| 8.8       Interrupt Sources       213         8.9       Usage Notes       213         8.9.1       Module Standby Mode Setting       213         8.9.2       On-Chip RAM       213         8.9.3       DTCE Bit Setting       213         8.9.4       Chain Transfer       213         8.9.5       Transfer Information Start Address, Source Address, and Destination       214         8.9.6       Access to DMAC or DTC Registers through DTC       214         8.9.7       Notes on IRQ Interrupt as DTC Activation Source       214         8.9.8       Notes on SCI and SCIF as DTC Activation Sources       214         8.9.9       Clearing Interrupt Source Flag       214         8.9.10       Conflict between NMI Interrupt and DTC Activation       215         8.9.11       Operation when a DTC Activation Request Is Cancelled While in Progress       215         Section 9       Bus State Controller (BSC)       217         9.1       Features       217         9.2       Input/Output Pins       220         9.3       Area Overview       222         9.3.1       Area Division       222         9.3.2       Address Map       222                                                                                                                       |      | 8.7.2     | Chain Transfer when Counter = 0                | 211 |

| 8.9       Usage Notes       213         8.9.1       Module Standby Mode Setting       213         8.9.2       On-Chip RAM       213         8.9.3       DTCE Bit Setting       213         8.9.4       Chain Transfer       213         8.9.5       Transfer Information Start Address, Source Address, and Destination       214         8.9.6       Access to DMAC or DTC Registers through DTC       214         8.9.7       Notes on IRQ Interrupt as DTC Activation Source       214         8.9.8       Notes on SCI and SCIF as DTC Activation Sources       214         8.9.9       Clearing Interrupt Source Flag       214         8.9.10       Conflict between NMI Interrupt and DTC Activation       215         8.9.11       Operation when a DTC Activation Request Is Cancelled While in Progress       215         Section 9       Bus State Controller (BSC)       217         9.1       Features       217         9.2       Input/Output Pins       220         9.3       Area Overview       222         9.3.1       Area Division       222         9.3.2       Address Map       222                                                                                                                                                                     | 8.8  | Interrup  |                                                |     |

| 8.9.1       Module Standby Mode Setting       213         8.9.2       On-Chip RAM       213         8.9.3       DTCE Bit Setting       213         8.9.4       Chain Transfer       213         8.9.5       Transfer Information Start Address, Source Address, and Destination Address       214         8.9.6       Access to DMAC or DTC Registers through DTC       214         8.9.7       Notes on IRQ Interrupt as DTC Activation Source       214         8.9.8       Notes on SCI and SCIF as DTC Activation Sources       214         8.9.9       Clearing Interrupt Source Flag       214         8.9.10       Conflict between NMI Interrupt and DTC Activation       215         8.9.11       Operation when a DTC Activation Request Is Cancelled While in Progress       215         Section 9       Bus State Controller (BSC)       217         9.1       Features       217         9.2       Input/Output Pins       220         9.3       Area Overview       222         9.3.1       Area Division       222         9.3.2       Address Map       222                                                                                                                                                                                                     | 8.9  | <u>*</u>  |                                                |     |

| 8.9.2       On-Chip RAM       213         8.9.3       DTCE Bit Setting       213         8.9.4       Chain Transfer       213         8.9.5       Transfer Information Start Address, Source Address, and Destination Address       214         8.9.6       Access to DMAC or DTC Registers through DTC       214         8.9.7       Notes on IRQ Interrupt as DTC Activation Source       214         8.9.8       Notes on SCI and SCIF as DTC Activation Sources       214         8.9.9       Clearing Interrupt Source Flag       214         8.9.10       Conflict between NMI Interrupt and DTC Activation       215         8.9.11       Operation when a DTC Activation Request Is Cancelled While in Progress       215         Section 9       Bus State Controller (BSC)       217         9.1       Features       217         9.2       Input/Output Pins       220         9.3       Area Overview       222         9.3.1       Area Division       222         9.3.2       Address Map       222                                                                                                                                                                                                                                                               |      | Ū         |                                                |     |

| 8.9.3       DTCE Bit Setting       213         8.9.4       Chain Transfer       213         8.9.5       Transfer Information Start Address, Source Address, and Destination Address       214         8.9.6       Access to DMAC or DTC Registers through DTC       214         8.9.7       Notes on IRQ Interrupt as DTC Activation Source       214         8.9.8       Notes on SCI and SCIF as DTC Activation Sources       214         8.9.9       Clearing Interrupt Source Flag       214         8.9.10       Conflict between NMI Interrupt and DTC Activation       215         8.9.11       Operation when a DTC Activation Request Is Cancelled While in Progress       215         Section 9       Bus State Controller (BSC)       217         9.1       Features       217         9.2       Input/Output Pins       220         9.3       Area Overview       222         9.3.1       Area Division       222         9.3.2       Address Map       222                                                                                                                                                                                                                                                                                                         |      | 8.9.2     | · · · · · · · · · · · · · · · · · · ·          |     |

| 8.9.4 Chain Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | 8.9.3     |                                                |     |

| 8.9.5 Transfer Information Start Address, Source Address, and Destination Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |           | 6                                              |     |

| Address       214         8.9.6       Access to DMAC or DTC Registers through DTC       214         8.9.7       Notes on IRQ Interrupt as DTC Activation Source       214         8.9.8       Notes on SCI and SCIF as DTC Activation Sources       214         8.9.9       Clearing Interrupt Source Flag       214         8.9.10       Conflict between NMI Interrupt and DTC Activation       215         8.9.11       Operation when a DTC Activation Request Is Cancelled While in Progress       215         Section 9       Bus State Controller (BSC)       217         9.1       Features       217         9.2       Input/Output Pins       220         9.3       Area Overview       222         9.3.1       Area Division       222         9.3.2       Address Map       222                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | 8.9.5     |                                                |     |

| 8.9.6 Access to DMAC or DTC Registers through DTC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |           |                                                | 214 |

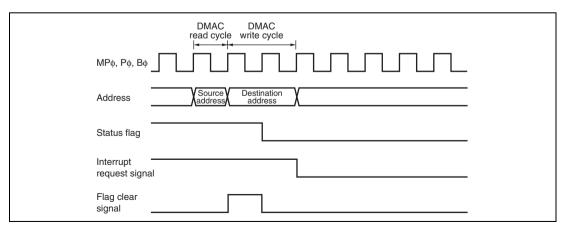

| 8.9.7 Notes on IRQ Interrupt as DTC Activation Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      | 8.9.6     |                                                |     |

| 8.9.8 Notes on SCI and SCIF as DTC Activation Sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |           |                                                |     |

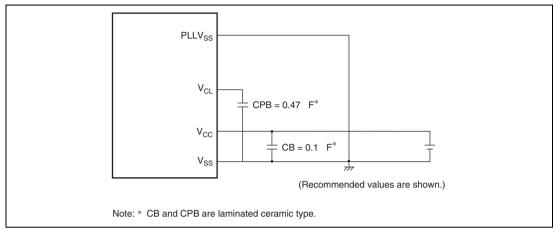

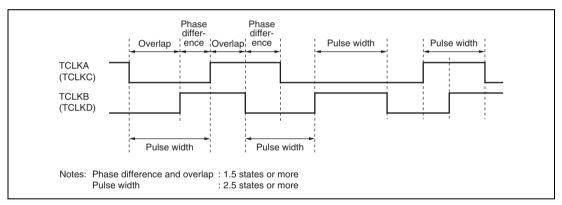

| 8.9.9 Clearing Interrupt Source Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |           |                                                |     |