# **TDA19978A**

Quad HDMI 1.4a receiver interface with equalizer (HDTV up to 1080p, up to UXGA for PC's format)

Rev. 4 — 6 December 2010

**Product data sheet**

### 1. General description

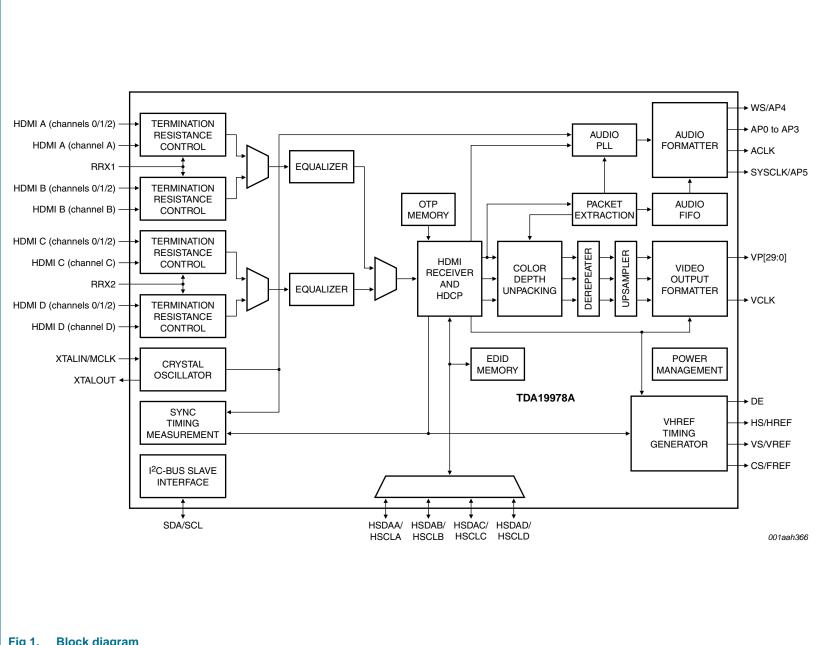

The TDA19978A is a four input HDMI 1.4a compliant receiver with embedded EDID memory. The built in auto-adaptive equalizer improves signal quality and allows the use of cable lengths up to 25 m (laboratory tested with a 0.5 mm (24 AWG) cable at 2.05 gigasamples per second). The HDCP key set is stored in non-volatile One Time Programmable (OTP) memory for maximum security. In addition, the TDA19978A is delivered with software drivers to ease configuration and use.

### The TDA19978A supports:

- TV resolutions:

- 480i (1440 × 480i at 60 Hz), 576i (1440 × 576i at 50 Hz) to HDTV (up to 1920 × 1080p at 50/60 Hz)

- WUXGA (1920 x 1200p at 60 Hz) reduced blanking format

- PC resolutions:

- VGA  $(640 \times 480 \text{p} \text{ at } 60 \text{ Hz})$  to UXGA  $(1600 \times 1200 \text{p} \text{ at } 60 \text{ Hz})$

- Deep Color mode in 10-bit and 12-bit (up to 205 MHz TMDS clock)

- Gamut boundary description

- IEC 60958/IEC 61937, One Bit Audio (in SACD), DST (in compressed DSD) and HBR stream

### The TDA19978A includes:

- An enhanced PC and TV format recognition system

- Generation of a  $128/256/512 \times f_s$  system clock allowing the use of simple audio DACs without an integrated PLL (such as the UDA1334BTS)

- An embedded oscillator (an external crystal can also be used)

- Improved audio clock generation using an external reference clock

- One Bit Audio (in SACD), DST (in compressed DSD) and HBR stream support

The TDA19978A converts HDMI streams with or without HDCP into RGB or YCbCr digital signals. The YCbCr digital output signal can be 4:4:4 or 4:2:2 semi-planar format based on the ITU-R BT.601 standard or 4:2:2 based on the ITU-R BT.656 format. The device can adjust the output timing of the video port by altering the values for  $t_{su(Q)}$  and  $t_{h(Q)}$ . In addition, all settings are controllable using the I²C-bus.

### Quad HDMI 1.4a receiver with digital processing)

### 2. Features and benefits

- Complies with the HDMI 1.4a, DVI 1.0, CEA-861-D and HDCP 1.4 standards

- Four (quad) independent HDMI inputs, up to the HDMI frequency of 205 MHz

- Embedded auto-adaptive equalizer on all HDMI links

- EDID memory: 253 shared bytes and three bytes dedicated to each HDMI input

- Supports color depth processing (8-bit, 10-bit or 12-bit per color)

- Color gamut metadata packet with interrupt on each update, readable via the I<sup>2</sup>C-bus

- Up to four S/PDIF or I<sup>2</sup>S-bus outputs (eight channels) at a sampling rate up to 192 kHz with IEC 60958/IEC 61937 stream

- HBR audio stream up to 768 kHz with four demultiplexed S/PDIF or I<sup>2</sup>S-bus outputs

- HBR streams (compatible with DTS-HD master audio and Dolby TrueHD up to eight channels due to HBR packet for stream with a frame rate up to 768 kHz) support

- DSD and DST audio stream up to six DSD channels output for SACD with DST Audio Packet support

- Channel status decoder supports multi-channel reception

- Improved audio clock generation using an external reference clock

- System/master clock output (128/256/512 × f<sub>s</sub>) enables the use of the UDA1334BTS

- The HDMI interface supports:

- ◆ All HDTV formats up to 1920 × 1080p at 50/60 Hz and WUXGA (1920 × 1200p at 60 Hz) with support for reduced blanking

- ◆ 3D formats including all primary formats up to 1920 × 1080p at 30 Hz Frame Packing and 1920 × 1080p at 60 Hz Top-and-Bottom

- ◆ PC formats up to UXGA (1600 × 1200p at 60 Hz)

- Embedded oscillator (an external crystal can be used)

- Frame and field detection for interlaced video signal

- Sync timing measurements for format recognition

- Improved system for measurements of blanking and video active area allowing an accurate recognition of PC and TV formats

- HDCP with repeater capability

- Embedded non-volatile memory storage of HDCP keys

- Programmable color space input signal conversion from RGB-to-YCbCr or YCbCr-to-RGB

- Output formats: RGB 4:4:4, YCbCr 4:4:4, YCbCr 4:2:2 semi-planar based on the ITU-R BT.601 standard and YCbCr 4:2:2 ITU-R BT.656

- 8-bit, 10-bit or 12-bit output formats selectable using the I<sup>2</sup>C-bus (8-bit and 10-bit only in 4:4:4 format)

- I<sup>2</sup>C-bus adjustable timing of video port  $(t_{su(Q)})$  and  $t_{h(Q)}$

- Downsampling-by-two with selectable filters on Cb and Cr channels in 4:2:2 mode

- Internal video and audio pattern generator

- Controllable using the I<sup>2</sup>C-bus; 5 V tolerant and bit rate up to 400 kbit/s

- DDC-bus inputs 5 V tolerant and bit rate up to 400 kbit/s

- LV-TTL outputs

- Power-down mode

- CMOS process

- 1.8 V and 3.3 V power supplies

TDA19978A\_SDS

### **Quad HDMI 1.4a receiver with digital processing)**

### ■ Lead-free (Pb) HLQFP144 package

## 3. Applications

- HDTV

- YCbCr or RGB HI-Speed video digitizer

- Projector, plasma and LCD TV

- Rear projection TV

- High-End TV

- Home theater amplifier

- DVD recorder

- AVR and HDMI splitter

### 4. Quick reference data

Table 1. Quick reference data

| Symbol                | Parameter                                       | Conditions                                                              |     | Min   | Тур  | Max   | Unit |

|-----------------------|-------------------------------------------------|-------------------------------------------------------------------------|-----|-------|------|-------|------|

| Digital in            | outs: pins RXxC+, RXxC-[1]                      |                                                                         |     |       |      |       |      |

| f <sub>clk(max)</sub> | maximum clock frequency                         |                                                                         |     | 205   | -    | -     | MHz  |

| Clock tim             | Clock timing output: pins VCLK, ACLK and SYSCLK |                                                                         |     |       |      |       |      |

| f <sub>clk(max)</sub> | maximum clock frequency                         | pin VCLK                                                                |     | 165   | -    | -     | MHz  |

|                       |                                                 | pin ACLK                                                                |     | 25    | -    | -     | MHz  |

|                       |                                                 | pin SYSCLK                                                              |     | 50    | -    | -     | MHz  |

| Supplies              |                                                 |                                                                         |     |       |      |       |      |

| V <sub>DDH(3V3)</sub> | HDMI supply voltage (3.3 V)                     |                                                                         |     | 3.135 | 3.3  | 3.465 | V    |

| V <sub>DDH(1V8)</sub> | HDMI supply voltage (1.8 V)                     |                                                                         |     | 1.71  | 1.8  | 1.89  | V    |

| V <sub>DDI(3V3)</sub> | input supply voltage (3.3 V)                    |                                                                         |     | 3.135 | 3.3  | 3.465 | V    |

| V <sub>DDC(1V8)</sub> | core supply voltage (1.8 V)                     |                                                                         |     | 1.71  | 1.8  | 1.89  | V    |

| V <sub>DDO(3V3)</sub> | output supply voltage (3.3 V)                   |                                                                         |     | 3.135 | 3.3  | 3.465 | V    |

| Р                     | power dissipation                               | active mode                                                             | [2] |       |      |       |      |

|                       |                                                 | 720p at 60 Hz                                                           |     | -     | 0.75 | -     | W    |

|                       |                                                 | 1080p at 60 Hz                                                          |     | -     | 1.13 | -     | W    |

|                       |                                                 | 1080p at 60 Hz; Deep Color mode                                         |     | -     | 1.63 | -     | W    |

| P <sub>cons</sub>     | power consumption                               | Power-down mode                                                         |     |       |      |       |      |

|                       |                                                 | pin PD = HIGH                                                           |     | -     | 1    | -     | mW   |

|                       |                                                 | I <sup>2</sup> C-bus; EDID and HDCP memory power-up                     |     | -     | 4    | -     | mW   |

|                       |                                                 | I <sup>2</sup> C-bus; EDID; activity detection and HDCP memory power-up |     | -     | 150  | -     | mW   |

<sup>[1]</sup> x = A, B, C or D.

<sup>[2]</sup> At 30 % activity on video port output.

### Quad HDMI 1.4a receiver with digital processing)

# 5. Ordering information

Table 2. Ordering information

| Type number | Package  |                                                                                                                       |          |  |  |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------|----------|--|--|

|             | Name     | Description                                                                                                           | Version  |  |  |

| TDA19978AHV | HLQFP144 | plastic thermal enhanced low profile quad flat package; 144 leads; body $20 \times 20 \times 1.4$ mm; exposed die pad | SOT612-3 |  |  |

# Quad HDMI 1.4a receiver with digital processing)

# <u>ဂ</u> Block diagram

© NXP B.V. 2010. All rights reserved

Product data sheet

All information provided in this document is subject to legal disclaimer

Rev.

4

6 December 2010

# 7. Limiting values

Table 3. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                | Parameter                        | Conditions | Min   | Max   | Unit |

|-----------------------|----------------------------------|------------|-------|-------|------|

| $V_{\text{DDx}(3V3)}$ | supply voltage on all 3.3 V pins |            | -0.5  | +4.6  | V    |

| V <sub>DDx(1V8)</sub> | supply voltage on all 1.8 V pins |            | -0.5  | +2.5  | V    |

| $\Delta V_{DD}$       | supply voltage difference        |            | -0.5  | +0.5  | V    |

| I <sub>O</sub>        | output current                   |            | -     | 35    | mA   |

| T <sub>stg</sub>      | storage temperature              |            | -55   | +150  | °C   |

| T <sub>amb</sub>      | ambient temperature              |            | 0     | 70    | °C   |

| Tj                    | junction temperature             |            | -     | 125   | °C   |

| V <sub>ESD</sub>      | electrostatic discharge voltage  | HBM        | -2000 | +2000 | V    |

Quad HDMI 1.4a receiver with digital processing)

### 8. Abbreviations

Table 4. Abbreviations

| Acronym | Description                                 |

|---------|---------------------------------------------|

| AVR     | Audio Video Receiver                        |

| CMOS    | Complementary Metal-Oxide-Semiconductor     |

| DAC     | Digital-to-Analog Converter                 |

| DDC-bus | Display Data Channel bus                    |

| DSD     | Direct Stream Digital                       |

| DST     | Direct Stream Transfer                      |

| DTS-HD  | Digital Theater Systems HD                  |

| DVD     | Digital Versatile Disc                      |

| DVI     | Digital Video Interface                     |

| EDID    | Extended Display Identification Data        |

| НВМ     | Human Body Model                            |

| HBR     | High-Bitrate                                |

| HD      | High-Definition                             |

| HDCP    | High-bandwidth Digital Content Protection   |

| HDMI    | High-Definition Multimedia Interface        |

| HDTV    | High-Definition TeleVision                  |

| LV-TTL  | Low Voltage Transistor-Transistor Logic     |

| OTP     | One Time Programmable                       |

| PLL     | Phase-Locked Loop                           |

| RGB     | Red Green Blue                              |

| SACD    | Super Audio CD                              |

| S/PDIF  | Sony/Philips Digital Interface Format       |

| SYNC    | SYNChronization                             |

| TMDS    | Transition Minimized Differential Signaling |

| UXGA    | Ultra eXtended Graphics Array               |

### Quad HDMI 1.4a receiver with digital processing)

Table 4.

Abbreviations ...continued

| Acronym | Description                                      |

|---------|--------------------------------------------------|

| VHREF   | Vertical Horizontal REFerence                    |

| VGA     | Video Graphics Array                             |

| WUXGA   | Wide Ultra eXtended Graphics Array               |

| YCbCr   | Y = Luminance, Cb = Chroma blue, Cr = Chroma red |

# 9. Revision history

Table 5. Revision history

| Document ID                                                         | Release date | Data sheet status    | Change notice | Supersedes                      |  |  |

|---------------------------------------------------------------------|--------------|----------------------|---------------|---------------------------------|--|--|

| TDA19978A_SDS v.4                                                   | 20101206     | Product data sheet   | -             | TDA19978A_SDS v.3               |  |  |

| Modifications: • Replaced in all document HDMI 1.3a with HDMI 1.4a  |              |                      |               |                                 |  |  |

| <ul> <li>Replaced in all document HDCP 1.2 with HDCP 1.4</li> </ul> |              |                      |               |                                 |  |  |

| TDA19978A_SDS v.3                                                   | 20100511     | Product data sheet   | -             | TDA19978A_SDS v.1 <sup>11</sup> |  |  |

| TDA19978A_SDS v.1                                                   | 20080528     | Objective data sheet | -             | -                               |  |  |

<sup>[1]</sup> Revision 2 is not available.

### Quad HDMI 1.4a receiver with digital processing)

### 10. Legal information

### 10.1 Data sheet status

| Document status[1][2]          | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions"

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

### 10.2 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

### 10.3 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Suitability for use** — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or

malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

TDA19978A\_SDS

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2010. All rights reserved.

### Quad HDMI 1.4a receiver with digital processing)

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

Non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

### 10.4 Licenses

### Purchase of NXP ICs with HDMI technology

Use of an NXP IC with HDMI technology in equipment that complies with the HDMI standard requires a license from HDMI Licensing LLC, 1060 E. Arques Avenue Suite 100, Sunnyvale CA 94085, USA, e-mail: admin@hdmi.org.

### 10.5 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

I<sup>2</sup>C-bus — logo is a trademark of NXP B.V.

### 11. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

### Quad HDMI 1.4a receiver with digital processing)

### 12. Contents

| 1    | General description   | 1  |

|------|-----------------------|----|

| 2    | Features and benefits | 2  |

| 3    | Applications          | 3  |

| 4    | Quick reference data  | 3  |

| 5    | Ordering information  | 4  |

| 6    | Block diagram         | 5  |

| 7    | Limiting values       | 6  |

| 8    | Abbreviations         | 6  |

| 9    | Revision history      | 7  |

| 10   | Legal information     | 8  |

| 10.1 | Data sheet status     | 8  |

| 10.2 | Definitions           | 8  |

| 10.3 | Disclaimers           | 8  |

| 10.4 | Licenses              | S  |

| 10.5 | Trademarks            | õ  |

| 11   | Contact information   | 9  |

| 12   | Contents              | 10 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.