BUILT ON 'ower **QorlQ Communications Platforms**

## **P4 Series Multicore Processors**

#### **Overview**

Freescale QorlQ communications platforms are the next-generation evolution of our leading PowerQUICC communications processors. Built using highperformance Power Architecture® cores, QorlQ platforms enable a new era of networking innovation where the reliability, security and quality of service for every connection matters.

#### **QorlQ P4080 Multicore Processor**

The QorIQ P4080 multicore processor, the first product offered in the QorlQ P4 platform series, delivers industry-leading performance in the under 30-watt power category. It combines eight Power Architecture e500mc cores operating at frequencies up to 1.5 GHz with high-performance datapath acceleration logic, as well as networking I/O and other peripheral bus interfaces. The P4080, built

in 45 nm technology, is designed to deliver high-performance, next-generation networking services in a very low power envelope.

The QorlQ P4080 processor is designed for combined control and dataplane processing, enabling high-performance layers 2-7 processing. Its high level of integration offers significant performance benefits compared to multiple discrete devices, while also greatly simplifying board design.

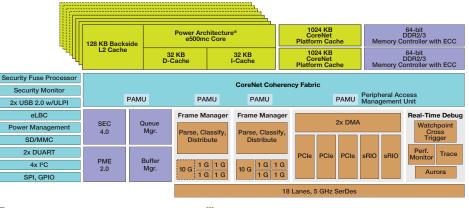

### QorlQ P4080/P4040/P4081 Block Diagram

Core Complex (CPU, L2 and Frontside CoreNet Platform Cache) Accelerators and Memory Control Networking Elements

P4080 and P4040 Only

Basic Peripherals and Interconnect

The processor is well suited for applications that are highly compute intensive, I/O intensive or both. This makes it ideal for applications such as enterprise and service provider routers, switches, media gateways, base station controllers, radio network controllers (RNCs), access gateways for long-term evolution (LTE) and generalpurpose embedded computing systems in the networking, telecom, industrial, aerospace and defense markets.

#### **Key Features**

Freescale delivers a groundbreaking threetiered cache hierarchy on the QorlQ P4 platform. Each core has an integrated level 1 (L1) cache as well as a dedicated level 2 (L2) backside cache that can significantly improve performance. Finally, a multi-megabyte level 3 (L3) cache is also provided for those tasks for which a shared cache is desirable.

The CoreNet coherency fabric is a key design component of the QorlQ P4 platform. It manages full coherency of the caches and provides scalable on-chip, point-to-point connectivity supporting concurrent traffic to and from multiple resources connected to the fabric, eliminating single-point bottlenecks for non-competing resources. This eliminates bus contention and latency issues associated with scaling shared bus/shared memory architectures that are common in other multicore approaches.

The QorlQ P4080 multicore processor is extremely flexible and can be configured to meet many system application needs. The processor's e500mc cores, leveraging advanced virtualization technology, can work as eight symmetric multiprocessing (SMP) cores, or eight completely asymmetric multiprocessing (AMP) cores, or they can be operated with varying degrees of independence with a combination of SMP and AMP groupings. Full processor independence, including the ability to independently boot and reset each e500mc core, is a defining characteristic of the device. The ability of the cores to run different operating systems (OS), or run OS-less, provides the user with significant flexibility in partitioning between control, datapath and applications processing. It also simplifies consolidation of functions previously spread across multiple discrete processors onto a single device.

Advanced virtualization technology brings a new level of hardware partitioning through an embedded hypervisor that allows system developers to ensure software running on any CPU only accesses the resources (memory, peripherals, etc.) that it is explicitly authorized to access. The embedded hypervisor enables safe and autonomous operation of multiple individual operating systems, allowing them to share system resources, including processor cores, memory and other on-chip functions.

#### Ecosystem and Developer Environment

Developers creating solutions with Power Architecture technology have long benefited from a vibrant support ecosystem, including high-quality tools, OSes and network protocol stacks. Freescale has collaborated with our partners on the QorlQ P4080 processor to continue our strong ecosystem heritage. This helps to ensure that the best enablement tools are available to cost-effectively meet the unique development challenges of multicore architectures and speed your time to market. To this end, Freescale has partnered with Virtutech to offer a robust, innovative hybrid simulation environment that provides a controlled, deterministic and fully reversible environment for the development, debugging and benchmarking of software for complex multicore-based architectures. The hybrid simulator combines Virtutech's fast, functional Simics<sup>™</sup> model, with a detailed performance model of the platform. This combination enables fast hardware concept testing and evaluation, as well as performance verification and helps accelerate your development cycle, provide more flexible debug capability and improve the overall quality of your software.

Freescale has also engineered capabilities into the QorlQ P4080 to enable advanced debugging while working in tandem with its ecosystem partners to assure availability of tools that can take advantage of these features. These capabilities include integrated instruction trace, watchpoint triggers, crossevent triggers, performance monitoring and other debug features as defined by the Power<sup>®</sup> ISA. These features enable dynamic debug essential for providing visibility into complex interactions that may occur among tasks running on different cores.

# QorlQ P4080 Technical Specifications

- Eight high-performance Power Architecture e500mc cores, each with a 32 KB instruction and data L1 cache and a private 128 KB L2 cache

- Three levels of instruction: user, supervisor and hypervisor

- Independent boot and reset

- Secure boot capability

- 2 MB shared L3 CoreNet platform cache

- Hierarchical interconnect fabric

- CoreNet fabric supporting coherent and non-coherent transactions with prioritization and bandwidth allocation amongst CoreNet end points

- · 800 Gb/s coherent read bandwidth

- Queue manager fabric supporting packet-level queue management and quality of service scheduling

- Two 64-bit DDR2/DDR3 SDRAM memory controllers with ECC and interleaving support

- Datapath acceleration architecture incorporating acceleration for the following functions:

- Packet parsing, classification and distribution

- Queue management for scheduling, packet sequencing and congestion management

- Hardware buffer management for buffer allocation and de-allocation

- Cryptographic security acceleration (SEC 4.0)

- RegEx pattern matching (PME 2.0)

- Ethernet interfaces

- Two 10 Gb/s Ethernet (XAUI) controllers

- Eight 1 Gb/s Ethernet (SGMII) controllers

- High-speed peripheral interfaces

- Three PCI Express® V2.0 controllers/ ports running at up to 5 GHz

- Two Serial RapidIO<sup>®</sup> 1.2 controllers/ ports running at up to 3.125 GHz

- Additional peripheral interfaces

- Two USB controllers with ULPI interface to external PHY

- SD/MMC

- SPI controller

- Four I<sup>2</sup>C controllers

- Two dual UARTs

- · Enhanced local bus controller

- Multicore programmable interrupt controller

- Two 4-channel DMA engines

For more information about Virtutech Simics, please visit **virtutech.com**.

## P4 Series Chart

The P4080 was the flagship product for the QorlQ family when it was first introduced to the market. It provided the foundation upon which the P5, P3, P2 and P1 processor families were built. In addition, the P4 series expanded its portfolio with the P4040 and P4081 communications processors. These processors provide the performance, power and price necessary to meet a broad spectrum of high-performance applications. The P4040 is pin-for-pin compatible with the P4080 processor, providing the same I/O functionality and frequency as the P4080 but with fewer cores. This is designed to provide the user with a smaller power envelope footprint. The P4081 addition brings high-performance computing to a broader spectrum of applications. Like the P4040, it is pin-for-pin compatible to both the P4080 and P4040. It contains eight cores, with each core capable of supporting 1.2 GHz. At attractive price and power points, this device expands the possibilities of applications for high-performance computing.

| P4 QorlQ<br>Platform | Device | Core | Top Core<br>Frequency | L2 Size | DDR 2/3<br>Support | GE Ports | Serdes | PCI<br>Express<br>Controllers | 10 GB<br>Ethernet<br>Ports | Trust<br>Architecture |

|----------------------|--------|------|-----------------------|---------|--------------------|----------|--------|-------------------------------|----------------------------|-----------------------|

| P4                   | P4080  | 8    | 1500 MHz              | 1 MB    | Dual 64-bit        | 8        | 16     | 3                             | 2                          | Yes                   |

| P4                   | P4040  | 4    | 1500 MHz              | 512 KB  | Dual 64-bit        | 8        | 16     | 3                             | 2                          | Yes                   |

| P4                   | P4081  | 8    | 1200 MHz              | 1 MB    | Dual 64-bit        | 8        | 16     | 3                             | 1                          | Yes                   |

#### For current information, please visit freescale.com/QorlQ

Freescale, the Freescale logo, PowerQUICC and QorlQ are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. CoreNet is a trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2008, 2014 Freescale Semiconductor, Inc.

Document Number: QP4080FS REV 4