Overview 1

QMC Memory Organization 2

QMC Commands 3

QMC Exceptions 4

Buffer Descriptors 5

QMC Initialization 6

Features Deleted in MC68MH360 7

Performance 8

68360 Bit Numbering

Frequently-Asked Questions

Connecting ISDN Interfaces to QUICC32

Multi-Subchannel (MSC) Microcode

Index IND

- 2 QMC Memory Organization

- 3 QMC Commands

- 4 QMC Exceptions

- 5 Buffer Descriptors

- 6 QMC Initialization

- 7 Features Deleted in MC68MH360

- 8 Performance

- 9 Multi-Subchannel (MSC) Microcode

- A 68360 Bit Numbering

- B Frequently-Asked Questions

- C Connecting ISDN Interfaces to QUICC32

IND Index

QMCSUPPLEMENT/AD 8/97

# QMC Supplement to MC68360 and MPC860 User's Manuals

Home Page:

www.freescale.com

email:

support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 (800) 521-6274 480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064, Japan 0120 191014 +81 2666 8080 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd.

Technical Information Center

2 Dai King Street

Tai Po Industrial Estate,

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor

Literature Distribution Center

P.O. Box 5405

Denver, Colorado 80217

(800) 441-2447

303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor

@hibbertgroup.com

implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for

surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product

could create a situation where personal injury or death may occur. Should Buyer

purchase or use Freescale Semiconductor products for any such unintended or

directly or indirectly, any claim of personal injury or death associated with such

Semiconductor was negligent regarding the design or manufacture of the part.

unintended or unauthorized use, even if such claim alleges that Freescale

unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor

claims, costs, damages, and expenses, and reasonable attorney fees arising out of,

and its officers, employees, subsidiaries, affiliates, and distributors harmless against all

Information in this document is provided solely to enable system and software

freescale™

# **CONTENTS**

| Paragraph<br>Number | Title                                                 | Page<br>Number |  |

|---------------------|-------------------------------------------------------|----------------|--|

|                     | AudienceOrganization                                  |                |  |

|                     | Additional Reading                                    | xii            |  |

|                     | Conventions                                           |                |  |

|                     | Acronyms and Abbreviations                            | xiii           |  |

|                     | Chapter 1<br>Overview                                 |                |  |

| 1.1                 | The QMC (QUICC Multichannel Controller)               | 1-1            |  |

| 1.2                 | Introduction                                          |                |  |

| 1.3                 | QMC Features                                          |                |  |

| 1.4                 | The Time Slot Assigner and the QMC                    |                |  |

| 1.5                 | The Serial Interface (SI)                             | 1-4            |  |

| 1.5.1               | Synchronization                                       | 1-5            |  |

| 1.5.2               | Loopback Mode                                         | 1-5            |  |

| 1.5.3               | Echo Mode                                             |                |  |

| 1.5.4               | Inverted Signals                                      |                |  |

| 1.6                 | QMC Serial Routing and Example Applications           |                |  |

| 1.7                 | SCC Changes on the Fly                                |                |  |

| 1.8                 | SI RAM Errors                                         |                |  |

| 1.9                 | E1/T1 Frame Description                               | 1-11           |  |

|                     | Chapter 2                                             |                |  |

|                     | QMC Memory Organization                               |                |  |

| 2.1                 | QMC Memory Structure                                  | 2-2            |  |

| 2.1.1               | Dual-Ported RAM Base                                  |                |  |

| 2.1.2               | SCC Base and Global Multichannel Parameters           |                |  |

| 2.1.3               | TSATRx/TSATTx Pointers and Time Slot Assignment Table |                |  |

| 2.1.4               | TSATRx/TSATTx Channel Pointers                        |                |  |

| 2.1.5               | Logical Channel TBASE and RBASE                       |                |  |

| 2.1.6               | MCBASE                                                |                |  |

| 2.1.7               | Buffer Descriptor Table                               |                |  |

| 2.1.8               | Data Buffer Pointer                                   | 2-5            |  |

Contents

# **CONTENTS**

| Paragraph<br>Number | Title                                          | Page<br>Number |  |

|---------------------|------------------------------------------------|----------------|--|

| 2.1.9               | Data Buffer                                    | 2-5            |  |

| 2.2                 | Global Multichannel Parameters                 | 2-5            |  |

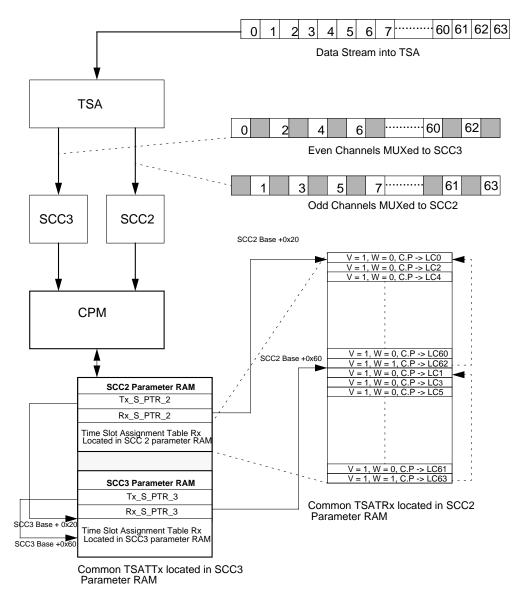

| 2.3                 | Multiple SCC Assignment Tables                 | 2-10           |  |

| 2.4                 | Channel-Specific Parameters                    |                |  |

| 2.4.1               | Channel-Specific HDLC Parameters               |                |  |

| 2.4.1.1             | CHAMR—Channel Mode Register (HDLC)             |                |  |

| 2.4.1.2             | TSTATE—Tx Internal State (HDLC)                |                |  |

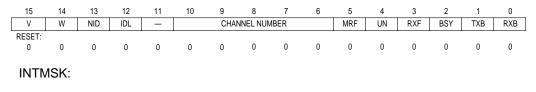

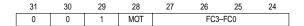

| 2.4.1.3             | INTMSK—Interrupt Mask (HDLC)                   |                |  |

| 2.4.1.4             | RSTATE—Rx Internal State (HDLC)                |                |  |

| 2.4.2               | Channel-Specific Transparent Parameters        |                |  |

| 2.4.2.1             | CHAMR—Channel Mode Register (Transparent Mode) |                |  |

| 2.4.2.2             | TSTATE—Tx Internal State (Transparent Mode)    |                |  |

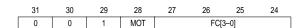

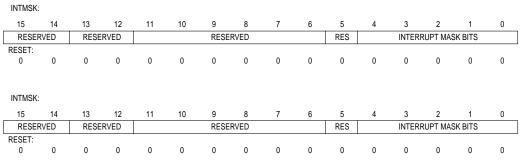

| 2.4.2.3             | INTMSK—Interrupt Mask (Transparent Mode)       |                |  |

| 2.4.2.4             | TRNSYNC—Transparent Synchronization            |                |  |

| 2.4.2.5             | RSTATE—Rx Internal State (Transparent Mode)    | 2-28           |  |

|                     | Chapter 3 QMC Commands                         |                |  |

| 3.1                 | Transmit Commands                              |                |  |

| 3.2                 | Receive Commands                               | 3-2            |  |

|                     | Chapter 4 QMC Exceptions                       |                |  |

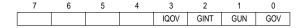

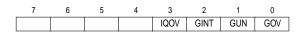

| 4.1                 | Global Error Events                            | 4-2            |  |

| 4.1.1               | Global Underrun (GUN)                          |                |  |

| 4.1.2               | Global Overrun (GOV) in the FIFO               |                |  |

| 4.1.3               | Restart from a Global Error                    |                |  |

| 4.2                 | SCC Event Register (SCCE)                      | 4-3            |  |

| 4.3                 | Interrupt Table Entry                          |                |  |

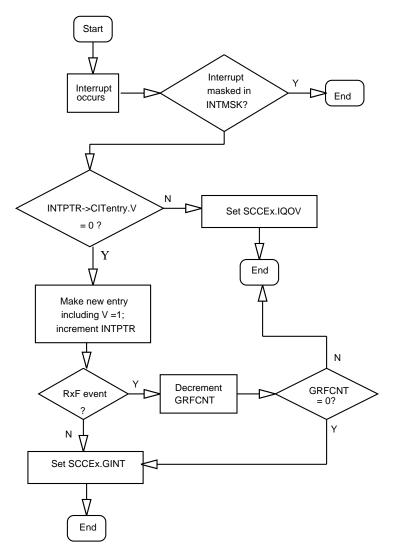

| 4.4                 | Channel Interrupt Processing Flow              |                |  |

|                     | Chapter 5<br>Buffer Descriptors                |                |  |

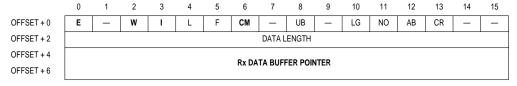

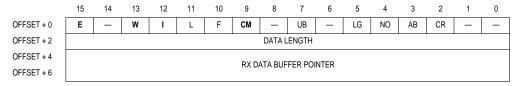

| 5.1                 | Receive Buffer Descriptor                      | 5-1            |  |

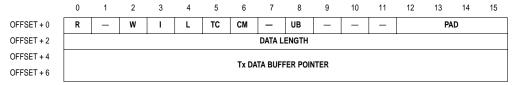

| 5.2                 | Transmit Buffer Descriptor                     |                |  |

| 5.3                 | Placement of Buffer Descriptors                |                |  |

| 5.3.1               | MC68MH360 Internal Memory Structure            |                |  |

| 5.3.2               | Parameter RAM Usage for QMC over Several SCCs  | 5-9            |  |

| 5.3.3               | MPC860MH Internal Memory Structure             |                |  |

# **CONTENTS**

| Paragraph<br>Number | Title                                     | Page<br>Number |

|---------------------|-------------------------------------------|----------------|

| 5.3.4               | MC68MH360 Configured for QMC and Ethernet | 5-20           |

|                     | Ohamtan C                                 |                |

|                     | Chapter 6 QMC Initialization              |                |

| 6.1                 | Initialization Stone                      | £ 1            |

| 6.2                 | Initialization Steps                      |                |

| 6.3                 | Restarting the Transmitter                |                |

| 6.4                 | Restarting the Receiver                   |                |

| 6.5                 | Disabling Receiver and Transmitter        |                |

| 6.6                 | Debugging Hints                           |                |

| 6.6.1               | Pointer Registers                         |                |

| 6.6.2               | State Registers                           |                |

| 0.0.2               | Suite Registers                           | 10             |

|                     | Chapter 7 Features Deleted in MC68MH360   |                |

|                     | Chapter 8                                 |                |

|                     | Performance                               |                |

| 8.1                 | Common Channel Combinations               | Q 1            |

| 8.2                 | CPM Loading                               |                |

| 8.3                 | Bus Latency and Peak Load                 |                |

| 0.5                 | Bus Latericy and I can Load               |                |

|                     | Chapter 9                                 |                |

|                     | Multi-Subchannel (MSC) Microcode          |                |

| 9.1                 | MSC Microcode Features                    | 9-1            |

| 9.2                 | MSC Microcode Operation                   |                |

| 9.3                 | Programming the MSC Protocol              |                |

| 9.4                 | MSC Subchanneling Example                 |                |

| 9.5                 | QMC Memory Organization                   |                |

| 9.6                 | Multi-Subchannel Initialization.          |                |

| ,                   |                                           |                |

|                     | Appendix A<br>68360 Bit Numbering         |                |

| A.1                 | Time Slot Assignment Table                | A-1            |

| A.2                 | Registers in HDLC Mode                    |                |

| A.3                 | Registers in Transparent Mode             |                |

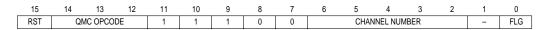

| A.4                 | Command Register                          | A-4            |

|                     |                                           |                |

**Contents** v

# **CONTENTS**

| Paragraph<br>Number | Title                                                              | Page<br>Number |

|---------------------|--------------------------------------------------------------------|----------------|

| A.5                 | SCC Event Register                                                 | A-5            |

| A.6                 | SCCM Register                                                      |                |

| A.7                 | Receive and Transmit Buffer Descriptors                            | A-5            |

|                     | Appendix B                                                         |                |

|                     | Frequently-Asked Questions                                         |                |

| B.1                 | Questions Common to MH360 and 860MH                                | B-1            |

| B.2                 | 860MH-Related Questions                                            |                |

| B.3                 | MH360-Related Questions                                            |                |

|                     | Appendix C Connecting ISDN Multiple S/T or U Interfaces to QUICC32 |                |

| C.1                 | The QMC Protocol                                                   | C-1            |

| C.2                 | Control and Status Information                                     |                |

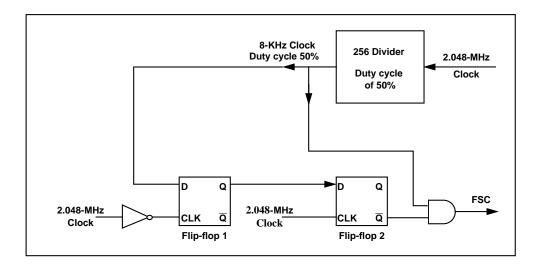

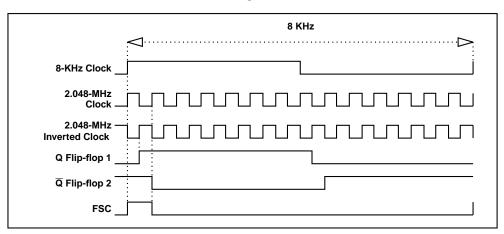

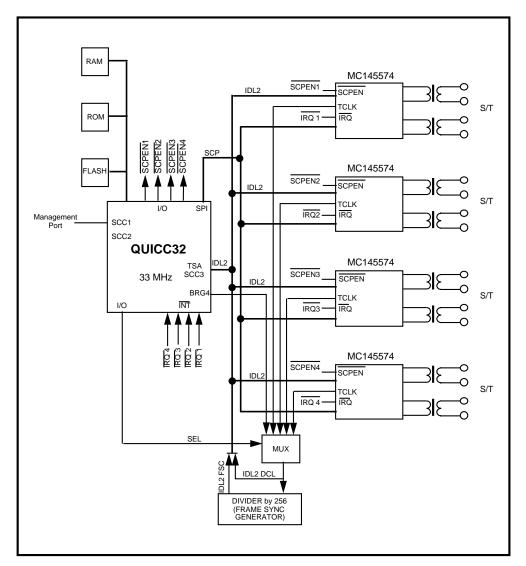

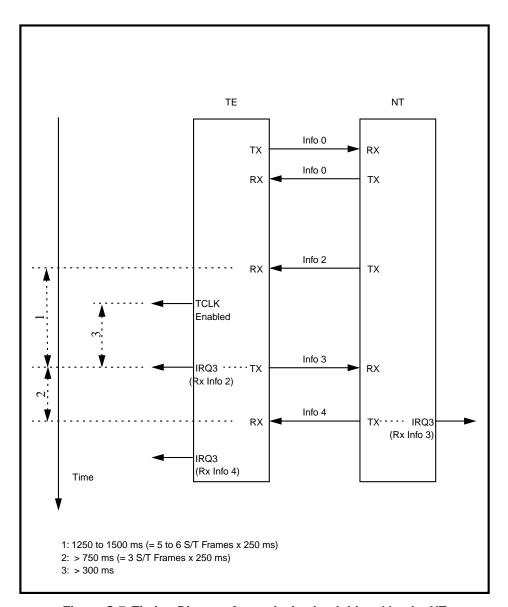

| C.3                 | Data Clock (DCL) and Frame Sync (FSC) Generation                   |                |

| C.3.1               | MC145574 S/T Interface                                             |                |

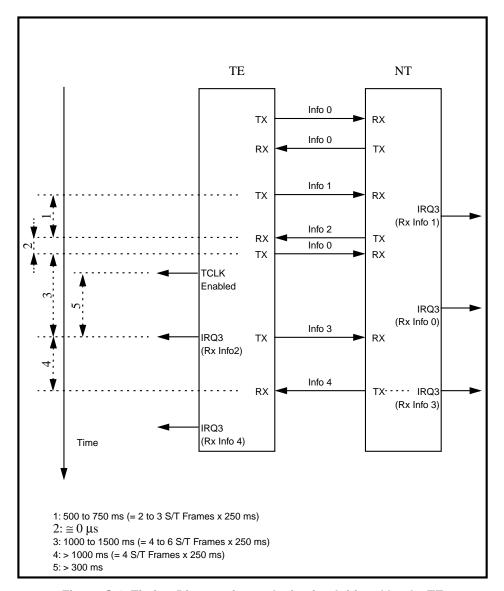

| C.3.1.1             | Activation Procedure                                               | C-8            |

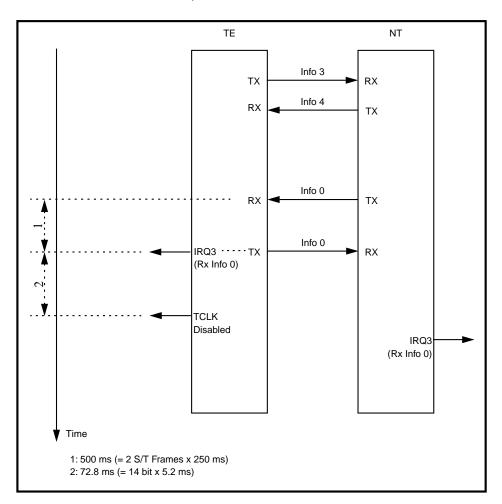

| C.3.1.2             | Deactivation Procedure                                             |                |

| C.3.2               | MC145572 U Interface                                               |                |

| C.3.2.1             | Activation Procedure                                               |                |

| C.3.2.2             | Deactivation Procedure                                             |                |

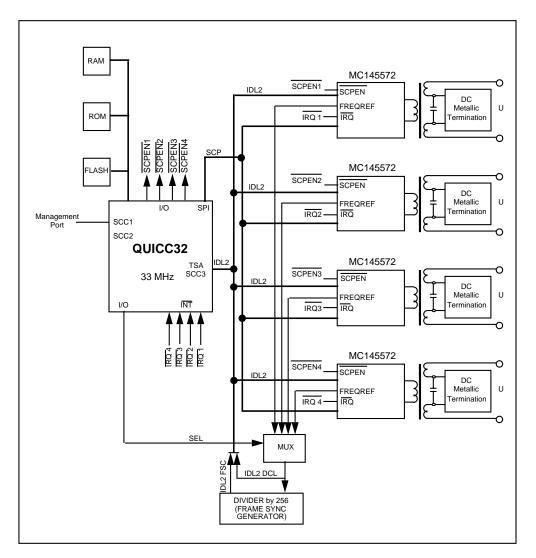

| C.3.3               | System Configuration                                               |                |

| C.3.3.1             | S/T-Interface Configuration                                        |                |

| C.3.3.2             | U-Interface Configuration                                          |                |

| C.3.3.3             | QUICC32 Configuration                                              |                |

# **ILLUSTRATIONS**

| Figur<br>Numl |                                                                                                 | Page<br>Number |

|---------------|-------------------------------------------------------------------------------------------------|----------------|

|               |                                                                                                 | 1.0            |

| 1-1           | QMC Channel Addressing Capability                                                               | 1-2            |

| 1-2           | Ethernet-to-BRI Bridge Using MC68EN360                                                          |                |

| 1-3           | Internal Routing for Ethernet-to-BRI Bridge Using MC68EN360                                     |                |

| 1-4           | Ethernet-to-BRI Bridge Using MC68MH360                                                          | 1-8            |

| 1-5           | Internal Routing for Ethernet-to-BRI Bridge Using MC68MH360                                     |                |

| 1-6<br>1-7    | Ethernet-to-PRI Bridge Using MPC860MH  Internal Routing for Ethernet-to-PRI Bridge Using MPC860 | 1 0            |

| 1-7           | Frame Structures for E1/CEPT and T1 TDM Interfaces                                              |                |

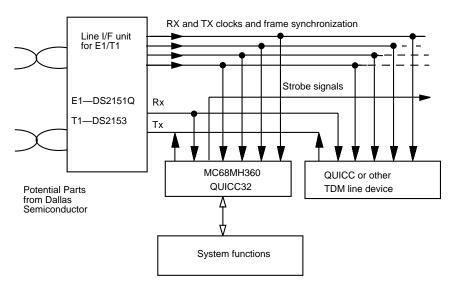

| 1-8           | MC68MH360 Connection to a TDM Bus                                                               |                |

| 2-1           | MC68MH360 and MPC860MH Internal Memory Structures                                               |                |

| 2-1           | QMC Memory Structure                                                                            |                |

| 2-3           | Time Slot Assignment Table                                                                      |                |

| 2-4           | Time Slot Assignment Table for 64-Channel Common Rx and Tx Mapping                              |                |

| 2-5           | Rx Time Slot Assignment Table for 32 Channels over Two SCCs                                     |                |

| 2-6           | Time Slot Assignment Tables for 64 Channels over 2 SCCs                                         |                |

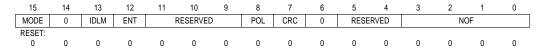

| 2-7           | CHAMR—Channel Mode Register (HDLC)                                                              |                |

| 2-8           | TSTATE—Tx Internal State (HDLC)                                                                 |                |

| 2-9           | INTMSK and Interrupt Table Entry (HDLC)                                                         |                |

| 2-10          | RSTATE—Rx Internal State (HDLC)                                                                 |                |

| 2-11          | CHAMR—Channel Mode Register (Transparent Mode)                                                  |                |

| 2-12          | TSTATE—Tx Internal State (Transparent Mode)                                                     |                |

| 2-13          | INTMSK and Interrupt Table Entry (Transparent Mode)                                             |                |

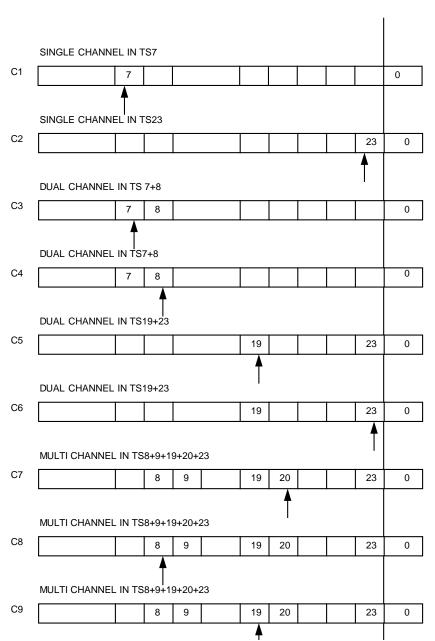

| 2-14          | Examples of Different T1 Time Slot Allocation                                                   |                |

| 2-15          | RSTATE—Rx Internal State (Transparent Mode)                                                     | 2-28           |

| 3-1           | Command Register (CR)                                                                           | 3-1            |

| 4-1           | Circular Interrupt Table in External Memory                                                     | 4-1            |

| 4-2           | SCC Event Register                                                                              | 4-4            |

| 4-3           | SCCM Register                                                                                   | 4-5            |

| 4-4           | Interrupt Table Entry                                                                           |                |

| 4-5           | Channel Interrupt Flow                                                                          |                |

| 5-1           | Receive Buffer Descriptor (RxBD)                                                                |                |

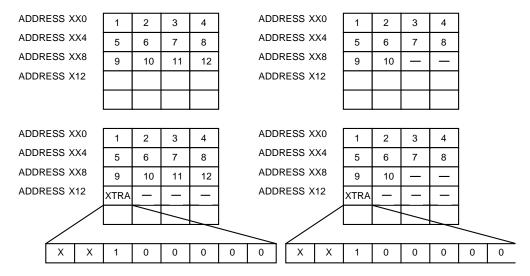

| 5-2           | Nonoctet Alignment Data                                                                         |                |

| 5-3           | Transmit Buffer Descriptor (TxBD)                                                               |                |

| 5-4           | Relation between PAD and NOF                                                                    |                |

| 5-5           | MC68MH360 Internal Memory                                                                       |                |

| 5-6           | SCC2 Parameter RAM Overlap Example                                                              | 5-8            |

Illustrations

# **ILLUSTRATIONS**

| Figure<br>Numb | ΙΙΤΙΔ                                                              | Page<br>Number |

|----------------|--------------------------------------------------------------------|----------------|

| 5-7            | MC68MH360 SCC1 Parameter RAM Usage                                 | 5-10           |

| 5-8            | MC68MH360 SCC2 Parameter RAM Usage                                 |                |

| 5-9            | MC68MH360 SCC3 Parameter RAM Usage                                 |                |

| 5-10           | MC68MH360 SCC4 Parameter RAM Usage                                 |                |

| 5-11           | MPC860MH Internal Memory                                           | 5-14           |

| 5-12           | MPC860MH SCC1 Parameter RAM Usage                                  | 5-16           |

| 5-13           | MPC860MH SCC2 Parameter RAM Usage                                  |                |

| 5-14           | MPC860MH SCC3 Parameter RAM Usage                                  | 5-18           |

| 5-15           | MPC860MH SCC4 Parameter RAM Usage                                  |                |

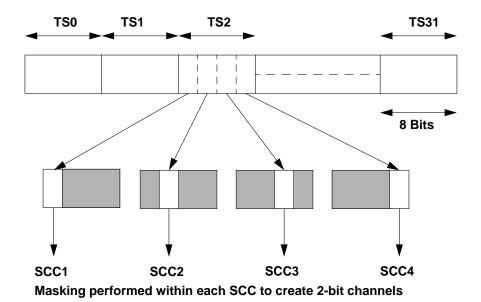

| 9-1            | Two-Bit Subchannel Implementation without MSC Microcode            | 9-2            |

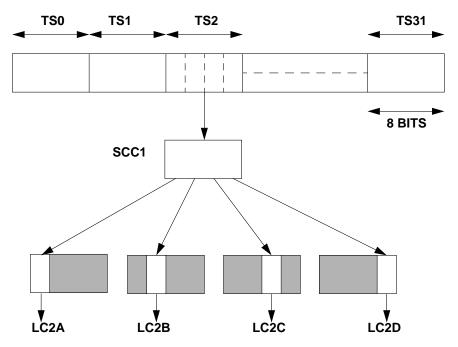

| 9-2            | Two-Bit Subchannel Implementation with MSC Microcode               | 9-3            |

| 9-3            | Time Slot Assignment Table Showing MSC Configuration               | 9-4            |

| 9-4            | Example for Eight 2-Bit Subchannels.                               |                |

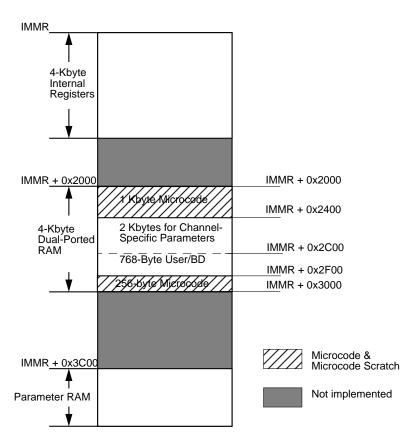

| 9-5            | MPC860MH Internal Memory Map with MSC Microcode Enabled            | 9-7            |

| A-1            | Time Slot Assignment Table                                         | A-1            |

| A-2            | Time Slot Assignment Table for 64-Channel Common Rx and Tx Mapping | A-2            |

| A-3            | CHAMR—Channel Mode Register (HDLC)                                 |                |

| A-4            | Interrupt Table Entry and INTMSK (HDLC)                            |                |

| A-5            | TSTATE (HDLC)                                                      | A-3            |

| A-6            | RSTATE (HDLC)                                                      | A-3            |

| A-7            | CHAMR—Channel Mode Register (Transparent Mode)                     | A-4            |

| A-8            | INTMSK and Interrupt Table Entry (Transparent Mode)                | A-4            |

| A-9            | TSTATE (Transparent Mode)                                          | A-4            |

| A-10           | RSTATE (Transparent Mode)                                          | A-4            |

| A-11           | Command Register                                                   | A-4            |

| A-12           | SCC Event (SCCE) Register                                          | A-5            |

| A-13           | SCCM Register                                                      | A-5            |

| A-14           | Receive Buffer Descriptor (RxBD)                                   | A-5            |

| A-15           | Transmit Buffer Descriptor (TxBD)                                  | A-5            |

| C-1            | IDL2 Bus Structure for a Connection to the QMC Bus                 |                |

| C-2            | IDL and SCP Connections between the QUICC32 and the S/T Interface  |                |

| C-3            | IDL and SCP Connections between the QUICC32 and the U Interface    | C-4            |

| C-4            | FSC Generation from a 2.048-MHz Clock—Block Diagram                | C-6            |

| C-5            | FSC Generation from a 2.048-MHz Clock—Timing                       | C-6            |

| C-6            | Connection between Four S/T Interfaces and the QUICC32             |                |

| C-7            | Timing Diagram for an Activation Initiated by the NT               |                |

| C-8            | Timing Diagram for an Activation Initiated by the TE               | C-10           |

| C-9            | Timing Diagram for a Deactivation (Always Initiated by the NT)     | C-11           |

| C-10           | Connection between Four U Interfaces and the QUICC32               | C-13           |

# **TABLES**

| Number Title |                                                              | Page<br>Number |

|--------------|--------------------------------------------------------------|----------------|

| i            | Acronyms and Abbreviated Terms                               | w:::           |

| 2-1          | Global Multichannel Parameters                               |                |

| 2-1          | Time Slot Assignment Table Entry Fields for Receive Section  |                |

| 2-3          | Time Slot Assignment Table Entry Fields for Transmit Section |                |

| 2-4          | Channel-Specific HDLC Parameters                             |                |

| 2-5          | CHAMR Field Descriptions (HDLC)                              |                |

| 2-6          | TSTATE Field Descriptions for MH360 (HDLC)                   |                |

| 2-7          | TSTATE Field Descriptions for 860MH (HDLC)                   |                |

| 2-8          | RSTATE Field Descriptions for MH360 (HDLC)                   |                |

| 2-9          | RSTATE Field Descriptions for 860MH (HDLC)                   |                |

| 2-10         | Channel-Specific Transparent Parameters                      |                |

| 2-11         | CHAMR Bit Settings (Transparent Mode)                        |                |

| 2-12         | TSTATE Field Descriptions for MH360 (Transparent Mode)       |                |

| 2-13         | TSTATE Field Descriptions for 860MH (Transparent Mode)       |                |

| 2-14         | RSTATE Field Descriptions for MH360 (Transparent Mode)       | 2-28           |

| 2-15         | RSTATE Field Descriptions for 860MH (Transparent Mode)       | 2-29           |

| 4-1          | SCC Event Register Field Descriptions                        | 4-4            |

| 4-2          | Interrupt Table Entry Field Descriptions                     | 4-5            |

| 5-1          | Receive Buffer Descriptor (RxBD) Field Descriptions          |                |

| 5-2          | Transmit Buffer Descriptor (TxBD) Field Descriptions         |                |

| 5-3          | MC68360 Functions Available                                  |                |

| 5-4          | MPC860MH Functions Available                                 |                |

| 6-1          | Transmit Buffer Descriptor Field Descriptions                |                |

| 6-2          | SICR Bit Settings                                            |                |

| 6-3          | SIGMR Bit Settings                                           |                |

| 6-4          | GSMR_H Bit Settings                                          |                |

| 6-5          | GSMR_L Bit Settings                                          |                |

| 6-6          | CHAMR Bit Settings                                           |                |

| 6-7          | Pointer Registers                                            |                |

| 6-8          | State Registers                                              |                |

| 8-1          | Common QMC Configurations                                    |                |

| 8-2          | CPM Performance Table                                        |                |

| 8-3          | QMC Actions in Tx Buffer Switch                              |                |

| 8-4          | Simulated Latencies                                          | 8-6            |

Tables

#### **TABLES**

| Tabl<br>Nun | ole Title<br>mber                                          | Page<br>Number |

|-------------|------------------------------------------------------------|----------------|

| 9-1         | Time Slot Assignment Table Entry Fields for Receive (MSC)  | 9-4            |

| 9-2         | Time Slot Assignment Table Entry Fields for Transmit (MSC) | 9-5            |

| B-1         | CPU Performance                                            | B-1            |

| C-1         | TCLK Frequencies Selected by BR13[5] and BR7[2]            | C-5            |

# **About This Book**

This document is a supplement to the *MC68360 Quad Integrated Communications Controller User's Manual* (MC68360UM/AD) and the *MPC860 PowerQUICC User's Manual* (MPC860UM/AD). It replaces the MC68MH360 Reference Manual (MC68MH360RM/AD).

To locate any published errata or updates for this document, refer to the website at http://www.mot.com/netcomm.

#### **Audience**

This manual is intended for system software and hardware developers. It is assumed that the reader understands basic concepts of time-division-multiplexed processors and how the MPC860 CPM operates.

#### **Organization**

Following is a summary and a brief description of the major sections of this manual:

- Chapter 1, "Overview," gives an introduction to the QMC (QUICC multichannel controller) protocol including some example applications.

- Chapter 2, "QMC Memory Organization," describes the operation specific to the QMC protocol.

- Chapter 3, "QMC Commands," discusses the transmit and receive commands.

- Chapter 4, "QMC Exceptions," describes QMC interrupt handling.

- Chapter 5, "Buffer Descriptors," describes the contents of the receive and transmit buffer descriptors for the QMC protocol and discusses the placement of QMC and non-QMC buffer descriptors in internal and external memory.

- Chapter 6, "QMC Initialization," discusses the essential steps to initialize QMC after a hard reset.

- Chapter 7, "Features Deleted in MC68MH360," lists the features deleted from the MH360.

- Chapter 8, "Performance," provides a performance table for common configurations supported by the 860MH and/or MH360; covers general guidelines and examples for determining the serial bit rate and CPM loading on a given system; and discusses system bus utilization and arbitration.

About This Book

- Chapter 9, "Multi-Subchannel (MSC) Microcode," provides the MSC microcode features and operation, and discusses how to program the MSC protocol.

- Appendix A, "68360 Bit Numbering," shows the bit numbering used for the 68360.

- Appendix B, "Frequently-Asked Questions," provides a list of common questions and solutions for the MH360 and 860MH.

- Appendix C, "Connecting S/T or U Interfaces to QUICC32," shows how multiple MC145574 (S/T interface) or MC145572 (U interface) can be connected to a QUICC32. It describes the level-1 connections and explains the data flow through the devices.

- This manual also includes an index.

#### **Additional Reading**

This section provides a brief list of additional reading that supplements the information in this manual.

The following materials are available from the Motorola Literature Distribution Centers listed on the back cover of this manual; the document order numbers are included in parentheses for ease in ordering:

- MPC860 PowerQUICC User's Manual (MPC860UM/AD)

- MC68360 Quad Integrated Communications Controller User's Manual, Rev. 1 (M68360UM/AD)

- M68000 Family Programmer's Reference Manual, Rev. 1 (M68000PM/AD)

#### Conventions

This document uses the following notational conventions:

ACTIVE\_HIGH Names for signals that are active high are shown in uppercase text

without an overbar. Active-high signals are referred to as asserted

when they are high and negated when they are low.

ACTIVE LOW A bar over a signal name indicates that the signal is active low.

Active-low signals are referred to as asserted (active) when they are

low and negated when they are high.

0x0F Hexadecimal numbers

0b0011 Binary numbers

REG[FIELD] Abbreviations or acronyms for registers are shown in uppercase text.

Specific bit fields or ranges are shown in brackets.

Bold font (field name)Entries in boldface must be initialized by the user.

# **Acronyms and Abbreviations**

Table i contains acronyms and abbreviations that are used in this document.

**Table i. Acronyms and Abbreviated Terms**

| Term             | Meaning                                      |

|------------------|----------------------------------------------|

| BD               | Buffer descriptor                            |

| bps              | Bits per second                              |

| BRI              | Basic rate interface                         |

| BRG              | Baud rate generator                          |

| СРМ              | Communications processor module              |

| CR               | Command register                             |

| DCL              | Data clock signal                            |

| FSC              | Frame sync signal                            |

| GSM              | Global system for mobile communications      |

| GOV              | Global receiver overrun (global error)       |

| GUN              | Global transmitting underrun (global error)  |

| HDLC             | High-level data link control                 |

| I <sup>2</sup> C | Interprocessor-integrated controller channel |

| MSC              | Multi-subchannel microcode                   |

| NMSI             | Nonmultiplexed serial interface              |

| QMC              | QUICC multichannel controller                |

| QUICC            | QUad integrated communication controller     |

| RCCR             | RISC controller configuration register       |

| RxBD             | Receive buffer descriptor                    |

| SCC              | Serial communication controller              |

| SCCE             | SCC event register                           |

| SI               | Serial interface routing                     |

| SS-7             | Signaling system 7                           |

| TDM              | Time-division multiplexing                   |

| TSA              | Time slot assigner                           |

| TSO              | Time slot zero                               |

| TxBD             | Transmit buffer descriptor                   |

About This Book

# Chapter 1 Overview

This chapter gives an overview of the QMC protocol including some example applications.

# 1.1 The QMC (QUICC Multichannel Controller)

The QMC protocol emulates up to 64 logical channels within one SCC (serial communication controller) using the same time-division-multiplexed (TDM) physical interface. This multichannel protocol is implemented using the CPM ROM space and additional hardware; it is not a downloadable microcode.

The standard QUICC family members (MC68360<sup>1</sup>, MPC860<sup>2</sup>, etc.) work in TDM applications but can only support one logical channel per SCC. The parts currently supporting the QMC protocol are a superset to the following devices:

- MC68MH360 is a superset of the MC68EN360<sup>3</sup>

- MPC860MH is a superset of the MPC860EN

- MPC860DH is a superset of the MPC860DE

The QMC parts are pin-compatible with their respective family members. With minor adjustments, they can be used in identical applications such as primary rate ISDN support.

#### 1.2 Introduction

Ideal for E1/T1 applications, the QMC protocol can multiplex any 64-channel combination of subgroups to one TDM interface.

Each of the channels can be separately programmed either to perform HDLC formatting/deformatting or to act as a transparent channel.

Both of the SI serial interfaces (for example, TDM<sub>a</sub> or TDM<sub>b</sub>) can be dedicated to the QMC protocol. The SI transfers the whole frame to an SCC<sup>4</sup>. Using the CPM RISC, the SCC

<sup>&</sup>lt;sup>1</sup>MC68360 is trademarked as the QUICC.

<sup>&</sup>lt;sup>2</sup>MPC860 is trademarked as the PowerQUICC.

<sup>&</sup>lt;sup>3</sup>On the MC68MH360, protocol support for Centronics and BISYNC have been removed to create space for the QMC microcode.

<sup>&</sup>lt;sup>4</sup>This is the normal operating mode; however, it is possible to split the TDM stream over several SCCs.

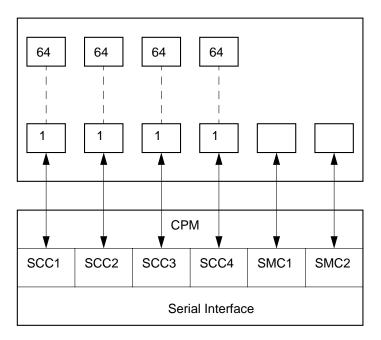

works transparently, not participating in any QMC protocol functions. The SCC only performs the parallel-to-serial conversion and adds elasticity through its FIFO memory. The CPM, with its special enhanced microcode and additional dedicated hardware for framing and masking support, does all of the protocol processing for each of the 64 channels. Note that it is executed without intervention from the on-board CPU. Figure 1-1 illustrates the QMC's multichannel capability. Note that each SCC can support up to 64 channels from the TDM; however, there are limitations depending on the device used. This is summarized in Section 1.3, "QMC Features."

Each SCC can work in QMC mode, either alone or together in any combination. The larger FIFO of SCC1 yields the best performance and is therefore recommended for QMC operation. One TDM connection can be routed to one or more SCCs operating in QMC mode, with each SCC operating on different time slots. It is possible to use both TDMs for QMC with combined routing to one SCC or to separate SCCs. When using two TDMs connected to one SCC, restrictions such as using common clocks and sync inputs apply; it is also important to avoid collisions by separating the serial interface (SI) routing.

Figure 1-1. QMC Channel Addressing Capability

#### 1.3 QMC Features

- MC68MH360-specific features

- Up to 32 independent communication channels

- Arbitrary mapping of any of 0–31 channels to any of 0–31 TDM time slot

- Can support arbitrary mapping of any of 0–31 channels to any of 0–63 TDM time slots in case of common Rx and Tx mapping

- Up to three additional HDLC 64-Kbps channels at 25-MHz system clock

- Simultaneous Ethernet support at 33-MHz system clock

- Up to 64 DMA channels with linear buffer array

- MPC860MH/DH-specific features

- Up to 64 independent communication channels

- Arbitrary mapping of any of 0–63 channels to any of 0–63 TDM time slots

- Supports arbitrary mapping of any of 0–63 channels to any of 0–127 TDM time slots in case of common Rx and Tx mapping

- Two simultaneous 32-channel E1 links at 50-MHz system clock

- Up to 128 DMA channels with linear buffer array

- Common features

- Independent mapping for receive/transmit

- Supports either transparent or HDLC protocols for each channel

- Interrupt circular buffer with programmable size and overflow identification

- Global loop mode

- Individual channel loop mode through the SI

- Programmable frame length (via SI)

- · Serial interface

- Serial-multiplexed (full duplex) input/output 2048-, 1544-, or 1536-Kbps PCM highways

- Compatible with T1/DS1 24-channel and CEPT E1 32-channel PCM highway, ISDN basic rate, ISDN primary rate and user-defined

- Subchanneling on each time slot

- Allows independent transmit and receive routing, frame syncs, and clocking

- Concatenation of any, not necessarily consecutive, time slots to channels independently for receive/transmit

- Supports H0, H11, and H12 ISDN channels

- Allows dynamic allocation of channels

Chapter 1. Overview

- · System interface

- On-chip bus arbitration for serial DMAs with no performance penalty

- Efficient bus usage (no bus usage for nonactive channels and active channels that have nothing to transmit)

- Efficient control of the interrupts to the CPU

- Supports external buffer descriptors table

- Uses on-chip enlarged dual-ported RAM for parameter storage

# 1.4 The Time Slot Assigner and the QMC

The time slot assigner (TSA) in the MH devices is no different from the other versions. This section discusses the new possibilities when using the TSA in combination with the QMC.

The QMC protocol can be executed in nonmultiplexed serial interface (NMSI) mode, but the usual operating mode takes advantage of the programmable time slot assigner,.

A frame synchronization pulse alerts the time slot assigner to start counting clock pulses. The user programs what bits are routed to the different internal serial channels. The TSA is an intelligent multiplexer that restarts its sequence on every frame synchronization pulse.

External strobe signals allow other devices that do not have built-in time slot assigner functions to participate in the TDM interface. This is very useful when interfacing to the MC68302 or other telecommunication devices like codecs.

The time slot assigner is not limited to standard TDM lines. It is a flexible, programmable device that allows the user to route any combination of bits and bytes to any channel. For example, the user can transmit 3 bits from SCC2, skip 12 bytes, and then transmit another 17 bits from SCC1. This routing must be programmed into the TSA memory. The complexity of the routing is limited only by the number of program entries in the TSA.

Ideal for TDM bridging applications, the MC68MH360 and MPC860MH have two independent time slot assigners and physical interfaces. A complete set of independent receive and transmit clock signals, as well as independent synchronization signals, are available for each TDM.

# 1.5 The Serial Interface (SI)

Functions such as frame synchronization, loopback, echo, and inverted signals are performed in the serial interface and cannot be achieved in NMSI mode. It is recommended to use the serial interface even if only one SCC is used for the TDM bus.

#### 1.5.1 Synchronization

Independent receive and transmit clocks and frame synchronization signals control the data transfer. In NMSI operation, synchronization occurs only once to initiate a transfer using the CD (receive) and CTS (transmit) signals in pulse mode. If any noise corrupts either signal, the QMC will be out of synchronization until the whole protocol is restarted.

In contrast, the more robust SI performs a synchronization on each frame, limiting the damage from noise error on the clock or synchronization lines. Noisy channels can be restarted individually without interrupting other channels. For more details about possible errors in the TDM interface, see Section 1.8, "SI RAM Errors."

#### 1.5.2 Loopback Mode

The loopback from a transmitter to a receiver is implemented on a per channel basis for every logical channel. A common transmit and receive clock as well as a common frame synchronization pulse must be provided for loopback mode to work. The loopback is done on a fixed time slot, meaning that if one logical channel transmits on time slot 17, the loopback occurs through time slot 17 also, whether it is same logical channel or not that receives the incoming data. The reason for this restriction is that no buffering is performed after a channel is processed by the transmitter, or before it reaches the receiver.

Previously reserved, bit 15 of each entry in the SI-RAM is now the loopback bit controlling the loopback for the corresponding time slot. It is important to have each individual time slot as an entry in the SI-RAM for proper loopback on each individual channel.

#### 1.5.3 Echo Mode

The SI can be programmed to echo incoming data. In this mode, the complete TDM link is retransmitted from the incoming L1RXDx to the L1TXDx pin on a bit-by-bit basis. The receiver section of the selected SCC can operate normally and also receive the incoming bit stream. This is also known as global echo mode on the whole link. Individual time slot echo is not possible with QMC without software intervention.

#### 1.5.4 Inverted Signals

For each SCC, the DPLL can be used to invert the bitstream of the transmitter before the signal reaches the pin. This is not a bit-order inversion, but a logical level inversion. The DPLL can also invert the incoming data before it is forwarded to the receiver section. A logical inversion on a per channel basis is not possible in the QMC without external hardware. To invert a specific channel, the SI can be programmed to send a strobe signal at the channel's corresponding time slot, assuming the SCC is operating in QMC mode. This strobe can then be connected to an external XOR gate to perform the inversion.

# 1.6 QMC Serial Routing and Example Applications

The QMC protocol provides multiple logical channels from a single SCC. The SCC channel dedicated to operate the QMC protocol should have all the relevant bits or time slots routed to it. Individual logical channels are selected by a combination of signals routed through the TDM and tables within the QMC protocol. Contrasting a non-QMC example application with QMC implementations highlights benefits of the multichannel protocol.

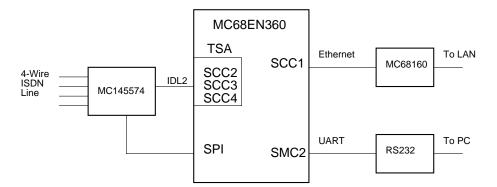

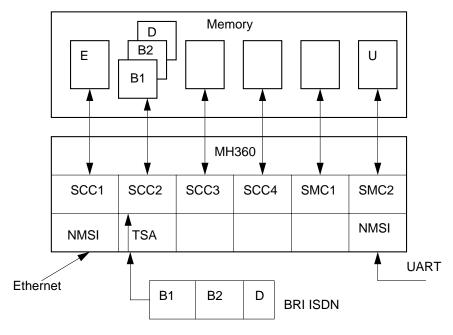

Figure 1-2 shows an Ethernet-to-BRI bridge using an MC68EN360, a non-QMC device. The configuration shows the Ethernet routed via an NMSI interface to SCC1. The ISDN BRI is routed via the TSA over an IDL2<sup>1</sup> interface to SCC2–SCC4 for the 2 B + D (B1, B2, and D) channels. The first byte of the frame (B1) is routed to SCC2, the second byte (B2) to SCC3, and then the next two bits (the D channel) to SCC4. In this example, SMC2 is used to connect to a PC over RS232. The internal routing is illustrated in Figure 1-3. Note that three SCCs are required to implement the ISDN BRI. This uses all the MC68EN360's serial channels without efficient use of the CPM bandwidth.

Figure 1-2. Ethernet-to-BRI Bridge Using MC68EN360

<sup>&</sup>lt;sup>1</sup>The IDL2 interface is a full duplex ISDN interface used to interface to a physical layer device, such as the Motorola ISDN S/T transceiver MC145474.

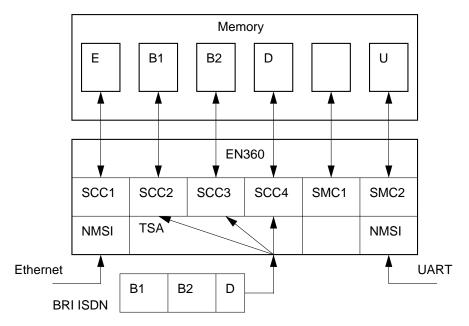

Figure 1-3. Internal Routing for Ethernet-to-BRI Bridge Using MC68EN360

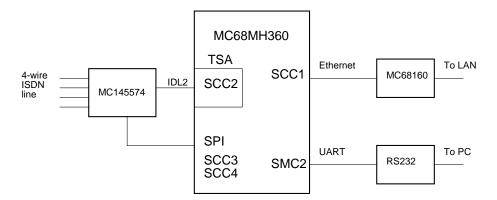

The following example shows how an MC68MH360 can implement the BRI using only one SCC, leaving SCC3 and SCC4 available to run other protocols such as frame relay over HDLC and another Ethernet link, on SCC1, to the LAN. The QMC protocol allows all three channels B1, B2, and D to be routed to SCC2 using the TSA. The first byte (B1) is routed to logical channel 1, the second byte (B2) to logical channel 2, and the third byte to logical channel 3, of which only the first 2 bits represent the D channel as illustrated in Figure 1-4 and Figure 1-5. This routing is defined in the QMC time slot assignment tables. The first advantage of the QMC protocol is that it releases SCCs to run other protocols. The second advantage is highlighted in the next example.

Figure 1-4. Ethernet-to-BRI Bridge Using MC68MH360

Figure 1-5. Internal Routing for Ethernet-to-BRI Bridge Using MC68MH360

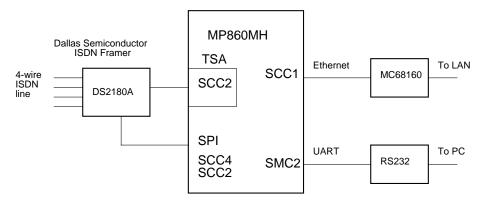

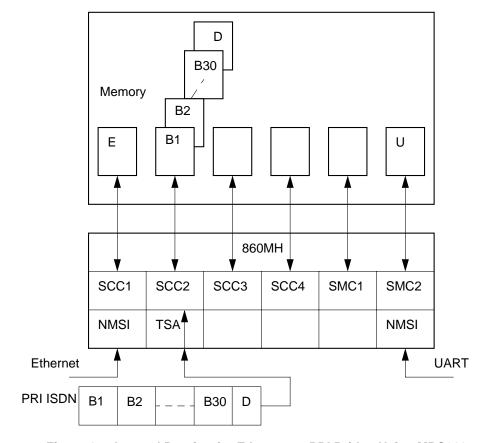

Figure 1-6 and Figure 1-7 show how to build a PRI ISDN-to-Ethernet bridge using an MPC860MH. SCC1 is used for the Ethernet channel. SCC2 is configured for QMC mode in which each of the 30 B channels and the D channel are routed to separate logical channels. The true advantage of the QMC protocol is the ability to route multiple channels to a single SCC.

Figure 1-6. Ethernet-to-PRI Bridge Using MPC860MH

Figure 1-7. Internal Routing for Ethernet-to-PRI Bridge Using MPC860

Chapter 1. Overview

# 1.7 SCC Changes on the Fly

Changes can be made on the fly in the QMC routing tables, but changes made in the SI RAM require the link to be disconnected. If the connection is maintained during changes, synchronization and routing errors are likely to happen in the current frame. A workaround uses a shadow RAM routing table. The shadow table can hold alternative routing information to be switched in at the appropriate time slot boundary. The drawback to this method is that the number of entries in the SI RAM is reduced by half. But since the routing tables in the QMC protocol are being changed anyway, the recommended solution is to have all relevant time slots routed to the SCC.

The SI RAM also gives the user the capability to multiplex other channels to and from a TDM if not all time slots are used by the QMC. A third option is to have several external devices multiplexed. Use the open collector mode if several QUICCs or PowerQUICCs are connected together for subchanneling applications.

#### 1.8 SI RAM Errors

The following three types of errors are identified:

- Data bit error

- Clock pulse error

- Synchronization pulse error

Errors in frame-based protocols are easy to detect by the protocol controller. An error in an HDLC channel is detected at the end of a frame when a buffer is closed and all status bits are reported in the buffer descriptor (BD). The error type for bit errors is normally CRC errors. For errors occurring in the SI (noise on clock or synchronization pulses), the error may also be of type frame-length-violation or non-octet-aligned. See Chapter 5, "Buffer Descriptors," for more information. This section covers the type of errors reported through the buffer descriptors. For transparent channels, the error detection mechanism is left to the user in higher-level software. Most transparent channels, such as voice carriers, are tolerant of errors. Frame-based channels, on the other hand, require error detection since they often rely on critical control messages.

The number of clocks that occur between sync pulses is given in the SI RAM programming. The clock-counting state machine expects a new sync pulse after the end of each frame. The following paragraphs discuss the different error cases and describe the counter state and the frame delay before synchronization is resumed.

A clock pulse error occurs if other than exactly one clock pulse is detected by the SI RAM in a given frame. In this error case, since the SI RAM bases its routing on counting clock pulses, the now corrupted signal routing affects all channels. The SI RAM expects another sync pulse when it reaches the last entry of the frame.

If a clock pulse is missing in a given frame N, the counter will fail to reach its end state before the next sync pulse (N+1) arrives, causing that sync pulse to be ignored. When the counter finally reaches its end state, it waits for the next sync pulse (N+2) before resetting. Correct routing is thus resumed in frame (N+2). In the case of an extra clock pulse, the counter reaches its end state too early and resumes synchronized routing upon detecting the next sync pulse (N+1).

Synchronization pulse errors are similar to clock pulse errors. If the frame pulse comes too late, this is similar to having missed a clock pulse in the last time slot. If the frame pulse is too early, it is similar to having one additional clock pulse.

# 1.9 E1/T1 Frame Description

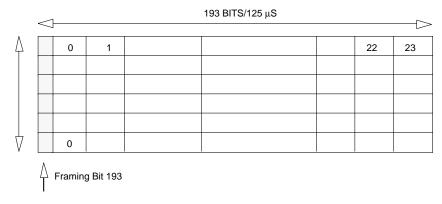

The primary rate ISDN connections offer a cost-effective, high-speed interface. The physical connections in North America offer 24 connections over a T1 interface; in Europe an E1 (or CEPT) connection gives 32 connections of 64 Kbps each with a time-division-multiplexed architecture.

Time-division-multiplexing (TDM) allows several communication channels to share the same physical media. The data stream of each channel is divided into a number of subpackages. Each channel is then assigned a subdivision of the TDM line called a time slot. This time slot is repeated over time in a regular pattern. A concatenation of the channels' subpackages comprises a frame. The frequency of frame repetition depends on the particular communication interface. Two examples—the T1 line used in North America and the E1 interface used in Europe illustrate TDM.

For both E1 and T1, the frames must be repeated at a frequency of 8 KHz, or every  $125\,\mu s$ . In many applications the required channel speed is 64 Kbps. For example, almost all voice channels use 8-KHz sampling with 8-bit resolution. Each channel in a T1 or E1 interface occupies 8 bits per time slot. The T1 interface multiplexes 24 channels, requiring 24 time slots per frame. In addition to the channels' bits, one more bit, for frame signaling and synchronization, is added to create a frame totaling 193 bits. The resulting T1 physical interface is thus 1.544 Mbps (8 KHz \* 193 bits). The E1 frame consists of multiplexing 32 channels resulting in a speed of 2.048 Mbps (8 KHz \* 256 bits). These two frames are illustrated in Figure 1-8.

# Frame Structure for E1 2.048 Mbps 256 Bits/125 μs 0 1 2 30 31 Δ Framing (TS0) Signaling (TS16)

#### FRAME STRUCTURE FOR T1 1.544 MBPS

Figure 1-8. Frame Structures for E1/CEPT and T1 TDM Interfaces

For any station to receive and transmit on a TDM line, it is necessary for it to determine the correct time slot boundary. The service provider or the PTT provides a 4-wire interface with a continuous bit stream coming down the line. The T1 and E1 have information embedded in the data stream that delineates frames. The bit pattern in position 193 in T1 over a period of several frames establishes a synchronization pattern. A station may have the capability to search for this pattern and thus find the correct time for frame synchronization. In a similar way, time slots 0 and 16 are reserved not only for synchronization but also for signaling in the E1 interface.

Depending on its capability, a node can either extract this synchronization information or it can be supported by framer and time slot assigner devices.

A framer device will retrieve the 8-KHz frame synchronization pulses and clock signals for both transmit and receive sections. A time slot assigner will use these signals as inputs to generate pulses or envelope signals for individual bit patterns, i.e., strobe signals for devices without time slot assignment capability such as the MC68302, a first-generation communication processor.

For a backplane type of design without a synchronization to a network, the QMC devices are capable of generating all necessary bus signals from their timers and baud-rate generators. This design type is illustrated for a QUICC32 in Figure 1-9.

Figure 1-9. MC68MH360 Connection to a TDM Bus

# **Chapter 2 QMC Memory Organization**

This section describes the operation specific to the QMC protocol. When not running the QMC protocol, SCCs operate as described in the MC68360 and MPC860 user's manuals.

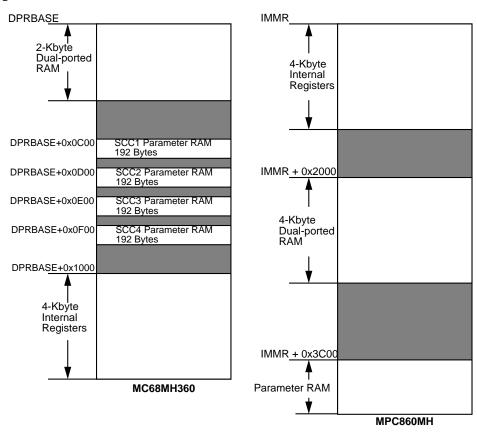

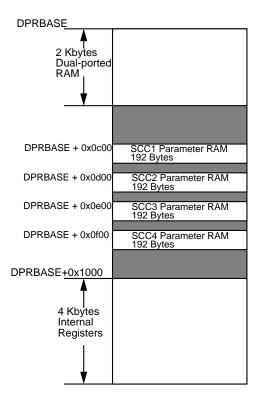

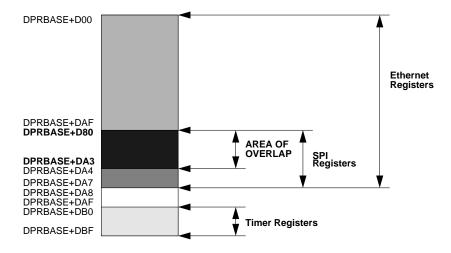

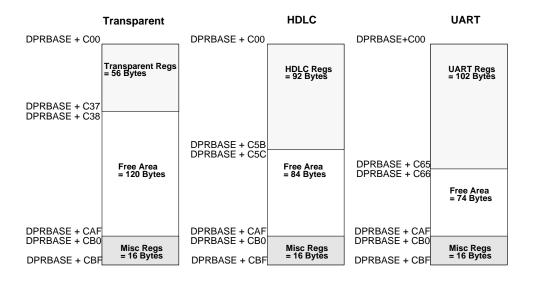

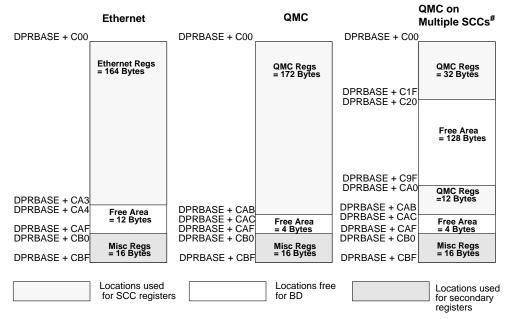

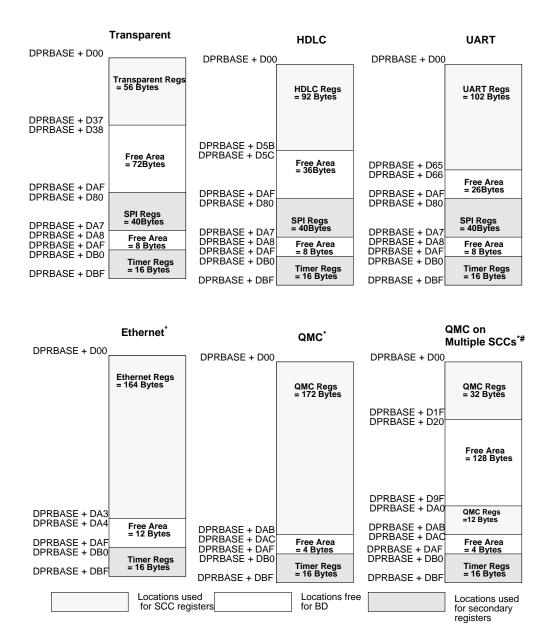

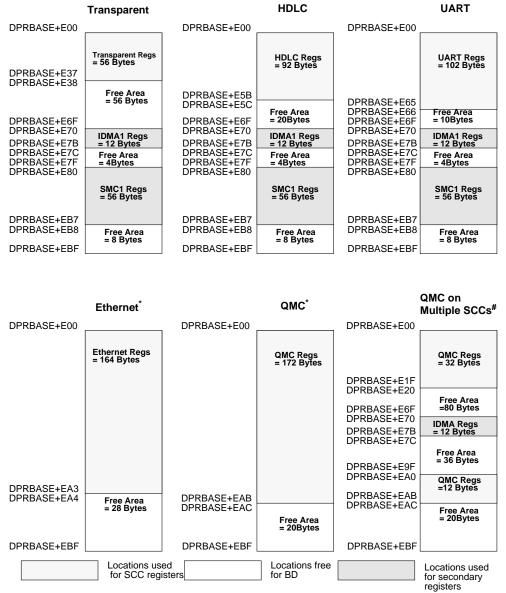

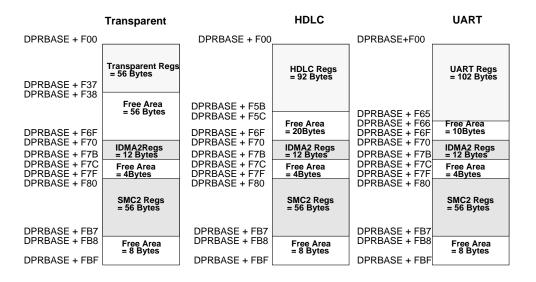

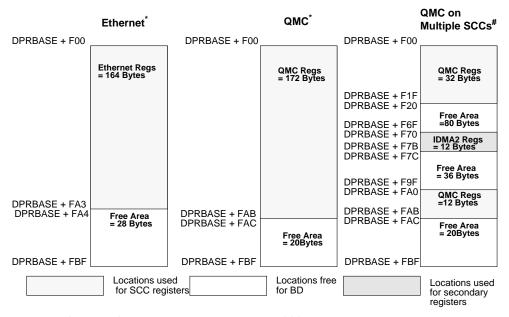

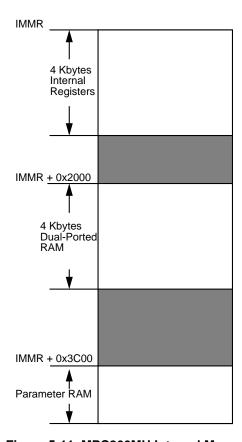

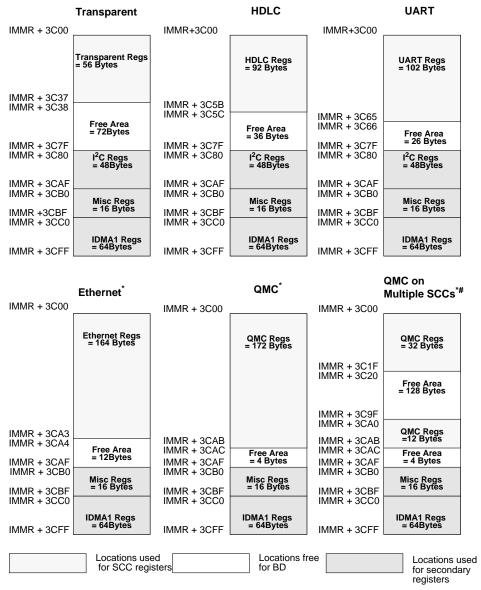

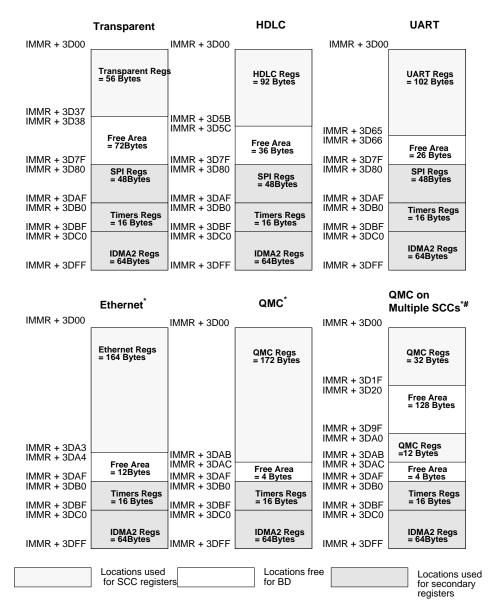

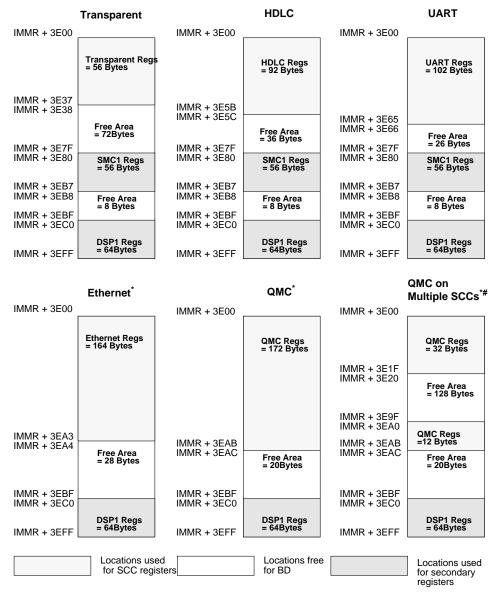

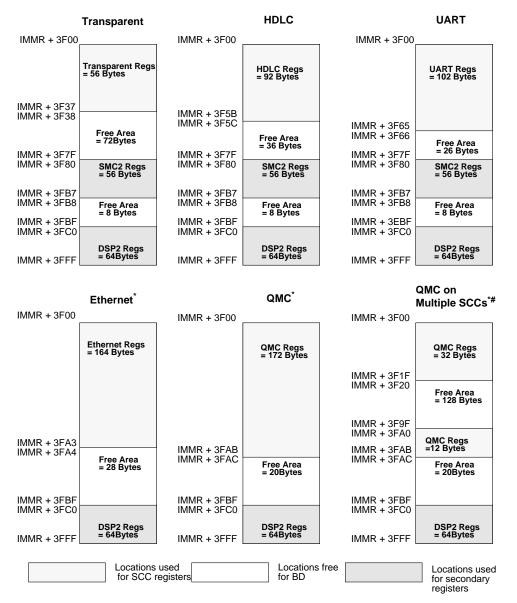

Figure 2-1 shows the dual-ported RAM structure for the MC68MH360 and the MPC860MH. The MC68MH360 and the MPC860MH have similar functionality but are organized in a different manner.

Figure 2-1. MC68MH360 and MPC860MH Internal Memory Structures

Chapter 2. QMC Memory Organization

# 2.1 QMC Memory Structure

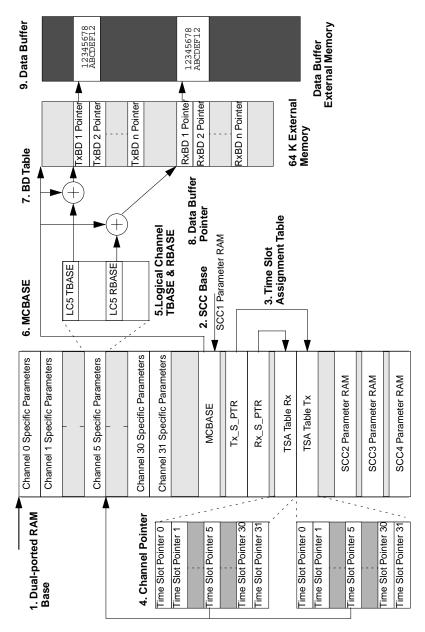

Figure 2-2 shows how data is addressed by the QMC protocol. It discusses addressing the dual-ported RAM to access data within the buffers.

Figure 2-2. QMC Memory Structure

#### 2.1.1 Dual-Ported RAM Base

The MC68MH360's internal memory is mapped into an 8-Kbyte block of memory, and the starting address is dictated by the DPRBASE programmed in the MBAR register. For more detail on the QUICC internal memory structure, see Section 3 of *MC68360 Quad Integrated Communications Controller User's Manual*. The MPC860MH has its internal memory mapped into a 16-Kbyte block of memory. The ISB programmed in the IMMR register determines the starting address of this memory block. For more information on the PowerQUICC internal memory structure, see Section 3 of *MPC860 PowerQUICC User's Manual*. All internal registers are addressed as offsets within the dual-ported RAM; therefore, all pointers are relative to this base address.

#### 2.1.2 SCC Base and Global Multichannel Parameters

The SCC base points to the start of the parameter RAM for each of the SCCs at 256-byte intervals. On the MC68MH360, each SCC has 192 bytes of parameter RAM; each SCC on the MPC860MH has 256 bytes. When the QMC protocol is enabled on an SCC, its parameter RAM is used to store the global multichannel parameters for all the logical channels. This area contains parameters and pointers that are common to all channels.

#### NOTE

As the QMC requires 0xAF bytes of parameter RAM for its global multichannel parameters, this may cause conflict with other CPM functionality. For example, when using the MPC860MH with SCC1 in OMC mode, I <sup>2</sup>C is unavailable.

#### 2.1.3 TSATRx/TSATTx Pointers and Time Slot Assignment Table

The time slot assignment table pointers are within the global multichannel parameters. There are two pointers—Tx\_S\_PTR for transmit and Rx\_S\_PTR for receive. The Rx\_S\_PTR is normally set to SCC Base + 20; this is the normal location of the receive time slot assignment table. The Tx\_S\_PTR is normally set to SCC Base + 60; this is the normal location of the transmit time slot assignment table. However, if the receiver and the transmitter have the same mapping for the logical channels, Tx\_S\_PTR can point to SCC base + 20 so that Rx and Tx have a common time slot assignment table. Note that if a single TDM channel is routed to more than one SCC, they may also use just one time slot assignment table for all SCCs. See Section 2.3, "Multiple SCC Assignment Tables," for more information. The time slot assignment table holds one 32-bit entry for each time slot. It has options for subchanneling, a valid bit, and a logical channel pointer. For 64-channel support there is only space for one table; therefore, common Rx and Tx parameters will need to be used unless one of the TSA tables can be accommodated elsewhere in memory, such as in the parameter RAM area of another SCC. Associated with the Rx/Tx\_S\_PTR are the Rx/TxPTR pointers that are maintained by the CPM and point to the current time slot.

#### 2.1.4 TSATRx/TSATTx Channel Pointers

The channel pointers are 12-bit pointers to the channel-specific parameters in the internal dual-ported RAM. These should not be confused with TSATRx/TSATTx pointers as described in Section 2.1.3, "TSATRx/TSATTx Pointers and Time Slot Assignment Table." The 6 most-significant bits of the address are taken from the time slot assignment table. For the MH360, the most-significant bit must be zero as the addressing range is only 2 Kbytes. The 6 least-significant bits are zero, mapping out a 64-byte area for each of the channel-specific parameters. The channel-specific parameters are common for Rx and Tx. For 32-channel support, 2 Kbytes of dual-ported RAM is required (32 \* 64), and for 64-channel support, 4 Kbytes of dual-ported RAM is required (64 \* 64). In most cases, time slot 0 channel pointer will address the base of dual-ported RAM for logical channel 0, and time slot 1 channel pointer would address the base of dual-ported RAM + 4 for logical channel 1. In Figure 2-2, time slot 5 channel pointer addresses logical channel 5, requiring the channel pointer being set to 0b000101.

#### NOTE

It is possible to concatenate multiple time slots to one logical channel. This is achieved by setting the channel pointers of the grouped time slots to the same logical channel.

#### 2.1.5 Logical Channel TBASE and RBASE

TBASE and RBASE are within the channel-specific parameters. TBASE is the Tx buffer descriptor base address, and RBASE is the Rx buffer descriptor base address. These 16-bit offsets from MCBASE point to individual logical channel's buffer descriptors located within the buffer descriptor table. Note that there are individual TBASE and RBASE values for each logical channel.

#### 2.1.6 MCBASE

MCBASE is located in the global multichannel parameters. Each SCC has a unique MCBASE value pointing to the base of the SCC's buffer descriptor table in external memory. For example, the address of logical channel five's Tx buffer descriptor table is MCBASE + logical channel five TBASE.

#### 2.1.7 Buffer Descriptor Table

A buffer descriptor table for each SCC is located in a 64-Kbyte area of external memory. This block size is determined by the TBASE and RBASE addressing range. The memory segment must be long-word-aligned but can start anywhere in memory. Each SCC has a maximum of 16,384 (64 Kbytes memory  $\div$  4-byte pointers) buffers. For a 32-channel implementation, each logical channel has a maximum of 256 (16,384 / (32 \* 2)) buffers for receive and 256 buffers for transmit. For each logical channel, there is a circular queue with programmable start address and length.

#### 2.1.8 Data Buffer Pointer

As with the standard CPM protocols, the data buffer is addressed by a 32-bit pointer within the buffer descriptor. This addresses the data received or transmitted from external memory.

#### 2.1.9 Data Buffer

The data buffers in external memory can hold up to 64 Kbytes of data as determined by the data length in the buffer descriptor.

#### 2.2 Global Multichannel Parameters

The global multichannel parameters reside in the SCC's parameter RAM page and are common to all logical channels.

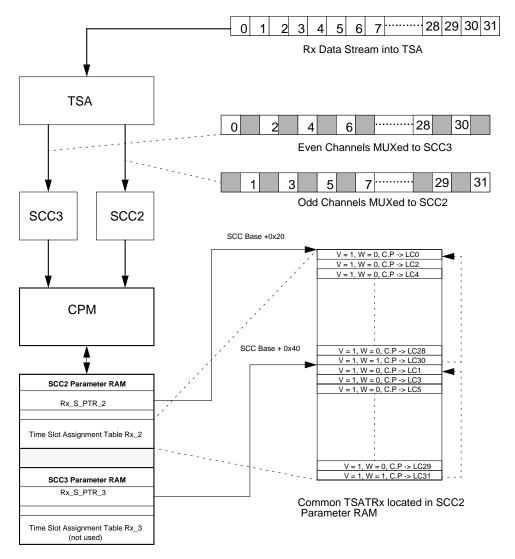

The largest portion of the global area is the time slot assigner tables for the receiver and transmitter section of the SCC. For 32-channel support, there is one table for Tx and one for Rx within the parameter RAM. If the connection is split over multiple SCCs, this table only needs to be present once for multiple SCCs operating in QMC mode. See Section 2.3, "Multiple SCC Assignment Tables," for more information. For 64-channel support there is only space for one table; therefore common Rx and Tx parameters will need to be used unless one of the TSA tables can be accommodated elsewhere in memory, such as in the parameter RAM area of another SCC.

The dual-ported RAM is used for the channel-specific area for all SCCs. It is important that individual time slots are mapped to only one SCC, and that individual logical channels are separated to avoid contention.

Table 2-1 lists the global parameters. Note that the boldfaced parameters must be initialized by the user. See Chapter 6, "QMC Initialization," for more information.

Offset Width to Name Description SCC (Bits) Base **MCBASE** Multichannel base pointer—This host-initialized parameter points to the starting address of the 64-Kbyte buffer descriptor table in external memory. The MCBASE is used with the TBASE and RBASE registers in the channel-specific parameters. **QMCSTATE** Multichannel controller state (initialize to 0x8000)—Internal QMC state machine value used by RISC processor for global state definition.

**Table 2-1. Global Multichannel Parameters**

**Table 2-1. Global Multichannel Parameters (Continued)**

| Offset<br>to<br>SCC<br>Base | Name     | Width<br>(Bits) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------|----------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06                          | MRBLR    | 16              | Maximum receive buffer length—This host-initialized entry defines the maximum number of bytes written to a receive buffer before moving to the next buffer for this channel. This parameter is only valid in HDLC mode.  The buffer area allocated in memory for each buffer is MRBLR + 4. The QMC adds another long word if non-octet-aligned frames are received in HDLC operation. The non-octet information is written only to the last buffer of a frame, but it can happen in any buffer. See Section 5.1, "Receive Buffer Descriptor," for more information.  As the QMC works on long-word alignment, MRBLR value should be a multiple of 4 bytes.           |

| 08                          | Tx_S_PTR | 16              | Tx time slot assignment table pointer (SCC base + 60 in normal mode; SCC base + 20 for common Rx & Tx time slot assignment tables)—This global QMC parameter defines the start value of the TSATTx table. The TSATTx table in the global multichannel parameter listing starts by default at SCC base + 60.  Tx_S_PTR lets the user move the starting address of this table. If the same routing and masking are used for the transmitter and receiver, the tables can be overlaid, so Tx_S_PTR can point to SCC base + 20. This parameter is an offset from DPRBASE. This table must be present only once per SCC global area. Other SCCs can access this location. |

| 0A                          | RxPTR    | 16              | Rx pointer (initialize to SCC base + 20)—This global QMC parameter is a RISC variable that points to the current receiver time slot. The host must initialize this pointer to the starting location of TSATRx. The RISC processor increments this pointer whenever it completes the processing of a received time slot.                                                                                                                                                                                                                                                                                                                                              |

| 0C                          | GRFTHR   | 16              | Global receive frame threshold—Used to reduce interrupt overhead when many short HDLC frames arrive, each causing an RXF interrupt. GRFTHR can be set to limit the frequency of interrupts. Note that the RXF event is written to the interrupt table on each received frame, but GINT is set only when the number of RXF events (by all channels) reaches the GRFTHR value. GRFTHR can be changed on the fly. For information about exception handling, see Chapter 4, "QMC Exceptions."                                                                                                                                                                            |

| 0E                          | GRFCNT   | 16              | Global receive frame count (initialized GRFCNT = GRFTHR)—A down-counter used to implement the GRFTHR feature. GRFCNT decrements for each frame received. No other receiver interrupts affect this counter. The counter value is set to the threshold during initialization. GRFCNT is automatically reset to the GRFTHR value by the CPM after a global interrupt.                                                                                                                                                                                                                                                                                                   |

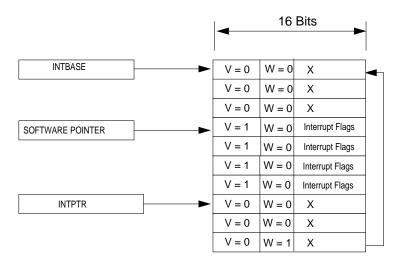

| 10                          | INTBASE  | 32              | Multichannel interrupt base address (host-initialized)—This pointer contains the starting address of the interrupt circular queue in external memory. Each entry contains information about an interrupt request that has been generated by the QMC to the host. Each SCC operating in QMC mode has its own interrupt table in external memory.  See Chapter 4, "QMC Exceptions."                                                                                                                                                                                                                                                                                    |

| 14                          | INTPTR   | 32              | Multichannel interrupt pointer (host-initialized)—This global parameter holds the address of the next QMC interrupt entry in the circular interrupt table. The RISC processor writes the next interrupt information to this entry when an exception occurs. The host must copy the value of INTBASE to INTPTR before enabling interrupts.                                                                                                                                                                                                                                                                                                                            |

**Table 2-1. Global Multichannel Parameters (Continued)**

|                             |          |                       | . ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------|----------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Offset<br>to<br>SCC<br>Base | Name     | Width<br>(Bits)       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 18                          | Rx_S_PTR | 16                    | Rx time-slot assignment table pointer (default = SCC base + 20 in normal mode)—This global QMC parameter defines the start value of the TSATRx table, which must be present only once per SCC global area. Other SCCs may access this location.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1A                          | TxPTR    | 16                    | TxPTR (initialize to SCC Base + 60)—This global parameter is a RISC variable that points to the current transmitter time slot. The host must initialize it to the starting location of TSATTx. The RISC processor increments this pointer whenever it completes the processing of a transmitter time slot.                                                                                                                                                                                                                                                                                                                                                                                          |

| 1C                          | C_MASK32 | 32                    | CRC constant (0xDEBB20E3)—Required to calculate 32-bit CRC-CCITT. C_MASK32 is written by the host during QMC initialization. It is used for 32-bit CRC-CCITT calculation if HDLC mode of operation is chosen for a selected channel. (This is a programmable option. For each HDLC channel, one of two CRCs can be chosen, as programmed in CHAMR.) For more information, see Section 2.4.1, "Channel-Specific HDLC Parameters," and Table 2-5. This entry must have a correct value if at least one HDLC channel is used; otherwise, it can be cleared (0).                                                                                                                                        |

| 20                          | TSATRX   | 32<br>Entries<br>x 16 | Time slot assignment table Rx—Host-initialized, 16-bit-wide table with 32 entries that define mapping of logical channels to time slots for the QMC receiver. The QMC protocol looks at chunks of 8 bits regardless of whether they come from one physical time slot of the TDM or whatever other combination of bits the TSA transfers to the SCC. These 8 bits are referred to as a time slot in the assignment table. It is recommended but not required to route all bits from the TDM to the SCC and to do all enabling and masking in the time-slot assignment table. See Figure 2-3.                                                                                                         |

| 60                          | TSATTX   | 32<br>Entries<br>x 16 | Time slot assignment table Tx—Maps a specific logical channel to each physical time slot. Time slot assignment table Tx is a host-initialized, 16-bit table with 32 entries that define the mapping of channels to time slots for the QMC transmitter. The QMC protocol looks at chunks of 8 bits regardless if they go to one physical time slot of the TDM or whatever other combination of bits are transferred from the SCC to the TDM through the TSA. These 8 bits are referred to as a time slot in the assignment table. It is recommended but not required to route all bits from the TDM to the SCC and to do all enabling and masking in the time slot assignment table. See Figure 2-3. |

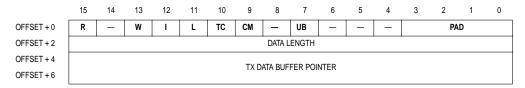

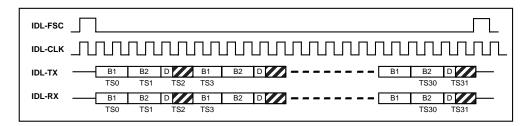

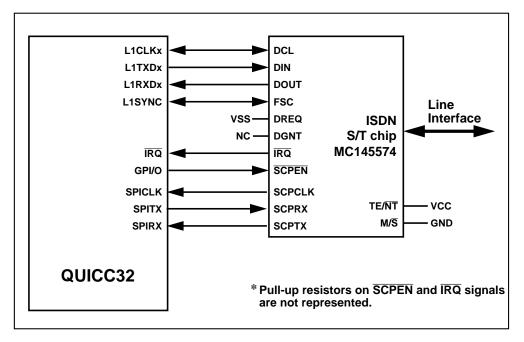

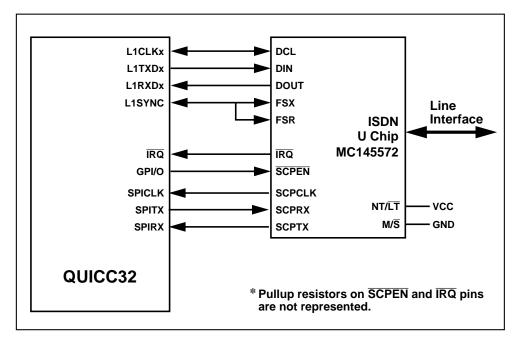

| AO                          | C_MASK16 | 16                    | CRC constant (0xF0B8)—Required to calculate 16-bit CRC-CCITT. This constant is written by the host during QMC initialization. It is used for 16-bit CRC-CCITT calculation if HDLC mode of operation is chosen for a selected channel. (This is a programmable option. For each HDLC channel, one of two CRCs can be chosen, as programmed in CHAMR.) For more information, see Section 2.4.1, "Channel-Specific HDLC Parameters," and Table 2-5. This entry must have a correct value if at least one HDLC channel is used; otherwise, it can be cleared (0).                                                                                                                                       |