### **SAA7118**

## Multistandard video decoder with adaptive comb filter and component video input

Rev. 07 — 7 July 2008

**Product data sheet**

### 1. General description

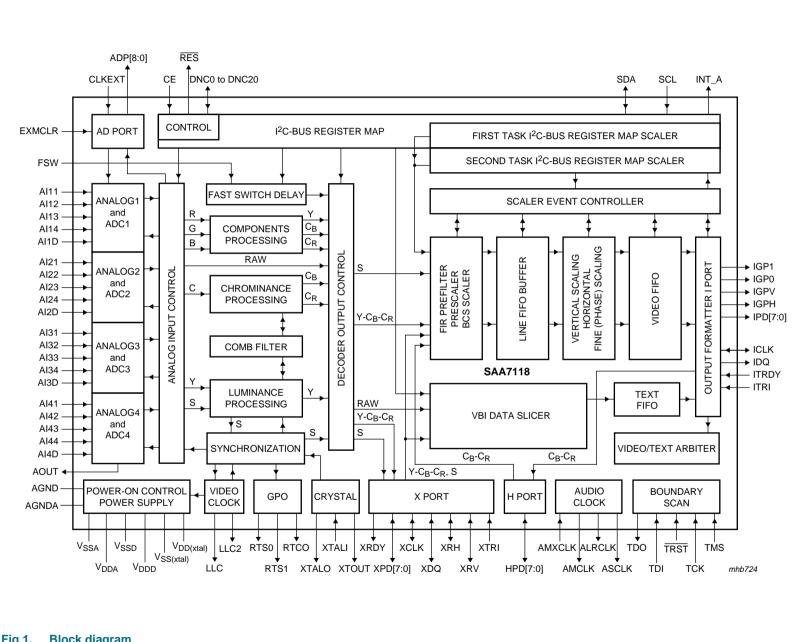

The SAA7118 is a multistandard comb filter video decoder supporting various applications to capture analog video; it includes digitizing of component formats Y-P<sub>B</sub>-P<sub>R</sub> and RGB, and is providing high quality, optionally scaled video.

The SAA7118 is a combination of a four-channel analog preprocessing circuit including source selection, anti-aliasing filter and Analog-to-Digital Converter (ADC) with succeeding decimation filters from 27 MHz to 13.5 MHz data rate. Each preprocessing channel comes with an automatic clamp and gain control. The SAA7118 combines a Clock Generation Circuit (CGC), a digital multistandard decoder containing two-dimensional chrominance/luminance separation by an adaptive comb filter and a high performance scaler, including variable horizontal and vertical up and downscaling and a brightness, contrast and saturation control circuit.

It is a highly integrated circuit for desktop video and similar applications. The decoder is based on the principle of line-locked clock decoding and is able to decode the color of PAL, SECAM and NTSC signals into ITU 601 compatible color component values. The SAA7118 accepts CVBS or S-video (Y/C) as analog inputs from TV or VCR sources, including weak and distorted signals as well as baseband component signals Y-P $_{\rm B}$ -P $_{\rm R}$  or RGB. An expansion port (X port) for digital video (bidirectional half duplex, D1 compatible) is also supported to connect to MPEG or a video phone codec. At the so called image port (I port) the SAA7118 supports 8-bit or 16-bit wide output data with auxiliary reference data for interfacing to VGA controllers.

The target application for the SAA7118 is to capture and scale video images, to be provided as a digital video stream through the image port of a VGA controller, for capture to system memory, or just to provide digital baseband video to any picture improvement processing.

The SAA7118 also provides a means for capturing the serially coded data in the Vertical Blanking Interval (VBI) data. Two principal functions are available:

- To capture raw video samples, after interpolation to the required output data rate, via the scaler

- 2. A versatile data slicer (data recovery) unit

The SAA7118 also incorporates field-locked audio clock generation. This function ensures that there is always the same number of audio samples associated with a field, or a set of fields. This prevents the loss of synchronization between video and audio during capture or playback.

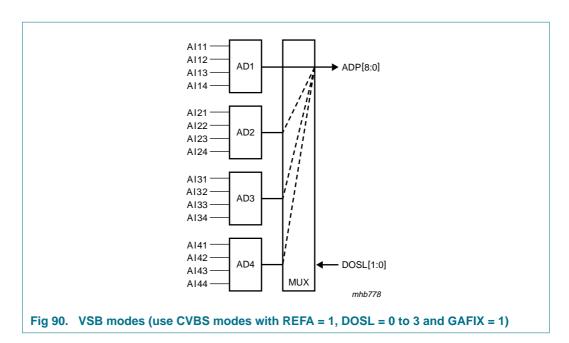

All of the ADCs may be used to digitize a Vestigial Side Band (VSB) signal for subsequent decoding; a dedicated output port and a selectable VSB clock input is provided.

### Multistandard video decoder with adaptive comb filter

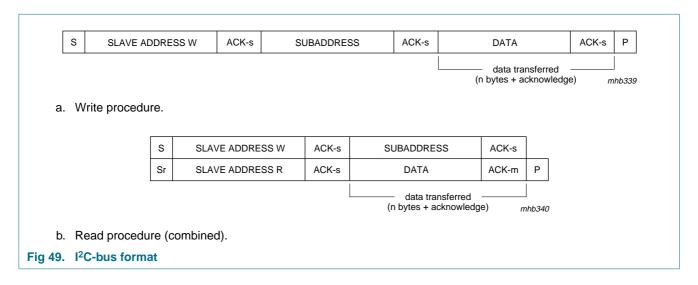

The circuit is I<sup>2</sup>C-bus controlled (full write/read capability for all programming registers, bit rate up to 400 kbit/s).

### 2. Features

### 2.1 Video acquisition/clock

- Up to sixteen analog CVBS, split as desired (all of the CVBS inputs optionally can be used to convert e.g. VSB signals)

- Up to eight analog Y + C inputs, split as desired

- Up to four analog component inputs, with embedded or separate sync, split as desired

- Four on-chip anti-aliasing filters in front of the ADCs

- Automatic Clamp Control (ACC) for CVBS, Y and C (or VSB) and component signals

- Switchable white peak control

- Four 9-bit low noise CMOS ADCs running at twice the oversampling rate (27 MHz)

- Fully programmable static gain or Automatic Gain Control (AGC), matching to the particular signal properties

- On-chip line-locked clock generation in accordance with "ITU 601"

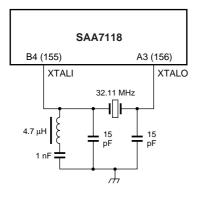

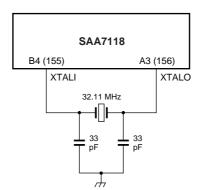

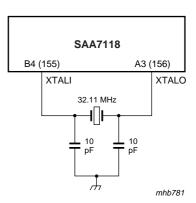

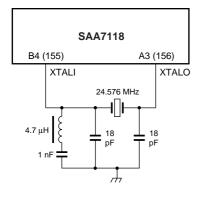

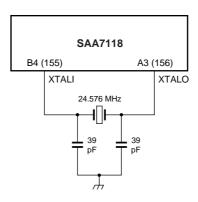

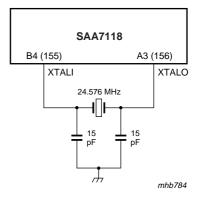

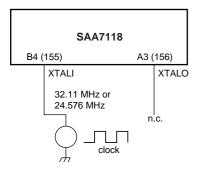

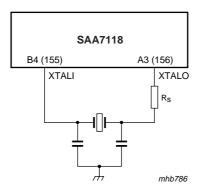

- Requires only one crystal (32.11 MHz or 24.576 MHz) for all standards

- Horizontal and vertical sync detection

### 2.2 Video decoder

- Digital Phase-Locked Loop (PLL) for synchronization and clock generation from all standards and non-standard video sources e.g. consumer grade VTR

- Automatic detection of any supported color standard

- Luminance and chrominance signal processing for PAL B, G, D, H, I and N, combination PAL N, PAL M, NTSC M, NTSC-Japan, NTSC 4.43 and SECAM

- Adaptive 2/4-line comb filter for two dimensional chrominance/luminance separation, also with VTR signals

- Increased luminance and chrominance bandwidth for all PAL and NTSC standards

- Reduced cross color and cross luminance artefacts

- PAL delay line for correcting PAL phase errors

- Brightness Contrast Saturation (BCS) adjustment, separately for composite and baseband signals

- User programmable sharpness control

- Detection of copy-protected signals according to the Macrovision standard, indicating level of protection

- Independent gain and offset adjustment for raw data path

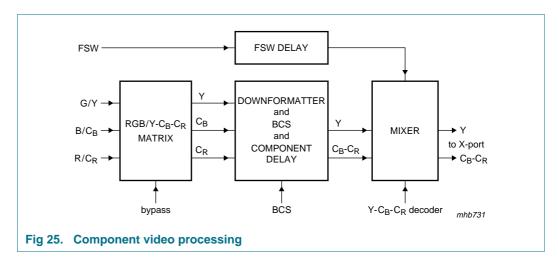

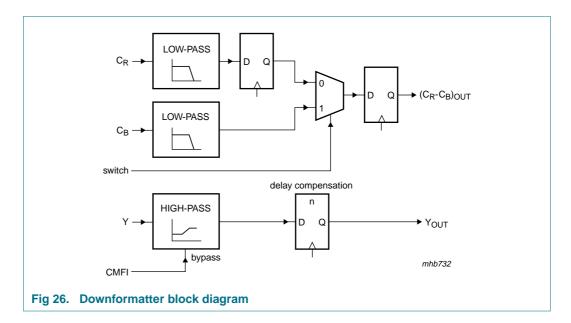

### 2.3 Component video processing

- RGB component inputs

- Y-P<sub>B</sub>-P<sub>R</sub> component inputs

- Fast blanking between CVBS and synchronous component inputs

- Digital RGB to Y-C<sub>B</sub>-C<sub>R</sub> matrix

### Multistandard video decoder with adaptive comb filter

### 2.4 Video scaler

- Horizontal and vertical downscaling and upscaling to randomly sized windows

- Horizontal and vertical scaling range: variable zoom to ½64 (icon) (it should be noted that the H and V zoom are restricted by the transfer data rates)

- Anti-alias and accumulating filter for horizontal scaling

- Vertical scaling with linear phase interpolation and accumulating filter for anti-aliasing (6-bit phase accuracy)

- Horizontal phase correct up and downscaling for improved signal quality of scaled data, especially for compression and video phone applications, with 6-bit phase accuracy (1.2 ns step width)

- Two independent programming sets for scaler part, to define two 'ranges' per field or sequences over frames

- Fieldwise switching between decoder part and expansion port (X port) input

- Brightness, contrast and saturation controls for scaled outputs

### 2.5 VBI data decoder and slicer

Versatile VBI data decoder, slicer, clock regeneration and byte synchronization e.g. for World Standard Teletext (WST), North American Broadcast Text System (NABTS), closed caption, Wide Screen Signalling (WSS), etc.

### 2.6 Audio clock generation

- Generation of a field-locked audio master clock to support a constant number of audio clocks per video field

- Generation of an audio serial and left/right (channel) clock signal

### 2.7 Digital I/O interfaces

- Real-time signal port (R port), inclusive continuous line-locked reference clock and real-time status information supporting RTC level 3.1 (refer to document "RTC Functional Specification" for details)

- Bidirectional expansion port (X port) with half duplex functionality (D1), 8-bit Y-C<sub>B</sub>-C<sub>R</sub>:

- Output from decoder part, real-time and unscaled

- Input to scaler part, e.g. video from MPEG decoder (extension to 16-bit possible)

- Video image port (I port) configurable for 8-bit data (extension to 16-bit possible) in master mode (own clock), or slave mode (external clock), with auxiliary timing and handshake signals

- Discontinuous data streams supported

- 32-word × 4-byte FIFO register for video output data

- 28-word × 4-byte FIFO register for decoded VBI data output

- Scaled 4: 2: 2, 4: 1: 1, 4: 2: 0, 4: 1: 0 Y-C<sub>B</sub>-C<sub>R</sub> output

- Scaled 8-bit luminance only and raw CVBS data output

- Sliced, decoded VBI data output

### 2.8 Miscellaneous

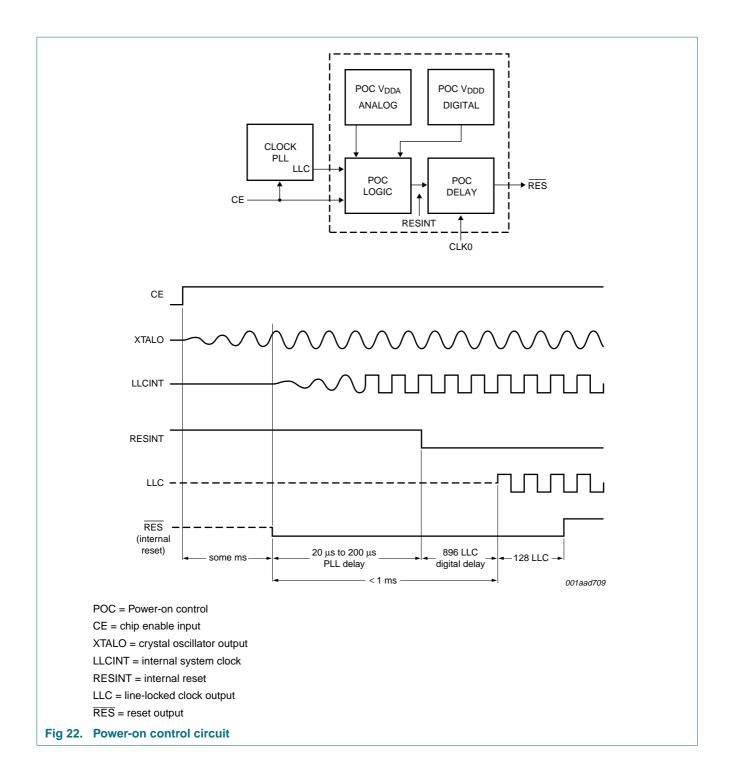

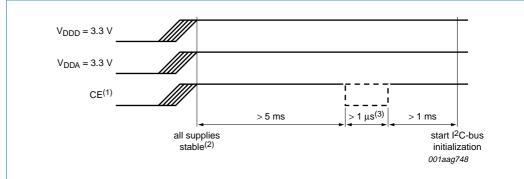

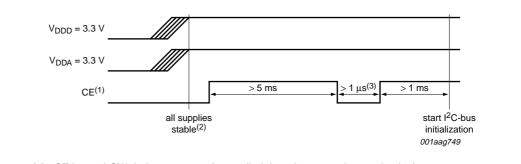

- Power-on control

- 5 V tolerant digital inputs and I/O ports

### Multistandard video decoder with adaptive comb filter

- Software controlled power saving standby modes supported

- Programming via serial I<sup>2</sup>C-bus, full read back ability by an external controller, bit rate up to 400 kbit/s

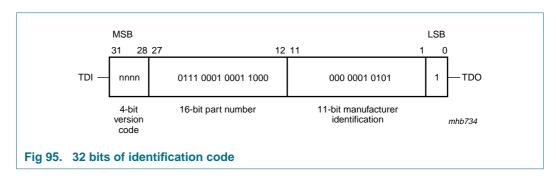

- Boundary scan test circuit complies with the "IEEE Std. 1149.b1 1994".

### 3. Applications

- PC-video capture and editing

- Personal video recorders (time shifting)

- Cable, terrestrial, and satellite set-top boxes

- Internet terminals

- Flat-panel monitors

- DVD recordable players

- AV-ready hard-disk drivers

- Digital televisions/scan conversion

- Video surveillance/security

- Video editing/postproduction

- Video phones

- Video projectors

- Digital VCRs

### Multistandard video decoder with adaptive comb filter

### 4. Quick reference data

Table 1. Quick reference data

| Symbol                | Parameter                                       | Conditions     | Min          | Тур  | Max  | Unit |

|-----------------------|-------------------------------------------------|----------------|--------------|------|------|------|

| $V_{DDD}$             | digital supply voltage                          |                | 3.0          | 3.3  | 3.6  | V    |

| $V_{DDA}$             | analog supply voltage                           |                | 3.1          | 3.3  | 3.5  | V    |

| $T_{amb}$             | ambient temperature                             |                | 0            | -    | 70   | °C   |

| P <sub>tot(A+D)</sub> | total power dissipation analog and digital part | component mode | <u>[1]</u> _ | 1105 | 1350 | mW   |

<sup>[1] 8-</sup>bit image port output mode, expansion port is 3-stated.

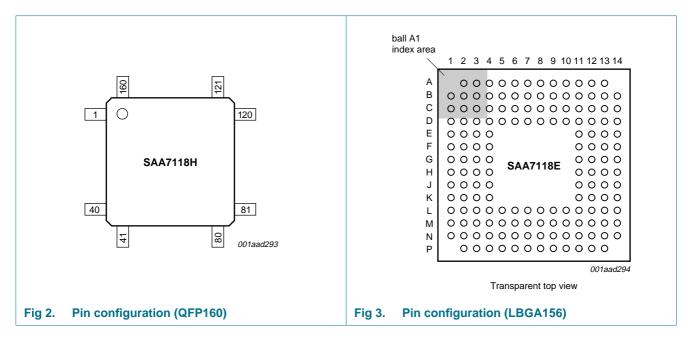

### 5. Ordering information

### Table 2. Ordering information

| Type number | Package |                                                                                                                     |          |  |  |  |  |  |

|-------------|---------|---------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|

|             | Name    | Description                                                                                                         | Version  |  |  |  |  |  |

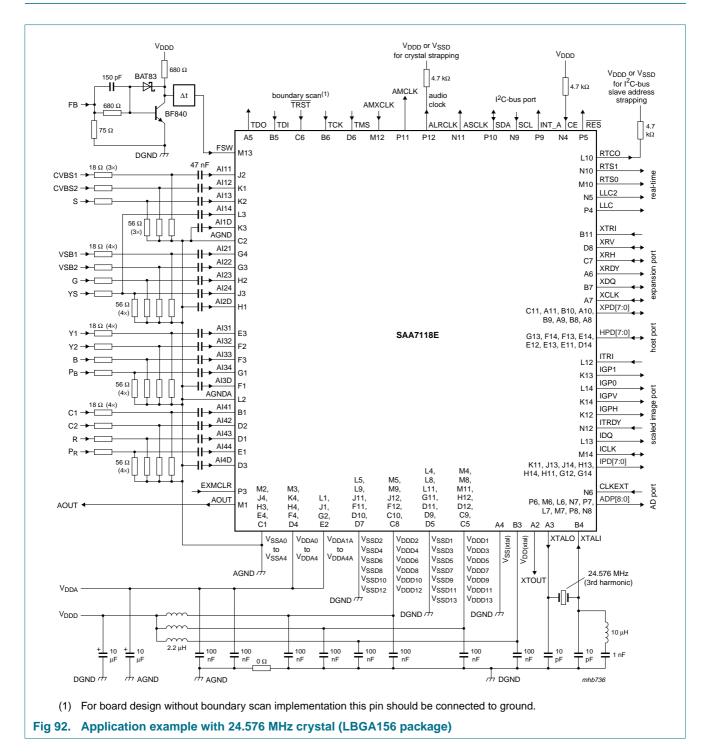

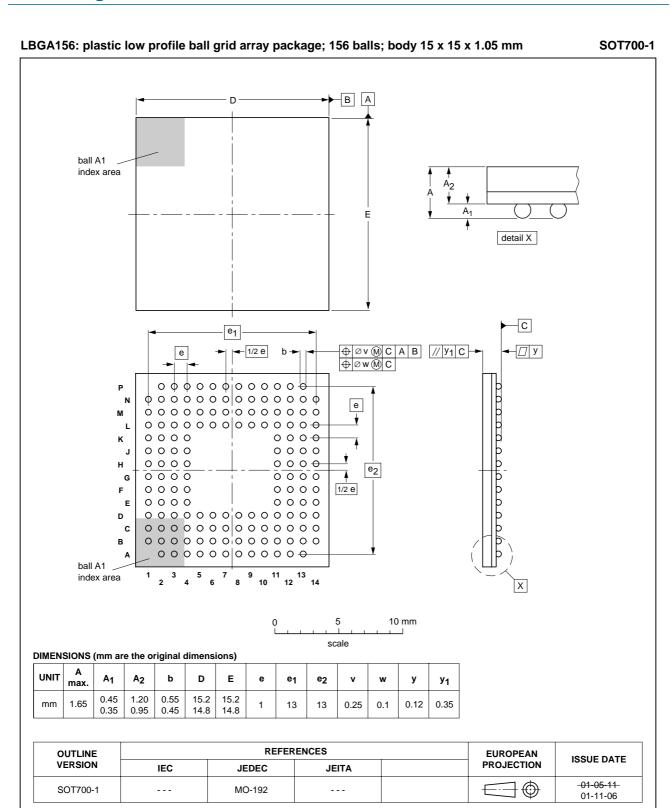

| SAA7118E    | LBGA156 | plastic low profile ball grid array package; 156 balls; body 15 × 15 × 1.05 mm                                      | SOT700-1 |  |  |  |  |  |

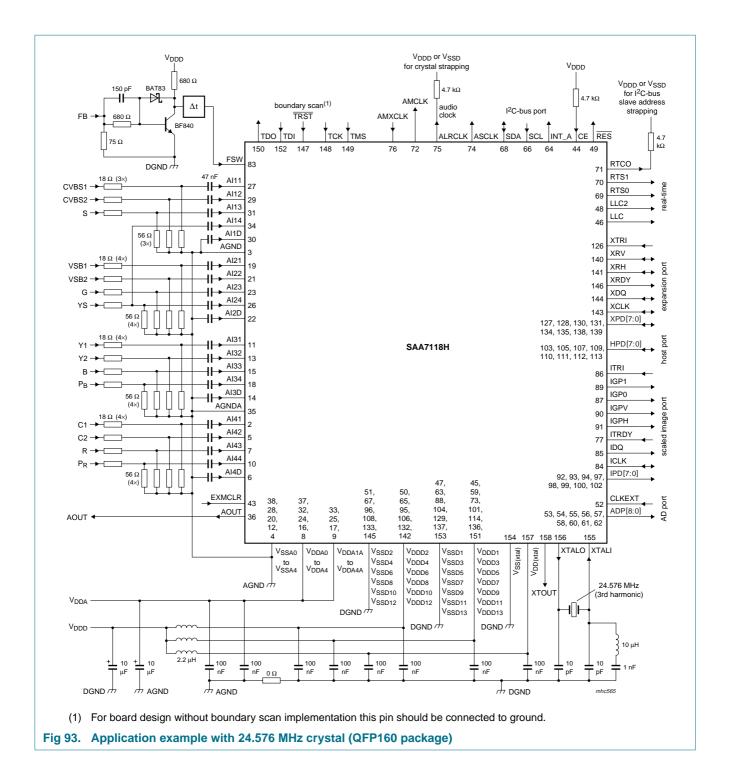

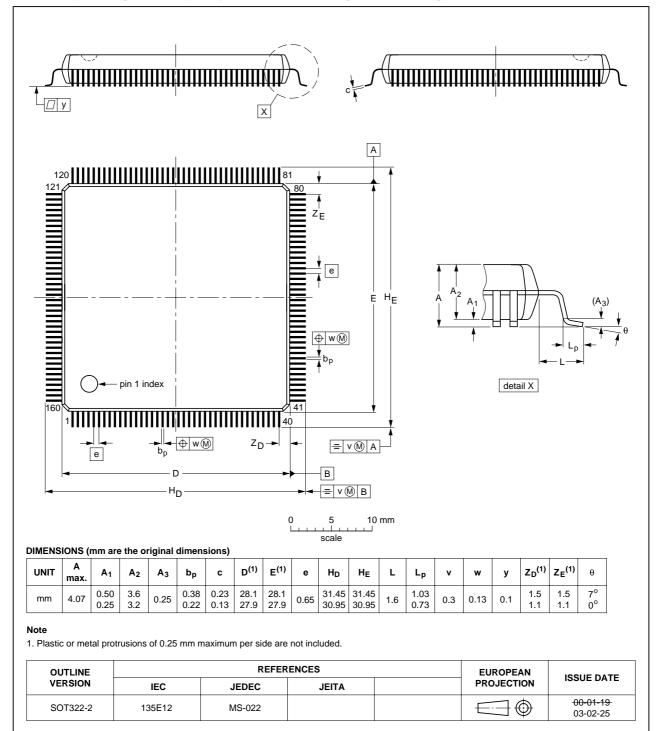

| SAA7118H    | QFP160  | plastic quad flat package; 160 leads (lead length 1.6 mm); body $28 \times 28 \times 3.4$ mm; high stand-off height | SOT322-2 |  |  |  |  |  |

# Multistandard video decoder with adaptive comb filter

# 9 Block diagram

Fig 1. **Block diagram**

**Product data**

sheet

Rev.

07

Ä

**July 2008**

### Multistandard video decoder with adaptive comb filter

### 7. Pinning information

### 7.1 Pinning

Table 3. Pin allocation table

| Pin | Symbol             | Pin | Symbol             | Pin | Symbol                | Pin | Symbol      |

|-----|--------------------|-----|--------------------|-----|-----------------------|-----|-------------|

| A2  | XTOUT              | А3  | XTALO              | A4  | V <sub>SS(xtal)</sub> | A5  | TDO         |

| A6  | XRDY               | A7  | XCLK               | A8  | XPD0                  | A9  | XPD2        |

| A10 | XPD4               | A11 | XPD6               | A12 | DNC5                  | A13 | DNC3        |

| B1  | Al41               | B2  | DNC6               | В3  | $V_{DD(xtal)}$        | B4  | XTALI       |

| B5  | TDI                | B6  | TCK                | B7  | XDQ                   | B8  | XPD1        |

| B9  | XPD3               | B10 | XPD5               | B11 | XTRI                  | B12 | DNC4        |

| B13 | DNC7               | B14 | DNC8               | C1  | $V_{SSA4}$            | C2  | AGND        |

| C3  | DNC9               | C4  | DNC10              | C5  | $V_{DDD13}$           | C6  | TRST        |

| C7  | XRH                | C8  | $V_{DDD12}$        | C9  | $V_{DDD11}$           | C10 | $V_{DDD10}$ |

| C11 | XPD7               | C12 | DNC11              | C13 | DNC12                 | C14 | DNC2        |

| D1  | Al43               | D2  | AI42               | D3  | AI4D                  | D4  | $V_{DDA4}$  |

| D5  | V <sub>SSD13</sub> | D6  | TMS                | D7  | $V_{SSD12}$           | D8  | XRV         |

| D9  | V <sub>SSD11</sub> | D10 | V <sub>SSD10</sub> | D11 | $V_{SSD9}$            | D12 | $V_{DDD9}$  |

| D13 | DNC1               | D14 | HPD0               | E1  | AI44                  | E2  | $V_{DDA4A}$ |

| E3  | Al31               | E4  | $V_{SSA3}$         | E11 | HPD1                  | E12 | HPD3        |

| E13 | HPD2               | E14 | HPD4               | F1  | AI3D                  | F2  | Al32        |

| F3  | Al33               | F4  | $V_{DDA3}$         | F11 | V <sub>SSD8</sub>     | F12 | $V_{DDD8}$  |

| F13 | HPD5               | F14 | HPD6               | G1  | Al34                  | G2  | $V_{DDA3A}$ |

| G3  | Al22               | G4  | Al21               | G11 | V <sub>SSD7</sub>     | G12 | IPD1        |

| G13 | HPD7               | G14 | IPD0               | H1  | AI2D                  | H2  | Al23        |

| НЗ  | V <sub>SSA2</sub>  | H4  | $V_{DDA2}$         | H11 | IPD2                  | H12 | $V_{DDD7}$  |

### Multistandard video decoder with adaptive comb filter

Table 3.

Pin allocation table ...continued

| Pin | Symbol     | Pin | Symbol            | Pin | Symbol            | Pin | Symbol     |

|-----|------------|-----|-------------------|-----|-------------------|-----|------------|

| H13 | IPD4       | H14 | IPD3              | J1  | $V_{DDA2A}$       | J2  | AI11       |

| J3  | Al24       | J4  | $V_{SSA1}$        | J11 | V <sub>SSD6</sub> | J12 | $V_{DDD6}$ |

| J13 | IPD6       | J14 | IPD5              | K1  | Al12              | K2  | AI13       |

| K3  | AI1D       | K4  | $V_{DDA1}$        | K11 | IPD7              | K12 | IGPH       |

| K13 | IGP1       | K14 | IGPV              | L1  | $V_{DDA1A}$       | L2  | AGNDA      |

| L3  | Al14       | L4  | V <sub>SSD1</sub> | L5  | $V_{SSD2}$        | L6  | ADP6       |

| L7  | ADP3       | L8  | $V_{SSD3}$        | L9  | $V_{SSD4}$        | L10 | RTCO       |

| L11 | $V_{SSD5}$ | L12 | ITRI              | L13 | IDQ               | L14 | IGP0       |

| M1  | AOUT       | M2  | V <sub>SSA0</sub> | МЗ  | $V_{DDA0}$        | M4  | $V_{DDD1}$ |

| M5  | $V_{DDD2}$ | M6  | ADP7              | M7  | ADP2              | M8  | $V_{DDD3}$ |

| M9  | $V_{DDD4}$ | M10 | RTS0              | M11 | $V_{DDD5}$        | M12 | AMXCLK     |

| M13 | FSW        | M14 | ICLK              | N1  | DNC13             | N2  | DNC14      |

| N3  | DNC15      | N4  | CE                | N5  | LLC2              | N6  | CLKEXT     |

| N7  | ADP5       | N8  | ADP0              | N9  | SCL               | N10 | RTS1       |

| N11 | ASCLK      | N12 | ITRDY             | N13 | DNC16             | N14 | DNC17      |

| P2  | DNC18      | P3  | EXMCLR            | P4  | LLC               | P5  | RES        |

| P6  | ADP8       | P7  | ADP4              | P8  | ADP1              | P9  | INT_A      |

| P10 | SDA        | P11 | AMCLK             | P12 | ALRCLK            | P13 | DNC0       |

### 7.2 Pin description

Table 4. Pin description

| Symbol      | Pin    |         | Type[1] | Description                                                    |

|-------------|--------|---------|---------|----------------------------------------------------------------|

|             | QFP160 | LBGA156 |         |                                                                |

| DNC6        | 1      | B2      | 0       | do not connect, reserved for future extensions and for testing |

| Al41        | 2      | B1      | I       | analog input 41                                                |

| AGND        | 3      | C2      | Р       | analog ground                                                  |

| $V_{SSA4}$  | 4      | C1      | Р       | ground for analog inputs Al4x                                  |

| Al42        | 5      | D2      | I       | analog input 42                                                |

| AI4D        | 6      | D3      | I       | differential input for ADC channel 4 (pins Al41 to Al44)       |

| Al43        | 7      | D1      | I       | analog input 43                                                |

| $V_{DDA4}$  | 8      | D4      | Р       | analog supply voltage for analog inputs Al4x (3.3 V)           |

| $V_{DDA4A}$ | 9      | E2      | Р       | analog supply voltage for analog inputs Al4x (3.3 V)           |

| Al44        | 10     | E1      | I       | analog input 44                                                |

| Al31        | 11     | E3      | I       | analog input 31                                                |

| $V_{SSA3}$  | 12     | E4      | Р       | ground for analog inputs Al3x                                  |

| Al32        | 13     | F2      | I       | analog input 32                                                |

| AI3D        | 14     | F1      | I       | differential input for ADC channel 3 (pins Al31 to Al34)       |

| Al33        | 15     | F3      | I       | analog input 33                                                |

| $V_{DDA3}$  | 16     | F4      | Р       | analog supply voltage for analog inputs Al3x (3.3 V)           |

| $V_{DDA3A}$ | 17     | G2      | Р       | analog supply voltage for analog inputs Al3x (3.3 V)           |

Table 4. Pin description ... continued

| Symbol            | Pin    |         | Type[1] | Description                                                                            |  |  |

|-------------------|--------|---------|---------|----------------------------------------------------------------------------------------|--|--|

|                   | QFP160 | LBGA156 |         |                                                                                        |  |  |

| Al34              | 18     | G1      | I       | analog input 34                                                                        |  |  |

| Al21              | 19     | G4      | I       | analog input 21                                                                        |  |  |

| V <sub>SSA2</sub> | 20     | H3      | Р       | ground for analog inputs Al2x                                                          |  |  |

| Al22              | 21     | G3      | I       | analog input 22                                                                        |  |  |

| AI2D              | 22     | H1      | I       | differential input for ADC channel 2 (pins Al24 to Al21)                               |  |  |

| Al23              | 23     | H2      | I       | analog input 23                                                                        |  |  |

| $V_{DDA2}$        | 24     | H4      | Р       | analog supply voltage for analog inputs Al2x (3.3 V)                                   |  |  |

| $V_{DDA2A}$       | 25     | J1      | Р       | analog supply voltage for analog inputs Al2x (3.3 V)                                   |  |  |

| Al24              | 26     | J3      | I       | analog input 24                                                                        |  |  |

| Al11              | 27     | J2      | I       | analog input 11                                                                        |  |  |

| V <sub>SSA1</sub> | 28     | J4      | Р       | ground for analog inputs Al1x                                                          |  |  |

| Al12              | 29     | K1      | I       | analog input 12                                                                        |  |  |

| AI1D              | 30     | K3      | I       | differential input for ADC channel 1 (pins Al14 to Al11)                               |  |  |

| Al13              | 31     | K2      | I       | analog input 13                                                                        |  |  |

| $V_{DDA1}$        | 32     | K4      | Р       | analog supply voltage for analog inputs Al1x (3.3 V)                                   |  |  |

| $V_{DDA1A}$       | 33     | L1      | Р       | analog supply voltage for analog inputs Al1x (3.3 V)                                   |  |  |

| Al14              | 34     | L3      | I       | analog input 14                                                                        |  |  |

| AGNDA             | 35     | L2      | Р       | analog signal ground                                                                   |  |  |

| AOUT              | 36     | M1      | 0       | analog test output (do not connect)                                                    |  |  |

| $V_{DDA0}$        | 37     | M3      | Р       | analog supply voltage (3.3 V) for internal clock generation circuit                    |  |  |

| V <sub>SSA0</sub> | 38     | M2      | Р       | ground for internal Clock Generation Circuit (CGC)                                     |  |  |

| DNC13             | 39     | N1      | NC      | do not connect, reserved for future extensions and for testing                         |  |  |

| DNC14             | 40     | N2      | I/pu    | do not connect, reserved for future extensions and for testing                         |  |  |

| DNC18             | 41     | P2      | I/O     | do not connect, reserved for future extensions and for testing                         |  |  |

| DNC15             | 42     | N3      | I/pd    | do not connect, reserved for future extensions and for testing                         |  |  |

| EXMCLR            | 43     | P3      | I/pd    | external mode clear (with internal pull-down)                                          |  |  |

| CE                | 44     | N4      | I/pu    | Chip Enable (CE) or reset input (with internal pull-up)                                |  |  |

| $V_{DDD1}$        | 45     | M4      | Р       | digital supply voltage 1 (peripheral cells)                                            |  |  |

| LLC               | 46     | P4      | 0       | line-locked system clock output (27 MHz nominal)                                       |  |  |

| V <sub>SSD1</sub> | 47     | L4      | Р       | digital ground 1 (peripheral cells)                                                    |  |  |

| LLC2              | 48     | N5      | 0       | line-locked $\frac{1}{2}$ clock output (13.5 MHz nominal)                              |  |  |

| RES               | 49     | P5      | 0       | reset output (active LOW)                                                              |  |  |

| $V_{DDD2}$        | 50     | M5      | Р       | digital supply voltage 2 (core)                                                        |  |  |

| V <sub>SSD2</sub> | 51     | L5      | Р       | digital ground 2 (core; substrate connection)                                          |  |  |

| CLKEXT            | 52     | N6      | I       | external clock input intended for analog-to-digital conversion of VSB signals (36 MHz) |  |  |

| ADP8              | 53     | P6      | 0       | MSB of direct analog-to-digital converted output data (VSB)                            |  |  |

| ADP7              | 54     | M6      | 0       | MSB – 1 of direct analog-to-digital converted output data (VSB)                        |  |  |

| ADP6              | 55     | L6      | 0       | MSB – 2 of direct analog-to-digital converted output data (VSB)                        |  |  |

| ADP5              | 56     | N7      | 0       | MSB – 3 of direct analog-to-digital converted output data (VSB)                        |  |  |

Table 4. Pin description ... continued

| ADP4 5 ADP3 5 VDDD3 5 ADP2 6 ADP1 6 ADP0 6 VSSD3 6 INT_A 6 VDDD4 6 SCL 6 VSSD4      | 57<br>58<br>59<br>60<br>61<br>62<br>63<br>64<br>65<br>66<br>67<br>68 | L7 M8 M7 P8 N8 L8 P9 M9 N9 L9 P10 | O O O P O O O P O O O P O O O P O O O P O O O O P O O O O O O O O O O O O O O O O O O O O | MSB – 4 of direct analog-to-digital converted output data (VSB)  MSB – 5 of direct analog-to-digital converted output data (VSB)  digital supply voltage 3 (peripheral cells)  MSB – 6 of direct analog-to-digital converted output data (VSB)  MSB – 7 of direct analog-to-digital converted output data (VSB)  LSB of direct analog-to-digital converted output data (VSB)  digital ground 3 (peripheral cells)  I²C-bus interrupt flag (LOW if any enabled status bit has changed)  digital supply voltage 4 (core)  serial clock input (I²C-bus) with inactive output path  digital ground 4 (core) |

|-------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADP3                                                                                | 58<br>59<br>60<br>61<br>62<br>63<br>64<br>65<br>66<br>67<br>68       | L7 M8 M7 P8 N8 L8 P9 M9 N9 L9 P10 | O P O O O O O O O O O O O O O O O O O O                                                   | MSB – 5 of direct analog-to-digital converted output data (VSB) digital supply voltage 3 (peripheral cells)  MSB – 6 of direct analog-to-digital converted output data (VSB)  MSB – 7 of direct analog-to-digital converted output data (VSB)  LSB of direct analog-to-digital converted output data (VSB)  digital ground 3 (peripheral cells)  I <sup>2</sup> C-bus interrupt flag (LOW if any enabled status bit has changed) digital supply voltage 4 (core) serial clock input (I <sup>2</sup> C-bus) with inactive output path                                                                    |

| V <sub>DDD3</sub>                                                                   | 59<br>60<br>61<br>62<br>63<br>64<br>65<br>66<br>67<br>68             | M8 M7 P8 N8 L8 P9 M9 N9 L9        | P O O O P O/od P I(/O)                                                                    | digital supply voltage 3 (peripheral cells)  MSB – 6 of direct analog-to-digital converted output data (VSB)  MSB – 7 of direct analog-to-digital converted output data (VSB)  LSB of direct analog-to-digital converted output data (VSB)  digital ground 3 (peripheral cells)  I²C-bus interrupt flag (LOW if any enabled status bit has changed)  digital supply voltage 4 (core)  serial clock input (I²C-bus) with inactive output path                                                                                                                                                            |

| ADP2 ADP1 ADP0 VSSD3 INT_A VDDD4 SCL VSSD4                                          | 60<br>61<br>62<br>63<br>64<br>65<br>66<br>67<br>68                   | M7 P8 N8 L8 P9 M9 N9 L9           | O O O P O/od P I(/O) P                                                                    | MSB – 6 of direct analog-to-digital converted output data (VSB)  MSB – 7 of direct analog-to-digital converted output data (VSB)  LSB of direct analog-to-digital converted output data (VSB)  digital ground 3 (peripheral cells)  I <sup>2</sup> C-bus interrupt flag (LOW if any enabled status bit has changed)  digital supply voltage 4 (core)  serial clock input (I <sup>2</sup> C-bus) with inactive output path                                                                                                                                                                               |

| ADP1 6 ADP0 6 Vssd3 6 INT_A 6 Vdd4 6 SCL 6 Vssd4                                    | 61<br>62<br>63<br>64<br>65<br>66<br>67<br>68<br>69                   | P8 N8 L8 P9 M9 N9 L9              | O<br>O<br>P<br>O/od<br>P<br>I(/O)                                                         | MSB – 7 of direct analog-to-digital converted output data (VSB)  LSB of direct analog-to-digital converted output data (VSB)  digital ground 3 (peripheral cells)  I <sup>2</sup> C-bus interrupt flag (LOW if any enabled status bit has changed)  digital supply voltage 4 (core)  serial clock input (I <sup>2</sup> C-bus) with inactive output path                                                                                                                                                                                                                                                |

| ADP0 6 V <sub>SSD3</sub> 6 INT_A 6 V <sub>DDD4</sub> 6 SCL 6 V <sub>SSD4</sub>      | 62<br>63<br>64<br>65<br>66<br>67<br>68<br>69                         | N8<br>L8<br>P9<br>M9<br>N9<br>L9  | O P O/od P I(/O) P                                                                        | LSB of direct analog-to-digital converted output data (VSB) digital ground 3 (peripheral cells)  I <sup>2</sup> C-bus interrupt flag (LOW if any enabled status bit has changed) digital supply voltage 4 (core) serial clock input (I <sup>2</sup> C-bus) with inactive output path                                                                                                                                                                                                                                                                                                                    |

| V <sub>SSD3</sub> 6<br>INT_A 6<br>V <sub>DDD4</sub> 6<br>SCL 6<br>V <sub>SSD4</sub> | 63<br>64<br>65<br>66<br>67<br>68<br>69                               | L8<br>P9<br>M9<br>N9<br>L9        | P<br>O/od<br>P<br>I(/O)                                                                   | digital ground 3 (peripheral cells)  I <sup>2</sup> C-bus interrupt flag (LOW if any enabled status bit has changed)  digital supply voltage 4 (core)  serial clock input (I <sup>2</sup> C-bus) with inactive output path                                                                                                                                                                                                                                                                                                                                                                              |

| INT_A 6 V <sub>DDD4</sub> 6 SCL 6 V <sub>SSD4</sub>                                 | 64<br>65<br>66<br>67<br>68<br>69                                     | P9<br>M9<br>N9<br>L9<br>P10       | O/od<br>P<br>I(/O)                                                                        | I <sup>2</sup> C-bus interrupt flag (LOW if any enabled status bit has changed) digital supply voltage 4 (core) serial clock input (I <sup>2</sup> C-bus) with inactive output path                                                                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>DDD4</sub> 6           SCL         6           V <sub>SSD4</sub> 6           | 65<br>66<br>67<br>68<br>69                                           | M9<br>N9<br>L9<br>P10             | P<br>I(/O)<br>P                                                                           | digital supply voltage 4 (core) serial clock input (I <sup>2</sup> C-bus) with inactive output path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SCL 6                                                                               | 66<br>67<br>68<br>69                                                 | N9<br>L9<br>P10                   | I(/O)<br>P                                                                                | serial clock input (I <sup>2</sup> C-bus) with inactive output path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>SSD4</sub>                                                                   | 67<br>68<br>69                                                       | L9<br>P10                         | Р                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                     | 68<br>69                                                             | P10                               |                                                                                           | digital ground 4 (core)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SDA 6                                                                               | 69                                                                   |                                   | I/O/od                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                     |                                                                      | M10                               |                                                                                           | serial data input/output (I <sup>2</sup> C-bus)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RTS0 6                                                                              | 70                                                                   |                                   | 0                                                                                         | real-time status or sync information, controlled by subaddresses 11h and 12h; see Section 10.2.18 and Section 10.2.19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RTS1 7                                                                              |                                                                      | N10                               | 0                                                                                         | real-time status or sync information, controlled by subaddresses 11h and 12h; see Section 10.2.18 and Section 10.2.19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RTCO 7                                                                              | 71                                                                   | L10                               | O/st/pd                                                                                   | real-time control output; contains information about actual system clock frequency, field rate, odd/even sequence, decoder status, subcarrier frequency and phase and PAL sequence (see document "RTC Functional Description", available on request); the RTCO pin is enabled via I <sup>2</sup> C-bus bit RTCE; see Table 35[2][3]                                                                                                                                                                                                                                                                     |

| AMCLK 7                                                                             | 72                                                                   | P11                               | 0                                                                                         | audio master clock output, up to 50 % of crystal clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| V <sub>DDD5</sub>                                                                   | 73                                                                   | M11                               | Р                                                                                         | digital supply voltage 5 (peripheral cells)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ASCLK 7                                                                             | 74                                                                   | N11                               | 0                                                                                         | audio serial clock output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ALRCLK 7                                                                            | 75                                                                   | P12                               | O/st/pd                                                                                   | audio left/right clock output; can be strapped to supply via a 3.3 k $\Omega$ resistor to indicate that the default 24.576 MHz crystal (pin ALRCLK = LOW; internal pull-down) has been replaced by a 32.110 MHz crystal (pin ALRCLK = HIGH)[2][4]                                                                                                                                                                                                                                                                                                                                                       |

| AMXCLK 7                                                                            | 76                                                                   | M12                               |                                                                                           | audio master external clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ITRDY 7                                                                             | 77                                                                   | N12                               | l/pu                                                                                      | target ready input for image port data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DNC0                                                                                | 78                                                                   | P13                               | I/pu                                                                                      | do not connect, reserved for future extensions and for testing: scan input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DNC16                                                                               | 79                                                                   | N13                               | NC                                                                                        | do not connect, reserved for future extensions and for testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DNC17 8                                                                             | 80                                                                   | N14                               | NC                                                                                        | do not connect, reserved for future extensions and for testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DNC19 8                                                                             | 81                                                                   | -                                 | NC                                                                                        | do not connect, reserved for future extensions and for testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DNC20 8                                                                             | 82                                                                   | -                                 | NC                                                                                        | do not connect, reserved for future extensions and for testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| FSW 8                                                                               | 83                                                                   | M13                               | I/pd                                                                                      | fast switch (blanking) with internal pull-down inserts component inputs into CVBS signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

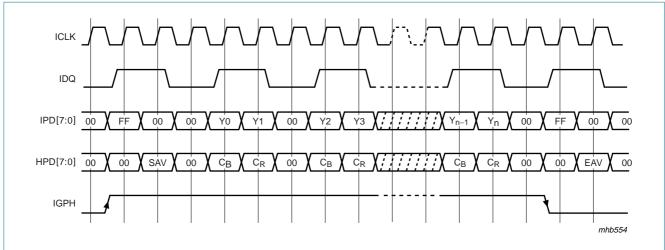

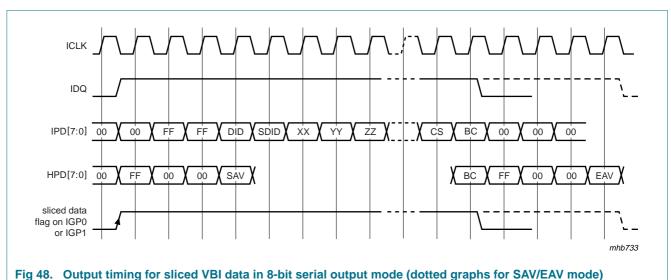

| ICLK 8                                                                              | 84                                                                   | M14                               | I/O                                                                                       | clock output signal for image port, or optional asynchronous back-end clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| IDQ 8                                                                               | 85                                                                   | L13                               | 0                                                                                         | output data qualifier for image port (optional: gated clock output)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ITRI 8                                                                              | 86                                                                   | L12                               | I(/O)                                                                                     | image port output control signal, affects all input port pins inclusive ICLK, enable and active polarity is under software control (bits IPE in subaddress 87h); output path used for testing: scan output                                                                                                                                                                                                                                                                                                                                                                                              |

Table 4.

Pin description ...continued

| Symbol            | Pin    |         | Type[1] | Description                                                                                                                          |  |  |  |

|-------------------|--------|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                   | QFP160 | LBGA156 |         |                                                                                                                                      |  |  |  |

| GP0               | 87     | L14     | 0       | general purpose output signal 0; image port (controlled by subaddresses 84h and 85h)                                                 |  |  |  |

| V <sub>SSD5</sub> | 88     | L11     | Р       | digital ground 5 (peripheral cells)                                                                                                  |  |  |  |

| IGP1              | 89     | K13     | 0       | general purpose output signal 1; image port (controlled by subaddresses 84h and 85h)                                                 |  |  |  |

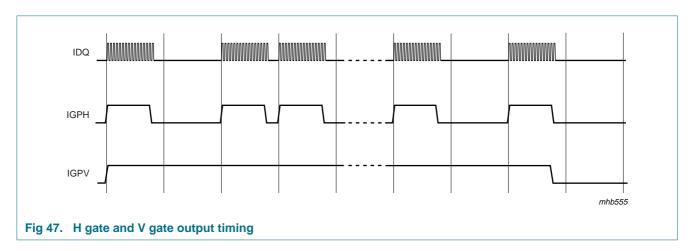

| IGPV              | 90     | K14     | 0       | multi purpose vertical reference output signal; image port (controlle by subaddresses 84h and 85h)                                   |  |  |  |

| IGPH              | 91     | K12     | 0       | multi purpose horizontal reference output signal; image port (controlled by subaddresses 84h and 85h)                                |  |  |  |

| IPD7              | 92     | K11     | 0       | MSB of image port data output                                                                                                        |  |  |  |

| IPD6              | 93     | J13     | 0       | MSB – 1 of image port data output                                                                                                    |  |  |  |

| IPD5              | 94     | J14     | 0       | MSB – 2 of image port data output                                                                                                    |  |  |  |

| V <sub>DDD6</sub> | 95     | J12     | Р       | digital supply voltage 6 (core)                                                                                                      |  |  |  |

| V <sub>SSD6</sub> | 96     | J11     | Р       | digital ground 6 (core)                                                                                                              |  |  |  |

| IPD4              | 97     | H13     | 0       | MSB – 3 of image port data output                                                                                                    |  |  |  |

| IPD3              | 98     | H14     | 0       | MSB – 4 of image port data output                                                                                                    |  |  |  |

| IPD2              | 99     | H11     | 0       | MSB – 5 of image port data output                                                                                                    |  |  |  |

| PD1               | 100    | G12     | 0       | MSB – 6 of image port data output                                                                                                    |  |  |  |

| √ <sub>DDD7</sub> | 101    | H12     | Р       | digital supply voltage 7 (peripheral cells)                                                                                          |  |  |  |

| PD0               | 102    | G14     | 0       | LSB of image port data output                                                                                                        |  |  |  |

| HPD7              | 103    | G13     | I/O     | MSB of host port data I/O, extended $C_B$ - $C_R$ input for expansion por extended $C_B$ - $C_R$ output for image port               |  |  |  |

| V <sub>SSD7</sub> | 104    | G11     | Р       | digital ground 7 (peripheral cells)                                                                                                  |  |  |  |

| HPD6              | 105    | F14     | I/O     | MSB $-$ 1 of host port data I/O, extended $C_B$ - $C_R$ input for expansion port, extended $C_B$ - $C_R$ output for image port       |  |  |  |

| $V_{\rm DDD8}$    | 106    | F12     | Р       | digital supply voltage 8 (core)                                                                                                      |  |  |  |

| HPD5              | 107    | F13     | I/O     | MSB $-$ 2 of host port data I/O, extended $C_B$ - $C_R$ input for expansion port, extended $C_B$ - $C_R$ output for image port       |  |  |  |

| V <sub>SSD8</sub> | 108    | F11     | Р       | digital ground 8 (core)                                                                                                              |  |  |  |

| HPD4              | 109    | E14     | I/O     | MSB $-$ 3 of host port data I/O, extended $C_B$ - $C_R$ input for expansion port, extended $C_B$ - $C_R$ output for image port       |  |  |  |

| HPD3              | 110    | E12     | I/O     | MSB $-$ 4 of host port data I/O, extended $C_B$ - $C_R$ input for expansion port, extended $C_B$ - $C_R$ output for image port       |  |  |  |

| HPD2              | 111    | E13     | I/O     | MSB $-$ 5 of host port data I/O, extended $C_B\text{-}C_R$ input for expansion port, extended $C_B\text{-}C_R$ output for image port |  |  |  |

| HPD1              | 112    | E11     | I/O     | MSB $-$ 6 of host port data I/O, extended $C_B\text{-}C_R$ input for expansion port, extended $C_B\text{-}C_R$ output for image port |  |  |  |

| HPD0              | 113    | D14     | I/O     | LSB of host port data I/O, extended $C_B\text{-}C_R$ input for expansion port extended $C_B\text{-}C_R$ output for image port        |  |  |  |

| $V_{\rm DDD9}$    | 114    | D12     | Р       | digital supply voltage 9 (peripheral cells)                                                                                          |  |  |  |

| DNC1              | 115    | D13     | l/pu    | do not connect, reserved for future extensions and for testing: scan input                                                           |  |  |  |

| DNC2              | 116    | C14     | l/pu    | do not connect, reserved for future extensions and for testing: scan input                                                           |  |  |  |

Table 4. Pin description ... continued

| Symbol             | Pin    |         | Type[1] | Description                                                                                                                                                                     |  |  |  |

|--------------------|--------|---------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Ī                  | QFP160 | LBGA156 |         |                                                                                                                                                                                 |  |  |  |

| DNC7               | 117    | B13     | NC      | do not connect, reserved for future extensions and for testing                                                                                                                  |  |  |  |

| DNC8               | 118    | B14     | NC      | do not connect, reserved for future extensions and for testing                                                                                                                  |  |  |  |

| DNC11              | 119    | C12     | NC      | do not connect, reserved for future extensions and for testing                                                                                                                  |  |  |  |

| DNC12              | 120    | C13     | NC      | do not connect, reserved for future extensions and for testing                                                                                                                  |  |  |  |

| DNC21              | 121    | -       | NC      | do not connect, reserved for future extensions and for testing                                                                                                                  |  |  |  |

| DNC22              | 122    | -       | NC      | do not connect, reserved for future extensions and for testing                                                                                                                  |  |  |  |

| DNC3               | 123    | A13     | l/pu    | do not connect, reserved for future extensions and for testing: scan input                                                                                                      |  |  |  |

| DNC4               | 124    | B12     | 0       | do not connect, reserved for future extensions and for testing: scan output                                                                                                     |  |  |  |

| DNC5               | 125    | A12     | l/pu    | do not connect, reserved for future extensions and for testing: scan input                                                                                                      |  |  |  |

| XTRI               | 126    | B11     | I       | X port output control signal, affects all X port pins (XPD7 to XPD0, XRH, XRV, XDQ and XCLK), enable and active polarity is under software control (bits XPE in subaddress 83h) |  |  |  |

| XPD7               | 127    | C11     | I/O     | MSB of expansion port data                                                                                                                                                      |  |  |  |

| XPD6               | 128    | A11     | I/O     | MSB – 1 of expansion port data                                                                                                                                                  |  |  |  |

| $V_{SSD9}$         | 129    | D11     | Р       | digital ground 9 (peripheral cells)                                                                                                                                             |  |  |  |

| XPD5               | 130    | B10     | I/O     | MSB – 2 of expansion port data                                                                                                                                                  |  |  |  |

| XPD4               | 131    | A10     | I/O     | MSB – 3 of expansion port data                                                                                                                                                  |  |  |  |

| $V_{DDD10}$        | 132    | C10     | Р       | digital supply voltage 10 (core)                                                                                                                                                |  |  |  |

| $V_{\text{SSD10}}$ | 133    | D10     | Р       | digital ground 10 (core)                                                                                                                                                        |  |  |  |

| XPD3               | 134    | B9      | I/O     | MSB – 4 of expansion port data                                                                                                                                                  |  |  |  |

| XPD2               | 135    | A9      | I/O     | MSB – 5 of expansion port data                                                                                                                                                  |  |  |  |

| $V_{DDD11}$        | 136    | C9      | Р       | digital supply voltage 11 (peripheral cells)                                                                                                                                    |  |  |  |

| $V_{SSD11}$        | 137    | D9      | Р       | digital ground 11 (peripheral cells)                                                                                                                                            |  |  |  |

| XPD1               | 138    | B8      | I/O     | MSB – 6 of expansion port data                                                                                                                                                  |  |  |  |

| XPD0               | 139    | A8      | I/O     | LSB of expansion port data                                                                                                                                                      |  |  |  |

| XRV                | 140    | D8      | I/O     | vertical reference I/O expansion port                                                                                                                                           |  |  |  |

| XRH                | 141    | C7      | I/O     | horizontal reference I/O expansion port                                                                                                                                         |  |  |  |

| $V_{DDD12}$        | 142    | C8      | Р       | digital supply voltage 12 (core)                                                                                                                                                |  |  |  |

| XCLK               | 143    | A7      | I/O     | clock I/O expansion port                                                                                                                                                        |  |  |  |

| XDQ                | 144    | B7      | I/O     | data qualifier for expansion port                                                                                                                                               |  |  |  |

| $V_{\text{SSD12}}$ | 145    | D7      | Р       | digital ground 12 (core)                                                                                                                                                        |  |  |  |

| XRDY               | 146    | A6      | 0       | task flag or ready signal from scaler, controlled by XRQT                                                                                                                       |  |  |  |

| TRST               | 147    | C6      | l/pu    | test reset input (active LOW), for boundary scan test (with internal pull-up)[5][6][7]                                                                                          |  |  |  |

| TCK                | 148    | B6      | I/pu    | test clock for boundary scan test[5]                                                                                                                                            |  |  |  |

| TMS                | 149    | D6      | I/pu    | test mode select input for boundary scan test or scan test[5]                                                                                                                   |  |  |  |

| TDO                | 150    | A5      | 0       | test data output for boundary scan test[5]                                                                                                                                      |  |  |  |

| $V_{DDD13}$        | 151    | C5      | Р       | digital supply voltage 13 (peripheral cells)                                                                                                                                    |  |  |  |

Table 4. Pin description ... continued

| Symbol                | Pin    |         | Type[1] | Description                                                                                                                                    |

|-----------------------|--------|---------|---------|------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | QFP160 | LBGA156 |         |                                                                                                                                                |

| TDI                   | 152    | B5      | l/pu    | test data input for boundary scan test[5]                                                                                                      |

| V <sub>SSD13</sub>    | 153    | D5      | Р       | digital ground 13 (peripheral cells)                                                                                                           |

| V <sub>SS(xtal)</sub> | 154    | A4      | Р       | ground for crystal oscillator                                                                                                                  |

| XTALI                 | 155    | B4      | I       | input terminal for 24.576 MHz (32.11 MHz) crystal oscillator or connection of external oscillator with TTL compatible square wave clock signal |

| XTALO                 | 156    | A3      | 0       | 24.576 MHz (32.11 MHz) crystal oscillator output; not connected if TTL clock input of XTALI is used                                            |

| V <sub>DD(xtal)</sub> | 157    | В3      | Р       | supply voltage for crystal oscillator                                                                                                          |

| XTOUT                 | 158    | A2      | 0       | crystal oscillator output signal; auxiliary signal                                                                                             |

| DNC9                  | 159    | C3      | NC      | do not connect, reserved for future extensions and for testing                                                                                 |

| DNC10                 | 160    | C4      | NC      | do not connect, reserved for future extensions and for testing                                                                                 |

- [1] I = input, O = output, P = power, NC = not connected, st = strapping, pu = pull-up, pd = pull-down, od = open-drain.

- [2] Pin strapping is done by connecting the pin to the supply via a 3.3 kΩ resistor. During the power-up reset sequence the corresponding pins are switched to input mode to read the strapping level. For the default setting no strapping resistor is necessary (internal pull-down).

- [3] Pin RTCO operates as I<sup>2</sup>C-bus slave address pin; RTCO = 0 slave address 42h/43h (default); RTCO = 1 slave address 40h/41h.

- [4] Pin ALRCLK = LOW for 24.576 MHz crystal (default); pin ALRCLK = HIGH for 32.110 MHz crystal.

- [5] In accordance with the "IEEE1149.1" standard the pads TDI, TMS, TCK and TRST are input pads with an internal pull-up transistor and TDO is a 3-state output pad.

- [6] For board design without boundary scan implementation connect the  $\overline{TRST}$  pin to ground.

- [7] This pin provides easy initialization of the Boundary Scan Test (BST) circuit. TRST can be used to force the Test Access Port (TAP) controller to the TEST\_LOGIC\_RESET state (normal operation) at once.

Multistandard video decoder with adaptive comb filter

IPE[1:0] 87h[1:0] + pin ITRI

IPE[1:0] 87h[1:0] + pin ITRI

ICKS[1:0] 80h[1:0], IPE[1:0] 87h[1:0] + pin ITRI

ICKS[3:2] 80h[3:2], IDQP[85h[0]],

clock input

gated clock

output

NXP

Semiconductors

clock output

data qualifier

output

99, 100, 102)

**ICLK**

IDQ

M14 (84)

L13 (85)

Product data sheet

Table 5.

8-bit/16-bit and alternative pin function configurations ...continued

| 47118_7 | Pin[1]   | Symbol | Input                |                                                                         |                             | Output              |                                                                          |                                             | I/O configuration                                                    |

|---------|----------|--------|----------------------|-------------------------------------------------------------------------|-----------------------------|---------------------|--------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------|

|         |          |        | 8-bit input<br>modes | 16-bit input<br>modes (only<br>for I <sup>2</sup> C-bus<br>programming) | Alternative input functions | 8-bit output modes  | 16-bit output<br>modes (only<br>for I <sup>2</sup> C-bus<br>programming) | Alternative output functions                | programming bits                                                     |

|         | N12 (77) | ITRDY  | -                    | -                                                                       | -                           | target ready input  | -                                                                        | -                                           | -                                                                    |

|         | K12 (91) | IGPH   | -                    | -                                                                       | -                           | H gate output       | -                                                                        | extended<br>H gate,<br>horizontal<br>pulses | IDH[1:0] 84h[1:0],<br>IRHP[85h[1]],<br>IPE[1:0] 87h[1:0] + pin ITRI  |

|         | K14 (90) | IGPV   | -                    | -                                                                       | -                           | V gate output       | -                                                                        | V-sync,<br>vertical pulses                  | IDV[1:0] 84h[3:2],<br>IRVP[85h[2]],<br>IPE[1:0] 87h[1:0] + pin ITRI  |

|         | K13 (89) | IGP1   | -                    | -                                                                       | -                           | general purpose     | -                                                                        | -                                           | IDG1[1:0] 84h[5:4],<br>IG1P[85h[3]],<br>IPE[1:0] 87h[1:0] + pin ITRI |

|         | L14 (87) | IGP0   | -                    | -                                                                       | -                           | general purpose     | -                                                                        | -                                           | IDG0[1:0] 84h[7:6],<br>IG0P[85h[4]],<br>IPE[1:0] 87h[1:0] + pin ITRI |

|         | L12 (86) | ITRI   | -                    | -                                                                       | -                           | output enable input | -                                                                        | -                                           | -                                                                    |

<sup>[1]</sup> Pin numbers for QFP160 in parenthesis.

**SAA7118 NXP Semiconductors**

Multistandard video decoder with adaptive comb filter

### **Functional description**

### 8.1 Decoder

### 8.1.1 Analog input processing

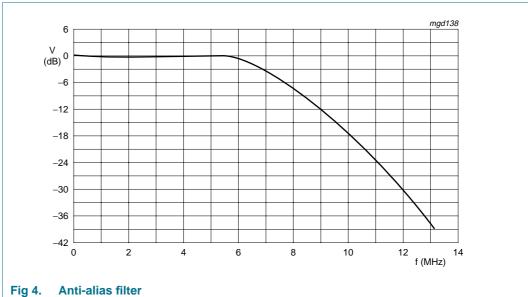

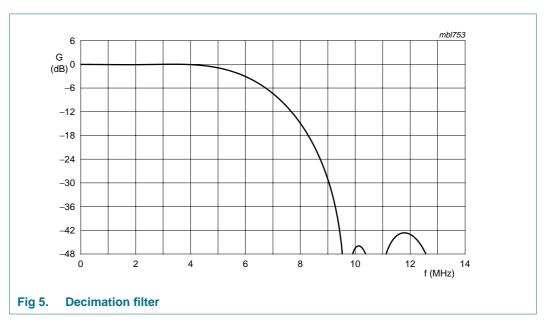

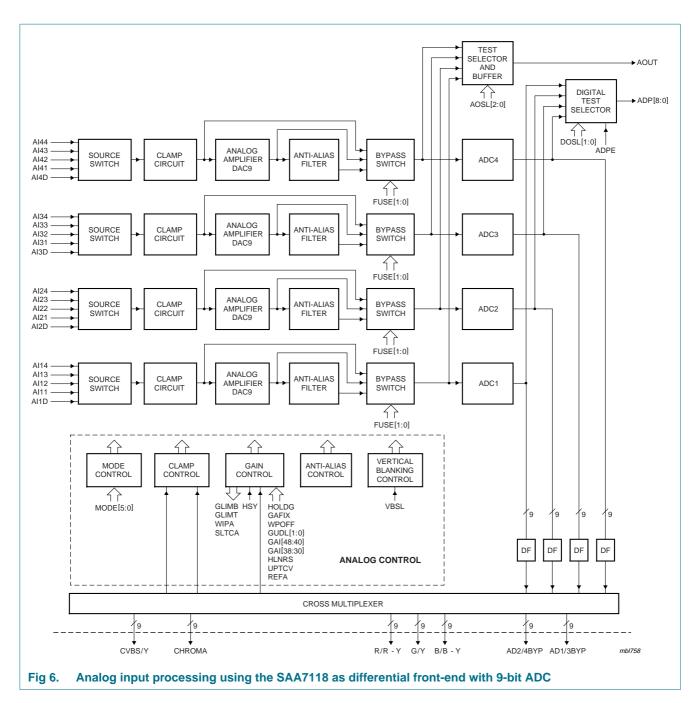

The SAA7118 offers sixteen analog signal inputs, four analog main channels with source switch, clamp circuit, analog amplifier, anti-alias filter and video 9-bit CMOS ADC with a Decimation Filter (DF); see Figure 5 and Figure 6.

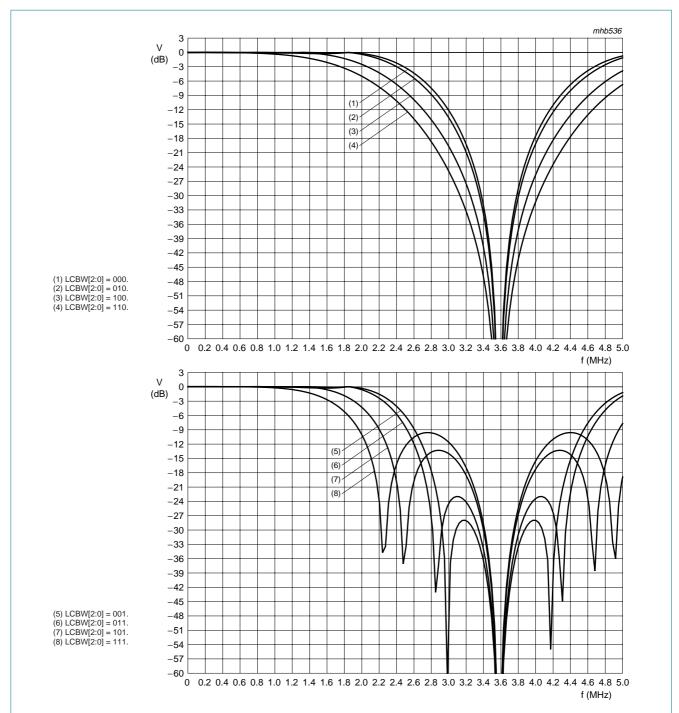

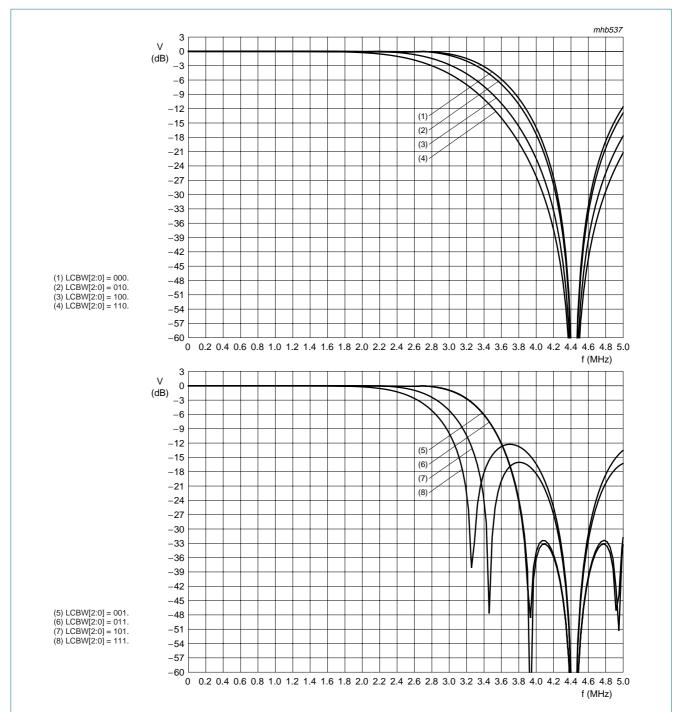

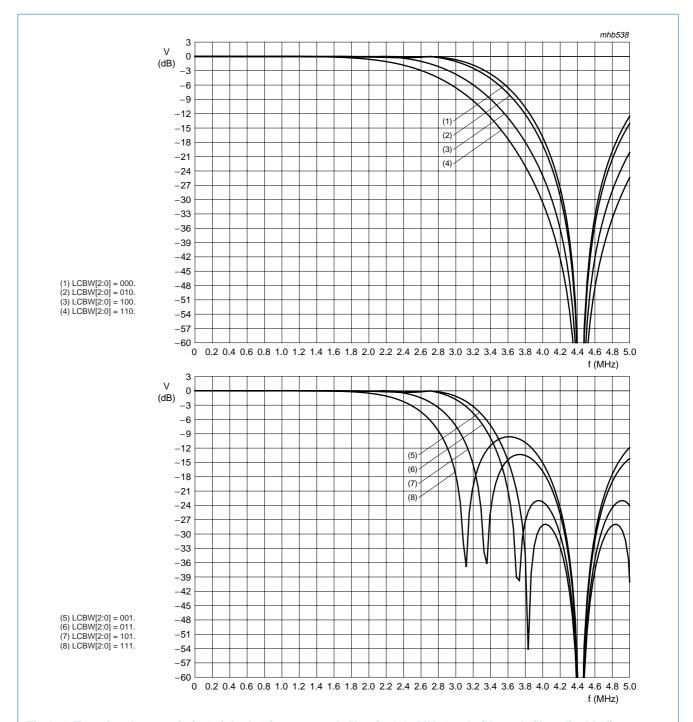

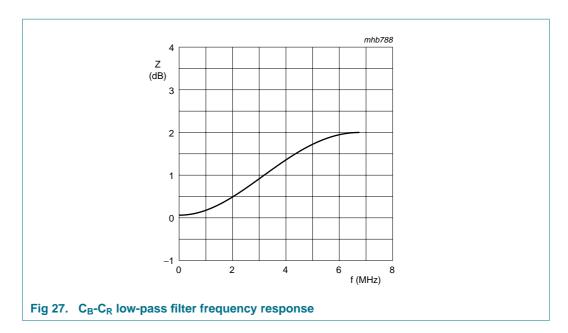

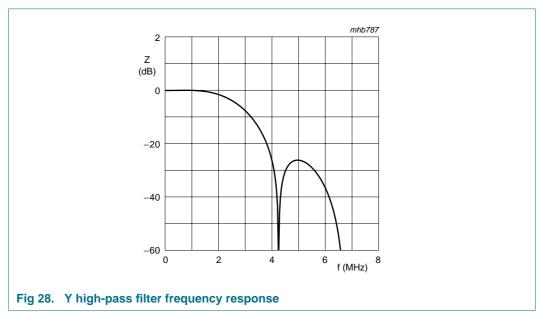

The anti-alias filters are adapted to the line-locked clock frequency via a filter control circuit. The characteristic is shown in Figure 4. During the vertical blanking period gain and clamping control are frozen.

### Multistandard video decoder with adaptive comb filter

### **8.1.1.1 Clamping**

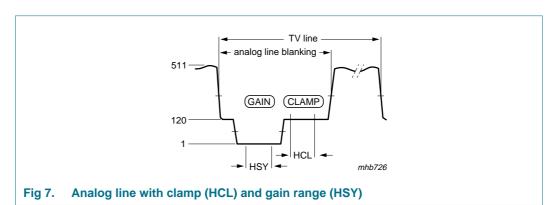

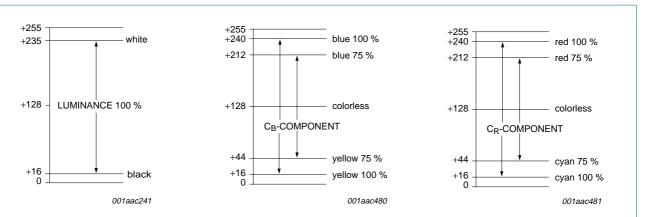

The clamp control circuit controls the correct clamping of the analog input signals. The coupling capacitor is also used to store and filter the clamping voltage. An internal digital clamp comparator generates the information with respect to clamp-up or clamp-down. The clamping levels for the four ADC channels are fixed for luminance (120), chrominance (256) and for component inputs as component Y (32), components  $P_B$  and  $P_R$  (256) or components RGB (32). Clamping time in normal use is set with the HCL pulse on the back porch of the video signal.

### Multistandard video decoder with adaptive comb filter

### 8.1.1.2 Gain control

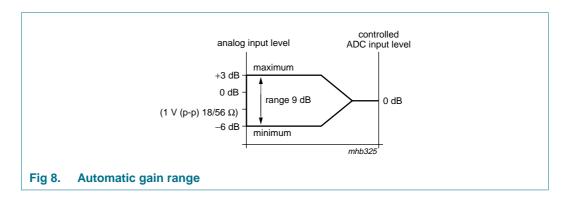

The gain control circuit receives (via the I<sup>2</sup>C-bus) the static gain levels for the four analog amplifiers or controls one of these amplifiers automatically via a built-in Automatic Gain Control (AGC) as part of the Analog Input COntrol (AICO).

The AGC for luminance is used to amplify a CVBS or Y signal to the required signal amplitude, matched to the ADCs input voltage range. Component inputs are gain adjusted manually at a fixed gain. The AGC active time is the sync bottom of the video signal.

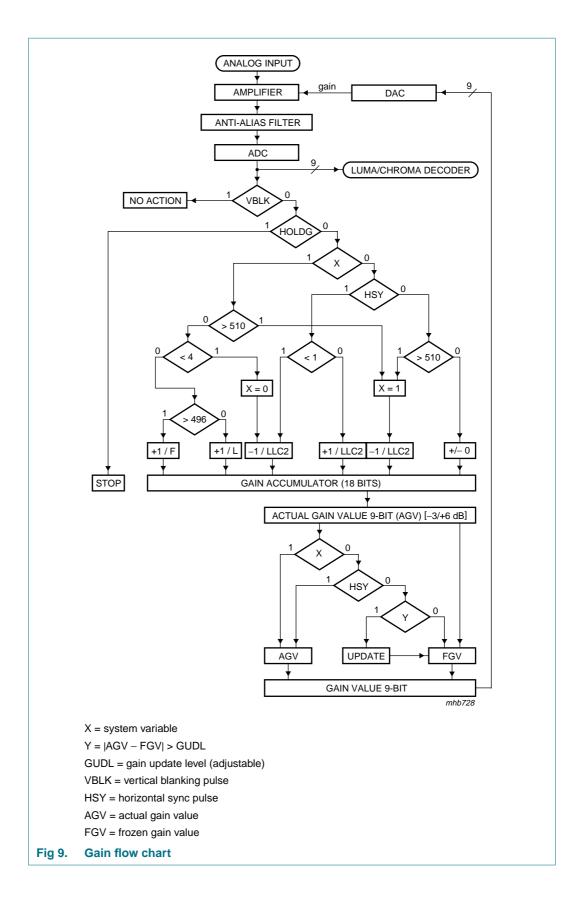

Signal (white) peak control limits the gain at signal overshoots. The flow charts (see Figure 9 and Figure 10) show more details of the AGC. The influence of supply voltage variation within the specified range is automatically eliminated by clamp and automatic gain control.

Multistandard video decoder with adaptive comb filter

**Product data**

sheet

Rev.

07

Ÿ

**July 2008**

### Multistandard video decoder with adaptive comb filter

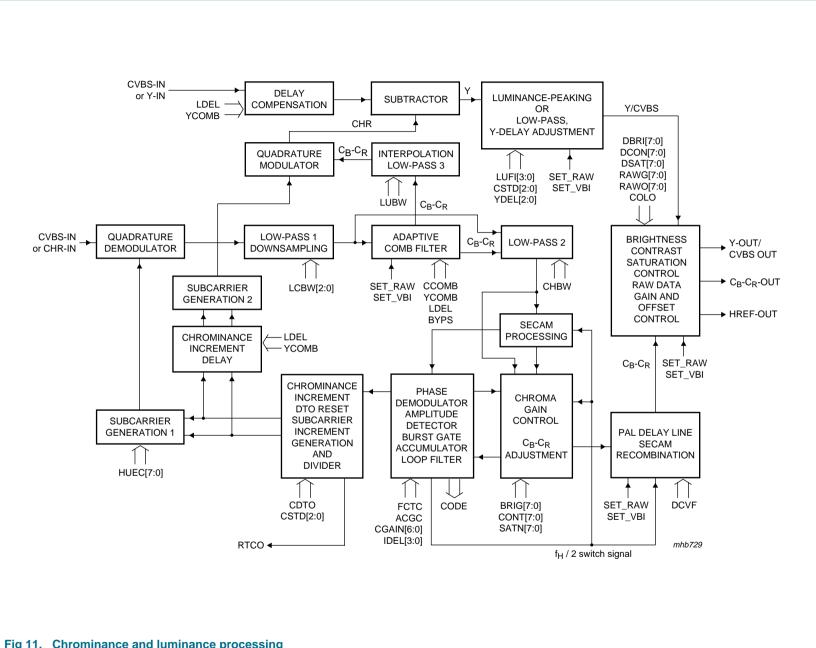

### 8.1.2.1 Chrominance path