NXP bidirectional low-voltage translators GTL20xx

# Low cost bidirectional voltage translation without directional control

Unlike level-shifting bus switches, which only translate between fixed voltages, these bidirectional low-voltage translators can translate any voltage between 1 and 5 V to any other voltage between 1 and 5 V. They also reduce ON-state resistance and minimize propagation delay.

## **Key features**

- No directional control required for bidirectional voltage translations

- Low RON resistance (6.5 Ω) between input and output pins (Sn/Dn)

- Propagation delay: 1.5 ns (typ)

- Channel off-state capacitance: 7.5 pF

- Very low (5 μA) standby current

- No power supply required prevents latch-ups

- Very small QFN package options

# Applications

- Uni- and bidirectional translation for any voltage between 1 and 5 V

- Bidirectional translation of lowvoltage and legacy I<sup>2</sup>C-bus signals

- Shifting processor sideband I/O signals between GTL and LVTTL/TTL levels

The NXP family of Gunning Transceiver Logic (GTL) bidirectional low-voltage translators includes the 22-bit GTL2000, the 2-bit GTL2002, the 8-bit GTL2003, and the 10-bit GTL2010.

Each delivers high-speed translation between different voltage levels with low ON-state resistance and minimal propagation delay.

They can translate any voltage between 1 and 5 V to any other voltage between 1 and 5 V as long as there is at least 1 V difference between the voltage levels, so they offer greater design flexibility than level-shifting bus switches, which only translate between fixed voltages.

Each GTL20xx device includes NMOS pass transistors (Sn and Dn pins) with a common gate ( $G_{REF}$  pin) and a reference transistor ( $S_{REF}$  and  $D_{REF}$  pins).

When one of the Sn or Dn ports is low, the clamp is in the ON-state and the Sn and Dn ports are linked through a low ON-resistance connection. Assuming the higher voltage is applied on the Dn port, when the Dn port is high, the voltage on the Sn port is limited to the voltage set by  $S_{REF}$ . When the Sn port is high, the Dn port is pulled to a higher voltage by a pull-up resistor.

This set-up enables seamless translation between user-selected voltages, without the need for directional control signals. All transistors have the same electrical characteristics so deviation from one output to another in voltage and propagation delay is kept to a minimum. The transistors also provide excellent ESD protection in case the low-voltage devices that are less resistant to ESD.

The translators can be used in any

application that requires uni- or bidirectional voltage translation for voltage levels between 1 and 5 V. The open-drain construction, which eliminates the need for directional control, makes the translators ideal for designs that combine low-voltage (1.0 to 1.8 V) and legacy (3.3 and/or 5.5 V) I<sup>2</sup>Cbus signals. The translators can change I<sup>2</sup>C-bus signal levels at speeds up to 3.4 MHz.

The translators can also be used in designs that combine GTL and LVTTL/ TTL signals, shifting processor sideband I/O signals between voltage levels.

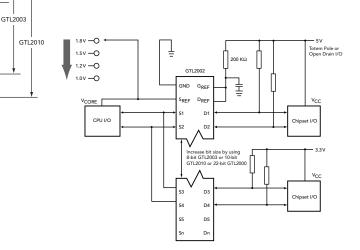

## **Bidirectional voltage translation**

To configure the translators for bidirectional clamping, the  $G_{RFF}$  input must be connected to  $\mathsf{D}_{\scriptscriptstyle \mathsf{RFF}}$  and both pins must be pulled to the high-side V<sub>cc</sub> through a pull-up resistor (typically 200 k $\Omega$ ). A filter capacitor on D<sub>RFF</sub> is recommended.

The CPU output can be set as totem pole or open drain (pull-up resistors may be required), as can the chipset output (pull-up resistors are required to pull the Dn outputs to  $V_{\rm CC}$ ). No directional control is needed if both outputs are set as open drain. If either output is set to totem pole, however, there may be highto-low contentions in either direction. To prevent this, set data as unidirectional or use 3-stateable outputs with a mechanism for direction control.

The opposite side of  $S_{RFF}$  is connected to the CPU power-supply voltage. When  $\mathsf{D}_{_{\text{RFF}}}$  is connected through a 200-k $\Omega$ resistor to  $V_{\rm\scriptscriptstyle CC}$  and  $\rm S_{\rm\scriptscriptstyle REF}$  is set between 1.0 and  $V_{cc}$  minus 1.5 V, the output of each Sn has a maximum output voltage equal

to  $S_{REE}$  and the output of each Dn has a maximum output voltage equal to the voltage of the pull-up resistor (3.3 and/or 5 V).

## **Unidirectional voltage translation**

The same configuration can be used for one-way voltage translation, either up or down. For down-only translation, if the chipset I/O are open drain, pull-up resistors are required.

48 GREF

46 D1

45 D<sub>2</sub>

44 D3 43 D4

42 D5

41 D6

40 D7

39 D8

38 D9

37 D<sub>10</sub>

36 D11

35 D12

34 D13

33 D14

32 D15 31 D16

30 D<sub>17</sub>

29 D<sub>18</sub>

28 D<sub>19</sub>

27 D<sub>20</sub>

26 D<sub>21</sub>

25 D<sub>22</sub>

GTL2000

47 D<sub>REF</sub> GTL2002

GND 1

S<sub>REF</sub> 2 S<sub>1</sub>3

S2 4

S3 5

S4 6 S5 7

S<sub>6</sub>8

S7 9

S<sub>8</sub> 10

Sg 11

S<sub>10</sub> 12

S11 13

S<sub>12</sub> 14

S<sub>13</sub> 15

S14 16

S<sub>15</sub> 17

S<sub>16</sub> 18

S<sub>17</sub> 19

S<sub>18</sub> 20

S<sub>19</sub> 21

S20 22

S<sub>21</sub> 23

S<sub>22</sub> 24

For up-only translation, a pull-up resistor is required on the high-side voltage (Dn). This is because the translator will only pass the reference source voltage (S<sub>REF</sub>) as a high when doing up-translation. The driver on the low-side voltage only needs a pull-up resistor if it is set as open drain.

For more information on using the GTL20xx family, please refer to Application Note AN10145 at www.nxp. com/interface.

GTL20xx pinout diagram

Typical configuration for bidirectional voltage translation

### **Ordering information**

| Package | Container | GTL2000      | GTL2002     | GTL2003     | GTL2010     |

|---------|-----------|--------------|-------------|-------------|-------------|

| SO      | Tube      |              | GTL2002D    |             |             |

|         | T&R       |              | GTL2002D-T  |             |             |

| SSOP    | Tube      | GTL2000DL    |             |             |             |

|         | T&R       | GTL2000DL-T  |             |             |             |

| TSSOP   | Tube      | GTL2000DGG   |             | GTL2003PW   | GTL2010PW   |

|         | T&R       | GTL2000DGG-T | GTL2002DP-T | GTL2003PW-T | GTL2010PW-T |

| HVQFN   | T&R       |              |             |             | GTL2010BS-T |

| DHVQFN  | T&R       |              |             | GTL2003BQ-T |             |

| VSSOP   | T&R       |              | GTL2002DC-T |             |             |

| XQFN    | T&R       |              | GTL2002GM-T |             |             |

Note: In Europe and Asia, for tube orders, add ", 112" (e.g. GTL2010PW, 112), and for tape and reel orders, replace "-T" with ", 118" (e.g. GTL2010PW, 118).

#### www.nxp.com

#### © 2007 NXP N.V

All rights reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent or other industrial or intellectual property rights

Date of release: March 2007 Document order number: 9397 750 15911 Printed in the USA