Thick-Film Hybrid IC

# **3-phase Brush-less DC Motor Driver IC**

#### Overview

The STK984-091A-E is a hybrid IC designed to be used in Brush-less DC Motor.

#### **Application**

• Industrial - Motor Drive

#### **Features**

- FET can be driven (built-in pre-driver IC) by microcontroller output (logic system).

- Various protections (Overcurrent Protection, Over Temperature Protection, Low Voltage Protection, Over Voltage Protection) are incorporated.

- Intelligent DIAG Function that externally outputs each protection status, such as Overcurrent Protection, Over Temperature Protection.

- Protection functions can be reset by external inputs.

#### Series model

|        | STK984-091A-E | STK984-090A-E |

|--------|---------------|---------------|

| VB max | 40V           | 40V           |

| ld max | 20A           | 20A           |

| IOC    | 91-170A       | 68-160A       |

| ISD    | 48-90A        | 22-65A        |

| TSD    | 135-145°C     | 126-136°C     |

#### **Specifications**

#### **Absolute Maximum Ratings** at Ta = 25°C, Tc = 25°C

| Parameter             | Symbol              | Conditions                      | Ratings     | Unit |

|-----------------------|---------------------|---------------------------------|-------------|------|

| Supply voltage        | V+B1                | +B1 to PG                       | 0.04.40     | .,,  |

|                       | V+B2                | +B2 to SG                       | -0.3 to 40  | V    |

| Control input voltage | V <sub>IN</sub> max | UT, VT, WT, UB, VB, WB to SG    | -0.3 to 6   | V    |

| DIAG terminal voltage | VDIAG               | DIAG1, DIAG2 to SG              | -0.3 to 6   | V    |

| Drain current         | ld max              | DC                              | 20          | Α    |

|                       |                     | Pulse (Single-Shot within 10μs) | 180         | Α    |

| Junction temperature  | Tj max              | Semiconductor device            | 150         | °C   |

| Storage temperature   | Tstg                |                                 | -40 to +125 | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 7 of this data sheet.

# Recommended Operating Conditions at -40°C $\leq$ Tc $\leq$ 125°C

| Parameter                       | Symbol | Test Conditions                                                   | min | typ  | max | Unit |

|---------------------------------|--------|-------------------------------------------------------------------|-----|------|-----|------|

| Supply voltage                  | V+B1   | +B1 to PG                                                         |     |      | 40  | .,,  |

|                                 | V+B2   | +B2 to SG                                                         | 8   | 13.5 | 18  | V    |

| Output current                  | lo     | I <sub>O</sub> ∞ ON duty, ON duty100%<br>120deg excitation method |     |      | 20  | А    |

| Operating substrate temperature | Тс     | Thick film IC substrate temperature                               | -40 |      | 125 | °C   |

| Drive PWM frequency             | FO     | ONDuty: 10 to 90%, 100%                                           |     |      | 20  | kHz  |

#### **Thermal Resistance**

| Parameter            | Symbol | Test Conditions                         | min | typ | max | Unit  |

|----------------------|--------|-----------------------------------------|-----|-----|-----|-------|

| Chip-case resistance | θјс    | Junction -to- backside of the substrate |     | 4.5 |     | °C/W  |

|                      |        | MOSFET/ch                               |     | 4.5 |     | -0/00 |

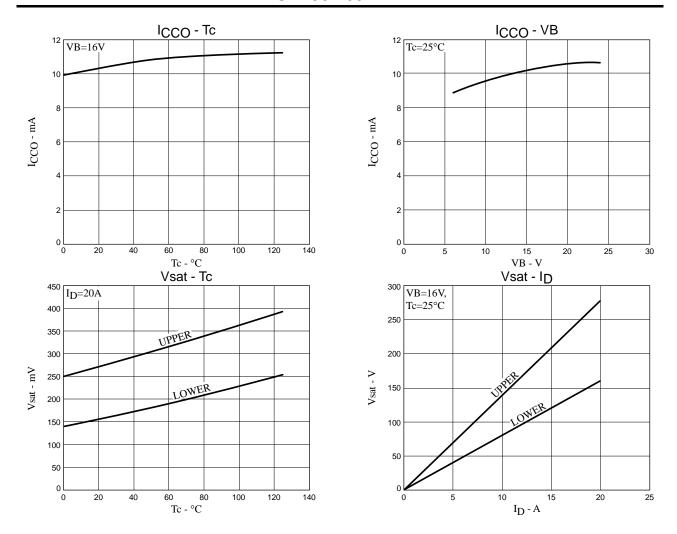

# **Electrical Characteristics** at Ta = 25°C, V+B1 (V+B2) = 13.5V unless otherwise specifed

| Parameter                            | Symbol                | Tes                 | Test Conditions |      | typ  | max  | Unit |

|--------------------------------------|-----------------------|---------------------|-----------------|------|------|------|------|

| Current consumption (Control system) | ICC                   | V+B1=V+B2=16V       |                 |      | 10   | 15   | mA   |

| Output saturation voltage            | V <sub>DS</sub> (sat) | I <sub>O</sub> =20A | +B1 to U, V, W  |      | 0.3  | 0.5  | .,   |

|                                      |                       |                     | U, V, W to PG   |      | 0.2  | 0.4  | V    |

| Current sensing resistor             | Rs                    |                     |                 | 2.91 | 3.00 | 3.09 | mΩ   |

| Time delay (ON)                      | td(on)                | 20A                 | U, V, W         | 0.9  | 1.8  | 2.8  |      |

|                                      |                       |                     | U-, V-, W-      | 0.9  | 1.9  | 3.0  | μS   |

| Rise time                            | tr                    | 20A                 |                 |      | 0.3  |      | μS   |

| Time delay (OFF)                     | td(off)               | 20A                 | U, V, W         | 1.3  | 2.9  | 4.5  |      |

|                                      |                       |                     | U-, V-, W-      | 0.8  | 2.2  | 3.5  | μS   |

| Fall time                            | tf                    | 20A                 |                 |      | 0.3  |      | μS   |

#### Motor Control Input Terminal at $8V \le V + B1$ $(V + B2) \le 18V$ , $-40^{\circ}C \le Ta \le 125^{\circ}C$

| Parameter         | Symbol                | Test Conditions                         | min | typ | max | Unit |

|-------------------|-----------------------|-----------------------------------------|-----|-----|-----|------|

| Input ON voltage  | V <sub>IN</sub> (on)  | Output on UT, VT, WT, UB, VB, WB to SG  | 3.5 |     |     | V    |

| Input OFF voltage | V <sub>IN</sub> (off) | Output off UT, VT, WT, UB, VB, WB to SG |     |     | 1.5 | V    |

#### Reset Input Terminal at $8V \le V + B1$ (V+B2) $\le 18V$ , $-40^{\circ}C \le Ta \le 125^{\circ}C$

| 10000 mput 10 mmut 400 y = +121 (+122) = 10+1, 10 0 = 14 = 120 0 |             |                                                    |     |      |     |      |

|------------------------------------------------------------------|-------------|----------------------------------------------------|-----|------|-----|------|

| Parameter                                                        | Symbol      | Test Conditions                                    | min | typ  | max | Unit |

| Reset high voltage                                               | Vreset(Hi)  | Output ON                                          | 3.5 |      |     | V    |

| Reset low voltage                                                | Vreset(Lo)  | Output OFF                                         |     |      | 1.5 | V    |

| Output delay time (ON)                                           | treset(on)  | From reset input terminal (RESET=Hi) to output ON  |     | 0.25 |     | ms   |

| Output delay time (OFF)                                          | treset(off) | From reset input terminal (RESET=Lo) to output OFF |     | 2    |     | μS   |

**Protective Function** at  $Ta = 25^{\circ}C$ , V+B1 (V+B2) = 13.5V unless otherwise specified

| Parameter                                                   | Symbol   | Test Conditions                                            | min  | typ  | max | Unit |

|-------------------------------------------------------------|----------|------------------------------------------------------------|------|------|-----|------|

| Low voltage protection threshold                            | Vuv      |                                                            | 4.45 | 4.75 | 5.1 | V    |

| Low voltage protection                                      | Vuv(hy)  |                                                            | 0.07 | 0.2  | 0.3 | V    |

| hysteresis                                                  |          |                                                            |      |      |     |      |

| Low voltage shutdown output delay                           | Tuvoff   |                                                            |      | 1.0  |     | μS   |

| Over current threshold                                      | ISD      | Automatic recovery                                         | 48   | 68   | 90  | Α    |

| Over current DIAG output delay time                         | Tocdgoff |                                                            |      | 4.3  |     | μs   |

| Over current shutdown interval                              | tint     |                                                            |      | 1    |     | ms   |

| Over current shutdown output delay                          | Tocoff   |                                                            |      | 4.3  |     | μs   |

| Ground fault short-circuit protection                       | IOC      | Power-cycle                                                | 91   | 134  | 170 | А    |

| Ground fault short-circuit detection DIAG output delay time | Tspdgoff |                                                            |      | 3.0  |     | ms   |

| Ground fault short-circuit shutdown output delay time       | Tspoff   |                                                            |      | 3.0  |     | ms   |

| Temperature protection shutdown                             | Tst      | Thick film IC substrate temperature, automatic restoration | 135  | 140  | 145 | °C   |

| Temperature protection recovery                             | Tst(hy)  | Thick film IC substrate temperature                        | 115  | 120  | 125 | °C   |

| Over temperature DIAG output delay time                     | Tthdgoff |                                                            |      | 3.4  |     | ms   |

| Over temperature shutdown output delay                      | Tthoff   |                                                            |      | 3.4  |     | μs   |

| Over voltage threshold                                      | Vov      |                                                            | 24   |      |     | V    |

| Over voltage protection hysteresis width                    | Vov(hy)  |                                                            |      | 0.5  |     | ٧    |

| Over voltage shutdown output delay                          | Tovoff   |                                                            |      | 1.0  |     | μS   |

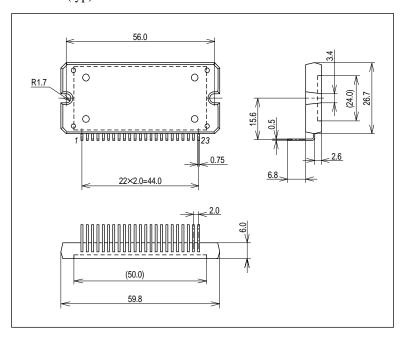

# **Package Dimensions**

unit: mm (typ)

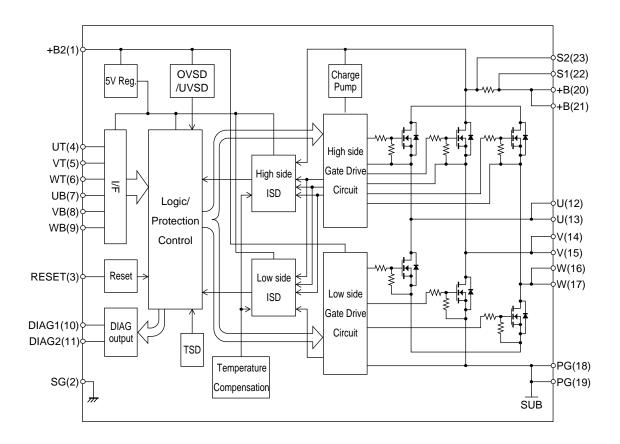

# **Internal Block Diagram**

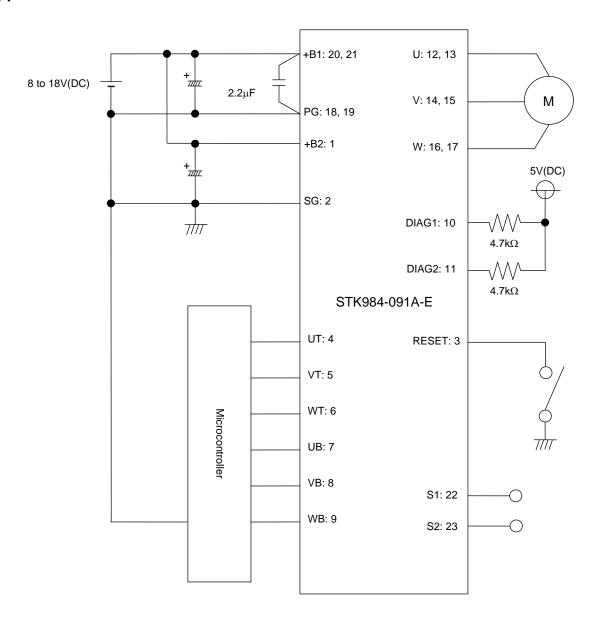

# **Application Circuit**

#### **NOTE**

- 1. A voltage overshoot with vibration will be occurred during a switching operation due to floating inductance of the power source wiring connected between terminal +B1 and PG. In order that the voltage overshoot between +B1 and PG, +B1 and each –UBW, each UVW and PG will not exceed its rating, please minimize wiring inductance by shortening the wiring, also connect a snubber circuit close to between +B1 and PG terminals.

- 2. With the object of the overcurrent protection circuit fail-safe design, inserting a fuse in +B1 line is recommended.

- 3. There is a  $100k\Omega$  (Typ) pull-down resister connected inside of the signal input terminal. However, in the case of mounting a resister externally to reduce noise due to wiring, please satisfy the input voltage threshold of this Hybrid-IC.

- 4. Terminal DIAG 1 and DIAG 2 are the open drain output configuration. Please pull up with  $4.7k\Omega$  resister to 5V power supply.

- 5. There is a  $100k\Omega$  (Typ) pull-up resister connected inside of the RESET terminal. It operates normally in the open-state. When the short-circuit protection operates and latches the output OFF, the latched output OFF can be released by making RESET terminal Low and re-opened.

**Pin Function Description**

| Pin No. | Pin Name | Description                                                                                                                                                                                                   | Pin* |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1       | +B2      | Control System Power                                                                                                                                                                                          | S    |

| 2       | SG       | Control System GND                                                                                                                                                                                            | S    |

| 3       | RESET    | RESET Terminal  Normal operating in RESET = H or Open-State  The Gate Output will be Lo-state for both Hi/Lo sides with RESET = L (Output OFF)  Output OFF Latch Release terminal of Short-circuit Protection | S    |

| 4       | UT       | Driving Signal Input Upper U-phase                                                                                                                                                                            | S    |

| 5       | VT       | Driving Signal Input Upper V-phase                                                                                                                                                                            | S    |

| 6       | WT       | Driving Signal Input Upper W-phase                                                                                                                                                                            | S    |

| 7       | UB       | Driving Signal Input Lower U-phase                                                                                                                                                                            | S    |

| 8       | VB       | Driving Signal Input Lower V-phase                                                                                                                                                                            | S    |

| 9       | WB       | Driving Signal Input Lower W-phase                                                                                                                                                                            | S    |

| 10      | DIAG1    | Fault Diagnosis Output 1 (Overcurrent) Normal Operation: Lo Abnormal Operation: Hi                                                                                                                            | S    |

| 11      | DIAG2    | Fault Diagnosis Output 2 (Over Temperature)  Normal Operation: Lo  Abnormal Operation: Hi                                                                                                                     | S    |

| 12      | U        | U-phase Output                                                                                                                                                                                                | Р    |

| 13      | U        | U-phase Output                                                                                                                                                                                                | Р    |

| 14      | V        | V-phase Output                                                                                                                                                                                                | Р    |

| 15      | V        | V-phase Output                                                                                                                                                                                                | Р    |

| 16      | W        | W-phase Output                                                                                                                                                                                                | Р    |

| 17      | W        | W-phase Output                                                                                                                                                                                                | Р    |

| 18      | PG       | Power System GND                                                                                                                                                                                              | Р    |

| 19      | PG       | Power System GND                                                                                                                                                                                              | Р    |

| 20      | +B1      | Power System Supply                                                                                                                                                                                           | Р    |

| 21      | +B1      | Power System Supply                                                                                                                                                                                           | Р    |

| 22      | S1       | Current Sense Resistor Sensing (+) terminal                                                                                                                                                                   | S    |

| 23      | S2       | Current Sense Resistor Sensing (-) terminal                                                                                                                                                                   | S    |

S: Signal terminal

P: Power terminal

#### ORDERING INFORMATION

| Device        | Package             | Shipping (Qty / Packing) |

|---------------|---------------------|--------------------------|

| STK984-091A-E | SIP-23<br>(Pb-Free) | 9 / Fan-Fold             |

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa