# Single, Dual, Quad General Purpose, Low Voltage Comparators

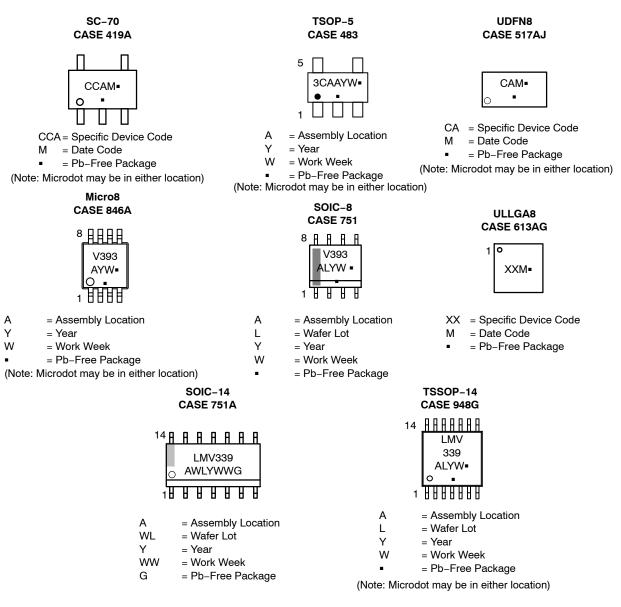

The LMV331 is a CMOS single channel, general purpose, low voltage comparator. The LMV393 and LMV339 are dual and quad channel versions, respectively. The LMV331/393/339 are specified for 2.7 V to 5 V performance, have excellent input common–mode range, low quiescent current, and are available in several space saving packages.

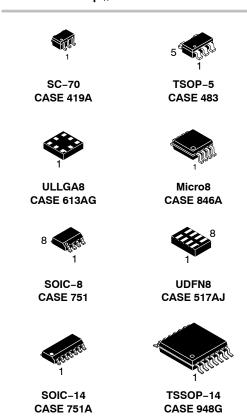

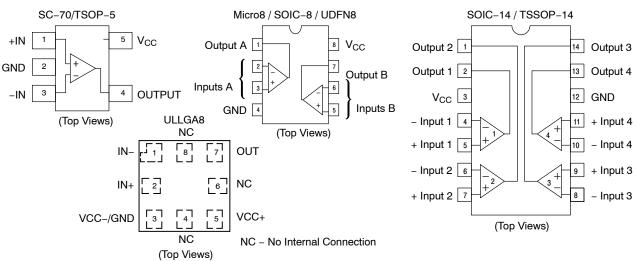

The LMV331 is available in a 5-pin SC-70, a TSOP-5, and a ULLGA8 package. The LMV393 is available in a 8-pin Micro8 $^{\text{™}}$ , SOIC-8, and a UDFN8 package, and the LMV339 is available in a SOIC-14 and a TSSOP-14 package.

The LMV331/393/339 are cost effective solutions for applications where space saving, low voltage operation, and low power are the primary specifications in circuit design for portable applications.

#### **Features**

- Guaranteed 2.7 V and 5 V Performance

- Input Common-mode Voltage Range Extends to Ground

- Open Drain Output for Wired-OR Applications

- Low Quiescent Current: 60 μA/channel TYP @ 5 V

- Low Saturation Voltage 200 mV TYP @ 5 V

- Propagation Delay 200 ns TYP @ 5 V

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- These are Pb-Free Devices

#### **Typical Applications**

- Battery Monitors

- Notebooks and PDA's

- General Purpose Portable Devices

- General Purpose Low Voltage Applications

#### ON Semiconductor®

http://onsemi.com

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 13 of this data sheet.

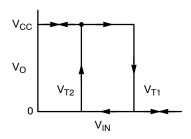

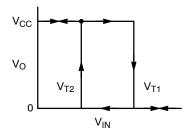

Figure 2. Hysteresis Curve

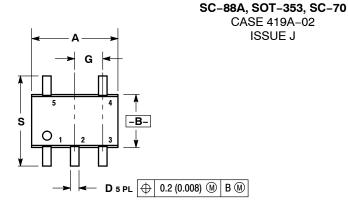

#### **MARKING DIAGRAMS**

#### **PACKAGE PINOUTS**

#### **MAXIMUM RATINGS**

| Symbol           | Rating                                                                         | Value                   | Unit |

|------------------|--------------------------------------------------------------------------------|-------------------------|------|

| Vs               | Voltage on any Pin (referred to V <sup>-</sup> pin)                            | 5.5                     | V    |

| V <sub>IDR</sub> | Input Differential Voltage Range                                               | ±Supply Voltage         | V    |

| TJ               | Maximum Junction Temperature                                                   | 150                     | °C   |

| T <sub>A</sub>   | Operating Ambient Temperature Range  LMV331, LMV393, LMV339  NCV331 (Note 3)   | -40 to 85<br>-40 to 125 | °C   |

| T <sub>stg</sub> | Storage Temperature Range                                                      | -65 to 150              | °C   |

| $T_L$            | Mounting Temperature (Infrared or Convection (1/16" From Case for 30 Seconds)) | 260                     | °C   |

| V <sub>ESD</sub> | ESD Tolerance (Note 1) Machine Model Human Body Model                          | 100<br>1000             | V    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

| Symbol          | Parameter                                                                   | Value                                                | Unit |

|-----------------|-----------------------------------------------------------------------------|------------------------------------------------------|------|

| V <sub>CC</sub> | Supply Voltage Temperature Range (Note 2)                                   | 2.7 to 5.0                                           | V    |

| θЈΑ             | Thermal Resistance SC-70 TSOP-5 ULLGA8 Micro8 SOIC-8 UDFN8 SOIC-14 TSSOP-14 | 280<br>333<br>340<br>238<br>212<br>350<br>156<br>190 | °C/W |

Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC) Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

The maximum power dissipation is a function of T<sub>J(MAX)</sub>, θ<sub>JA</sub>. The maximum allowable power dissipation at any ambient temperature is P<sub>D</sub> = (T<sub>J(MAX)</sub> – T<sub>A</sub>)/<sub>θJA</sub>. All numbers apply for packages soldered directly onto a PC board.

NCV prefix is qualified for automotive usage.

# **2.7 V DC ELECTRICAL CHARACTERISTICS** (All limits are guaranteed for $T_A = 25^{\circ}C$ , $V^+ = 2.7$ V, $V^- = 0$ V, $V_{CM} = 1.35$ V unless otherwise noted.)

| Parameter                                           | Symbol                         | Condition                | Min | Тур                   | Max                      | Unit  |

|-----------------------------------------------------|--------------------------------|--------------------------|-----|-----------------------|--------------------------|-------|

| Input Offset Voltage                                | V <sub>IO</sub>                |                          |     | 1.7                   | 9                        | mV    |

| Input Offset Voltage Average Drift                  | T <sub>C</sub> V <sub>IO</sub> |                          |     | 5                     |                          | μV/°C |

| Input Bias Current (Note 4)                         | Ι <sub>Β</sub>                 |                          |     | < 1                   |                          | nA    |

| Input Offset Current (Note 4)                       | I <sub>IO</sub>                |                          |     | < 1                   |                          | nA    |

| Input Voltage Range                                 | $V_{CM}$                       |                          |     | 0 to 2                |                          | V     |

| Saturation Voltage                                  | $V_{SAT}$                      | I <sub>SINK</sub> ≤ 1 mA |     | 120                   |                          | mV    |

| Output Sink Current                                 | I <sub>O</sub>                 | V <sub>O</sub> ≤ 1.5 V   | 5   | 23                    |                          | mA    |

| Supply Current LMV331<br>NCV331<br>LMV393<br>LMV339 | I <sub>CC</sub>                |                          |     | 40<br>40<br>70<br>140 | 100<br>100<br>140<br>200 | μΑ    |

## **2.7 V AC ELECTRICAL CHARACTERISTICS** ( $T_A = 25^{\circ}C$ , $V^+ = 2.7$ V, $R_L = 5.1$ k $\Omega$ , $V^- = 0$ V unless otherwise noted.)

| Parameter                       | Symbol           | Condition                                           | Min | Тур         | Max | Unit |

|---------------------------------|------------------|-----------------------------------------------------|-----|-------------|-----|------|

| Propagation Delay – High to Low | t <sub>PHL</sub> | Input Overdrive = 10 mV<br>Input Overdrive = 100 mV |     | 1000<br>500 |     | ns   |

| Propagation Delay – Low to High | t <sub>PLH</sub> | Input Overdrive = 10 mV<br>Input Overdrive = 100 mV |     | 800<br>200  |     | ns   |

<sup>4.</sup> Guaranteed by design and/or characterization.

#### **5.0 V DC ELECTRICAL CHARACTERISTICS** (All limits are guaranteed for $T_A = 25$ °C, $V^+ = 5$ V, $V^- = 0$ V, $V_{CM} = 2.5$ V unless otherwise noted.)

| Parameter                          | Symbol           | Condition (Note 6)           | Min | Тур      | Max        | Unit  |

|------------------------------------|------------------|------------------------------|-----|----------|------------|-------|

| Input Offset Voltage               | V <sub>IO</sub>  | $T_A = T_{LO}$ to $T_{HIGH}$ |     | 1.7      | 9          | mV    |

| Input Offset Voltage Average Drift |                  | $T_A = T_{LO}$ to $T_{HIGH}$ |     | 5        |            | μV/°C |

| Input Bias Current (Note 5)        | Ι <sub>Β</sub>   | $T_A = T_{LO}$ to $T_{HIGH}$ |     | < 1      |            | nA    |

| Input Offset Current (Note 5)      | I <sub>IO</sub>  | $T_A = T_{LO}$ to $T_{HIGH}$ |     | < 1      |            | nA    |

| Input Voltage Range                | $V_{CM}$         |                              |     | 0 to 4.2 |            | V     |

| Voltage Gain (Note 5)              | $A_V$            |                              | 20  | 50       |            | V/mV  |

| Saturation Voltage                 | V <sub>SAT</sub> | $T_A = T_{LO}$ to $T_{HIGH}$ |     | 200      | 400<br>700 | mV    |

| Output Sink Current                | I <sub>O</sub>   | V <sub>O</sub> ≤ 1.5 V       | 10  | 84       |            | mA    |

| Supply Current LMV331              | I <sub>CC</sub>  | $T_A = T_{LO}$ to $T_{HIGH}$ |     | 60       | 120<br>150 | μΑ    |

| Supply Current LMV393              | I <sub>CC</sub>  | $T_A = T_{LO}$ to $T_{HIGH}$ |     | 100      | 200<br>250 | μΑ    |

| Supply Current LMV339              | Icc              | $T_A = T_{LO}$ to $T_{HIGH}$ |     | 170      | 300<br>350 | μΑ    |

| Output Leakage Current (Note 5)    |                  | $T_A = T_{LO}$ to $T_{HIGH}$ |     | 0.003    | 1          | μΑ    |

## **5.0 V AC ELECTRICAL CHARACTERISTICS** ( $T_A = 25$ °C, $V^+ = 5$ V, $R_L = 5.1$ k $\Omega$ , $V^- = 0$ V unless otherwise noted.)

| Parameter                       | Symbol           | Condition                                           | Min | Тур         | Max | Unit |

|---------------------------------|------------------|-----------------------------------------------------|-----|-------------|-----|------|

| Propagation Delay – High to Low | t <sub>PHL</sub> | Input Overdrive = 10 mV<br>Input Overdrive = 100 mV |     | 1500<br>900 |     | ns   |

| Propagation Delay – Low to High | t <sub>PLH</sub> | Input Overdrive = 10 mV<br>Input Overdrive = 100 mV |     | 800<br>200  |     | ns   |

<sup>5.</sup> Guaranteed by design and/or characterization.

6. For LMV331, LMV393, LMV339: T<sub>A</sub> = -40°C to 85°C For NCV331: T<sub>A</sub> = -40°C to 125°C

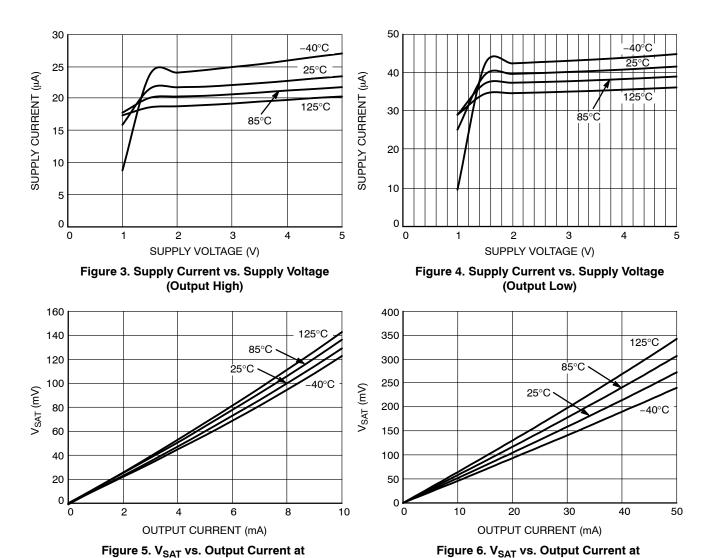

#### **TYPICAL CHARACTERISTICS**

$(V_{CC} = 5.0 \text{ V}, T_A = 25^{\circ}\text{C}, R_L = 5 \text{ k}\Omega \text{ unless otherwise specified})$

$V_{CC} = 5.0 \text{ V}$

V<sub>CC</sub> = 2.7 V

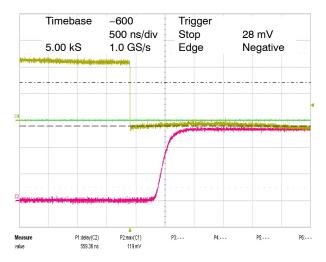

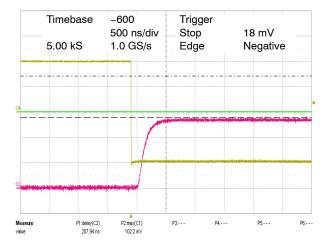

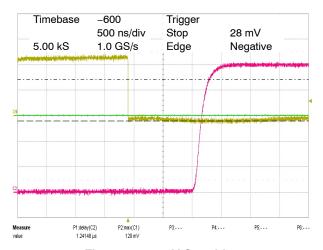

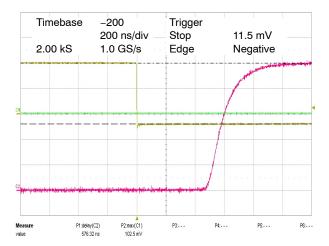

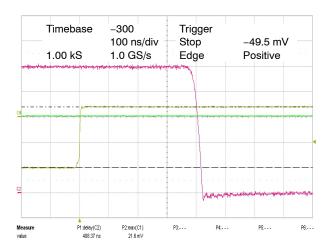

## NEGATIVE TRANSITION INPUT – $V_{CC} = 2.7 \text{ V}$

Figure 7. 10 mV Overdrive

Figure 8. 20 mV Overdrive

Figure 9. 100 mV Overdrive

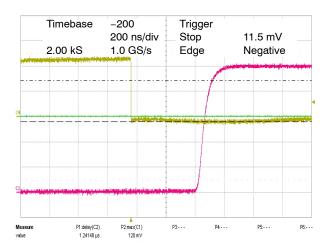

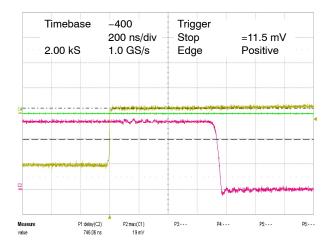

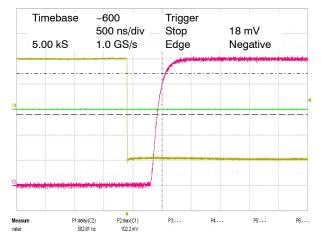

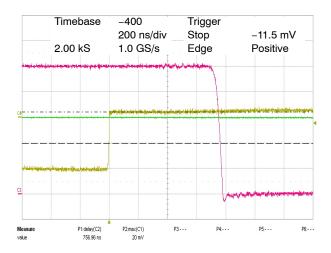

## POSITIVE TRANSITION INPUT – $V_{CC} = 2.7 \text{ V}$

Figure 10. 10 mV Overdrive

Figure 11. 20 mV Overdrive

Figure 12. 100 mV Overdrive

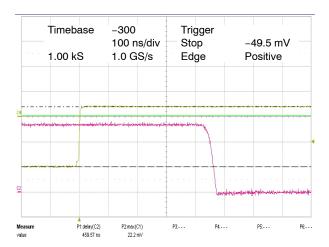

## NEGATIVE TRANSITION INPUT – $V_{CC} = 5.0 \text{ V}$

Figure 13. 10 mV Overdrive

Figure 14. 20 mV Overdrive

Figure 15. 100 mV Overdrive

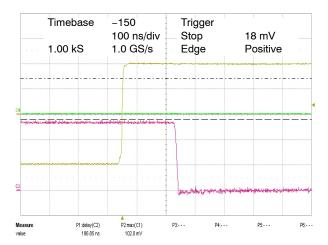

## POSITIVE TRANSITION INPUT – $V_{CC} = 5.0 \text{ V}$

Figure 16. 10 mV Overdrive

Figure 17. 20 mV Overdrive

Figure 18. 100 mV Overdrive

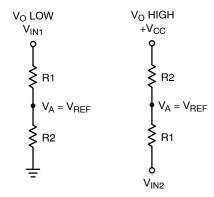

#### **APPLICATION CIRCUITS**

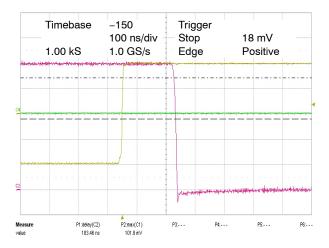

#### **Basic Comparator Operation**

The basic operation of a comparator is to compare two input voltage signals, and produce a digital output signal by determining which input signal is higher. If the voltage on the non-inverting input is higher, then the internal output transistor is off and the output will be high. If the voltage on the inverting input is higher, then the output transistor will be on and the output will be low. The LMV331/393/339 has an open-drain output stage, so a pull-up resistor to a positive supply voltage is required for the output to switch properly.

The size of the pull-up resistor is recommended to be between 1 k $\Omega$  and 10 k $\Omega$ . This range of values will balance two key factors; i.e., power dissipation and drive capability for interface circuitry.

Figure 19 illustrates the basic operation of a comparator and assumes dual supplies. The comparator compares the input voltage  $(V_{IN})$  on the non–inverting input to the reference voltage  $(V_{REF})$  on the inverting input. If  $V_{IN}$  is less than  $V_{REF}$ , the output voltage  $(V_O)$  will be low. If  $V_{IN}$  is greater than  $V_{REF}$ , then  $V_O$  will be high.

#### Comparators and Stability

A common problem with comparators is oscillation due to their high gain. The basic comparator configuration in Figure 19 may oscillate if the differential voltage between the input pins is close to the device's offset voltage. This can happen if the input signal is moving slowly through the comparator's switching threshold or if unused channels are connected to the same potential for termination of unused channels. One way to eliminate output oscillations or 'chatter' is to include external hysteresis in the circuit design.

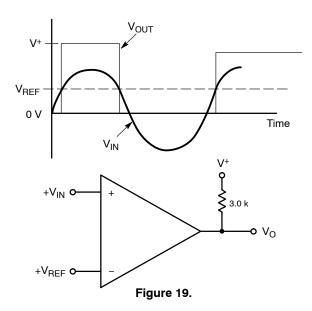

#### **Inverting Configuration with Hysteresis**

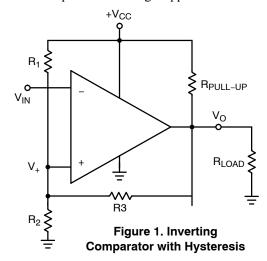

An inverting comparator with hysteresis is shown in Figure 20.

When  $V_{IN}$  is less than the voltage at the non-inverting node,  $V_+$ , the output voltage will be high. When  $V_{IN}$  is greater than the voltage at  $V_+$ , then the output will be low. The hysteresis band (Figure 21) created from the resistor network is defined as:

$$\Delta V_{+} = V_{T1} - V_{T2}$$

where  $V_{T1}$  and  $V_{T2}$  are the lower and upper trip points, respectively.

Figure 21.

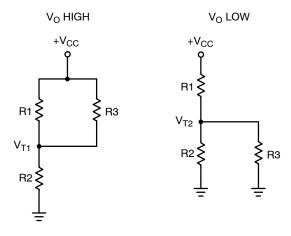

$V_{T1}$  is calculated by assuming that the output of the comparator is pulled up to supply when high. The resistances  $R_1$  and  $R_3$  can be viewed as being in parallel which is in series with  $R_2$  (Figure 22). Therefore  $V_{T1}$  is:

$$V_{T1} = \frac{V_{CC} R_2}{(R_1 \parallel R_3) + R_2}$$

$V_{T2}$  is calculated by assuming that the output of the comparator is at ground potential when low. The resistances  $R_2$  and  $R_3$  can be viewed as being in parallel which is in series with  $R_1$  (Figure 23). Therefore  $V_{T2}$  is:

$$V_{T2} = \frac{V_{CC}(R_2 \parallel R_3)}{R_1 + (R_2 \parallel R_2)}$$

Figure 22.

Figure 23.

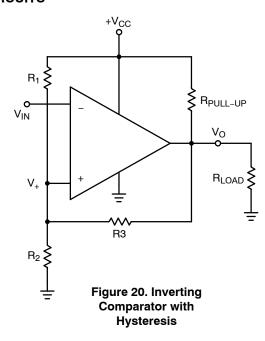

#### Non-inverting Configuration with Hysteresis

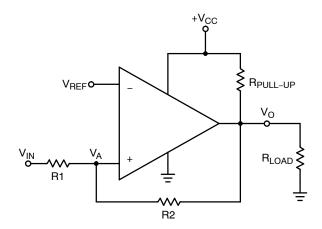

A non-inverting comparator is shown in Figure 24.

Figure 24.

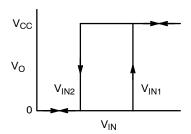

The hysteresis band (Figure 25) of the non-inverting configuration is defined as follows:

$$\Delta V_{in} = V_{CC}R_1/R_2$$

Figure 25.

When  $V_{IN}$  is much less than the voltage at the inverting input ( $V_{REF}$ ), then the output is low.  $R_2$  can then be viewed as being connected to ground (Figure 26). To calculate the voltage required at  $V_{IN}$  to trip the comparator high, the following equation is used:

$$V_{in1} = \frac{V_{ref} (R_1 + R_2)}{R_2}$$

When the output is high,  $V_{IN}$  must less than or equal to  $V_{REF}$  ( $V_{IN} \leq V_{REF}$ ) before the output will be low again (Figure 27). The following equation is used to calculate the voltage at  $V_{IN}$  to switch the output back to the low state:

$$V_{in2} = \frac{V_{ref} (R_1 + R_2) - V_{CC} R_1}{R_2}$$

Figure 26.

Figure 27.

#### **Termination of Unused Inputs**

Proper termination of unused inputs is a good practice to keep the output from 'chattering.' For example, if one channel of a dual or quad package is not being used, then the inputs must be connected to a defined state. The recommended connections would be to tie one input to  $V_{\rm CC}$  and the other input to ground.

#### **ORDERING INFORMATION**

| Order Number  | Number of Channels | Specific Device Marking | Package Type          | Shipping <sup>†</sup> |

|---------------|--------------------|-------------------------|-----------------------|-----------------------|

| LMV331SQ3T2G  | Single             | CCA                     | SC-70<br>(Pb-Free)    | 3000 / Tape & Reel    |

| LMV331SN3T1G  | Single             | зса                     | TSOP-5<br>(Pb-Free)   | 3000 / Tape & Reel    |

| LMV331MU3TBG* | Single             | 3C                      | ULLGA8<br>(Pb-Free)   | 3000 / Tape & Reel    |

| NCV331SN3T1G  | Single             | зса                     | TSOP-5<br>(Pb-Free)   | 3000 / Tape & Reel    |

| LMV393DMR2G   | Dual               | V393                    | Micro8<br>(Pb-Free)   | 4000 / Tape & Reel    |

| LMV393DR2G    | Dual               | V393                    | SOIC-8<br>(Pb-Free)   | 2500 / Tape & Reel    |

| LMV393MUTAG   | Dual               | CA                      | UDFN8<br>(Pb-Free)    | 3000 / Tape & Reel    |

| LMV339DR2G    | Quad               | LMV339                  | SOIC-14<br>(Pb-Free)  | 2500 / Tape & Reel    |

| LMV339DTBR2G  | Quad               | LMV<br>339              | TSSOP-14<br>(Pb-Free) | 2500 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

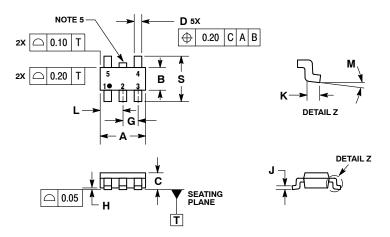

#### **PACKAGE DIMENSIONS**

#### NOTES:

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. 419A-01 OBSOLETE. NEW STANDARD 419A-02.

4. DIMENSIONS A AND B DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS.

|     | INC       | HES   | MILLIM   | ETERS |

|-----|-----------|-------|----------|-------|

| DIM | MIN       | MAX   | MIN      | MAX   |

| Α   | 0.071     | 0.087 | 1.80     | 2.20  |

| В   | 0.045     | 0.053 | 1.15     | 1.35  |

| С   | 0.031     | 0.043 | 0.80     | 1.10  |

| D   | 0.004     | 0.012 | 0.10     | 0.30  |

| G   | 0.026     | BSC   | 0.65     | BSC   |

| Н   |           | 0.004 | -        | 0.10  |

| J   | 0.004     | 0.010 | 0.10     | 0.25  |

| K   | 0.004     | 0.012 | 0.10     | 0.30  |

| N   | 0.008 REF |       | 0.20 REF |       |

| S   | 0.079     | 0.087 | 2.00     | 2.20  |

<sup>\*</sup>Contact factory.

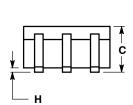

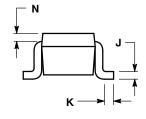

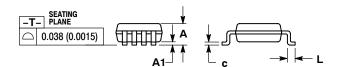

#### PACKAGE DIMENSIONS

TSOP-5 CASE 483-02 **ISSUE H**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER

- ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

- MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH THICKNESS. MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL.

- DIMENSIONS A AND B DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE

- BURRS.

OPTIONAL CONSTRUCTION: AN

ADDITIONAL TRIMMED LEAD IS ALLOWED

IN THIS LOCATION. TRIMMED LEAD NOT TO

EXTEND MORE THAN 0.2 FROM BODY.

|     | MILLIMETERS |      |  |  |  |

|-----|-------------|------|--|--|--|

| DIM | MIN MAX     |      |  |  |  |

| Α   | 3.00        | BSC  |  |  |  |

| В   | 1.50        | BSC  |  |  |  |

| C   | 0.90        | 1.10 |  |  |  |

| D   | 0.25        | 0.50 |  |  |  |

| G   | 0.95        | BSC  |  |  |  |

| Н   | 0.01        | 0.10 |  |  |  |

| 7   | 0.10        | 0.26 |  |  |  |

| K   | 0.20        | 0.60 |  |  |  |

| L   | 1.25        | 1.55 |  |  |  |

| М   | 0 °         | 10°  |  |  |  |

| S   | 2.50        | 3.00 |  |  |  |

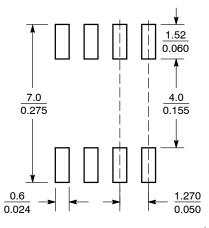

#### **SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

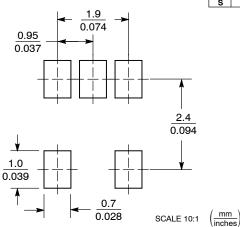

#### PACKAGE DIMENSIONS

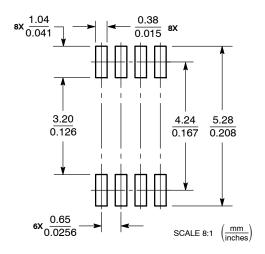

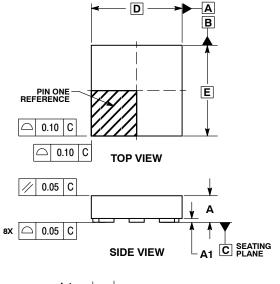

UDFN8 1.8x1.2, 0.4P CASE 517AJ-01 ISSUE O

0.05 M C NOTE 3

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30 mm FROM TERMINAL TIP.

4. MOLD FLASH ALLOWED ON TERMINALS ALONG EDGE OF PACKAGE, FLASH MAY NOT EXCEED 0.03 ONTO BOTTOM SURFACE OF TERMINALS.

5. DETAIL A SHOWS OPTIONAL CONSTRUCTION FOR TERMINALS.

|     | MILLIMETERS |      |  |  |

|-----|-------------|------|--|--|

| DIM | MIN         | MAX  |  |  |

| Α   | 0.45        | 0.55 |  |  |

| A1  | 0.00        | 0.05 |  |  |

| А3  | 0.127       | REF  |  |  |

| b   | 0.15        | 0.25 |  |  |

| b2  | 0.30        | REF  |  |  |

| D   | 1.80        | BSC  |  |  |

| E   | 1.20        | BSC  |  |  |

| е   | 0.40        | BSC  |  |  |

| L   | 0.45 0.55   |      |  |  |

| L1  | 0.00        | 0.03 |  |  |

| L2  | 0.40        | REF  |  |  |

#### **MOUNTING FOOTPRINT\* SOLDERMASK DEFINED**

**DIMENSIONS: MILLIMETERS**

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

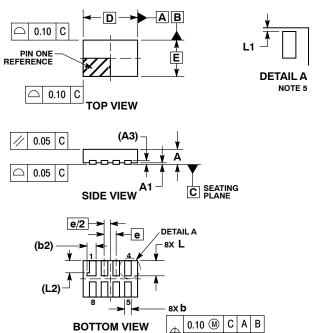

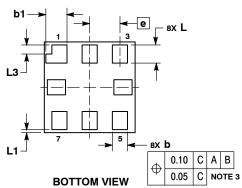

#### PACKAGE DIMENSIONS

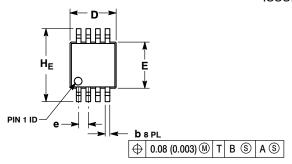

#### Micro8™ CASE 846A-02 **ISSUE H**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED

- D.15 (0.006) PER SIDE.

D.15 (0.006) PER SIDE.

DIES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.

B46A-01 OBSOLETE, NEW STANDARD 846A-02.

|     | MILLIMETERS |          |      | INCHES    |       |       |

|-----|-------------|----------|------|-----------|-------|-------|

| DIM | MIN         | NOM      | MAX  | MIN       | NOM   | MAX   |

| Α   |             |          | 1.10 |           |       | 0.043 |

| A1  | 0.05        | 0.08     | 0.15 | 0.002     | 0.003 | 0.006 |

| b   | 0.25        | 0.33     | 0.40 | 0.010     | 0.013 | 0.016 |

| С   | 0.13        | 0.18     | 0.23 | 0.005     | 0.007 | 0.009 |

| D   | 2.90        | 3.00     | 3.10 | 0.114     | 0.118 | 0.122 |

| E   | 2.90        | 3.00     | 3.10 | 0.114     | 0.118 | 0.122 |

| е   |             | 0.65 BSC |      | 0.026 BSC |       |       |

| L   | 0.40        | 0.55     | 0.70 | 0.016     | 0.021 | 0.028 |

| HE  | 4.75        | 4.90     | 5.05 | 0.187     | 0.193 | 0.199 |

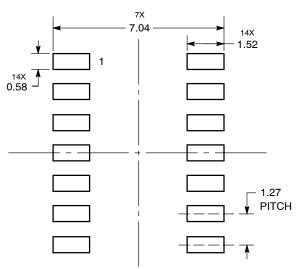

#### **SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### PACKAGE DIMENSIONS

#### SOIC-8 NB CASE 751-07 **ISSUE AJ**

#### NOTES:

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) DED SIDE

- MAXIMUM MOLD PROTRUSION 0.15 (0.006)

PER SIDE.

DIMENSION D DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR

PROTRUSION SHALL BE 0.127 (0.005) TOTAL

IN EXCESS OF THE D DIMENSION AT

MAXIMUM MATERIAL CONDITION.

751-01 THRU 751-06 ARE OBSOLETE. NEW

STANDARD IS 751.07

- STANDARD IS 751-07.

|     | MILLIN | METERS | INC       | HES   |  |

|-----|--------|--------|-----------|-------|--|

| DIM | MIN    | MAX    | MIN       | MAX   |  |

| Α   | 4.80   | 5.00   | 0.189     | 0.197 |  |

| В   | 3.80   | 4.00   | 0.150     | 0.157 |  |

| С   | 1.35   | 1.75   | 0.053     | 0.069 |  |

| D   | 0.33   | 0.51   | 0.013     | 0.020 |  |

| G   | 1.27   | 7 BSC  | 0.050 BSC |       |  |

| Н   | 0.10   | 0.25   | 0.004     | 0.010 |  |

| J   | 0.19   | 0.25   | 0.007     | 0.010 |  |

| K   | 0.40   | 1.27   | 0.016     | 0.050 |  |

| М   | 0 °    | 8 °    | 0 °       | 8 °   |  |

| N   | 0.25   | 0.50   | 0.010     | 0.020 |  |

| s   | 5.80   | 6.20   | 0.228     | 0.244 |  |

#### **SOLDERING FOOTPRINT\***

(mm inches SCALE 6:1

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

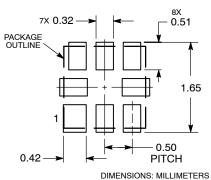

#### PACKAGE DIMENSIONS

ULLGA8, 1.5x1.5, 0.5P CASE 613AG-01 ISSUE O

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30 mm FROM THE TERMINAL TIP.

|     | MILLIMETERS |      |  |  |

|-----|-------------|------|--|--|

| DIM | MIN MAX     |      |  |  |

| Α   |             | 0.40 |  |  |

| A1  | 0.00        | 0.05 |  |  |

| b   | 0.20        | 0.30 |  |  |

| b1  | 0.30        | 0.40 |  |  |

| D   | 1.50 BSC    |      |  |  |

| E   | 1.50 BSC    |      |  |  |

| е   | 0.50 BSC    |      |  |  |

| L   | 0.25        | 0.35 |  |  |

| L1  | 0.05 REF    |      |  |  |

| L3  | 0.15 REF    |      |  |  |

#### **MOUNTING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

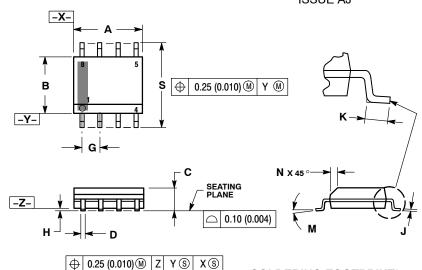

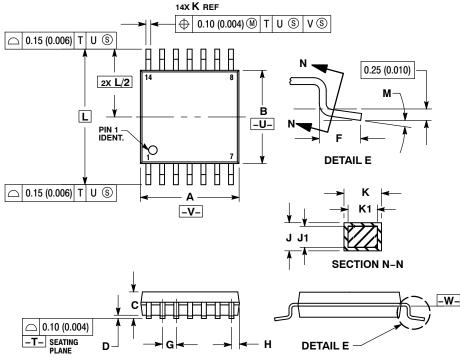

#### **PACKAGE DIMENSIONS**

# SOIC-14 CASE 751A-03 ISSUE H -A--B-**P** 7 PL ⊕ 0.25 (0.010) M B M -T-SEATING PLANE

⊕ 0.25 (0.010) M T B S A S

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

5. DIMENSION D. DOES NOT INCLUDE.

- PER SIDE.

5. DIMENSION D DOES NOT INCLUDE

DAMBAR PROTRUSION. ALLOWABLE

DAMBAR PROTRUSION SHALL BE 0.127

(0.005) TOTAL IN EXCESS OF THE D

DIMENSION AT MAXIMUM MATERIAL

CONDITION.

|     | MILLIN   | IETERS | INCHES    |       |

|-----|----------|--------|-----------|-------|

| DIM | MIN      | MAX    | MIN       | MAX   |

| Α   | 8.55     | 8.75   | 0.337     | 0.344 |

| В   | 3.80     | 4.00   | 0.150     | 0.157 |

| С   | 1.35     | 1.75   | 0.054     | 0.068 |

| D   | 0.35     | 0.49   | 0.014     | 0.019 |

| F   | 0.40     | 1.25   | 0.016     | 0.049 |

| G   | 1.27 BSC |        | 0.050 BSC |       |

| J   | 0.19     | 0.25   | 0.008     | 0.009 |

| K   | 0.10     | 0.25   | 0.004     | 0.009 |

| М   | 0 °      | 7°     | 0 °       | 7°    |

| Р   | 5.80     | 6.20   | 0.228     | 0.244 |

| R   | 0.25     | 0.50   | 0.010     | 0.019 |

#### **SOLDERING FOOTPRINT\***

DIMENSIONS: MILLIMETERS

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

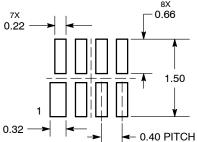

#### PACKAGE DIMENSIONS

#### TSSOP-14 CASE 948G-01 **ISSUE B**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT

- EXCEED 0.15 (0.006) PER SIDE.

4. DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL

- NOT EXCEED 0.25 (0.010) PER SIDE.

5. DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION. SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.

- TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

- DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE -W-.

|     | MILLIN   | IETERS | INCHES    |       |

|-----|----------|--------|-----------|-------|

| DIM | MIN      | MAX    | MIN       | MAX   |

| Α   | 4.90     | 5.10   | 0.193     | 0.200 |

| В   | 4.30     | 4.50   | 0.169     | 0.177 |

| С   |          | 1.20   |           | 0.047 |

| D   | 0.05     | 0.15   | 0.002     | 0.006 |

| F   | 0.50     | 0.75   | 0.020     | 0.030 |

| G   | 0.65 BSC |        | 0.026 BSC |       |

| н   | 0.50     | 0.60   | 0.020     | 0.024 |

| J   | 0.09     | 0.20   | 0.004     | 0.008 |

| J1  | 0.09     | 0.16   | 0.004     | 0.006 |

| Κ   | 0.19     | 0.30   | 0.007     | 0.012 |

| K1  | 0.19     | 0.25   | 0.007     | 0.010 |

| L   | 6.40 BSC |        | 0.252 BSC |       |

| M   | 0 °      | 8 °    | 0 °       | 8 °   |

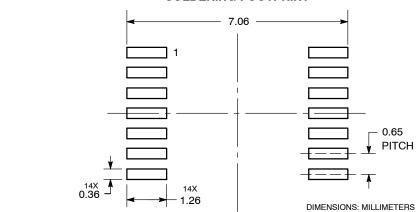

#### SOLDERING FOOTPRINT

#### Micro8 is a trademark of International Rectifier.

ON Semiconductor and un are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking, tadefined to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

**Phone**: 303–675–2175 or 800–344–3860 Toll Free USA/Canada **Fax**: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative