# **High-Performance ROM-less Microcontrollers** with External Memory Bus

#### **High Performance RISC CPU:**

- · C compiler optimized architecture instruction set

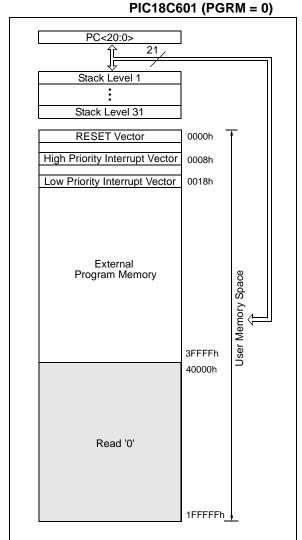

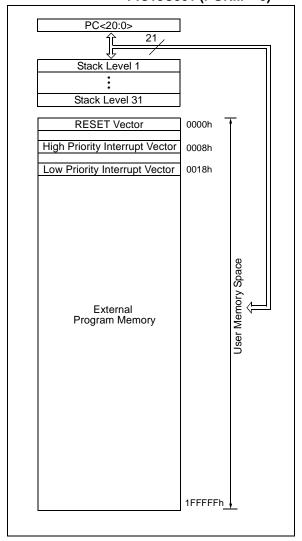

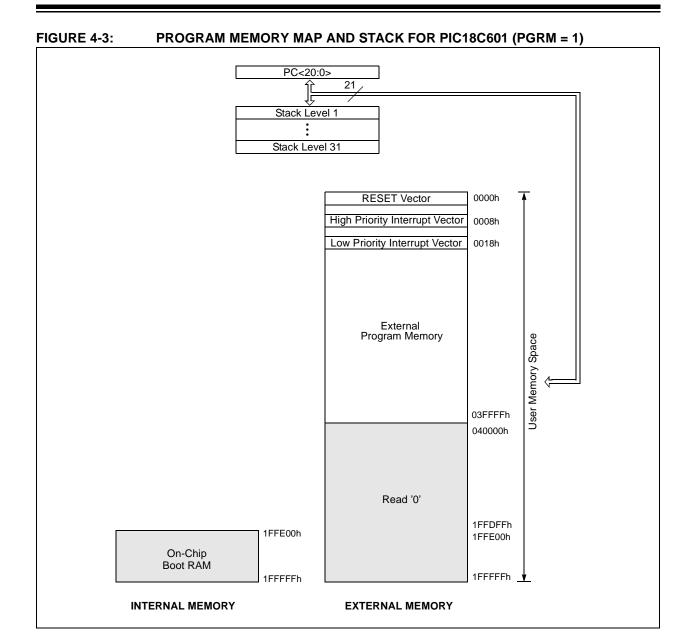

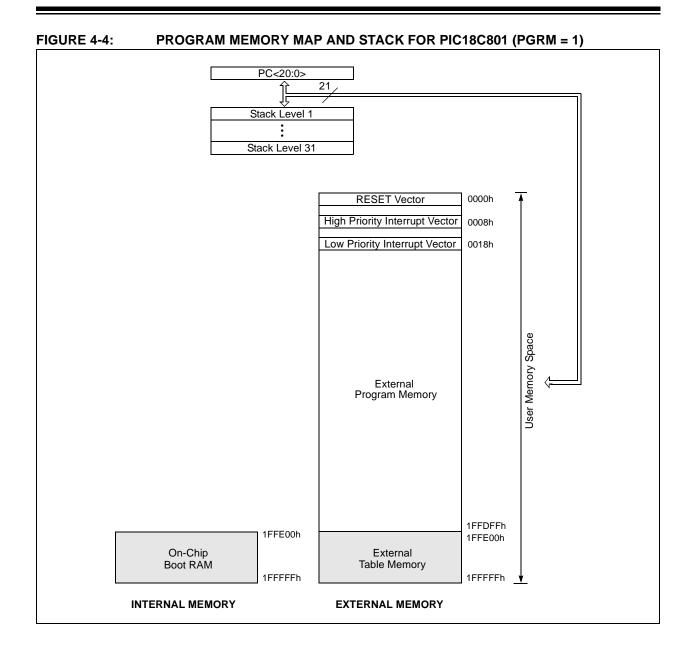

- Linear program memory addressing up to 2 Mbytes

- · Linear data memory addressing to 4 Kbytes

|           | External Prog                    | gram Memory            |      |  |  |  |  |

|-----------|----------------------------------|------------------------|------|--|--|--|--|

|           | On-                              | On-Chip                |      |  |  |  |  |

| Device    | Maximum<br>Addressing<br>(bytes) | Addressing Single Word |      |  |  |  |  |

| PIC18C601 | 256K                             | 128K                   | 1.5K |  |  |  |  |

| PIC18C801 | 2M                               | 1M                     | 1.5K |  |  |  |  |

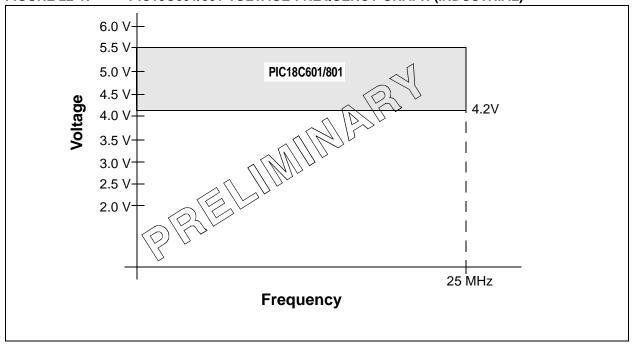

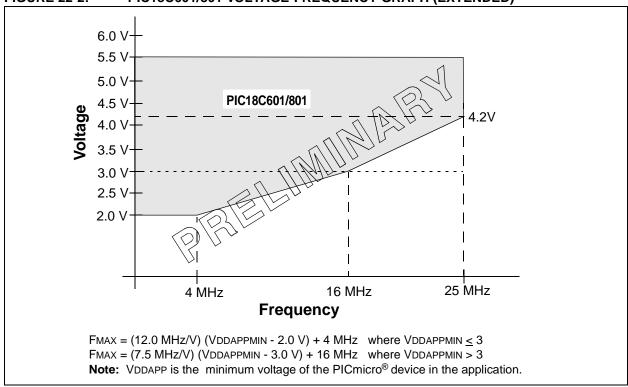

- Up to 160 ns instruction cycle:

- DC 25 MHz clock input

- 4 MHz 6 MHz clock input with PLL active

- 16-bit wide instructions, 8-bit wide data path

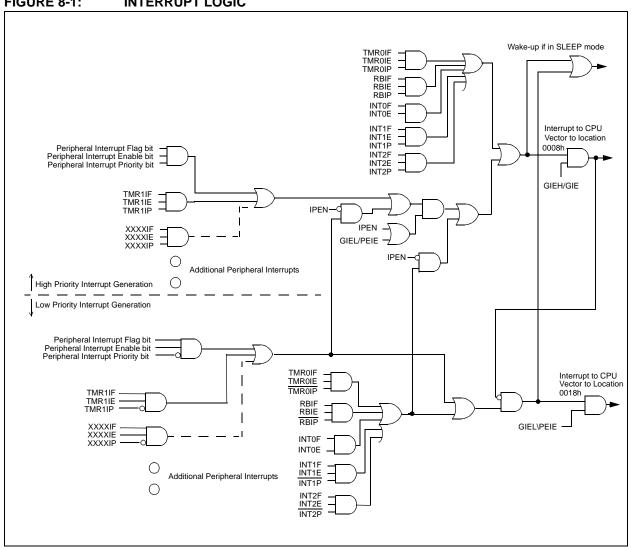

- · Priority levels for interrupts

- 8 x 8 Single Cycle Hardware Multiplier

#### **Peripheral Features:**

- High current sink/source 25 mA/25 mA

- Up to 47 I/O pins with individual direction control

- · Three external interrupt pins

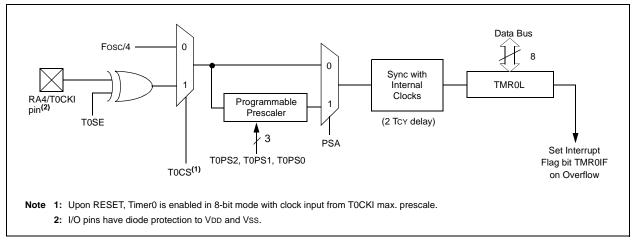

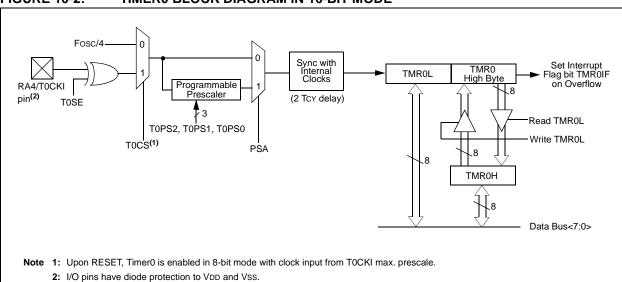

- Timer0 module: 8-bit/16-bit timer/counter with 8-bit programmable prescaler

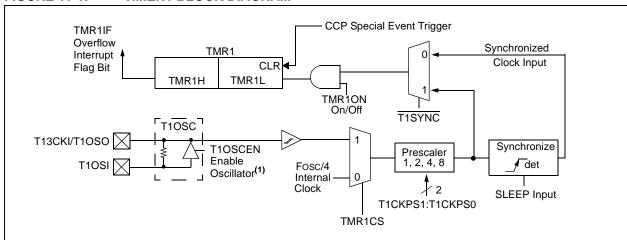

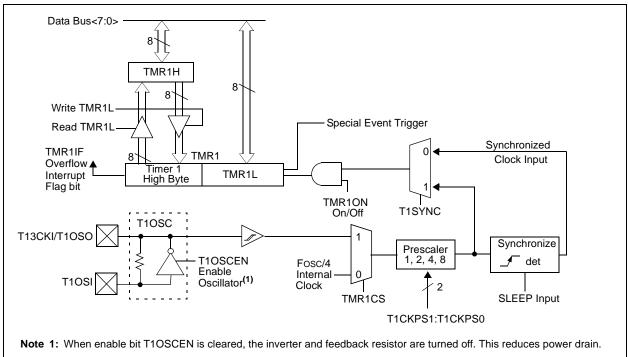

- Timer1 module: 16-bit timer/counter (time-base for CCP)

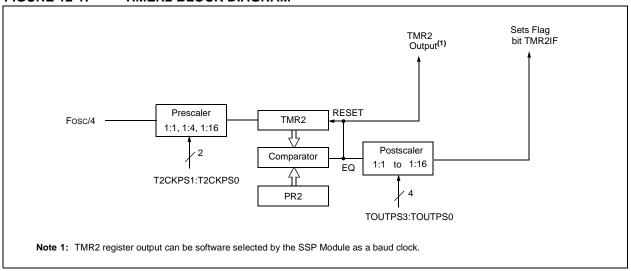

- Timer2 module: 8-bit timer/counter with 8-bit period register

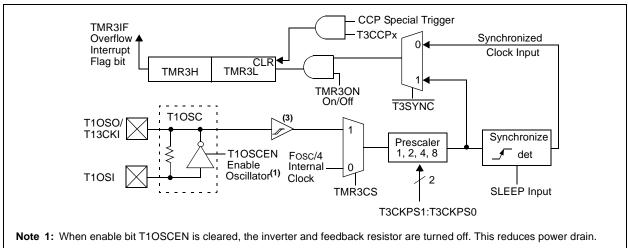

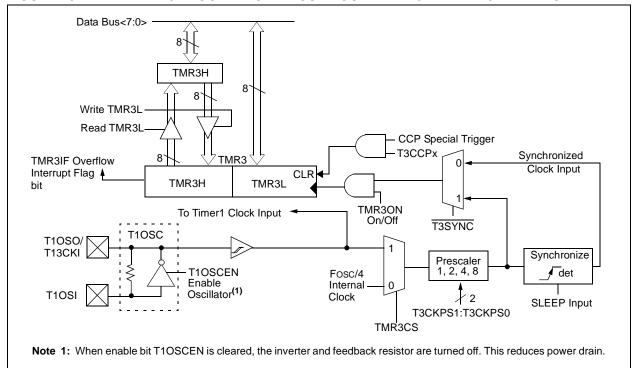

- Timer3 module: 16-bit timer/counter

- Secondary oscillator clock option Timer1/Timer3

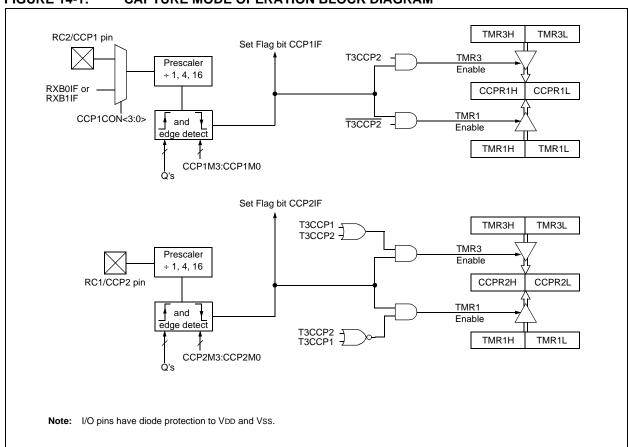

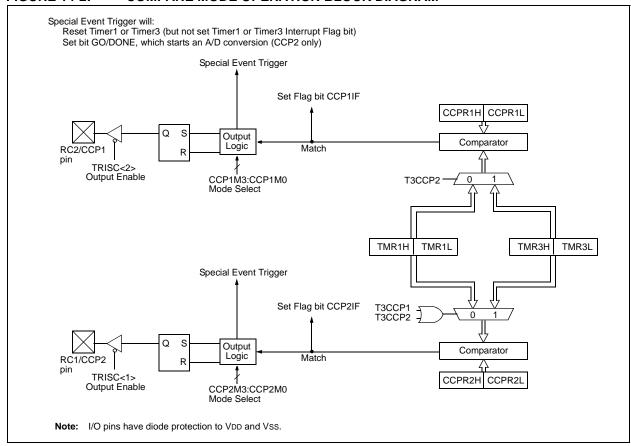

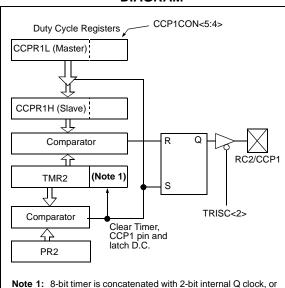

- Two Capture/Compare/PWM (CCP) modules CCP pins can be configured as:

- Capture input: 16-bit, max. resolution 10 ns

- Compare is 16-bit, max. resolution 160 ns (Tcy)

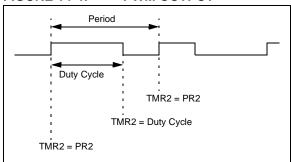

- PWM output: PWM resolution is 1- to 10-bit Max. PWM freq. @:

8-bit resolution = 99 kHz 10-bit resolution = 24.4 kHz

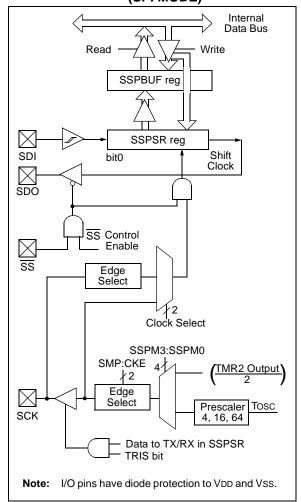

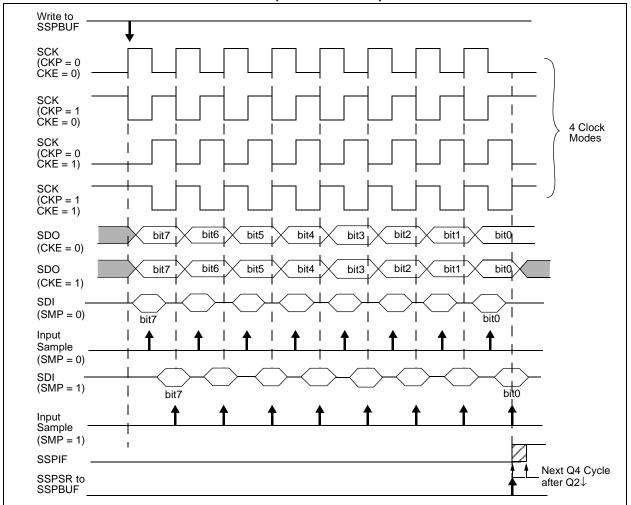

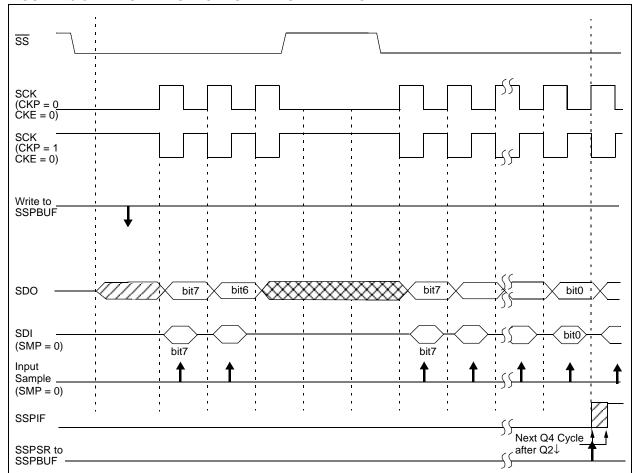

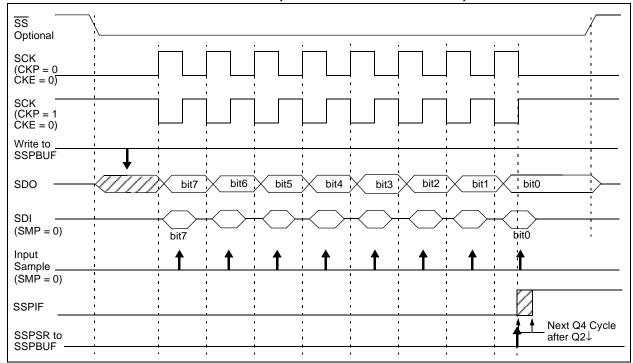

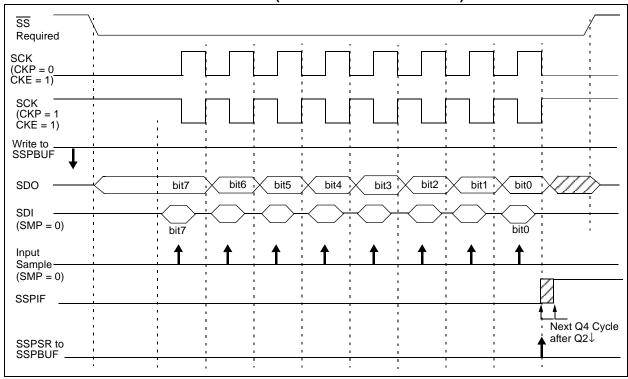

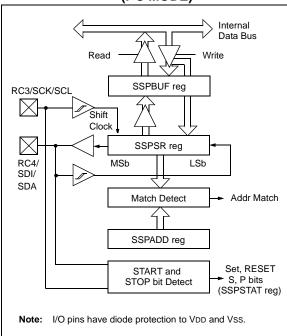

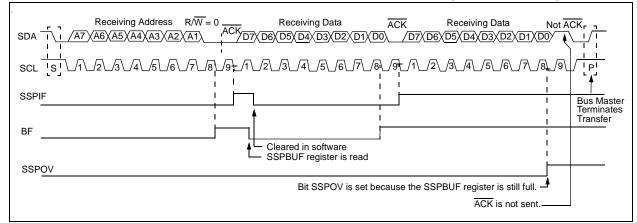

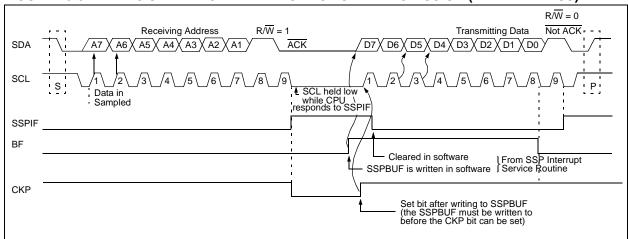

- Master Synchronous Serial Port (MSSP) with two modes of operation:

- 3-wire SPI™ (Supports all 4 SPI modes)

- I<sup>2</sup>C™ Master and Slave mode

- Addressable USART module: Supports Interrupt on Address bit

#### **Advanced Analog Features:**

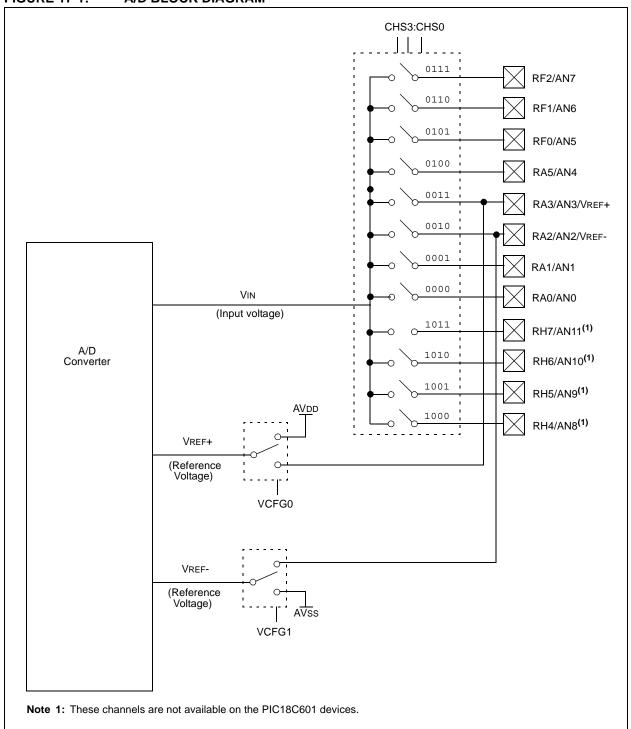

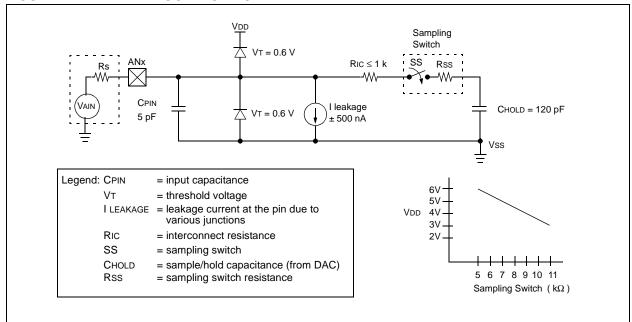

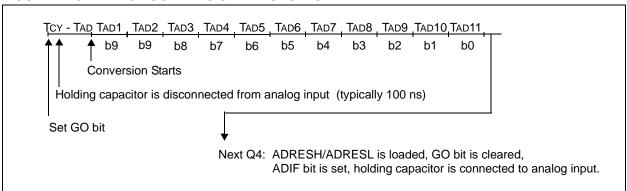

- 10-bit Analog-to-Digital Converter module (A/D) with:

- Fast sampling rate

- Conversion available during SLEEP

- DNL =  $\pm 1$  LSb, INL =  $\pm 1$  LSb

- Up to 12 channels available

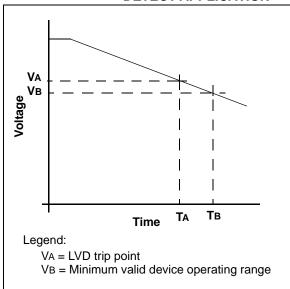

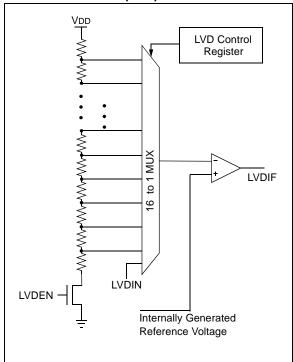

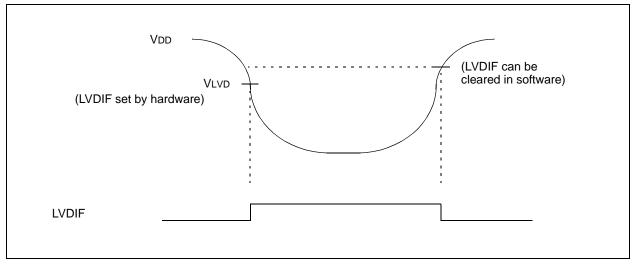

- Programmable Low Voltage Detection (LVD) module

- Supports interrupt on Low Voltage Detection

#### **Special Microcontroller Features:**

- Power-on Reset (POR), Power-up Timer (PWRT), and Oscillator Start-up Timer (OST)

- Watchdog Timer (WDT) with its own on-chip RC oscillator

- On-chip Boot RAM for boot loader application

- 8-bit or 16-bit external memory interface modes

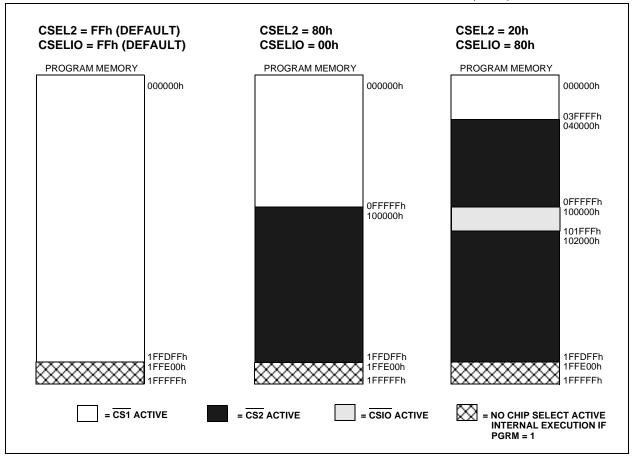

- Up to two software programmable chip select signals (CS1 and CS2)

- One programmable chip I/O select signal (CSIO) for memory mapped I/O expansion

- Power saving SLEEP mode

- · Different oscillator options, including:

- 4X Phase Lock Loop (of primary oscillator)

- Secondary Oscillator (32 kHz) clock input

#### **CMOS Technology:**

- · Low power, high speed CMOS technology

- · Fully static design

- Wide operating voltage range (2.0V to 5.5V)

- Industrial and Extended temperature ranges

- · Low power consumption

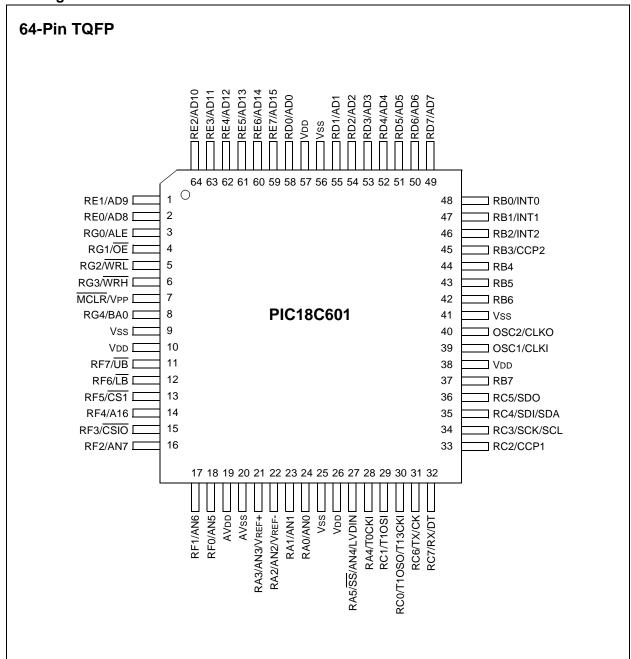

#### **Pin Diagrams**

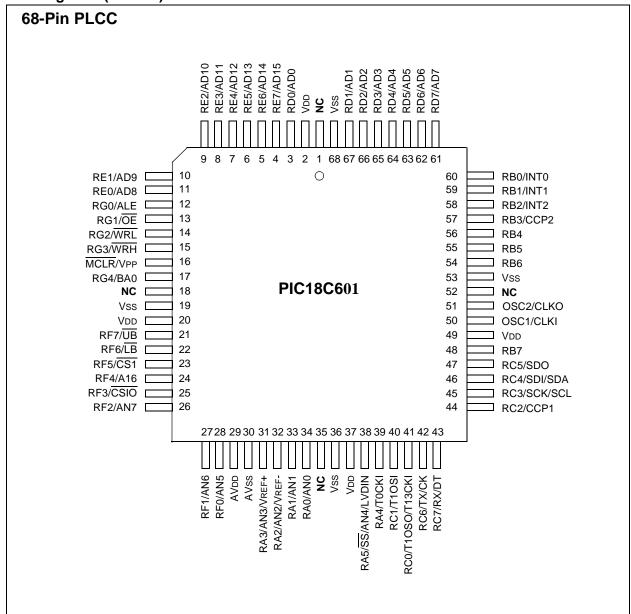

#### Pin Diagrams (Cont.'d)

#### Pin Diagrams (Cont.'d) 80-Pin TQFP RE4/AD12 RE2/AD10 RE3/AD11 RE5/AD13 RE6/AD14 RE7/AD15 RD0/AD0 RD3/AD3 RD5/AD5 RD6/AD6 RH0/A16 RD2/AD2 ☐RH1/A17 RD1/AD1 RD4/AD4 RD7/AD7 RJ0/D7 VDD Vss 80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 RH2/A18 [ 10 RJ5/D5 2 59 RH3/A19 □ RJ4/D4 □ RB0/INT0 58 3 RE1/AD9 RE0/AD8 D 4 57 RB1/INT1 56 RB2/INT2 RG0/ALE [ 5 RG1/OE 55 RB3/CCP2 6 RG2/WRL 7 54 □ RB4 □ RB5 RG3/WRH I 8 53 MCLR/VPP 9 52 RB6 RG4/BA0 [ 10 51 Vss Vss L 11 50 OSC2/CLKO PIC18C801 49 OSC1/CLKI VDD 12 RF7/UB 48 □ Vdd 13 RB7 RF6/LB L 47 14 RF5/CS1 15 46 ☐ RC5/SDO RF4/CS2 L 45 RC4/SDI/SDA 16 RC3/SCK/SCL RF3/CSIO 17 44 □ RC2/CCP1 RF2/AN7 18 43 42 □ RJ3/D3 19 RH4/AN8 [ RJ2/D2 RH5/AN9 [ 20 41 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 V<sub>DD</sub> RH7/AN11 □ RA5/SS/AN4/LVDIN RA4/T0CKI RF1/AN6 RF0/AN5 RA1/AN1 ERA0/AN0 E AVDD AVss Vss RJ0/D0 [ RC0/T10S0/T13CKI RC6/TX/CK RH6/AN10 RC7/RX/DT RA3/AN3/VREF+ RA2/AN2/VREF-

#### Pin Diagrams (Cont.'d)

#### **Table of Contents**

| 1.0   | Device Overview                                                             |                                        |

|-------|-----------------------------------------------------------------------------|----------------------------------------|

| 2.0   | Oscillator Configurations                                                   | 21                                     |

| 3.0   | RESET                                                                       |                                        |

| 4.0   | Memory Organization                                                         | 39                                     |

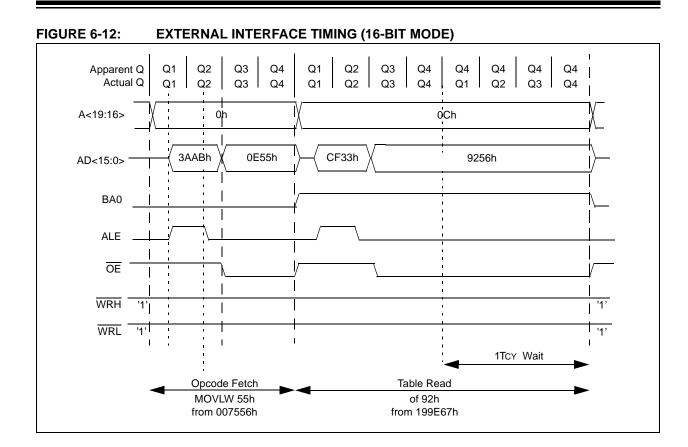

| 5.0   | External Memory Interface                                                   | 63                                     |

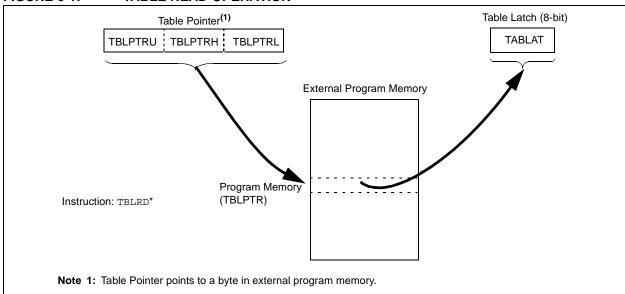

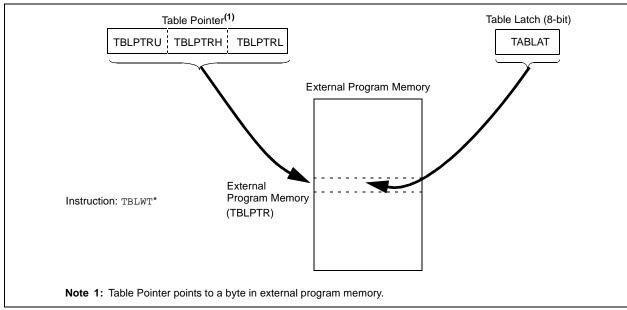

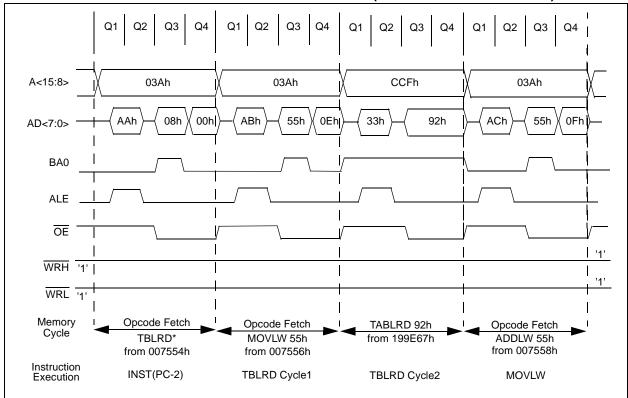

| 6.0   | Table Reads/Table Writes                                                    | 73                                     |

| 7.0   | 8 X 8 Hardware Multiplier                                                   | 85                                     |

| 8.0   | Interrupts                                                                  | 89                                     |

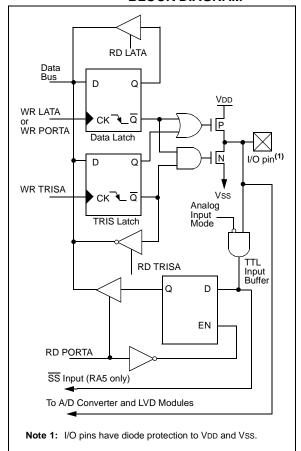

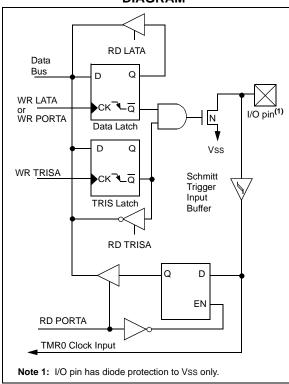

| 9.0   | I/O Ports                                                                   | 103                                    |

| 10.0  | Timer0 Module                                                               | 127                                    |

| 11.0  | Timer1 Module                                                               | 130                                    |

| 12.0  | Timer2 Module                                                               | 135                                    |

| 13.0  | Timer3 Module                                                               | 137                                    |

| 14.0  | Capture/Compare/PWM (CCP) Modules                                           | 141                                    |

| 15.0  | Master Synchronous Serial Port (MSSP) Module                                |                                        |

| 16.0  | Addressable Universal Synchronous Asynchronous Receiver Transmitter (USART) | 177                                    |

| 17.0  | 10-bit Analog-to-Digital Converter (A/D) Module                             | 193                                    |

| 18.0  | Low Voltage Detect                                                          | 203                                    |

| 19.0  | Special Features of the CPU                                                 | 207                                    |

| 20.0  | Instruction Set Summary                                                     |                                        |

| 21.0  | Development Support                                                         | 259                                    |

| 22.0  | Electrical Characteristics                                                  | ······································ |

| 23.0  | DC and AC Characteristics Graphs and Tables                                 |                                        |

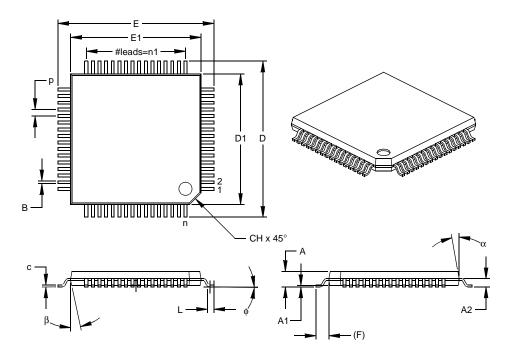

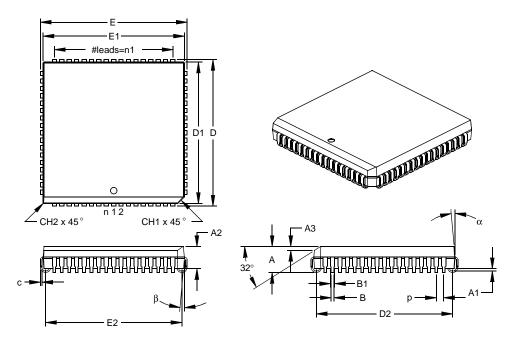

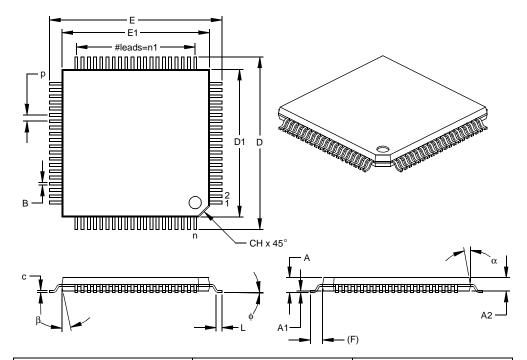

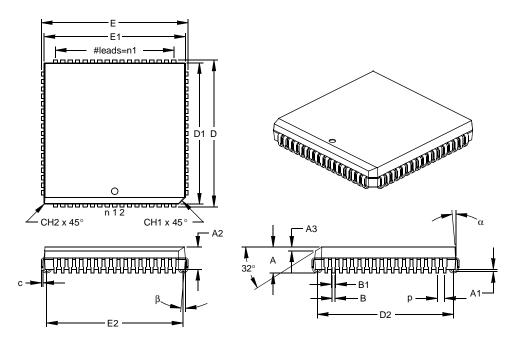

| 24.0  | Packaging Information                                                       | 297                                    |

|       | ndix A: Data Sheet Revision History                                         |                                        |

|       | ndix B: Device Differences                                                  |                                        |

| Appe  | ndix C: Device Migrations                                                   | 304                                    |

| Appe  | ndix D: Migrating from other PICmicro Devices                               | 304                                    |

| Appe  | ndix E: Development Tool Version Requirements                               | 305                                    |

| Index |                                                                             | 307                                    |

| On-Li | ne Support                                                                  | 315                                    |

| Read  | er Response                                                                 | 316                                    |

| Produ | uct Identification System                                                   | 317                                    |

© 2001 Microchip Technology Inc.

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

NOTES:

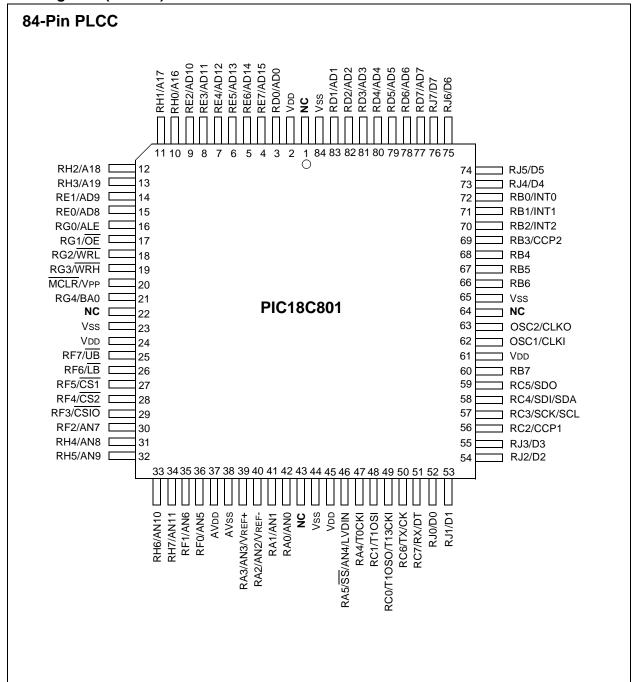

#### 1.0 DEVICE OVERVIEW

This document contains device specific information for the following two devices:

- 1. PIC18C601

- 2. PIC18C801

The PIC18C601 is available in 64-pin TQFP and 68-pin PLCC packages. The PIC18C801 is available in 80-pin TQFP and 84-pin PLCC packages.

An overview of features is shown in Table 1-1.

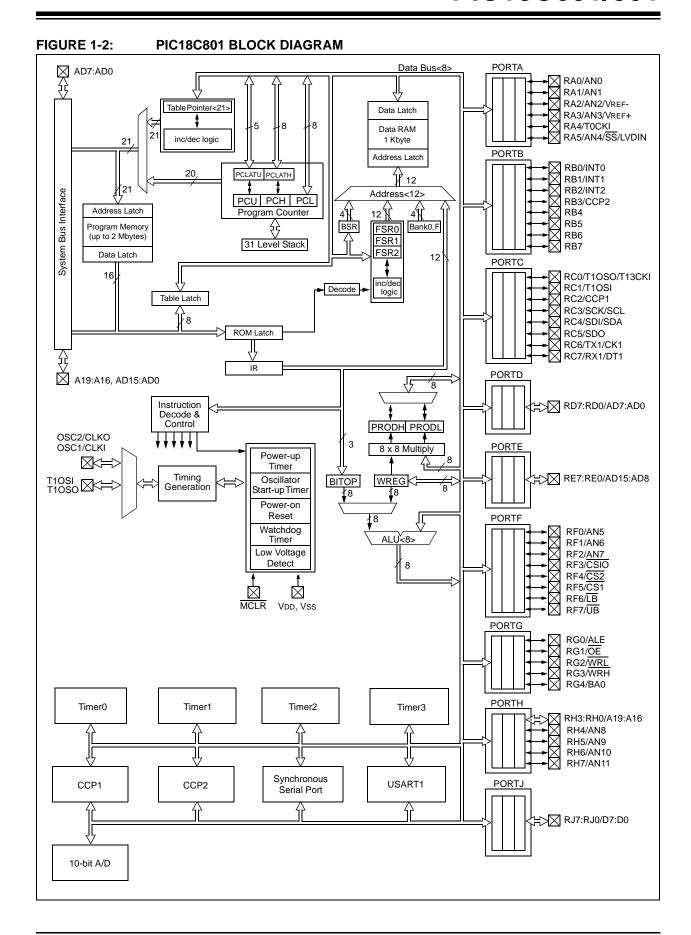

Device block diagrams are provided in Figure 1-1 for the 64/68-pin configuration, and Figure 1-2 for the 80/84-pin configuration. The pinouts for both packages are listed in Table 1-2.

TABLE 1-1: DEVICE FEATURES

| Fea                                          | tures                              | PIC18C601                                                       | PIC18C801                                                       |  |  |

|----------------------------------------------|------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|--|--|

| Operating Frequency                          |                                    | DC - 25 MHz                                                     | DC - 25 MHz                                                     |  |  |

| External                                     | Bytes                              | 256K                                                            | 2M                                                              |  |  |

| Program Memory                               | Max. # of Single Word Instructions | 128K                                                            | 1M                                                              |  |  |

| Data Memory (Bytes)                          |                                    | 1536                                                            | 1536                                                            |  |  |

| Interrupt Sources                            |                                    | 15                                                              | 15                                                              |  |  |

| I/O Ports                                    |                                    | Ports A - G                                                     | Ports A - H, J                                                  |  |  |

| Timers                                       |                                    | 4                                                               | 4                                                               |  |  |

| Capture/Compare/PWM                          | modules                            | 2                                                               | 2                                                               |  |  |

| Serial Communications                        |                                    | MSSP,<br>Addressable USART                                      | MSSP,<br>Addressable USART                                      |  |  |

| 10-bit Analog-to-Digital                     | Module                             | 8 input channels                                                | 12 input channels                                               |  |  |

| RESETS (and Delays)                          |                                    | POR, RESET Instruction, Stack Full, Stack Underflow (PWRT, OST) | POR, RESET Instruction, Stack Full, Stack Underflow (PWRT, OST) |  |  |

| Programmable Low Volt                        | age Detect                         | Yes                                                             | Yes                                                             |  |  |

| 8-bit External Memory In                     | nterface                           | Yes                                                             | Yes                                                             |  |  |

| 8-bit De-multiplexed Ext<br>Memory Interface | ernal                              | No                                                              | Yes                                                             |  |  |

| 16-bit External Memory                       | Interfaces                         | Yes                                                             | Yes                                                             |  |  |

| On-chip Chip Select Sig                      | nals                               | CS1                                                             | CS1, CS2                                                        |  |  |

| On-chip I/O Chip Select                      | Signal                             | Yes                                                             | Yes                                                             |  |  |

| Instruction Set                              |                                    | 75 Instructions                                                 | 75 Instructions                                                 |  |  |

| Packages                                     |                                    | 64-pin TQFP<br>68-pin PLCC                                      | 80-pin TQFP<br>84-pin PLCC                                      |  |  |

TABLE 1-2: PINOUT I/O DESCRIPTIONS

|                         |       | Pin N            | umber |                  |             |                |                                                                                                                |

|-------------------------|-------|------------------|-------|------------------|-------------|----------------|----------------------------------------------------------------------------------------------------------------|

| Pin Name                | PIC18 | BC601            | PIC1  | 8C801            | Pin<br>Type | Buffer<br>Type |                                                                                                                |

|                         | TQFP  | PLCC             | TQFP  | PLCC             | .,,,,       | .,,,,,         | Description                                                                                                    |

| MCLR/VPP<br>MCLR<br>VPP | 7     | 16               | 9     | 20               | I<br>P      | ST             | Master clear (RESET) input. This pin is an active low RESET to the device.                                     |

| NC VPP                  | _     | 1, 18,<br>35, 52 | _     | 1, 22,<br>43, 64 | <u> </u>    | _              | Programming voltage input.  These pins should be left unconnected.                                             |

| OSC1/CLKI<br>OSC1       | 39    | 50               | 49    | 62               | I           | CMOS/ST        | Oscillator crystal input or external clock source input. ST buffer when in RC mode. Otherwise CMOS.            |

| CLKI                    |       |                  |       |                  | I           | CMOS           | External clock source input. Always associated with pin function OSC1 (see OSC1/CLKI, OSC2/CLKO pins).         |

| OSC2/CLKO<br>OSC2       | 40    | 51               | 50    | 63               | 0           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode.                        |

| CLKO                    |       |                  |       |                  | 0           | _              | In RC mode, OSC2 pin outputs CLKO, which has 1/4 the frequency of OSC1 and denotes the instruction cycle rate. |

Legend: TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I = Input

P = Power

CMOS = CMOS compatible input or output

Analog = Analog input

O = Output

TABLE 1-2: PINOUT I/O DESCRIPTIONS (CONTINUED)

|                  |       | Pin N | umber |       |             |                |                                     |

|------------------|-------|-------|-------|-------|-------------|----------------|-------------------------------------|

| Pin Name         | PIC18 | 8C601 | PIC18 | BC801 | Pin<br>Type | Buffer<br>Type |                                     |

|                  | TQFP  | PLCC  | TQFP  | PLCC  | .,,,,       | .,,,,          | Description                         |

|                  |       |       |       |       |             |                | PORTA is a bi-directional I/O port. |

| RA0/AN0          | 24    | 34    | 30    | 42    |             |                |                                     |

| RA0              |       |       |       |       | I/O         | TTL            | Digital I/O.                        |

| AN0              |       |       |       |       | - 1         | Analog         | Analog input 0.                     |

| RA1/AN1          | 23    | 33    | 29    | 41    |             |                |                                     |

| RA1              |       |       |       |       | I/O         | TTL            | Digital I/O.                        |

| AN1              |       |       |       |       | - 1         | Analog         | Analog input 1.                     |

| RA2/AN2/VREF-    | 22    | 32    | 28    | 40    |             |                |                                     |

| RA2              |       |       |       |       | I/O         | TTL            | Digital I/O.                        |

| AN2              |       |       |       |       | I           | Analog         | Analog input 2.                     |

| VREF-            |       |       |       |       | I           | Analog         | A/D reference voltage (Low) input.  |

| RA3/AN3/VREF+    | 21    | 31    | 27    | 39    |             |                |                                     |

| RA3              |       |       |       |       | I/O         | TTL            | Digital I/O.                        |

| AN3              |       |       |       |       | I           | Analog         | Analog input 3.                     |

| VREF+            |       |       |       |       | 1           | Analog         | A/D reference voltage (High) input. |

| RA4/T0CKI        | 28    | 39    | 34    | 47    |             |                |                                     |

| RA4              |       |       |       |       | I/O         | ST/OD          | Digital I/O – Open drain when       |

|                  |       |       |       |       |             |                | configured as output.               |

| T0CKI            |       |       |       |       | 1           | ST             | Timer0 external clock input.        |

| RA5/AN4/SS/LVDIN | 27    | 38    | 33    | 46    |             |                |                                     |

| RA5              |       |       |       |       | I/O         | TTL            | Digital I/O.                        |

| AN4              |       |       |       |       | I           | Analog         | Analog input 4.                     |

| SS               |       |       |       |       | I           | ST             | SPI slave select input.             |

| LVDIN            |       |       |       |       | - 1         | Analog         | Low voltage detect input.           |

Legend: TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I = Input

P = Power

CMOS = CMOS compatible input or output

Analog = Analog input O = Output

TABLE 1-2: PINOUT I/O DESCRIPTIONS (CONTINUED)

|                         | Pin Number |           | Pin  |           |            |                |                                                                                                                |

|-------------------------|------------|-----------|------|-----------|------------|----------------|----------------------------------------------------------------------------------------------------------------|

| Pin Name                | PIC1       | PIC18C601 |      | PIC18C801 |            | Buffer<br>Type |                                                                                                                |

|                         | TQFP       | PLCC      | TQFP | PLCC      | Туре       | .,,,,,         | Description                                                                                                    |

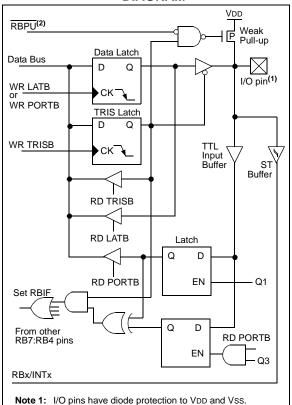

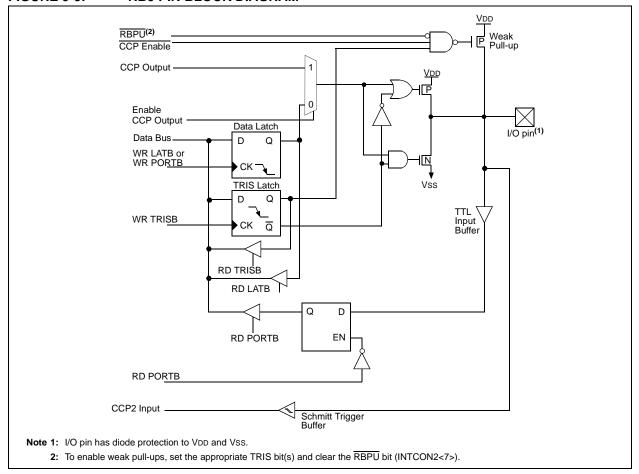

|                         |            |           |      |           |            |                | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs. |

| RB0/INT0<br>RB0<br>INT0 | 48         | 60        | 58   | 72        | I/O<br>I   | TTL<br>ST      | Digital I/O. External interrupt 0.                                                                             |

| RB1/INT1<br>RB1<br>INT1 | 47         | 59        | 57   | 71        | I/O<br>I   | TTL<br>ST      | Digital I/O. External interrupt 1.                                                                             |

| RB2/INT2<br>RB2<br>INT2 | 46         | 58        | 56   | 70        | I/O<br>I   | TTL<br>ST      | Digital I/O. External interrupt 2.                                                                             |

| RB3/CCP2<br>RB3<br>CCP2 | 45         | 57        | 55   | 69        | I/O<br>I/O | TTL<br>ST      | Digital I/O. Capture2 input, Compare2 output, PWM2 output.                                                     |

| RB4                     | 44         | 56        | 54   | 68        | I/O        | TTL            | Digital I/O, Interrupt-on-change pin.                                                                          |

| RB5                     | 43         | 55        | 53   | 67        | I/O        | TTL            | Digital I/O, Interrupt-on-change pin.                                                                          |

| RB6                     | 42         | 54        | 52   | 66        | I/O<br>I   | TTL<br>ST      | Digital I/O, Interrupt-on-change pin. ICSP programming clock.                                                  |

| RB7                     | 37         | 48        | 47   | 60        | I/O<br>I/O | TTL<br>ST      | Digital I/O, Interrupt-on-change pin. ICSP programming data.                                                   |

Legend: TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I = Input

P = Power

CMOS = CMOS compatible input or output

Analog = Analog input

O = Output

TABLE 1-2: PINOUT I/O DESCRIPTIONS (CONTINUED)

|                  | Pin Number |       |       |          |             |                |                                                     |

|------------------|------------|-------|-------|----------|-------------|----------------|-----------------------------------------------------|

| Pin Name         | PIC1       | 8C601 | PIC18 | BC801    | Pin<br>Type | Buffer<br>Type |                                                     |

|                  | TQFP       | PLCC  | TQFP  | PLCC     | .,,,,       | .,,,,          | Description                                         |

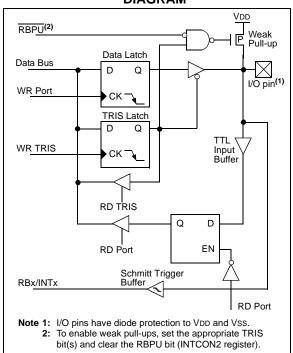

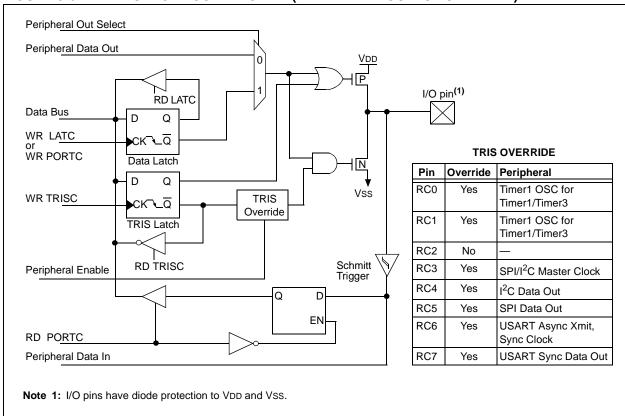

|                  |            |       |       |          |             |                | PORTC is a bi-directional I/O port.                 |

| RC0/T1OSO/T13CKI | 30         | 41    | 36    | 49       |             |                |                                                     |

| RC0              |            |       |       |          | I/O         | ST             | Digital I/O.                                        |

| T1OSO            |            |       |       |          | 0           | _              | Timer1 oscillator output.                           |

| T13CKI           |            |       |       |          | I           | ST             | Timer1/Timer3 external clock input.                 |

| RC1/T1OSI        | 29         | 40    | 35    | 48       |             |                |                                                     |

| RC1              |            |       |       |          | I/O         | ST             | Digital I/O.                                        |

| T1OSI            |            |       |       |          | I           | CMOS           | Timer1 oscillator input.                            |

| RC2/CCP1         | 33         | 44    | 43    | 56       |             |                |                                                     |

| RC2              |            |       |       |          | I/O         | ST             | Digital I/O.                                        |

| CCP1             |            |       |       |          | I/O         | ST             | Capture1 input/Compare1                             |

|                  |            |       |       |          |             |                | output/PWM1 output.                                 |

| RC3/SCK/SCL      | 34         | 45    | 44    | 57       |             | o <del>.</del> | D: 11 11/0                                          |

| RC3              |            |       |       |          | 1/0         | ST             | Digital I/O.                                        |

| SCK              |            |       |       |          | I/O         | ST             | Synchronous serial clock input/output for SPI mode. |

| SCL              |            |       |       |          | 1/0         | ST             | Synchronous serial clock                            |

| JOL              |            |       |       |          | 1/0         | 01             | input/output for I <sup>2</sup> C mode.             |

| RC4/SDI/SDA      | 35         | 46    | 45    | 58       |             |                | mparauparier i o maasi                              |

| RC4              | 00         | 70    | 45    | 30       | I/O         | ST             | Digital I/O.                                        |

| SDI              |            |       |       |          | ı, o        | ST             | SPI data in.                                        |

| SDA              |            |       |       |          | I/O         | ST             | I <sup>2</sup> C data I/O.                          |

| RC5/SDO          | 36         | 47    | 46    | 59       |             |                | 1 o data 1/o.                                       |

| RC5              | 30         | 47    | 40    | 59       | I/O         | ST             | Digital I/O.                                        |

| SDO              |            |       |       |          | 0           | <del>-</del>   | SPI data out.                                       |

| RC6/TX/CK        | 31         | 42    | 37    | 50       |             |                | or radia odi.                                       |

| RC6              | 31         | 72    | 31    | 30       | I/O         | ST             | Digital I/O.                                        |

| TX               |            |       |       |          | 0           | _              | USART asynchronous transmit.                        |

| CK               |            |       |       |          | I/O         | ST             | USART synchronous clock.                            |

| RC7/RX/DT        | 32         | 43    | 38    | 51       |             |                | ,                                                   |

| RC7              | J          |       |       | <b>.</b> | I/O         | ST             | Digital I/O.                                        |

| RX               |            |       |       |          | I           | ST             | USART asynchronous receive.                         |

| DT               |            |       |       |          | I/O         | ST             | USART synchronous data.                             |

Legend: TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I = Input

P = Power

CMOS = CMOS compatible input or output

Analog = Analog input O = Output

TABLE 1-2: PINOUT I/O DESCRIPTIONS (CONTINUED)

|                       | Pin Number |       |      |       |             |                |                                                                                                        |

|-----------------------|------------|-------|------|-------|-------------|----------------|--------------------------------------------------------------------------------------------------------|

| Pin Name              | PIC1       | 8C601 | PIC1 | 8C801 | Pin<br>Type | Buffer<br>Type |                                                                                                        |

|                       | TQFP       | PLCC  | TQFP | PLCC  | .,,,,       | .,,,,,         | Description                                                                                            |

|                       |            |       |      |       |             |                | PORTD is a bi-directional I/O port. These pins have TTL input buffers when external memory is enabled. |

| RD0/AD0<br>RD0<br>AD0 | 58         | 3     | 72   | 3     | I/O<br>I/O  | ST<br>TTL      | Digital I/O.<br>External memory address/data 0.                                                        |

| RD1/AD1<br>RD1<br>AD1 | 55         | 67    | 69   | 83    | I/O<br>I/O  | ST<br>TTL      | Digital I/O. External memory address/data 1.                                                           |

| RD2/AD2<br>RD2<br>AD2 | 54         | 66    | 68   | 82    | I/O<br>I/O  | ST<br>TTL      | Digital I/O. External memory address/data 2.                                                           |

| RD3/AD3<br>RD3<br>AD3 | 53         | 65    | 67   | 81    | I/O<br>I/O  | ST<br>TTL      | Digital I/O. External memory address/data 3.                                                           |

| RD4/AD4<br>RD4<br>AD4 | 52         | 64    | 66   | 80    | I/O<br>I/O  | ST<br>TTL      | Digital I/O. External memory address/data 4.                                                           |

| RD5/AD5<br>RD5<br>AD5 | 51         | 63    | 65   | 79    | I/O<br>I/O  | ST<br>TTL      | Digital I/O. External memory address/data 5.                                                           |

| RD6/AD6<br>RD6<br>AD6 | 50         | 62    | 64   | 78    | I/O<br>I/O  | ST<br>TTL      | Digital I/O. External memory address/data 6.                                                           |

| RD7/AD7<br>RD7<br>AD7 | 49         | 61    | 63   | 77    | I/O<br>I/O  | ST<br>TTL      | Digital I/O. External memory address/data 7.                                                           |

Legend: TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I = Input

P = Power

CMOS = CMOS compatible input or output

Analog = Analog input

O = Output

TABLE 1-2: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          | Pin Number |       |       |       |             |                |                                     |

|----------|------------|-------|-------|-------|-------------|----------------|-------------------------------------|

| Pin Name | PIC18      | BC601 | PIC18 | BC801 | Pin<br>Type | Buffer<br>Type |                                     |

|          | TQFP       | PLCC  | TQFP  | PLCC  | .,,,,       | .,,,,,         | Description                         |

|          |            |       |       |       |             |                | PORTE is a bi-directional I/O port. |

| RE0/AD8  | 2          | 11    | 4     | 15    |             |                |                                     |

| RE0      |            |       |       |       | I/O         | ST             | Digital I/O.                        |

| AD8      |            |       |       |       | I/O         | TTL            | External memory address/data 8.     |

| RE1/AD9  | 1          | 10    | 3     | 14    |             |                |                                     |

| RE1      |            |       |       |       | I/O         | ST             | Digital I/O.                        |

| AD9      |            |       |       |       | I/O         | TTL            | External memory address/data 9.     |

| RE2/AD10 | 64         | 9     | 78    | 9     |             |                |                                     |

| RE2      |            |       |       |       | I/O         | ST             | Digital I/O.                        |

| AD10     |            |       |       |       | I/O         | TTL            | External memory address/data 10.    |

| RE3/AD11 | 63         | 8     | 77    | 8     |             |                |                                     |

| RE3      |            |       |       |       | I/O         | ST             | Digital I/O.                        |

| AD11     |            |       |       |       | I/O         | TTL            | External memory address/data 11.    |

| RE4/AD12 | 62         | 7     | 76    | 7     |             |                |                                     |

| RE4      |            |       |       |       | I/O         | ST             | Digital I/O.                        |

| AD12     |            |       |       |       | I/O         | TTL            | External memory address/data 12.    |

| RE5/AD13 | 61         | 6     | 75    | 6     |             |                |                                     |

| RE5      |            |       |       |       | I/O         | ST             | Digital I/O.                        |

| AD13     |            |       |       |       | I/O         | TTL            | External memory address/data 13.    |

| RE6/AD14 | 60         | 5     | 74    | 5     |             |                |                                     |

| RE6      |            |       |       |       | I/O         | ST             | Digital I/O.                        |

| AD14     |            |       |       |       | I/O         | TTL            | External memory address/data 14.    |

| RE7/AD15 | 59         | 4     | 73    | 4     |             |                |                                     |

| RE7      |            |       |       |       | I/O         | ST             | Digital I/O.                        |

| AD15     |            |       |       |       | I/O         | ST             | External memory address/data 15.    |

Legend: TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I = Input

P = Power

CMOS = CMOS compatible input or output

Analog = Analog input

O = Output

TABLE 1-2: PINOUT I/O DESCRIPTIONS (CONTINUED)

|                                    | Pin Number |       |         |        |             |                |                                                        |

|------------------------------------|------------|-------|---------|--------|-------------|----------------|--------------------------------------------------------|

| Pin Name                           | PIC18      | 3C601 | PIC18   | 8C801  | Pin<br>Type | Buffer<br>Type |                                                        |

|                                    | TQFP       | PLCC  | TQFP    | PLCC   | 1960        | 1,700          | Description                                            |

|                                    |            |       |         |        |             |                | PORTF is a bi-directional I/O port.                    |

| RF0/AN5                            | 18         | 28    | 24      | 36     |             | 0.7            | D: :: 11/0                                             |

| RF0<br>AN5                         |            |       |         |        | I/O<br>I    | ST<br>Analog   | Digital I/O.<br>Analog input 5.                        |

| RF1/AN6                            | 17         | 27    | 23      | 35     | '           | 7 trialog      | , water o.                                             |

| RF1                                |            |       |         |        | I/O         | ST             | Digital I/O.                                           |

| AN6                                |            |       |         |        | I           | Analog         | Analog input 6.                                        |

| RF2/AN7<br>RF2                     | 16         | 26    | 18      | 30     | I/O         | ST             | Dinital I/O                                            |

| AN7                                |            |       |         |        | 1/O<br>     | Analog         | Digital I/O. Analog input 7.                           |

| RF3/CSIO                           | 15         | 25    | 17      | 29     |             | 7              | , and og any at the                                    |

| RF3                                |            |       |         |        | I/O         | ST             | Digital I/O.                                           |

| CSIO                               |            |       |         |        | I/O         | ST             | System bus chip select I/O.                            |

| RF4/ <u>A16</u><br>RF4/ <u>CS2</u> | 14         | 24    | —<br>16 | <br>28 |             |                |                                                        |

| RF4/C52                            | _          | _     | 16      | 20     | I/O         | ST             | Digital I/O.                                           |

| A16                                |            |       |         |        | I/O         | TTL            | External memory address 16.                            |

| CS2                                |            |       |         |        | 0           | TTL            | Chip select 2.                                         |

| RF5/CS1                            | 13         | 23    | 15      | 27     | 1/0         | ОТ             | Di-it-11/O                                             |

| RF5<br>CS1                         |            |       |         |        | I/O<br>O    | ST<br>TTL      | Digital I/O.<br>Chip select 1.                         |

| RF6/LB                             | 12         | 22    | 14      | 26     |             |                | 5p 55.65                                               |

| RF6                                |            |       |         |        | I/O         | ST             | Digital I/O.                                           |

| LB                                 |            |       |         |        | 0           | TTL            | Low byte select signal for external memory interface.  |

| RF7/UB                             | 11         | 21    | 13      | 25     |             |                |                                                        |

| RF7                                |            |       |         |        | I/O         | ST             | Digital I/O.                                           |

| ŪB                                 |            |       |         |        | 0           | TTL            | High byte select signal for external memory interface. |

Legend: TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I = Input

P = Power

CMOS = CMOS compatible input or output

Analog = Analog input

O = Output

TABLE 1-2: PINOUT I/O DESCRIPTIONS (CONTINUED)

|                 | Pin Number |       |       |       |             |                |                                     |

|-----------------|------------|-------|-------|-------|-------------|----------------|-------------------------------------|

| Pin Name        | PIC18      | BC601 | PIC18 | BC801 | Pin<br>Type | Buffer<br>Type |                                     |

|                 | TQFP       | PLCC  | TQFP  | PLCC  | .,,,,       | .,,,,          | Description                         |

|                 |            |       |       |       |             |                | PORTG is a bi-directional I/O port. |

| RG0/ALE         | 3          | 12    | 5     | 16    |             |                |                                     |

| RG0             |            |       |       |       | I/O         | ST             | Digital I/O.                        |

| ALE             |            |       |       |       | 0           | TTL            | Address Latch Enable.               |

| RG1/OE          | 4          | 13    | 6     | 17    |             |                |                                     |

| <u>RG</u> 1     |            |       |       |       | I/O         | ST             | Digital I/O.                        |

| ŌĒ              |            |       |       |       | 0           | TTL            | Output Enable.                      |

| RG2/WRL         | 5          | 14    | 7     | 18    |             |                |                                     |

| RG2             |            |       |       |       | I/O         | ST             | Digital I/O.                        |

| WRL             |            |       |       |       | 0           | TTL            | Write Low control.                  |

| RG3/WRH         | 6          | 15    | 8     | 19    |             |                |                                     |

| RG3             |            |       |       |       | I/O         | ST             | Digital I/O.                        |

| WRH             |            |       |       |       | 0           | TTL            | Write High control.                 |

| RG4/BA0         | 8          | 17    | 10    | 21    |             |                |                                     |

| RG4             |            |       |       |       | I/O         | ST             | Digital I/O.                        |

| BA0             |            |       |       |       | 0           | TTL            | System bus byte address 0.          |

|                 |            |       |       |       |             |                | PORTH is a bi-directional I/O port. |

| RH0/A16         | _          | _     | 79    | 10    |             |                |                                     |

| RH0             |            |       |       |       | I/O         | ST             | Digital I/O.                        |

| A16             |            |       |       |       | 0           | TTL            | External memory address 16.         |

| RH1/A17         | _          | _     | 80    | 11    |             |                |                                     |

| RH1             |            |       |       |       | I/O         | ST             | Digital I/O.                        |

| A17             |            |       |       |       | 0           | _              | External memory address 17.         |

| RH2/A18         | _          | _     | 1     | 12    |             |                |                                     |

| RH2             |            |       |       |       | I/O         | ST             | Digital I/O.                        |

| A18             |            |       |       |       | 0           | _              | External memory address 18.         |

| RH3/A19         | _          | _     | 2     | 13    |             |                |                                     |

| RH3             |            |       |       |       | 1/0         | ST             | Digital I/O.                        |

| A19             |            |       |       |       | 0           | _              | External memory address 19.         |

| RH4/AN8         | _          | _     | 19    | 31    |             | 0.7            | D: 11 10                            |

| RH4             |            |       |       |       | I/O         | ST             | Digital I/O.                        |

| AN8             |            |       |       |       | I           | Analog         | Analog input 8.                     |

| RH5/AN9         | _          | _     | 20    | 32    | 1/0         | C <del></del>  | District I/O                        |

| RH5<br>AN9      |            |       |       |       | I/O<br>I    | ST<br>Analog   | Digital I/O.                        |

| _               |            |       | 0.4   | 00    | '           | Analog         | Analog input 9.                     |

| RH6/AN10        | _          | _     | 21    | 33    | 1/0         | ST             | Digital I/O                         |

| RH6<br>AN10     |            |       |       |       | I/O<br>I    | _              | Digital I/O.                        |

|                 |            |       | 20    | 0.4   | '           | Analog         | Analog input 10.                    |

| RH7/AN11<br>RH7 | _          | _     | 22    | 34    | I/O         | ST             | Digital I/O                         |

| AN11            |            |       |       |       | 1/O<br>     | Analog         | Digital I/O. Analog input 11.       |

| AINTI           |            |       |       |       |             | Alialog        | Λιταίος πιραί ττ.                   |

Legend: TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I = Input

P = Power

CMOS = CMOS compatible input or output

Analog = Analog input

O = Output

TABLE 1-2: PINOUT I/O DESCRIPTIONS (CONTINUED)

|               | Pin Number |         |        |         |             |                |                                          |

|---------------|------------|---------|--------|---------|-------------|----------------|------------------------------------------|

| Pin Name      | PIC1       | 8C601   | PIC1   | 8C801   | Pin<br>Type | Buffer<br>Type |                                          |

|               | TQFP       | PLCC    | TQFP   | PLCC    | Турс        | туре           | Description                              |

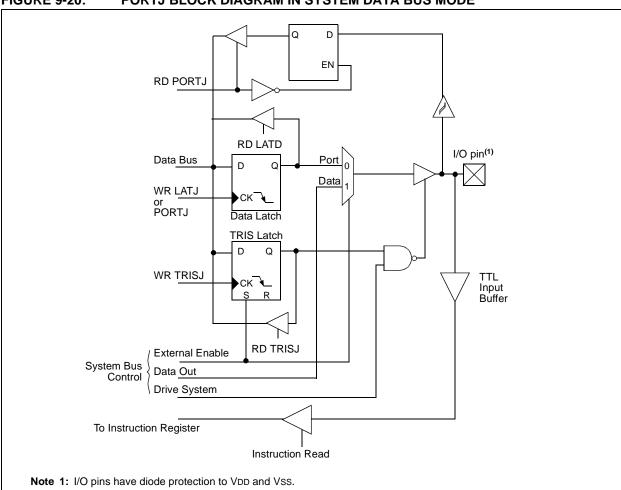

|               |            |         |        |         |             |                | PORTJ is a bi-directional I/O port.      |

| RJ0/D0        | _          | _       | 39     | 52      |             |                |                                          |

| RJ0           |            |         |        |         | I/O         | ST             | Digital I/O.                             |

| D0            |            |         |        |         | I/O         | TTL            | System bus data bit 0.                   |

| RJ1/D1        | _          | _       | 40     | 53      |             | 0.7            | 5: 11/0                                  |

| RJ1<br>D1     |            |         |        |         | I/O<br>I/O  | ST<br>TTL      | Digital I/O.                             |

| RJ2/D2        |            |         | 41     | 54      | 1/0         | IIL            | System bus data bit 1.                   |

| RJ2/D2<br>RJ2 | _          |         | 41     | 54      | I/O         | ST             | Digital I/O.                             |

| D2            |            |         |        |         | 1/0         | TTL            | System bus data bit 2.                   |

| RJ3/D3        | _          | _       | 42     | 55      |             |                |                                          |

| RJ3           |            |         |        |         | I/O         | ST             | Digital I/O.                             |

| D3            |            |         |        |         | I/O         | TTL            | System bus data bit 3.                   |

| RJ4/D4        | _          | _       | 59     | 73      |             |                |                                          |

| RJ4           |            |         |        |         | I/O         | ST             | Digital I/O.                             |

| D4            |            |         |        |         | I/O         | TTL            | System bus data bit 4.                   |

| RJ5/D5        | _          | _       | 60     | 74      |             |                |                                          |

| RJ5<br>D5     |            |         |        |         | I/O<br>I/O  | ST<br>TTL      | Digital I/O.                             |

| RJ6/D6        |            |         | 61     | 75      | 1/0         | IIL            | System bus data bit 5.                   |

| RJ6/D6        | _          |         | 01     | 75      | I/O         | ST             | Digital I/O.                             |

| D6            |            |         |        |         | 1/0         | TTL            | System bus data bit 6.                   |

| RJ7/D7        | _          | _       | 62     | 76      |             |                | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,  |

| RJ7           |            |         |        |         | I/O         | ST             | Digital I/O.                             |

| D7            |            |         |        |         | I/O         | TTL            | System bus data bit 7.                   |

| Vss           | 9, 25,     | 19, 36, | 11,31, | 23, 44, | Р           | _              | Ground reference for logic and I/O pins. |

|               | 41, 56     | 53, 68  | 51, 70 | 65, 84  |             |                |                                          |

| VDD           | 10,26,     | 2, 20,  | 12,32, | 2, 24,  | Р           | _              | Positive supply for logic and I/O pins.  |

|               | 38, 57     | 37, 49  | 48, 71 | 45, 61  |             |                |                                          |

| Avss          | 20         | 30      | 26     | 38      | P           | _              | Ground reference for analog modules.     |

| AVDD          | 19         | 29      | 25     | 37      | Р           |                | Positive supply for analog modules.      |

Legend: TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I = Input

P = Power

CMOS = CMOS compatible input or output

Analog = Analog input

O = Output

## 2.0 OSCILLATOR CONFIGURATIONS

#### 2.1 Oscillator Types

PIC18C601/801 can be operated in one of four oscillator modes, programmable by configuration bits FOSC1:FOSC0 in CONFIG1H register:

- 1. LP Low Power Crystal

- 2. HS High Speed Crystal/Resonator

- 3. RC External Resistor/Capacitor

- 4. EC External Clock

### 2.2 Crystal Oscillator/Ceramic Resonators

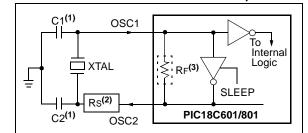

In LP or HS oscillator modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation. Figure 2-1 shows the pin connections. An external clock source may also be connected to the OSC1 pin, as shown in Figure 2-3 and Figure 2-4.

PIC18C601/801 oscillator design requires the use of a parallel cut crystal.

**Note:** Use of a series cut crystal may give a frequency out of the crystal manufacturer's specifications.

# FIGURE 2-1: CRYSTAL/CERAMIC RESONATOR OPERATION (HS OR LP OSC CONFIGURATION)

- **Note 1:** See Table 2-1 and Table 2-2 for recommended values of C1 and C2.

- **2:** A series resistor (Rs) may be required for AT strip cut crystals.

- 3: RF varies with the crystal chosen.

TABLE 2-1: CERAMIC RESONATORS

| Ranges Tested:                         |                                                       |                                 |                                     |  |  |  |  |  |

|----------------------------------------|-------------------------------------------------------|---------------------------------|-------------------------------------|--|--|--|--|--|

| Mode                                   | Mode Freq. OSC1                                       |                                 |                                     |  |  |  |  |  |

| HS                                     | 8.0 MHz<br>16.0 MHz<br>20.0 MHz<br>25.0 MHz           | 10 - 68 pF<br>10 - 22 pF<br>TBD | 10 €8 pF<br>10 €22 pF<br>√BD<br>TBD |  |  |  |  |  |

| HS+PLL                                 | 4.0 MHz                                               | MBD                             | TBD                                 |  |  |  |  |  |

|                                        | values are to<br>tes on this pa                       | r design guida<br>ge.           | nce only.                           |  |  |  |  |  |

|                                        | 777 \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \               | ators Used:                     |                                     |  |  |  |  |  |

| 40 MHz                                 | ADMIZ Murata Erie CSA4.00MG ± 0.5%                    |                                 |                                     |  |  |  |  |  |

| 8 0 MHz Murata Erie CSA8.00MT ± 0.5%   |                                                       |                                 |                                     |  |  |  |  |  |

| 16.0 MHz Murata Erie CSA16.00MX ± 0.5% |                                                       |                                 |                                     |  |  |  |  |  |

| All reso                               | All resonators used did not have built-in capacitors. |                                 |                                     |  |  |  |  |  |

TABLE 2-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq. | Cap. Range<br>C1 | Cap. Range<br>C2 |

|----------|------------------|------------------|------------------|

| LP       | 32.0 kHz         | 33 pF            | 33 pF            |

|          | 200 kHz          | 15 pF            | 15¢F             |

| HS       | 4.0 MHz          | 15 pF            | (15 pF)          |

|          | 8.0 MHz          | 15-33 pF         | 15-33 pF         |

|          | 20.0 MHz         | 15-33-pt         | 15-33 pF         |

|          | 25.0 MHz         | 1/ <u>/</u> /BD  | TBD              |

| HS+PLL   | 4.0 MH2          | √15 pF           | 15 pF            |

| These    | values are fo    | or design guida  | ince only.       |

| See not  | és on this pa    | ge.              |                  |

|          | Crys             | tals Used        |                  |

| 320 kHz  | Epson C-00       | 1R32.768K-A      | ± 20 PPM         |

| 200 kHz  | STD XTL          | 200.000kHz       | ± 20 PPM         |

| 1.0 MHz  | ECS EC           | ± 50 PPM         |                  |

| 4.0 MHz  | ECS EC           | ± 50 PPM         |                  |

| 8.0 MHz  | EPSON CA-        | ± 30 PPM         |                  |

| 20.0 MHz | EPSON CA-        | 301 20.000M-C    | ± 30 PPM         |

- **Note 1:** Recommended values of C1 and C2 are identical to the ranges tested (Table 2-1).

- **2:** Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

- **3:** Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- **4:** Rs may be required in HS mode to avoid overdriving crystals with low drive level specification.

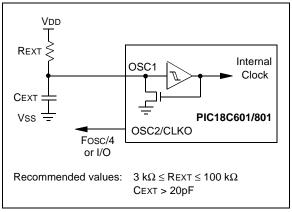

#### 2.3 RC Oscillator

For timing insensitive applications, the "RC" oscillator mode offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 2-2 shows how the RC combination is connected.

In the RC oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic.

FIGURE 2-2: RC OSCILLATOR MODE

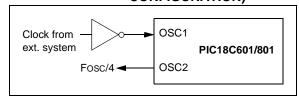

#### 2.4 External Clock Input

The EC oscillator mode requires an external clock source to be connected to the OSC1 pin. The feedback device between OSC1 and OSC2 is turned off in these modes to save current. There is no oscillator start-up time required after a Power-on Reset or after a recovery from SLEEP mode.

In the EC oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 2-3 shows the pin connections for the EC oscillator mode.

FIGURE 2-3: EXTERNAL CLOCK INPUT OPERATION (EC OSC CONFIGURATION)

#### 2.5 HS4 (PLL)

A Phase Lock Loop (PLL) circuit is provided as a software programmable option for users that want to multiply the frequency of the incoming crystal oscillator signal by 4. For an input clock frequency of 6 MHz, the internal clock frequency will be multiplied to 24 MHz. This is useful for customers who are concerned with EMI due to high frequency crystals.

The PLL is enabled by configuring HS oscillator mode and setting the PLLEN bit in the OSCON register. If HS oscillator mode is not selected, or PLLEN bit in OSCCON register is clear, the PLL is not enabled and the system clock will come directly from OSC1. HS oscillator mode is the default for PIC18C601/801. In all other modes, the PLLEN bit and the SCS1 bit are forced to '0'.

A PLL lock timer is used to ensure that the PLL has locked before device execution starts. The PLL lock timer has a time-out, referred to as TPLL.

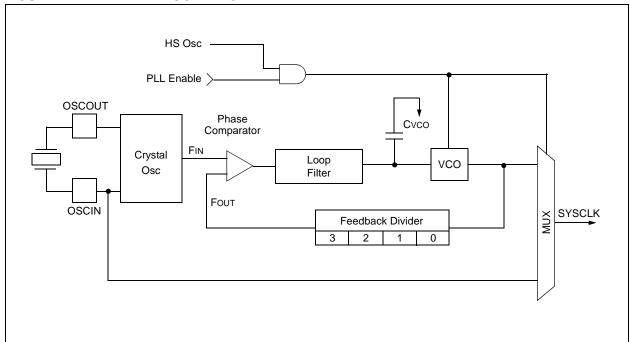

FIGURE 2-4: PLL BLOCK DIAGRAM

#### 2.6 Oscillator Switching Feature

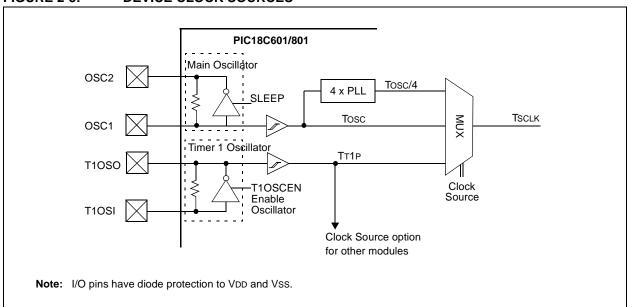

PIC18C601/801 devices include a feature that allows the system clock source to be switched from the main oscillator to an alternate low frequency clock source. For PIC18C601/801 devices, this alternate clock source is the Timer1 oscillator. If a low frequency crystal (32 kHz, for example) has been attached to the Timer1 oscillator pins and the Timer1 oscillator has been enabled, the device can switch to a low power execution mode. Figure 2-5 shows a block diagram of the system clock sources.

#### 2.6.1 SYSTEM CLOCK SWITCH BIT

The system clock source switching is performed under software control. The system clock switch bit, SCS0 (OSCCON register), controls the clock switching. When the SCS0 bit is '0', the system clock source comes from the main oscillator, selected by the FOSC2:FOSC0 configuration bits in CONFIG1H register. When the SCS0 bit is set, the system clock source will come from the Timer1 oscillator. The SCS0 bit is cleared on all forms of RESET.

The Timer1 oscillator must be enabled to switch the system clock source. The Timer1 oscillator is enabled by setting the T1OSCEN bit in the Timer1 control register (T1CON). If the Timer1 oscillator is not enabled, any write to the SCS0 bit will be ignored (SCS0 bit forced cleared) and the main oscillator will continue to be the system clock source.

FIGURE 2-5: DEVICE CLOCK SOURCES

Note:

#### REGISTER 2-1: OSCCON REGISTER

|   | U-0   | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|---|-------|-----|-----|-----|-------|-------|-------|-------|

| Ī | _     | _   | _   | _   | LOCK  | PLLEN | SCS1  | SCS0  |

| _ | bit 7 |     |     |     |       |       |       | bit 0 |

bit 7-4 **Unimplemented:** Read as '0'

bit 3 LOCK: Phase Lock Loop Lock Status bit

1 = Phase Lock Loop output is stable as system clock

0 = Phase Lock Loop output is not stable and cannot be used as system clock

bit 2 PLLEN: Phase Lock Loop Enable bit

1 = Enable Phase Lock Loop output as system clock

0 = Disable Phase Lock Loop

bit 1 SCS1: System Clock Switch bit 1

When PLLEN and LOCK bit are set:

1 = Use PLL output

0 = Use primary oscillator/clock input pin When PLLEN bit or LOCK bit is cleared:

Bit is forced clear

bit 0 SCS0: System Clock Switch bit 0

When T1OSCEN bit is set:

1 = Switch to Timer1 oscillator/clock pin

0 = Use primary oscillator/clock input pin

When T1OSCEN is cleared:

Bit is forced clear

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### 2.6.2 OSCILLATOR TRANSITIONS

PIC18C601/801 devices contain circuitry to prevent "glitches" when switching between oscillator sources. Essentially, the circuitry waits for eight rising edges of the clock source that the processor is switching to. This ensures that the new clock source is stable and that its pulse width will not be less than the shortest pulse width of the two clock sources.

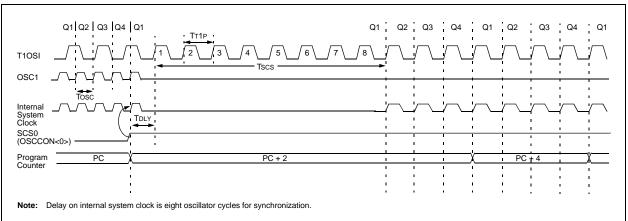

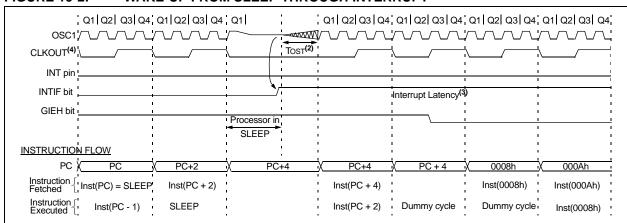

A timing diagram indicating the transition from the main oscillator to the Timer1 oscillator is shown in Figure 2-6. The Timer1 oscillator is assumed to be running all the time. After the SCS0 bit is set, the processor is frozen at the next occurring Q1 cycle. After eight synchronization cycles are counted from the Timer1 oscillator, operation resumes. No additional delays are required after the synchronization cycles.

The sequence of events that takes place when switching from the Timer1 oscillator to the main oscillator will depend on the mode of the main oscillator. In addition to eight clock cycles of the main oscillator, additional delays may take place.

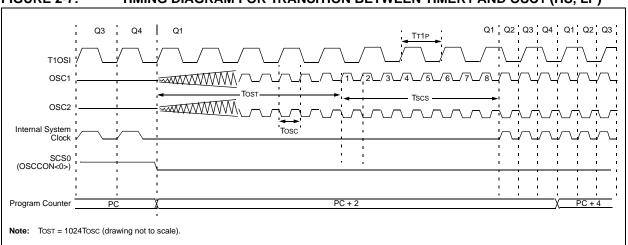

If the main oscillator is configured for an external crystal (HS, LP), the transition will take place after an oscillator start-up time (Tost) has occurred. A timing diagram indicating the transition from the Timer1 oscillator to the main oscillator for HS and LP modes is shown in Figure 2-7.

#### FIGURE 2-6: TIMING DIAGRAM FOR TRANSITION FROM OSC1 TO TIMER1 OSCILLATOR

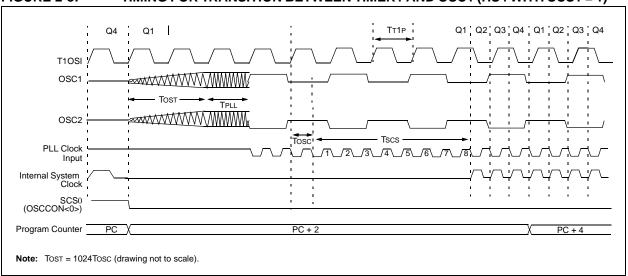

#### FIGURE 2-7: TIMING DIAGRAM FOR TRANSITION BETWEEN TIMER1 AND OSC1 (HS, LP)

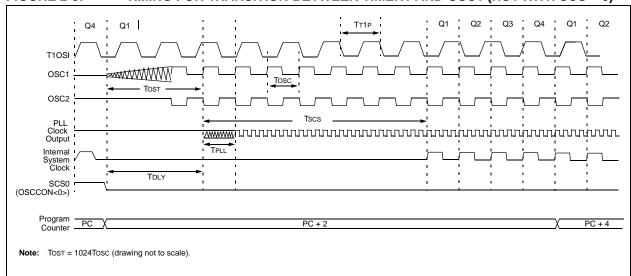

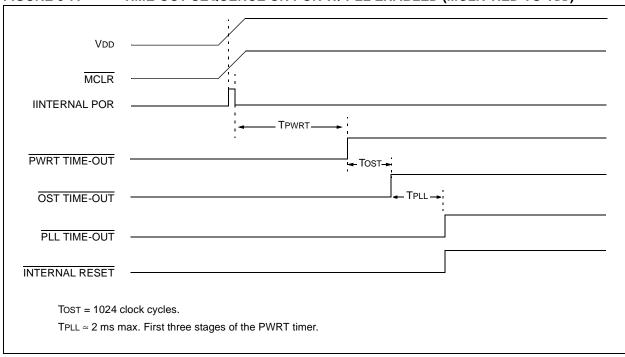

If the main oscillator is configured for HS4 (PLL) mode with SCS1 bit set to '1', an oscillator start-up time (Tost), plus an additional PLL time-out (TPLL) will occur. The PLL time-out is typically 2 ms and allows the PLL to lock to the main oscillator frequency. A timing diagram indicating the transition from the Timer1 oscillator to the main oscillator for HS4 mode is shown in Figure 2-8.

If the main oscillator is configured for HS4 (PLL) mode, with SCS1 bit set to '0', only oscillator start-up time (Tost) will occur. Since SCS1 bit is set to '0', PLL out-

put is not used, so the system oscillator will come from OSC1 directly and additional delay of TPLL is not required. A timing diagram indicating the transition from the Timer1 oscillator to the main oscillator for HS4 mode is shown in Figure 2-9.

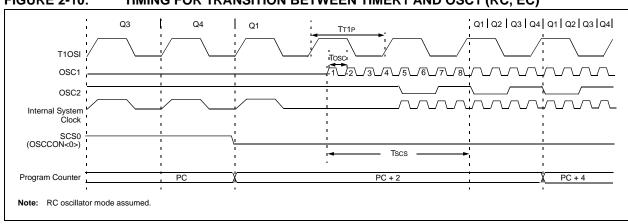

If the main oscillator is configured in the RC or EC modes, there is no oscillator start-up time-out. Operation will resume after eight cycles of the main oscillator have been counted. A timing diagram indicating the transition from the Timer1 oscillator to the main oscillator for RC and EC modes is shown in Figure 2-10.

FIGURE 2-8: TIMING FOR TRANSITION BETWEEN TIMER1 AND OSC1 (HS4 WITH SCS1 = 1)

FIGURE 2-9: TIMING FOR TRANSITION BETWEEN TIMER1 AND OSC1 (HS4 WITH SCS = 0)

FIGURE 2-10: TIMING FOR TRANSITION BETWEEN TIMER1 AND OSC1 (RC, EC)

#### 2.6.3 SCS0, SCS1 PRIORITY

If both SCS0 and SCS1 are set to '1' simultaneously, the SCS0 bit has priority over the SCS1 bit. This means that the low power option will take precedence over the PLL option. If both bits are cleared simultaneously, the system clock will come from OSC1, after a ToST timeout. If only the SCS0 bit is cleared, the system clock will come from the PLL output, following ToST and TPLL time.

TABLE 2-3: SCS0, SCS1 PRIORITY

| SCS1 | SCS0 | Clock Source        |

|------|------|---------------------|

| 0    | 0    | Ext Oscillator OSC1 |

| 0    | 1    | Timer1 Oscillator   |

| 1    | 0    | HS + PLL            |

| 1    | 1    | Timer1 Oscillator   |

#### 2.7 Effects of SLEEP Mode on the On-Chip Oscillator

When the device executes a SLEEP instruction, the on-chip clocks and oscillator are turned off and the device is held at the beginning of an instruction cycle (Q1 state). With the oscillator off, the OSC1 and OSC2 signals will stop oscillating. Since all the transistor switching currents have been removed, SLEEP mode achieves the lowest current consumption of the device (only leakage currents). Enabling any on-chip feature that will operate during SLEEP, will increase the cur-

rent consumed during SLEEP. The user can wake from SLEEP through external RESET, Watchdog Timer Reset, or through an interrupt.

#### 2.8 Power-up Delays

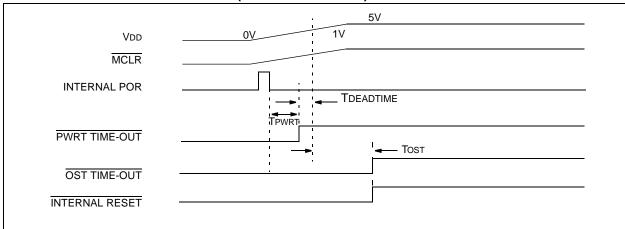

Power-up delays are controlled by two timers, so that no external RESET circuitry is required for most applications. The delays ensure that the device is kept in RESET until the device power supply and clock are stable. For additional information on RESET operation, see Section 3.0 RESET.

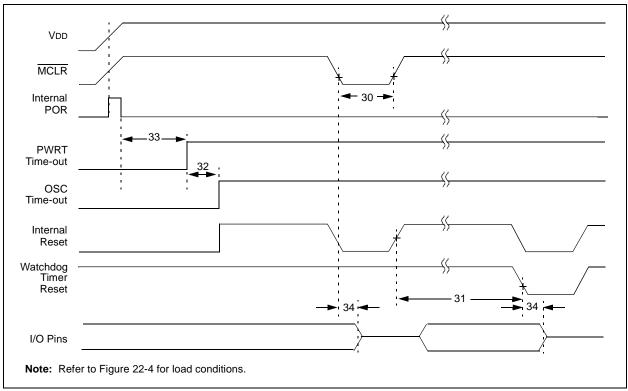

The first timer is the Power-up Timer (PWRT), which optionally provides a fixed delay of TPWRT (parameter #33) on power-up only. The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable.

PIC18C601/801 devices provide a configuration bit, PWRTEN in CONFIG2L register, to enable or disable the Power-up Timer. By default, the Power-up Timer is enabled.

With the PLL enabled (HS4 oscillator mode), the time-out sequence following a Power-on Reset is different from other oscillator modes. The time-out sequence is as follows: the PWRT time-out is invoked after a POR time delay has expired, then, the Oscillator Start-up Timer (OST) is invoked. However, this is still not a sufficient amount of time to allow the PLL to lock at high frequencies. The PWRT timer is used to provide an additional time-out, called TPLL (parameter #7), to allow the PLL ample time to lock to the incoming clock frequency.

TABLE 2-4: OSC1 AND OSC2 PIN STATES IN SLEEP MODE

| OSC Mode  | OSC1 Pin                                               | OSC2 Pin                                               |

|-----------|--------------------------------------------------------|--------------------------------------------------------|

| RC        | Floating, external resistor should pull high           | At logic low                                           |

| EC        | Floating                                               | At logic low                                           |

| LP and HS | Feedback inverter disabled, at quiescent voltage level | Feedback inverter disabled, at quiescent voltage level |

Note: See Table 3-1 in Section 3.0 RESET, for time-outs due to SLEEP and MCLR Reset.

#### 3.0 RESET

PIC18C601/801 devices differentiate between various kinds of RESET:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during SLEEP

- d) Watchdog Timer (WDT) Reset during normal operation

- e) RESET Instruction

- f) Stack Full Reset

- g) Stack Underflow Reset

Most registers are unaffected by a RESET. Their status is unknown on POR and unchanged by all other RESETS. The other registers are forced to a "RESET" state on Power-on Reset, MCLR, WDT Reset, MCLR Reset during SLEEP, and by the RESET instruction.

Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register,  $\overline{\text{RI}}$ ,  $\overline{\text{TO}}$ ,  $\overline{\text{PD}}$  and  $\overline{\text{POR}}$ , are set or cleared differently in different RESET situations, as indicated in Table 3-2. These bits are used in software to determine the nature of the RESET. See Table 3-3 for a full description of the RESET states of all registers.

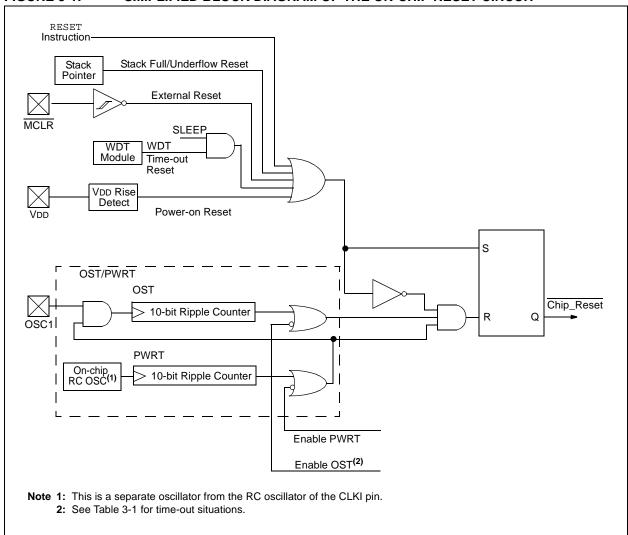

A simplified block diagram of the on-chip RESET circuit is shown in Figure 3-1.

PIC18C601/801 has a  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

A WDT Reset does not drive MCLR pin low.

FIGURE 3-1: SIMPLIFIED BLOCK DIAGRAM OF THE ON-CHIP RESET CIRCUIT

#### 3.1 Power-on Reset (POR)

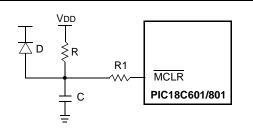

A Power-on Reset pulse is generated on-chip when a VDD rise is detected. To take advantage of the POR circuitry, connect the MCLR pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified (parameter D004). For a slow rise time, see Figure 3-2.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met. Power-on Reset may be used to meet the voltage start-up condition.

# FIGURE 3-2: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if the VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2:  $R < 40 \ k\Omega$  is recommended to make sure that the voltage drop across R does not violate the device's electrical specification.

- 3: R1 =  $100\Omega$  to 1 k $\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C, in the event of  $\overline{MCLR}$ /VPP pin breakdown due to Electrostatic Discharge (ESD), or Electrical Overstress (EOS).

#### 3.2 Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out (parameter #33), only on power-up from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. The PWRT time delay allows VDD to rise to an acceptable level. PIC18C601/801 devices are available with PWRT enabled or disabled.

The power-up time delay will vary from chip to chip, due to VDD, temperature and process variation. See DC parameter #33 for details.

#### 3.3 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (parameter #32). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for LP, HS and HS4 modes and only on Power-on Reset or wake-up from SLEEP.

#### 3.4 PLL Lock Time-out

With the PLL enabled, the time-out sequence following a Power-on Reset is different from other oscillator modes. A portion of the Power-up Timer is used to provide a fixed time-out that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 1 ms and follows the oscillator start-up time-out (OST).

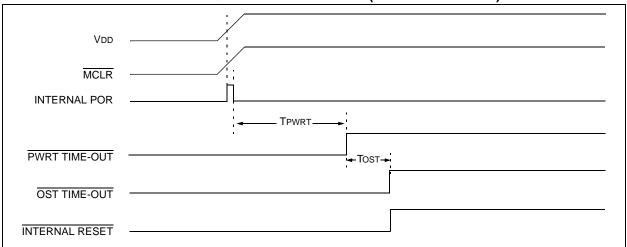

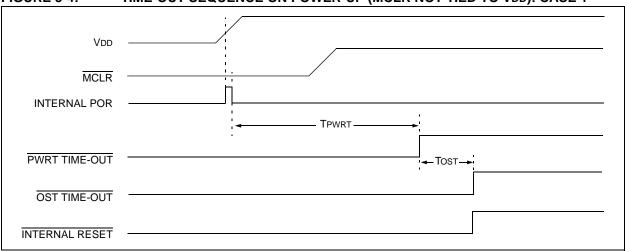

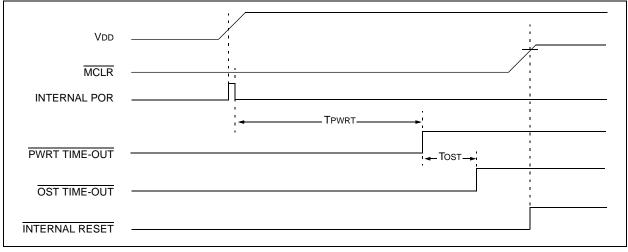

#### 3.5 Time-out Sequence

On power-up, the time-out sequence is as follows: First, PWRT time-out is invoked after the POR time delay has expired; then, OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 3-3, Figure 3-4, Figure 3-5, Figure 3-6 and Figure 3-7 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the time-outs will expire. Bringing MCLR high will begin execution immediately (Figure 3-5). This is useful for testing purposes or to synchronize more than one PIC18C601/801 device operating in parallel.

Table 3-2 shows the RESET conditions for some Special Function Registers, while Table 3-3 shows the RESET conditions for all registers.

TABLE 3-1: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator                         | Powe             | Wake-up from |                                              |  |

|------------------------------------|------------------|--------------|----------------------------------------------|--|

| Configuration                      | PWRTEN = 0       | PWRTEN = 1   | SLEEP or<br>Oscillator Switch <sup>(1)</sup> |  |

| HS with PLL enabled <sup>(1)</sup> | 72 ms + 1024Tosc | 1024Tosc     | 1024Tosc + 1 ms                              |  |

| HS, LP                             | 72 ms + 1024Tosc | 1024Tosc     | 1024Tosc                                     |  |

| EC                                 | 72 ms            | _            | _                                            |  |

| External RC                        | 72 ms            | _            | _                                            |  |

Note 1: 1 ms is the nominal time required for the 4X PLL to lock. Maximum time is 2 ms.

2: 72 ms is the nominal Power-up Timer delay.

#### REGISTER 3-1: RCON REGISTER BITS AND POSITIONS

| R/W-0 | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | U-0   |

|-------|-----|-----|-------|-------|-------|-------|-------|

| IPEN  | r   | _   | RI    | TO    | PD    | POR   | r     |

| bit 7 |     |     |       |       |       |       | bit 0 |

TABLE 3-2: STATUS BITS, THEIR SIGNIFICANCE, AND THE INITIALIZATION CONDITION FOR RCON REGISTER

| Condition                                     | Program<br>Counter    | RCON<br>Register | RI | то | PD | POR | STKFUL | STKUNF |

|-----------------------------------------------|-----------------------|------------------|----|----|----|-----|--------|--------|

| Power-on Reset                                | 00000h                | 0r-1 110r        | 1  | 1  | 1  | 0   | u      | u      |

| MCLR Reset during normal operation            | 00000h                | 0r-u uuur        | u  | u  | u  | u   | u      | u      |

| Software Reset during normal operation        | 00000h                | 0r-0 uuur        | 0  | u  | u  | u   | u      | u      |

| Stack Full Reset during normal operation      | 00000h                | 0r-u uu1r        | u  | u  | u  | 1   | u      | 1      |

| Stack Underflow Reset during normal operation | 00000h                | 0r-u uu1r        | u  | u  | u  | 1   | 1      | u      |

| MCLR Reset during SLEEP                       | 00000h                | 0r-u 10ur        | u  | 1  | 0  | u   | u      | u      |

| WDT Reset                                     | 00000h                | 0r-u 01ur        | u  | 0  | 1  | u   | u      | u      |

| WDT Wake-up                                   | PC + 2                | ur-u 00ur        | u  | 0  | 0  | u   | u      | u      |

| Interrupt wake-up from SLEEP                  | PC + 2 <sup>(1)</sup> | ur-u 00ur        | u  | 0  | 0  | u   | u      | u      |

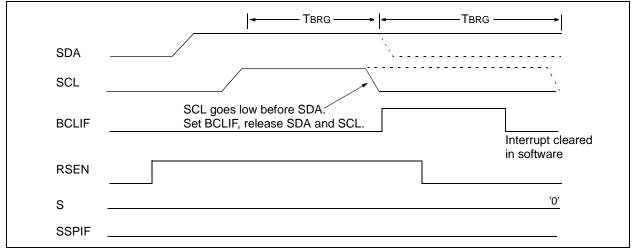

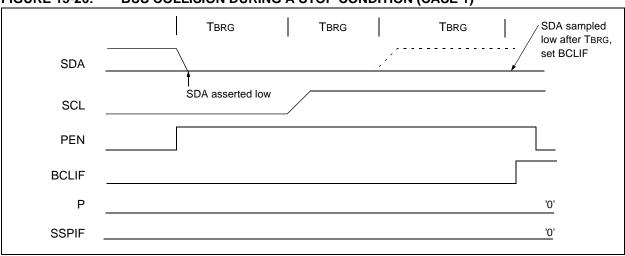

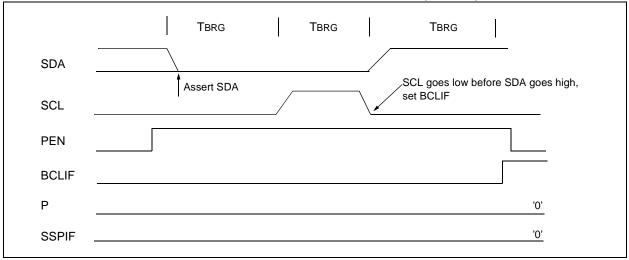

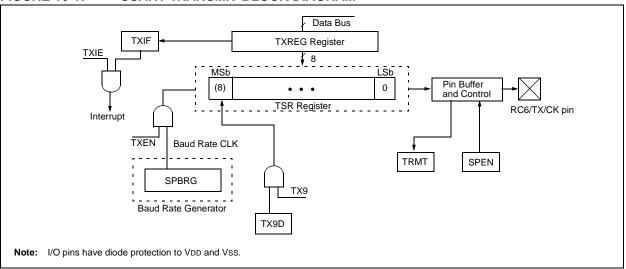

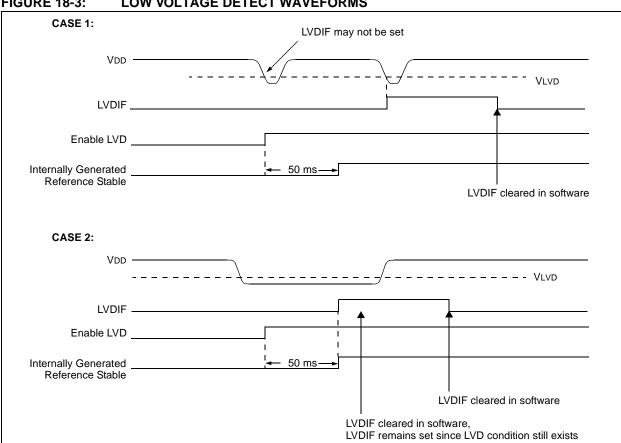

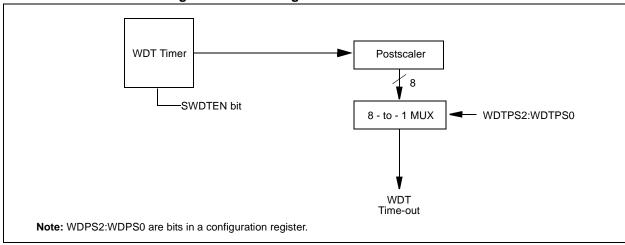

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', r = reserved, maintain '0'