# Single-Channel, 1024-Position, 1% R-Tolerance Digital Potentiometer

AD5293

#### **FEATURES**

Single-channel, 1024-position resolution 20 k $\Omega$ , 50 k $\Omega$ , and 100 k $\Omega$  nominal resistance Calibrated 1% nominal resistor tolerance (resistor performance mode)

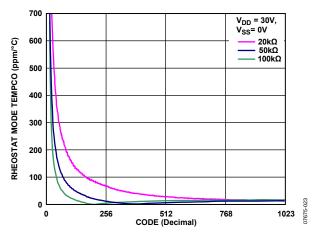

Rheostat mode temperature coefficient: 35 ppm/°C Voltage divider temperature coefficient: 5 ppm/°C Single-supply operation: 9 V to 33 V Dual-supply operation:  $\pm 9$  V to  $\pm 16.5$  V

SPI-compatible serial interface

Wiper setting readback

#### **APPLICATIONS**

Mechanical potentiometer replacement

Instrumentation: gain and offset adjustment

Programmable voltage-to-current conversion

Programmable filters, delays, and time constants

Programmable power supply

Low resolution DAC replacements

Sensor calibration

#### **GENERAL DESCRIPTION**

The AD5293 is a single-channel, 1024-position digital potentiometer  $^1$  with a <1% end-to-end resistor tolerance error. The AD5293 performs the same electronic adjustment function as a mechanical potentiometer with enhanced resolution, solid state reliability, and superior low temperature coefficient performance. This device is capable of operating at high voltages and supporting both dual-supply operation at  $\pm 10.5~\rm V$  to  $\pm 15~\rm V$  and single-supply operation at 21 V to 30 V.

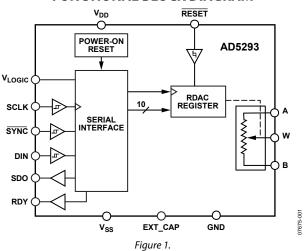

#### **FUNCTIONAL BLOCK DIAGRAM**

The AD5293 offers guaranteed industry-leading low resistor tolerance errors of  $\pm 1\%$  with a nominal temperature coefficient of 35 ppm/°C. The low resistor tolerance feature simplifies open-loop applications as well as precision calibration and tolerance matching applications.

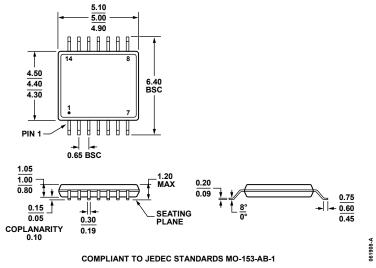

The AD5293 is available in a compact 14-lead TSSOP package. The part is guaranteed to operate over the extended industrial temperature range of  $-40^{\circ}$ C to  $+105^{\circ}$ C.

<sup>&</sup>lt;sup>1</sup> In this data sheet, the terms digital potentiometer and RDAC are used interchangeably.

#### TABLE OF CONTENTS Features ......1 Applications......1 Functional Block Diagram ......1 General Description.....1 Revision History ......2 Specifications......3 Electrical Characteristics—20 kΩ Versions......3 Resistor Performance Mode Code Range—20 kΩ Versions ...4 Electrical Characteristics—50 kΩ and 100 kΩ Versions......5 Resistor Performance Mode Code Range—50 k $\Omega$ and 100 k $\Omega$ Programming the Potentiometer Divider .......21 Versions......6 Timing Diagrams.....8 Absolute Maximum Ratings......9 High Voltage DAC......22 Programmable Voltage Source with Boosted Output............ 22 ESD Caution 9 Ordering Guide......24 **REVISION HISTORY** 3/11—Rev. C to Rev. D Changes to Table 1, Endnote 2 ......4 Changes to Table 2......4 9/10—Rev. B to Rev. C Changes to Table 6 and Note 1, Table 7......9 Added CPOL = 0, CPHA = 1 to Figure 3 and Figure 4 Captions.....8 Changes to SDO Pin and Daisy-Chain Operation Section...... 19 Changes to Typical Performance Characteristics Section....... 11 Changes to Programming the Variable Resistor Section ........ 20 Changes to Programming the Potentiometer 3/10-Rev. A to Rev. B Changes to Resistor Noise Density Conditions (Table 3) .......... 6 12/09-Rev. 0 to Rev. A

4/09—Revision 0: Initial Version

### **SPECIFICATIONS**

#### ELECTRICAL CHARACTERISTICS—20 kΩ VERSIONS

$V_{DD} = 21 \text{ V to } 33 \text{ V}, V_{SS} = 0 \text{ V}; V_{DD} = 10.5 \text{ V to } 16.5 \text{ V}, V_{SS} = -10.5 \text{ V to } -16.5 \text{ V}; V_{LOGIC} = 2.7 \text{ V to } 5.5 \text{ V}, V_A = V_{DD}, V_B = V_{SS}, -40^{\circ}\text{C} < T_A < +105^{\circ}\text{C}, \text{ unless otherwise noted.}$

Table 1.

| Parameter                                                | Symbol                                        | Conditions                                                              | Min                      | Typ <sup>1</sup> | Max       | Unit   |

|----------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------|--------------------------|------------------|-----------|--------|

| DC CHARACTERISTICS,<br>RHEOSTAT MODE                     |                                               |                                                                         |                          |                  |           |        |

| Resolution                                               | N                                             |                                                                         | 10                       |                  |           | Bits   |

| Resistor Differential Nonlinearity <sup>2</sup>          | R-DNL                                         | RwB                                                                     | -1                       |                  | +1        | LSB    |

| Resistor Integral Nonlinearity <sup>2</sup>              | R-INL                                         | $ V_{DD} - V_{SS}  = 26 \text{ V to } 33 \text{ V}$                     | -2                       |                  | +2        | LSB    |

| j ,                                                      | R-INL                                         | $ V_{DD} - V_{SS}  = 21 \text{ V to } 26 \text{ V}$                     | -3                       |                  | +3        | LSB    |

| Nominal Resistor Tolerance<br>(R-Perf Mode) <sup>3</sup> | ΔR <sub>AB</sub> /R <sub>AB</sub>             | See Table 2                                                             | -1                       | ±0.5             | +1        | %      |

| Nominal Resistor Tolerance<br>(Normal Mode)              | ΔR <sub>AB</sub> /R <sub>AB</sub>             |                                                                         |                          | ±7               |           | %      |

| Resistance Temperature Coefficient <sup>4</sup>          | $(\Delta R_{AB}/R_{AB})/\Delta T \times 10^6$ |                                                                         |                          | 35               |           | ppm/°C |

| Wiper Resistance                                         | Rw                                            |                                                                         |                          | 60               | 100       | Ω      |

| DC CHARACTERISTICS, POTENTIOMETER DIVIDER MODE           |                                               |                                                                         |                          |                  |           |        |

| Resolution                                               | N                                             |                                                                         | 10                       |                  |           | Bits   |

| Differential Nonlinearity <sup>5</sup>                   | DNL                                           |                                                                         | -1                       |                  | +1        | LSB    |

| Integral Nonlinearity⁵                                   | INL                                           |                                                                         | -1.5                     |                  | +1.5      | LSB    |

| Voltage Divider Temperature<br>Coefficient <sup>4</sup>  | $(\Delta V_W/V_W)/\Delta T \times 10^6$       | Code = half scale                                                       |                          | 5                |           | ppm/°C |

| Full-Scale Error                                         | $V_{WFSE}$                                    | Code = full scale                                                       | -8                       |                  | 0         | LSB    |

| Zero-Scale Error                                         | V <sub>wzse</sub>                             | Code = zero scale                                                       | 0                        |                  | 8         | LSB    |

| RESISTOR TERMINALS                                       |                                               |                                                                         |                          |                  |           |        |

| Terminal Voltage Range <sup>6</sup>                      | $V_A$ , $V_B$ , $V_W$                         |                                                                         | Vss                      |                  | $V_{DD}$  | ٧      |

| Capacitance A, Capacitance B <sup>4</sup>                | C <sub>A</sub> , C <sub>B</sub>               | f = 1 MHz, measured to GND, code = half-scale                           |                          | 85               |           | pF     |

| Capacitance W <sup>4</sup>                               | Cw                                            | f = 1 MHz, measured to GND, code = half-scale                           |                          | 65               |           | pF     |

| Common-Mode Leakage Current                              | Ісм                                           | $V_A = V_B = V_W$                                                       |                          | ±1               |           | nA     |

| DIGITAL INPUTS                                           |                                               |                                                                         | JED                      | EC comp          | liant     |        |

| Input Logic High                                         | V <sub>IH</sub>                               | $V_{LOGIC} = 2.7 \text{ V to } 5.5 \text{ V}$                           | 2.0                      |                  |           | V      |

| Input Logic Low                                          | VIL                                           | $V_{LOGIC} = 2.7 \text{ V to } 5.5 \text{ V}$                           |                          |                  | 0.8       | V      |

| Input Current                                            | I <sub>IL</sub>                               | $V_{IN} = 0 V \text{ or } V_{LOGIC}$                                    |                          |                  | ±1        | μΑ     |

| Input Capacitance⁴                                       | C <sub>IL</sub>                               |                                                                         |                          | 5                |           | рF     |

| DIGITAL OUTPUTS (SDO and RDY)                            |                                               |                                                                         |                          |                  |           |        |

| Output High Voltage                                      | V <sub>OH</sub>                               | $R_{PULL\_UP} = 2.2 \text{ k}\Omega \text{ to } V_{LOGIC}$              | V <sub>LOGIC</sub> – 0.4 |                  |           | ٧      |

| Output Low Voltage                                       | V <sub>OL</sub>                               | $R_{PULL\_UP} = 2.2 \text{ k}\Omega \text{ to } V_{LOGIC}$              |                          |                  | GND + 0.4 | ٧      |

| Tristate Leakage Current                                 |                                               |                                                                         | -1                       |                  | +1        | μΑ     |

| Output Capacitance <sup>4</sup>                          | C <sub>OL</sub>                               |                                                                         |                          | 5                |           | pF     |

| POWER SUPPLIES                                           |                                               |                                                                         |                          |                  |           |        |

| Single-Supply Power Range                                | $V_{DD}$                                      | $V_{SS} = 0 V$                                                          | 9                        |                  | 33        | V      |

| Dual-Supply Power Range                                  | $V_{DD}/V_{SS}$                               |                                                                         | ±9                       |                  | ±16.5     | V      |

| Positive Supply Current                                  | I <sub>DD</sub>                               | $V_{DD}/V_{SS} = \pm 16.5 \text{ V}$                                    |                          | 0.1              | 2         | μΑ     |

| Negative Supply Current                                  | Iss                                           | $V_{DD}/V_{SS} = \pm 16.5 \text{ V}$                                    | -2                       | -0.1             |           | μΑ     |

| Logic Supply Range                                       | V <sub>LOGIC</sub>                            |                                                                         | 2.7                      |                  | 5.5       | V      |

| Logic Supply Current                                     | ILOGIC                                        | $V_{LOGIC} = 5 \text{ V}; V_{IH} = 5 \text{ V or } V_{IL} = \text{GND}$ |                          | 1                | 10        | μΑ     |

| Power Dissipation <sup>7</sup>                           | P <sub>DISS</sub>                             | $V_{IH} = 5 \text{ V or } V_{IL} = \text{GND}$                          |                          | 8                | 110       | μW     |

| Power Supply Rejection Ratio <sup>4</sup>                | PSSR                                          | $\Delta V_{DD}/\Delta V_{SS} = \pm 15 \text{ V} \pm 10\%$               |                          | 0.103            |           | %/%    |

| Parameter                               | Symbol            | Conditions                                                                                            | Min Typ <sup>1</sup> | Max | Unit   |

|-----------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------|----------------------|-----|--------|

| DYNAMIC CHARACTERISTICS <sup>4, 8</sup> |                   |                                                                                                       |                      |     |        |

| Bandwidth                               | BW                | -3 dB                                                                                                 | 520                  |     | kHz    |

| <b>Total Harmonic Distortion</b>        | THDw              | $V_A = 1 \text{ V rms}, V_B = 0 \text{ V}, f = 1 \text{ kHz},$                                        | -93                  |     | dB     |

| V <sub>W</sub> Settling Time            | ts                | $V_A = 30 \text{ V}, V_B = 0 \text{ V}, \pm 0.5 \text{ LSB error}$<br>band, initial code = zero scale |                      |     |        |

|                                         |                   | Code = full scale, R-normal mode                                                                      | 750                  |     | ns     |

|                                         |                   | Code = full scale, R-perf mode                                                                        | 2.5                  |     | μs     |

|                                         |                   | Code = half scale, R-normal mode                                                                      | 2.5                  |     | μs     |

|                                         |                   | Code = half scale, R-perf mode                                                                        | 5                    |     | μs     |

| Resistor Noise Density                  | e <sub>N_WB</sub> | $R_{WB} = 10 \text{ k}\Omega$ , $T_A = 25^{\circ}\text{C}$ , $0 \text{ kHz}$ to $200 \text{ kHz}$     | 10                   |     | nV/√Hz |

$<sup>^{1}</sup>$  Typicals represent average readings at 25°C;  $V_{DD} = +15 \text{ V}$ ,  $V_{SS} = -15 \text{ V}$ , and  $V_{LOGIC} = 5 \text{ V}$ .

#### RESISTOR PERFORMANCE MODE CODE RANGE—20 kΩ VERSIONS

Table 2.

| Resistor       |                                                     |                        | 20 kΩ                                               |                        |                                                     |                        |                                                     |                        |

|----------------|-----------------------------------------------------|------------------------|-----------------------------------------------------|------------------------|-----------------------------------------------------|------------------------|-----------------------------------------------------|------------------------|

| Tolerance      | $ V_{DD} - V_{SS}  = 30 \text{ V to } 33 \text{ V}$ |                        | $ V_{DD} - V_{SS}  = 26 \text{ V to } 30 \text{ V}$ |                        | $ V_{DD} - V_{SS}  = 22 \text{ V to } 26 \text{ V}$ |                        | $ V_{DD} - V_{SS}  = 21 \text{ V to } 22 \text{ V}$ |                        |

| per Code       | R <sub>WB</sub>                                     | Rwa                    |

| 1% R-Tolerance | From 0x15E<br>to 0x3FF                              | From 0x000<br>to 0x2A1 | From 0x1F4<br>to 0x3FF                              | From 0x000<br>to 0x20B | From 0x1F4<br>to 0x3FF                              | From 0x000<br>to 0x20B | N/A                                                 | N/A                    |

| 2% R-Tolerance | From 0x8C<br>to 0x3FF                               | From 0x000<br>to 0x373 | From 0xB4<br>to 0x3FF                               | From 0x000<br>to 0x34B | From 0xFA<br>to 0x3FF                               | From 0x000<br>to 0x305 | From 0xFA<br>to 0x3FF                               | From 0x000<br>to 0x305 |

| 3% R-Tolerance | From 0x5A<br>to 0x3FF                               | From 0x000<br>to 0x3A5 | From 0x64<br>to 0x3FF                               | From 0x000<br>to 0x39B | From 0x78<br>to 0x3FF                               | From 0x000<br>to 0x387 | From 0x78<br>to 0x3FF                               | From 0x000<br>to 0x387 |

Pyblical Replace of the Web School of the S

<sup>&</sup>lt;sup>3</sup> The terms resistor performance mode and R-perf mode are used interchangeably.

<sup>&</sup>lt;sup>4</sup> Guaranteed by design; not subject to production test.

<sup>&</sup>lt;sup>5</sup> INL and DNL are measured at  $V_W$  with the RDAC configured as a potentiometer divider similar to a voltage output DAC.  $V_A = V_{DD}$  and  $V_B = 0$  V. DNL specification limits of  $\pm 1$  LSB maximum are guaranteed monotonic operating conditions.

<sup>&</sup>lt;sup>6</sup> The A, B, and W resistor terminals have no limitations on polarity with respect to each other. Dual-supply operation enables ground-referenced bipolar signal adjustment.

<sup>&</sup>lt;sup>7</sup>  $P_{DISS}$  is calculated from  $(I_{DD} \times V_{DD}) + (I_{SS} \times V_{SS}) + (I_{LOGIC} \times V_{LOGIC})$ .

$<sup>^8</sup>$  All dynamic characteristics use  $V_{DD} = +15 \ V, \, V_{SS} = -15 \ V, \, and \, V_{LOGIC} = 5 \ V.$

#### ELECTRICAL CHARACTERISTICS—50 $k\Omega$ AND 100 $k\Omega$ VERSIONS

$V_{\text{DD}} = 21 \text{ V to } 33 \text{ V, } V_{\text{SS}} = 0 \text{ V; } V_{\text{DD}} = 10.5 \text{ V to } 16.5 \text{ V, } V_{\text{SS}} = -10.5 \text{ V to } -16.5 \text{ V; } V_{\text{LOGIC}} = 2.7 \text{ V to } 5.5 \text{ V, } V_{\text{A}} = V_{\text{DD}}, V_{\text{B}} = V_{\text{SS}}, -40^{\circ}\text{C} < T_{\text{A}} < +105^{\circ}\text{C, unless otherwise noted.}$

Table 3.

| Parameter                                                | Symbol                                        | Conditions                                                       | Min                      | Typ <sup>1</sup> | Max       | Unit   |

|----------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------|--------------------------|------------------|-----------|--------|

| DC CHARACTERISTICS,                                      |                                               |                                                                  |                          |                  |           |        |

| RHEOSTAT MODE                                            |                                               |                                                                  |                          |                  |           |        |

| Resolution                                               | N                                             |                                                                  | 10                       |                  |           | Bits   |

| Resistor Differential Nonlinearity <sup>2</sup>          | R-DNL                                         | R <sub>WB</sub>                                                  | -1                       |                  | +1        | LSB    |

| Resistor Integral Nonlinearity <sup>2</sup>              | R-INL                                         |                                                                  | -2                       |                  | +2        | LSB    |

| Nominal Resistor Tolerance<br>(R-Perf Mode) <sup>3</sup> | $\Delta R_{AB}/R_{AB}$                        | See Table 4                                                      | -1                       | ±0.5             | +1        | %      |

| Nominal Resistor Tolerance<br>(Normal Mode)              | ΔR <sub>AB</sub> /R <sub>AB</sub>             |                                                                  |                          | ±20              |           | %      |

| Resistance Temperature Coefficient <sup>4</sup>          | $(\Delta R_{AB}/R_{AB})/\Delta T \times 10^6$ |                                                                  |                          | 35               |           | ppm/°C |

| Wiper Resistance                                         | Rw                                            |                                                                  |                          | 60               | 100       | Ω      |

| DC CHARACTERISTICS, POTENTIOMETER DIVIDER MODE           |                                               |                                                                  |                          |                  |           |        |

| Resolution                                               | N                                             |                                                                  | 10                       |                  |           | Bits   |

| Differential Nonlinearity <sup>5</sup>                   | DNL                                           |                                                                  | -1                       |                  | +1        | LSB    |

| Integral Nonlinearity <sup>5</sup>                       | INL                                           |                                                                  | -1.5                     |                  | +1.5      | LSB    |

| Voltage Divider Temperature<br>Coefficient <sup>4</sup>  | $(\Delta V_w/V_w)/\Delta T \times 10^6$       | Code = half scale                                                |                          | 5                |           | ppm/°C |

| Full-Scale Error                                         | V <sub>WFSE</sub>                             | Code = full scale                                                | -8                       |                  | +1        | LSB    |

| Zero-Scale Error                                         | V <sub>WZSE</sub>                             | Code = zero scale                                                | 0                        |                  | 8         | LSB    |

| RESISTOR TERMINALS                                       |                                               |                                                                  |                          |                  |           |        |

| Terminal Voltage Range <sup>6</sup>                      | $V_A$ , $V_B$ , $V_W$                         |                                                                  | V <sub>SS</sub>          |                  | $V_{DD}$  | V      |

| Capacitance A, Capacitance B <sup>4</sup>                | C <sub>A</sub> , C <sub>B</sub>               | f = 1 MHz, measured to GND, code = half-scale                    |                          | 85               |           | pF     |

| Capacitance W <sup>4</sup>                               | Cw                                            | f = 1 MHz, measured to GND, code = half-scale                    |                          | 65               |           | pF     |

| Common-Mode Leakage Current                              | Ісм                                           | $V_A = V_B = V_W$                                                |                          | ±1               |           | nA     |

| DIGITAL INPUTS                                           |                                               |                                                                  | JEDI                     | EC comp          | liant     |        |

| Input Logic High                                         | V <sub>IH</sub>                               | $V_{LOGIC} = 2.7 \text{ V to } 5.5 \text{ V}$                    | 2.0                      | ·                |           | V      |

| Input Logic Low                                          | V <sub>IL</sub>                               | $V_{LOGIC} = 2.7 \text{ V to } 5.5 \text{ V}$                    |                          |                  | 0.8       | V      |

| Input Current                                            | I <sub>IL</sub>                               | $V_{IN} = 0 V \text{ or } V_{LOGIC}$                             |                          |                  | ±1        | μΑ     |

| Input Capacitance <sup>4</sup>                           | C <sub>IL</sub>                               |                                                                  |                          | 5                |           | pF     |

| DIGITAL OUTPUTS (SDO and RDY)                            |                                               |                                                                  |                          |                  |           |        |

| Output High Voltage                                      | V <sub>OH</sub>                               | $R_{PULL\_UP} = 2.2 \text{ k}\Omega \text{ to } V_{LOGIC}$       | V <sub>LOGIC</sub> - 0.4 |                  |           | V      |

| Output Low Voltage                                       | V <sub>OL</sub>                               | $R_{PULL\_UP} = 2.2 \text{ k}\Omega \text{ to } V_{LOGIC}$       |                          |                  | GND + 0.4 | V      |

| Tristate Leakage Current                                 |                                               |                                                                  | -1                       |                  | +1        | μΑ     |

| Output Capacitance <sup>4</sup>                          | C <sub>OL</sub>                               |                                                                  |                          | 5                |           | pF     |

| POWER SUPPLIES                                           |                                               |                                                                  |                          |                  |           | -      |

| Single-Supply Power Range                                | $V_{DD}$                                      | $V_{SS} = 0 V$                                                   | 9                        |                  | 33        | V      |

| Dual-Supply Power Range                                  | V <sub>DD</sub> /V <sub>SS</sub>              |                                                                  | ±9                       |                  | ±16.5     | V      |

| Positive Supply Current IDD                              |                                               | $V_{DD}/V_{SS} = \pm 16.5 \text{ V}$                             |                          | 0.1              | 2         | μΑ     |

| Negative Supply Current Iss                              |                                               | $V_{DD}/V_{SS} = \pm 16.5 \text{ V}$                             | -2                       | -0.1             |           | μA     |

| Logic Supply Range                                       | V <sub>LOGIC</sub>                            |                                                                  | 2.7                      |                  | 5.5       | V      |

| Logic Supply Current                                     | I <sub>LOGIC</sub>                            | $V_{LOGIC} = 5 \text{ V}; V_{IH} = 5 \text{ V or } V_{IL} = GND$ |                          | 1                | 10        | μΑ     |

| Power Dissipation <sup>7</sup>                           | P <sub>DISS</sub>                             | $V_{IH} = 5 \text{ V or } V_{IL} = \text{GND}$                   |                          | 8                | 110       | μW     |

| Power Supply Rejection Ratio <sup>4</sup>                | PSSR                                          | $\Delta V_{DD}/\Delta V_{SS} = \pm 15 \text{ V} \pm 10\%$        |                          |                  |           |        |

|                                                          |                                               | $R_{AB} = 50 \text{ k}\Omega$                                    |                          | 0.039            |           | %/%    |

|                                                          |                                               | $R_{AB} = 100 \text{ k}\Omega$                                   |                          | 0.021            |           | %/%    |

| Parameter                               | Symbol            | Conditions                                                                                            | Min Typ¹ Max | Unit   |

|-----------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------|--------------|--------|

| DYNAMIC CHARACTERISTICS <sup>4, 8</sup> |                   |                                                                                                       |              |        |

| Bandwidth                               | BW                | -3 dB                                                                                                 |              | kHz    |

|                                         |                   | $R_{AB} = 50 \text{ k}\Omega$                                                                         | 210          |        |

|                                         |                   | $R_{AB} = 100 \text{ k}\Omega$                                                                        | 105          |        |

| <b>Total Harmonic Distortion</b>        | THDw              | $V_A = 1 \text{ V rms}, V_B = 0 \text{ V}, f = 1 \text{ kHz}$                                         |              |        |

|                                         |                   | $R_{AB} = 50 \text{ k}\Omega$                                                                         | -101         | dB     |

|                                         |                   | $R_{AB} = 100 \text{ k}\Omega$                                                                        | -106         | dB     |

| V <sub>w</sub> Settling Time            | ts                | $V_A = 30 \text{ V}, V_B = 0 \text{ V}, \pm 0.5 \text{ LSB error}$<br>band, initial code = zero scale |              |        |

|                                         |                   | Code = full scale, R-normal mode                                                                      | 750          | ns     |

|                                         |                   | Code = full scale, R-perf mode                                                                        | 2.5          | μs     |

|                                         |                   | Code = half scale, R-normal mode, $R_{AB} = 50 \text{ k}\Omega$                                       | 7            | μs     |

|                                         |                   | Code = half scale, R-normal mode,<br>$R_{AB} = 100 \text{ k}\Omega$                                   | 14           | μs     |

|                                         |                   | Code = half scale, R-perf mode,<br>$R_{AB} = 50 \text{ k}\Omega$                                      | 9            | μs     |

|                                         |                   | Code = half scale, R-perf mode,<br>$R_{AB} = 100 \text{ k}\Omega$                                     | 16           | μs     |

| Resistor Noise Density                  | e <sub>N_wB</sub> | Code = half scale, $T_A$ = 25°C, 0 kHz to 200 kHz,                                                    |              |        |

|                                         |                   | $R_{AB} = 50 \text{ k}\Omega$                                                                         | 18           | nV/√Hz |

|                                         |                   | $R_{AB} = 100 \text{ k}\Omega$                                                                        | 27           | nV/√Hz |

$<sup>^1</sup>$  Typicals represent average readings at 25°C;  $V_{DD} = +15$  V,  $V_{SS} = -15$  V, and  $V_{LOGIC} = 5$  V.

#### RESISTOR PERFORMANCE MODE CODE RANGE—50 k $\Omega$ AND 100 k $\Omega$ VERSIONS

Table 4.

|                    | R <sub>AB</sub> = 50 kΩ |                 |                                                     |                 | R <sub>AB</sub> = 100 kΩ                            |                 |                                                     |                 |

|--------------------|-------------------------|-----------------|-----------------------------------------------------|-----------------|-----------------------------------------------------|-----------------|-----------------------------------------------------|-----------------|

| Resistor Tolerance | $ V_{DD} - V_{SS}  =$   | 26 V to 33 V    | $ V_{DD} - V_{SS}  = 21 \text{ V to } 26 \text{ V}$ |                 | $ V_{DD} - V_{SS}  = 26 \text{ V to } 33 \text{ V}$ |                 | $ V_{DD} - V_{SS}  = 21 \text{ V to } 26 \text{ V}$ |                 |

| per Code           | R <sub>WB</sub>         | R <sub>WA</sub> | R <sub>WB</sub>                                     | R <sub>WA</sub> | R <sub>WB</sub>                                     | R <sub>WA</sub> | R <sub>WB</sub>                                     | R <sub>WA</sub> |

| 1% R-Tolerance     | From 0x08C              | From 0x000      | From 0x0B4                                          | From 0x000      | From 0x04B                                          | From 0x000      | From 0x064                                          | From 0x000      |

|                    | to 0x3FF                | to 0x35F        | to 0x3FF                                            | to 0x31E        | to 0x3FF                                            | to 0x3B4        | to 0x3FF                                            | to 0x39B        |

| 2% R-Tolerance     | From 0X03C              | From 0x000      | From 0x050                                          | From 0x000      | From 0x028                                          | From 0x000      | From 0x028                                          | From 0x000      |

|                    | to 0x3FF                | to 0x3C3        | to 0x3FF                                            | to 0x3AF        | to 0x3FF                                            | to 0x3D7        | to 0x3FF                                            | to 0x3D7        |

| 3% R-Tolerance     | From 0X028              | From 0x000      | From 0x032                                          | From 0x000      | From 0x019                                          | From 0x000      | From 0x019                                          | From 0x000      |

|                    | to 0x3FF                | to 0x3D7        | to 0x3FF                                            | to 0x3CD        | to 0x3FF                                            | to 0x3E6        | to 0x3FF                                            | to 0x3E6        |

<sup>&</sup>lt;sup>2</sup> Resistor position nonlinearity error. R-INL is the deviation from an ideal value measured between  $R_{WB}$  at Code 0x00B to Code 0x3FF or between  $R_{WA}$  at Code 0x0FF or between R<sub>WB</sub> at Code 0x0FF or between Successive tap positions. The specification is guaranteed in resistor performance mode with a wiper current of 1 mA for  $V_A < 12 \text{ V}$  and 1.2 mA for  $V_A \ge 12 \text{ V}$ .

<sup>&</sup>lt;sup>3</sup> The terms resistor performance mode and R-perf mode are used interchangeably.

<sup>&</sup>lt;sup>4</sup> Guaranteed by design; not subject to production test.

<sup>&</sup>lt;sup>5</sup> INL and DNL are measured at  $V_W$  with the RDAC configured as a potentiometer divider similar to a voltage output DAC.  $V_A = V_{DD}$  and  $V_B = 0$  V. DNL specification limits of  $\pm 1$  LSB maximum are guaranteed monotonic operating conditions.

<sup>&</sup>lt;sup>6</sup> The A, B, and W resistor terminals have no limitations on polarity with respect to each other. Dual-supply operation enables ground-referenced bipolar signal adjustment.

<sup>&</sup>lt;sup>7</sup> P<sub>DISS</sub> is calculated from  $(I_{DD} \times V_{DD}) + (I_{SS} \times V_{SS}) + (I_{LOGIC} \times V_{LOGIC})$ .

$<sup>^8</sup>$  All dynamic characteristics use  $V_{DD} = +15 \ V, \, V_{SS} = -15 \ V, \, and \, V_{LOGIC} = 5 \ V.$

#### INTERFACE TIMING SPECIFICATIONS

$V_{DD} = V_{SS} = \pm 15 \text{ V}, V_{LOGIC} = 2.7 \text{ V to } 5.5 \text{ V}, and -40 ^{\circ}\text{C} < T_{A} < +105 ^{\circ}\text{C}. \text{ All specifications } T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$

Table 5.

| Parameter                    | Limit <sup>1</sup> | Unit   | Test Conditions/Comments                                                           |

|------------------------------|--------------------|--------|------------------------------------------------------------------------------------|

| t <sub>1</sub> <sup>2</sup>  | 20                 | ns min | SCLK cycle time                                                                    |

| $t_2$                        | 10                 | ns min | SCLK high time                                                                     |

| t <sub>3</sub>               | 10                 | ns min | SCLK low time                                                                      |

| t <sub>4</sub>               | 10                 | ns min | SYNC to SCLK falling edge setup time                                               |

| <b>t</b> <sub>5</sub>        | 5                  | ns min | Data setup time                                                                    |

| t <sub>6</sub>               | 5                  | ns min | Data hold time                                                                     |

| t <sub>7</sub>               | 1                  | ns min | SCLK falling edge to SYNC rising edge                                              |

| t <sub>8</sub>               | 400³               | ns min | Minimum SYNC high time                                                             |

| t <sub>9</sub>               | 14                 | ns min | SYNC rising edge to next SCLK fall ignored                                         |

| t <sub>10</sub> <sup>4</sup> | 1                  | ns min | RDY rise to SYNC falling edge                                                      |

| t <sub>11</sub> <sup>4</sup> | 40                 | ns max | SYNC rise to RDY fall time                                                         |

| $t_{12}^{4}$                 | 2.4                | μs max | RDY low time, RDAC register write command execute time (resistor performance mode) |

| $t_{12}^{4}$                 | 410                | ns max | RDY low time, RDAC register write command execute time (normal mode)               |

| $t_{12}^{4}$                 | 1.5                | ms max | Software\hardware reset                                                            |

| $t_{13}^{4}$                 | 450                | ns max | RDY low time, RDAC register read command execute time                              |

| t <sub>14</sub> <sup>4</sup> | 450                | ns max | SCLK rising edge to SDO valid                                                      |

| treset                       | 20                 | ns min | Minimum RESET pulse width (asynchronous)                                           |

| t <sub>POWER-UP</sub> 5      | 2                  | ms max | Power-on time to half scale                                                        |

$<sup>^1</sup>$  All input signals are specified with  $t_R = t_F = 1$  ns/V (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ .

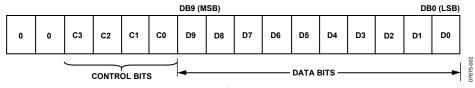

Figure 2. Shift Register Contents

<sup>&</sup>lt;sup>2</sup> Maximum SCLK frequency = 50 MHz. <sup>3</sup> Refer to t<sub>12</sub> and t<sub>13</sub> for RDAC register commands operations.

<sup>&</sup>lt;sup>4</sup> R<sub>PULL\_UP</sub> = 2.2 kΩ to V<sub>LOGIC</sub> with a capacitance load of 168 pF. <sup>5</sup> Typical power supply voltage slew-rate of 2 V/ms.

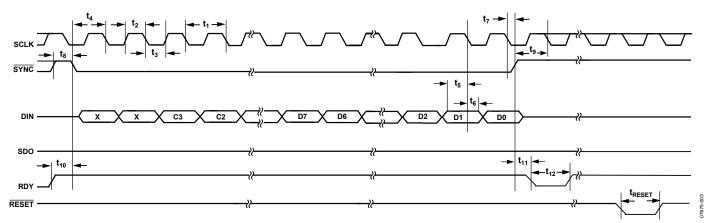

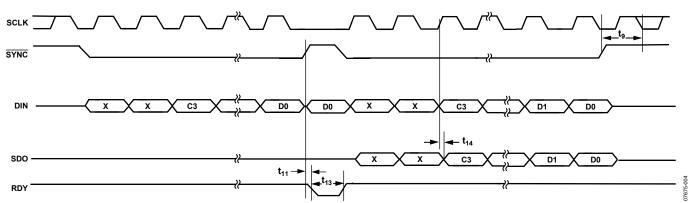

#### **TIMING DIAGRAMS**

Figure 3. Write Timing Diagram, CPOL = 0, CPHA = 1

Figure 4. Read Timing Diagram, CPOL = 0, CPHA =1

#### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 6.

| Tuble of                                              |                                                      |  |  |

|-------------------------------------------------------|------------------------------------------------------|--|--|

| Parameter                                             | Rating                                               |  |  |

| V <sub>DD</sub> to GND                                | −0.3 V to +35 V                                      |  |  |

| V <sub>SS</sub> to GND                                | +0.3 V to −25 V                                      |  |  |

| V <sub>LOGIC</sub> to GND                             | −0.3 V to +7 V                                       |  |  |

| $V_{DD}$ to $V_{SS}$                                  | 35 V                                                 |  |  |

| $V_A$ , $V_B$ , $V_W$ to GND                          | $V_{SS} - 0.3  V, V_{DD} + 0.3  V$                   |  |  |

| Digital Input and Output Voltage to GND               | $-0.3 \text{ V to V}_{\text{LOGIC}} + 0.3 \text{ V}$ |  |  |

| EXT_CAP Voltage to GND                                | −0.3 V to +7 V                                       |  |  |

| I <sub>A</sub> , I <sub>B</sub> , I <sub>W</sub>      |                                                      |  |  |

| Continuous                                            |                                                      |  |  |

| $R_{AB} = 20 \text{ k}\Omega$                         | ±3 mA                                                |  |  |

| $R_{AB} = 50 \text{ k}\Omega$ , $100 \text{ k}\Omega$ | ±2 mA                                                |  |  |

| Pulsed <sup>1</sup>                                   |                                                      |  |  |

| Frequency > 10 kHz                                    | $MCC^2/d^3$                                          |  |  |

| Frequency ≤ 10 kHz                                    | $MCC^2/\sqrt{d^3}$                                   |  |  |

| Operating Temperature Range                           | −40°C to +105°C                                      |  |  |

| Maximum Junction Temperature (T <sub>J</sub> max)     | 150°C                                                |  |  |

| Storage Temperature Range                             | −65°C to +150°C                                      |  |  |

| Reflow Soldering                                      |                                                      |  |  |

| Peak Temperature                                      | 260°C                                                |  |  |

| Time at Peak Temperature                              | 20 sec to 40 sec                                     |  |  |

| Package Power Dissipation                             | $(T_J max - T_A)/\theta_{JA}$                        |  |  |

| ·                                                     |                                                      |  |  |

<sup>&</sup>lt;sup>1</sup> Maximum terminal current is bounded by the maximum current handling of the switches, maximum power dissipation of the package, and maximum applied voltage across any two of the A, B, and W terminals at a given resistance.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

**Table 7. Thermal Resistance**

| Package Type  | θιΑ             | θις | Unit |

|---------------|-----------------|-----|------|

| 14-Lead TSSOP | 93 <sup>1</sup> | 20  | °C/W |

<sup>&</sup>lt;sup>1</sup> JEDEC 2S2P test board, still air (from 0 m/sec to 1 m/sec of air flow).

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> Maximum continuous current.

<sup>&</sup>lt;sup>3</sup> Pulse duty factor.

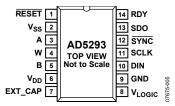

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 5. Pin Configuration

#### **Table 8. Pin Function Descriptions**

| Pin No. | Mnemonic    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | RESET       | Hardware Reset Pin. Sets the RDAC register to midscale. RESET is activated at the logic high transition. Tie RESET to                                                                                                                                                                                                                                                                                                                                                                             |

|         |             | V <sub>LOGIC</sub> if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2       | Vss         | Negative Supply. Connect to 0 V for single-supply applications. This pin should be decoupled with 0.1 $\mu$ F ceramic capacitors and 10 $\mu$ F capacitors.                                                                                                                                                                                                                                                                                                                                       |

| 3       | Α           | Terminal A of RDAC. $V_{SS} \le V_A \le V_{DD}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4       | W           | Wiper Terminal W of RDAC. $V_{SS} \le V_W \le V_{DD}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5       | В           | Terminal B of RDAC. $V_{SS} \le V_B \le V_{DD}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6       | $V_{DD}$    | Positive Power Supply. This pin should be decoupled with 0.1 μF ceramic capacitors and 10 μF capacitors.                                                                                                                                                                                                                                                                                                                                                                                          |

| 7       | EXT_CAP     | Connect a 1 µF capacitor to EXT_CAP. This capacitor must have a voltage rating of ≥7 V.                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8       | $V_{LOGIC}$ | Logic Power Supply, 2.7 V to 5.5 V. This pin should be decoupled with 0.1 μF ceramic capacitors and 10 μF capacitors.                                                                                                                                                                                                                                                                                                                                                                             |

| 9       | GND         | Ground Pin, Logic Ground Reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 10      | DIN         | Serial Data Input. This part has a 16-bit shift register. Data is clocked into the register on the falling edge of the serial clock input.                                                                                                                                                                                                                                                                                                                                                        |

| 11      | SCLK        | Serial Clock Input. Data is clocked into the shift register on the falling edge of the serial clock input. Data can be transferred at rates up to 50 MHz.                                                                                                                                                                                                                                                                                                                                         |

| 12      | SYNC        | Falling Edge Synchronization Signal. This is the frame synchronization signal for the input data. When SYNC goes low, it enables the shift register, and data is transferred in on the falling edges of the following clocks. The selected register is updated on the rising edge of SYNC, following the 16 <sup>th</sup> clock cycle. If SYNC is taken high before the 16 <sup>th</sup> clock cycle, the rising edge of SYNC acts as an interrupt, and the write sequence is ignored by the DAC. |

| 13      | SDO         | Serial Data Output. This open-drain output requires an external pull-up resistor. SDO can be used to clock data from the serial register in daisy-chain mode or in readback mode.                                                                                                                                                                                                                                                                                                                 |

| 14      | RDY         | Ready Pin. This active-high, open-drain output identifies the completion of a write or read operation to or from the RDAC register.                                                                                                                                                                                                                                                                                                                                                               |

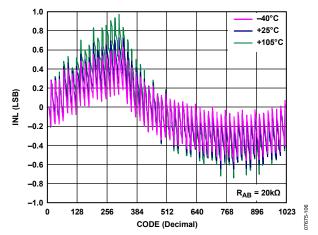

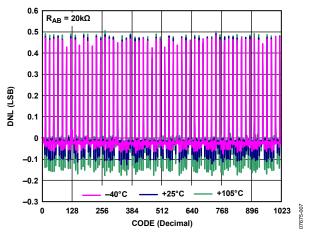

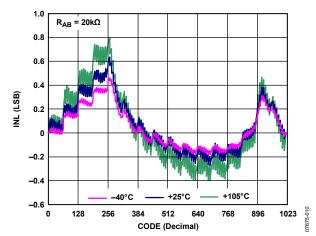

### TYPICAL PERFORMANCE CHARACTERISTICS

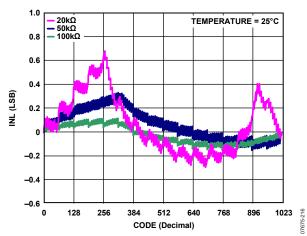

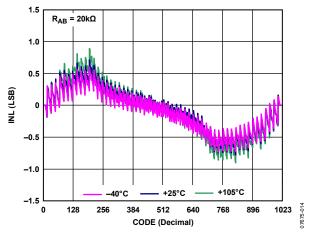

Figure 6. R-INL in R-Perf Mode vs. Code vs. Temperature

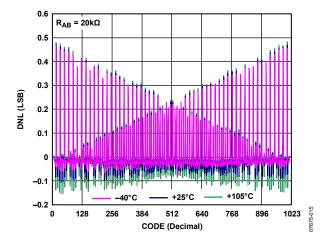

Figure 7. R-DNL in R-Perf Mode vs. Code vs. Temperature

Figure 8. R-INL in Normal Mode vs. Code vs. Temperature

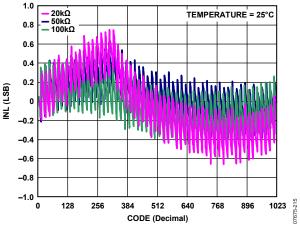

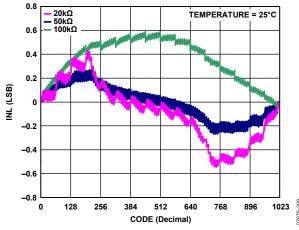

Figure 9. R-INL in R-Perf Mode vs. Code vs. Nominal Resistance

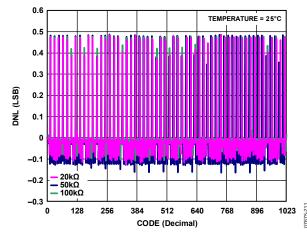

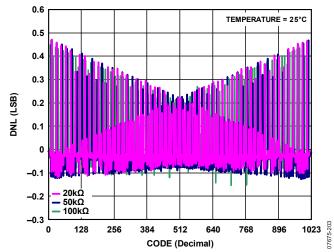

Figure 10. R-DNL in R-Perf Mode vs. Code vs. Nominal Resistance

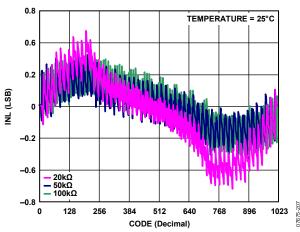

Figure 11. R-INL in Normal Mode vs. Code vs. Nominal Resistance

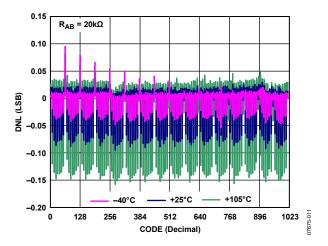

Figure 12. R-DNL in Normal Mode vs. Code vs. Temperature

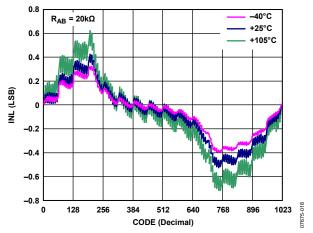

Figure 13. INL in R-Perf Mode vs. Code vs. Temperature

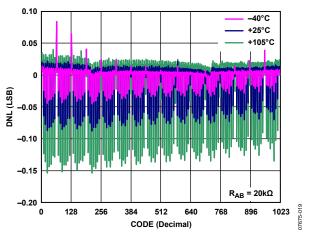

Figure 14. DNL in R-Perf Mode vs. Code vs. Temperature

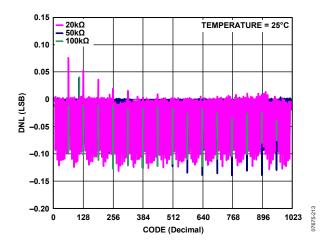

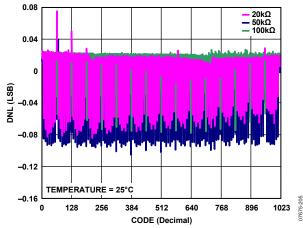

Figure 15. R-DNL in Normal Mode vs. Code vs. Nominal Resistance

Figure 16. INL in R-Perf Mode vs. Code vs. Nominal Resistance

Figure 17. DNL in R-Perf Mode vs. Code vs. Nominal Resistance

Figure 18. INL in Normal Mode vs. Code vs. Temperature

Figure 19. DNL in Normal Mode vs. Code vs. Temperature

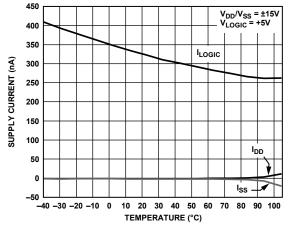

Figure 20. Supply Current vs. Temperature

Figure 21. DNL in Normal Mode vs. Code vs. Temperature

Figure 22. DNL in Normal Mode vs. Code vs. Temperature

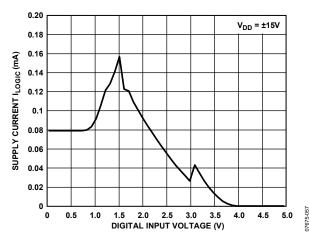

Figure 23. Supply Current, ILOGIC, vs. Digital Input Voltage.

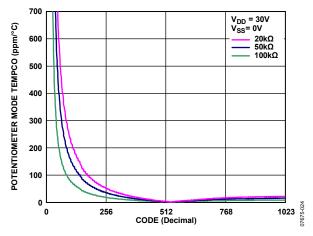

Figure 24. Rheostat Mode Tempco ΔR<sub>WB</sub>/ΔT vs. Code

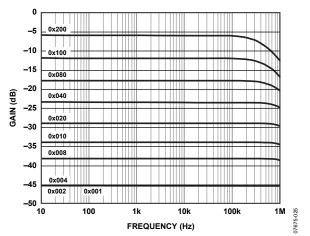

Figure 25. 20 k $\Omega$  Gain vs. Frequency vs. Code

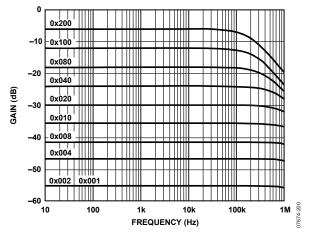

Figure 26. 50 k $\Omega$  Gain vs. Frequency vs. Code

Figure 27. Potentiometer Mode Tempco ΔR<sub>WB</sub>/ΔT vs. Code

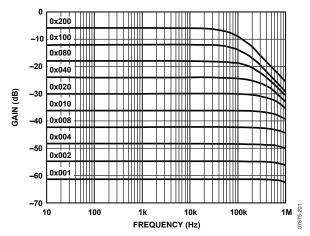

Figure 28. 100 k $\Omega$  Gain vs. Frequency vs. Code

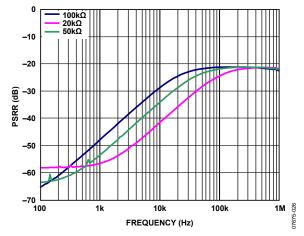

Figure 29. Power Supply Rejection Ratio (PSRR) vs. Frequency

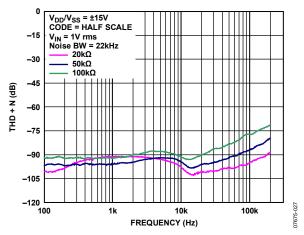

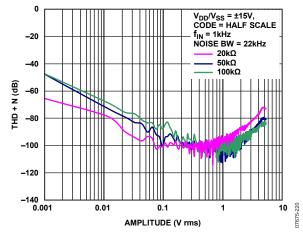

Figure 30. Total Harmonic Distortion + Noise (THD + N) vs. Frequency

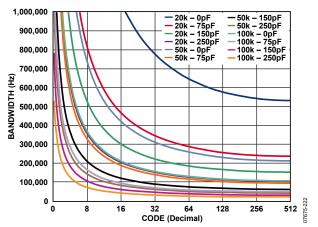

Figure 31. Maximum Bandwidth vs. Code vs. Net Capacitance

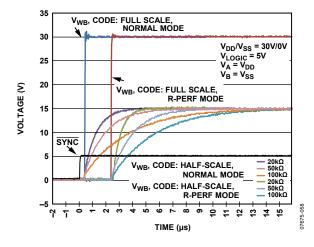

Figure 32. Large Signal Settling Time, Code from Zero Scale to Full Scale

Figure 33. Total Harmonic Distortion + Noise (THD + N) vs. Amplitud

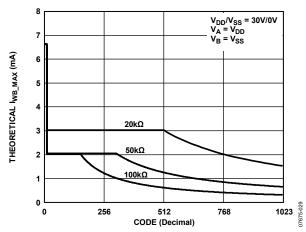

Figure 34. Theoretical Maximum Current vs. Code

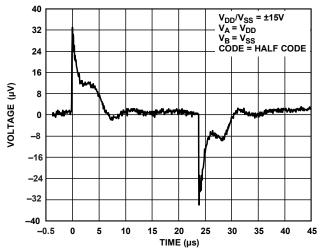

Figure 35. Digital Feedthrough

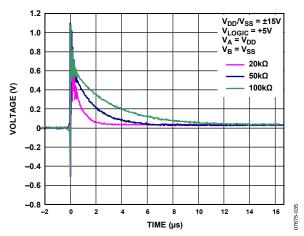

Figure 36. Maximum Transition Glitch

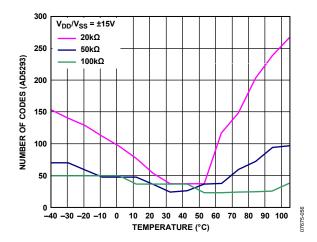

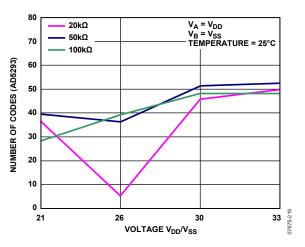

Figure 37. Code Range > 1% R-Tolerance Error vs. Temperature

Figure 38. Code Range > 1% R-Tolerance Error vs. Voltage

### **TEST CIRCUITS**

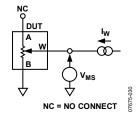

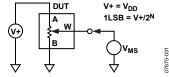

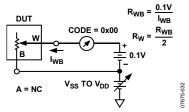

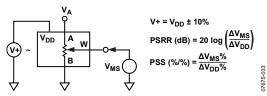

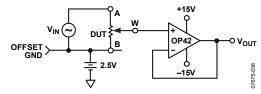

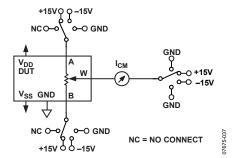

Figure 39 to Figure 44 define the test conditions used in the Specifications section.

Figure 39. Resistor Position Nonlinearity Error (Rheostat Operation: R-INL, R-DNL)

Figure 40. Potentiometer Divider Nonlinearity Error (INL, DNL)

Figure 41. Wiper Resistance

Figure 42. Power Supply Sensitivity (PSS, PSRR)

Figure 43. Gain vs. Frequency

Figure 44. Common-Mode Leakage Current

#### THEORY OF OPERATION

The AD5293 digital potentiometer is designed to operate as a true variable resistor for analog signals that remain within the terminal voltage range of  $V_{\text{SS}} < V_{\text{TERM}} < V_{\text{DD}}$ . The patented  $\pm 1\%$  resistor tolerance feature helps to minimize the total RDAC resistance error, which reduces the overall system error by offering better absolute matching and improved open-loop performance. The digital potentiometer wiper position is determined by the RDAC register contents. The RDAC register acts as a scratchpad register, allowing as many value changes as necessary to place the potentiometer wiper in the correct position. The RDAC register can be programmed with any position setting via the standard serial peripheral interface (SPI) by loading the 16-bit data-word.

#### **SERIAL DATA INTERFACE**

The AD5293 contains a serial interface (SYNC, SCLK, DIN, and SDO) that is compatible with SPI standards, as well as most DSPs. The device allows data to be written to every register via the SPI.

#### **SHIFT REGISTER**

The AD5293 shift register is 16 bits wide (see Figure 2). The 16-bit data-word consists of two unused bits, which are set to 0, followed by four control bits and 10 RDAC data bits. Data is loaded MSB first (Bit 15). The four control bits determine the function of the software command (see Table 11). Figure 3 shows a timing diagram of a typical write sequence.

The write sequence begins by bringing the \$\overline{SYNC}\$ line low. The \$\overline{SYNC}\$ pin must be held low until the complete data-word is loaded from the DIN pin. When \$\overline{SYNC}\$ returns high, the serial data-word is decoded according to the instructions in Table 11. The command bits (Cx) control the operation of the digital potentiometer. The data bits (Dx) are the values that are loaded into the decoded register. The AD5293 has an internal counter that counts a multiple of 16 bits (per frame) for proper operation. For example, the AD5293 works with a 32-bit word, but it cannot work properly with a 31- or 33-bit word. The AD5293 does not require a continuous SCLK, when \$\overline{SYNC}\$ is high, and all interface pins should be operated close to the supply rails to minimize power consumption in the digital input buffers.

#### **RDAC REGISTER**

The RDAC register directly controls the position of the digital potentiometer wiper. For example, when the RDAC register is loaded with all zeros, the wiper is connected to Terminal B of the variable resistor. The RDAC register is a standard logic register; there is no restriction on the number of changes allowed. The RDY pin can be used to monitor the completion of a write to or read from the RDAC register. The AD5293 presets to midscale on power-up.

#### WRITE PROTECTION

On power-up, the serial data input register write command for the RDAC register is disabled. The RDAC write protect bit, C1 of the control register (see Table 12 and Table 13), is set to 0 by default. This disables any change of the RDAC register content, regardless of the software commands, except that the RDAC register can be refreshed to midscale using the software reset command (Command 3, see Table 11) or through hardware, using the RESET pin. To enable programming of the variable resistor wiper position (programming the RDAC register), the write protect bit, C1 of the control register, must first be programmed. This is accomplished by loading the serial data input register with Command 4 (see Table 11).

#### **BASIC OPERATION**

The basic mode of setting the variable resistor wiper position (programming the RDAC register) is accomplished by loading the serial data input register with Command 1 (see Table 11) and the desired wiper position data. The RDY pin can be used to monitor the completion of this RDAC register write command. Command 2 can be used to read back the contents of the RDAC register (see Table 11). After issuing the readback command, the RDY pin can be monitored to indicate when the data is available to be read out on SDO in the next SPI operation. Instead of monitoring the RDY pin, a minimum delay can be implemented when executing a write or read command (see Table 5). Table 9 provides an example listing of a sequence of serial data input (DIN) words with the serial data output appearing at the SDO pin in hexadecimal format for an RDAC write and read.

Table 9. RDAC Register Write and Read

| DIN  |     | SDO                 | Action                                                                                                                |

|------|-----|---------------------|-----------------------------------------------------------------------------------------------------------------------|

| 0x18 | 302 | 0xXXXX <sup>1</sup> | Enable update of wiper position.                                                                                      |

| 0x0  | 500 | 0x1802              | Write 0x100 to the RDAC register. Wiper moves to ¼ full-scale position.                                               |

| 0x0  | 300 | 0x0500              | Prepare data read from RDAC register.                                                                                 |

| 0x0  | 000 | 0x0100              | NOP (Instruction 0) sends a 16-bit word out of SDO, where the last 10 bits contain the contents of the RDAC register. |

<sup>&</sup>lt;sup>1</sup> X = unknown.

#### SHUTDOWN MODE

The AD5293 can be placed in shutdown mode by executing the software shutdown command (see Command 6 in Table 11), and setting the LSB to 1. This feature places the RDAC in a special state in which Terminal A is open-circuited and Wiper W is connected to Terminal B. The contents of the RDAC register are unchanged by entering shutdown mode. However, all commands listed in Table 11 are supported while in shutdown mode.

#### **RESET**

A low-to-high transition of the hardware RESET pin loads the RDAC register with midscale. The AD5293 can also be reset through software by executing Command 3 (see Table 11). The control register is restored with default bits (see Table 13).

#### RESISTOR PERFORMANCE MODE

This mode activates a new, patented 1% end-to-end resistor tolerance that ensures a  $\pm 1\%$  resistor tolerance on each code, that is, code = half scale,  $R_{WB}$  =10 k $\Omega$   $\pm$  100  $\Omega$ . See Table 2 and Table 4 to verify which codes achieve  $\pm 1\%$  resistor tolerance. The resistor performance mode is activated by programming Bit C2 of the control register (see Table 12 and Table 13). The typical settling time is shown in Figure 32.

#### **SDO PIN AND DAISY-CHAIN OPERATION**

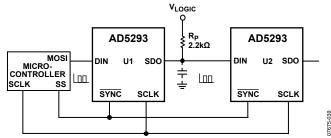

The serial data output pin (SDO) serves two purposes: it can be used to read the contents of the wiper setting and control register using Command 2, and Command 5, respectively (see Table 11) or the SDO pin can be used in daisy-chain mode. Data is clocked out of SDO on the rising edge of SCLK. The SDO pin contains an open-drain N-channel FET that requires a pull-up resistor if this pin is used. To place the pin in high impedance and minimize the power dissipation when the pin is used, the 0x8001 data word followed by Command 0 should be sent to the part. Table 10 provides a sample listing for the

sequence of the serial data input (DIN). Daisy chaining minimizes the number of port pins required from the controlling IC. As shown in Figure 45, users need to tie the SDO pin of one package to the DIN pin of the next package. Users may need to increase the clock period, because the pull-up resistor and the capacitive loading at the SDO-to-DIN interface may require additional time delay between subsequent devices.

When two AD5293s are daisy-chained, 32 bits of data are required. The first 16 bits go to U2, and the second 16 bits go to U1. The  $\overline{\text{SYNC}}$  pin should be held low until all 32 bits are clocked into their respective serial registers. The  $\overline{\text{SYNC}}$  pin is then pulled high to complete the operation.

Keep the  $\overline{\text{SYNC}}$  pin low until all 32 bits are clocked into their respective serial registers. The  $\overline{\text{SYNC}}$  pin is then pulled high to complete the operation.

Figure 45. Daisy-Chain Configuration Using SDO

Table 10. Minimize Power Dissipation at the SDO Pin

| DIN    | SDO <sup>1</sup> | Action                                                   |

|--------|------------------|----------------------------------------------------------|

| 0xXXXX | 0xXXXX           | Last user command sent to the digipot                    |

| 0x8001 | 0xXXXX           | Prepares the SDO pin to be placed in high impedance mode |

| 0x0000 | High impedance   | The SDO pin is placed in high impedance                  |

$<sup>^{1}</sup>$  X = don't care.

**Table 11. Command Operation Truth Table**

|         | Command Bits[B13:B10] |    |    |    |    | Data Bits[B9:B0] <sup>1</sup> |    |    |    |    |    |    |    |    |                                                                                       |

|---------|-----------------------|----|----|----|----|-------------------------------|----|----|----|----|----|----|----|----|---------------------------------------------------------------------------------------|

| Command | C3                    | C2 | C1 | CO | D9 | D8                            | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Operation                                                                             |

| 0       | 0                     | 0  | 0  | 0  | Χ  | Х                             | Χ  | Χ  | Х  | Χ  | Х  | Χ  | Χ  | Х  | NOP command. Do nothing.                                                              |

| 1       | 0                     | 0  | 0  | 1  | D9 | D8                            | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Write contents of serial register data to RDAC.                                       |

| 2       | 0                     | 0  | 1  | 0  | Х  | Х                             | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Read RDAC wiper setting from SDO output in the next frame.                            |

| 3       | 0                     | 1  | 0  | 0  | Χ  | Χ                             | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Reset. Refresh RDAC with midscale code.                                               |

| 4       | 0                     | 1  | 1  | 0  | Х  | Х                             | Х  | Х  | Х  | Х  | Х  | D2 | D1 | Х  | Write contents of serial register data to control register.                           |

| 5       | 0                     | 1  | 1  | 1  | Х  | Х                             | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Read control register from SDO output in the next frame.                              |

| 6       | 1                     | 0  | 0  | 0  | Х  | Х                             | Х  | Х  | Х  | Х  | Х  | Х  | Х  | D0 | Software power-down.  D0 = 0 (normal mode).  D0 = 1 (device placed in shutdown mode). |

<sup>&</sup>lt;sup>1</sup> X = don't care.

Table 12. Control Register Bit Map

| D9             | D8             | D7             | D6             | D5             | D4             | D3             | D2 | D1 | D0             |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----|----|----------------|

| X <sup>1</sup> | C2 | C1 | X <sup>1</sup> |

<sup>&</sup>lt;sup>1</sup> X = don't care.

**Table 13. Control Register Function**

| Register Name | Bit Name | Description                                                           |

|---------------|----------|-----------------------------------------------------------------------|

| Control       | C2       | Calibration enable.                                                   |

|               |          | 0 = resistor performance mode (default).                              |

|               |          | 1 = normal mode.                                                      |

|               | C1       | RDAC register write protect.                                          |

|               |          | 0 = locks the wiper position through the digital interface (default). |

|               |          | 1 = allows update of wiper position through digital interface.        |

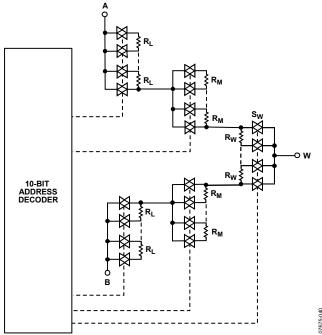

#### **RDAC ARCHITECTURE**

To achieve optimum performance, Analog Devices, Inc., has patented the RDAC segmentation architecture for all the digital potentiometers. In particular, the AD5293 employs a 3-stage segmentation approach, as shown in Figure 46. The AD5293 wiper switch is designed with transmission gate CMOS topology and with the gate voltage derived from  $V_{\rm DD}.\,$

Figure 46. Simplified RDAC Circuit

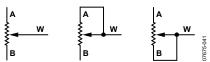

#### PROGRAMMING THE VARIABLE RESISTOR

#### Rheostat Operation—1% Resistor Tolerance

The AD5293 operates in rheostat mode when only two terminals are used as a variable resistor. The unused terminal can be left floating or it can be tied to the W terminal, as shown in Figure 47.

Figure 47. Rheostat Mode Configuration

The nominal resistance between Terminal A and Terminal B,  $R_{AB}$ , is available in  $20~k\Omega$ ,  $50~k\Omega$ , and  $100~k\Omega$  and has 1024 tap points that are accessed by the wiper terminal. The 10-bit data in the RDAC latch is decoded to select one of the 1024 possible wiper settings. The AD5293 contains an internal  $\pm 1\%$  resistor tolerance calibration feature that can be enabled or disabled, enabled by default by programming Bit C2 of the control register (see Table 12 and Table 13).

The digitally programmed output resistance between the W terminal and the A terminal,  $R_{\text{WA}}$ , and the W terminal and B terminal,  $R_{\text{WB}}$ , is calibrated to give a maximum of  $\pm 1\%$  absolute resistance error over both the full supply and temperature ranges. As a result, the general equation for determining the digitally programmed output resistance between the W terminal and B terminal is

$$R_{WB}(D) = \frac{D}{1024} \times R_{AB} \tag{1}$$

where:

D is the decimal equivalent of the binary code loaded in the 10-bit RDAC register.

$R_{AB}$  is the end-to-end resistance.

Similar to the mechanical potentiometer, the resistance of the RDAC between the W terminal and the A terminal also produces a digitally controlled complementary resistance,  $R_{WA}$ .  $R_{WA}$  is also calibrated to give a maximum of 1% absolute resistance error.  $R_{WA}$  starts at the maximum resistance value and decreases as the data loaded into the latch increases. The general equation for this operation is

$$R_{WA}(D) = \frac{1024 - D}{1024} \times R_{AB} \tag{2}$$

where:

*D* is the decimal equivalent of the binary code loaded in the 10-bit RDAC register.

$R_{AB}$  is the end-to-end resistance.

In the zero-scale condition, a finite total wiper resistance of 120  $\Omega$  is present. Regardless of the setting in which the part is operating, care should be taken to limit the current between the A terminal to B terminal, the W terminal to the A terminal, and the W terminal to the B terminal to the maximum continuous current of  $\pm 3$  mA or to the pulse current specified in Table 6. Otherwise, degradation, or possible destruction of the internal switch contact, can occur.

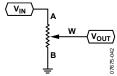

### PROGRAMMING THE POTENTIOMETER DIVIDER

#### **Voltage Output Operation**

The digital potentiometer easily generates a voltage divider at wiper-to-B terminal and wiper-to-A terminal that is proportional to the input voltage at A to B, as shown in Figure 48. Unlike the polarity of  $V_{\rm DD}$  to GND, which must be positive, voltage across A to B, W to A, and W to B can be at either polarity.

Figure 48. Potentiometer Mode Configuration

If ignoring the effect of the wiper resistance for simplicity, connecting the A terminal to 30 V and the B terminal to ground produces an output voltage at the Wiper W to Terminal B that ranges from 0 V to 30 V - 1 LSB. Each LSB of voltage is equal to the voltage applied across the A terminal and B terminal, divided by the 1024 positions of the potentiometer divider. The general equation defining the output voltage at  $V_{\rm W}$ , with respect to ground for any valid input voltage applied to Terminal A and Terminal B, is

$$V_W(D) = \frac{D}{1024} \times V_A + \frac{1024 - D}{1024} \times V_B$$

(3)

To optimize the wiper position update rate when in voltage divider mode, it is recommended that the internal  $\pm 1\%$  resistor tolerance calibration feature be disabled by programming Bit C2 of the control register (see Table 11).

Operation of the digital potentiometer in the divider mode results in a more accurate operation over temperature. Unlike rheostat mode, the output voltage is dependent mainly on the ratio of the internal resistors, R<sub>WA</sub> and R<sub>WB</sub>, and not on the absolute values. Therefore, the temperature drift reduces to 5 ppm/°C.

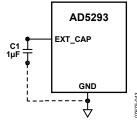

#### **EXT\_CAP CAPACITOR**

A 1  $\mu$ F capacitor to GND must be connected to the EXT\_CAP pin (see Figure 49) on power-up and throughout the operation of the AD5293. This capacitor must have a voltage rating of  $\geq$ 7 V.

Figure 49. Hardware Setup for the EXT\_CAP Pin

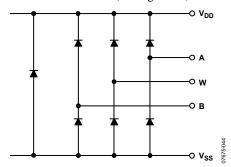

#### **TERMINAL VOLTAGE OPERATING RANGE**

The positive  $V_{DD}$  and negative  $V_{SS}$  power supplies of the AD5293 define the boundary conditions for proper 3-terminal, digital potentiometer operation. Supply signals present on the A, B, and W terminals that exceed  $V_{DD}$  or  $V_{SS}$  are clamped by the internal forward-biased diodes (see Figure 50).

Figure 50. Maximum Terminal Voltages Set by V<sub>DD</sub> and V<sub>SS</sub>

The ground pin of the AD5293 is primarily used as a digital ground reference. To minimize the digital ground bounce, the AD5293 ground pin should be joined remotely to common ground. The digital input control signals to the AD5293 must be referenced to the device ground pin (GND) to satisfy the logic level defined in the Specifications section.

#### Power-Up Sequence

Because there are diodes to limit the voltage compliance at the A, B, and W terminals (see Figure 50), it is important to power  $V_{\rm DD}$  and  $V_{\rm SS}$  first, before applying any voltage to the A, B, and W terminals. Otherwise, the diode is forward-biased such that  $V_{\rm DD}$  and  $V_{\rm SS}$  are powered up unintentionally. The ideal power-up sequence is GND,  $V_{\rm SS}$ ,  $V_{\rm LOGIC}$ ,  $V_{\rm DD}$ , the digital inputs, and then  $V_{\rm A}$ ,  $V_{\rm B}$ , and  $V_{\rm W}$ . The order of powering up  $V_{\rm A}$ ,  $V_{\rm B}$ ,  $V_{\rm W}$ , and the digital inputs is not important, as long as they are powered after  $V_{\rm DD}$ ,  $V_{\rm SS}$ , and  $V_{\rm LOGIC}$ .

Regardless of the power-up sequence and the ramp rates of the power supplies, the power-on preset activates after  $V_{\text{LOGIC}}$  is powered, restoring midscale to the RDAC register.

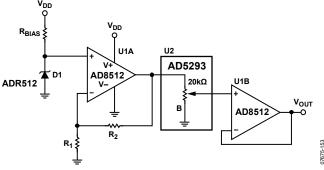

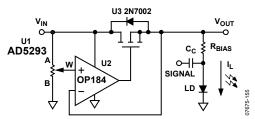

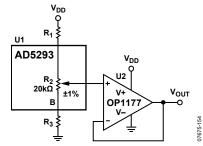

## APPLICATIONS INFORMATION HIGH VOLTAGE DAC

The AD5293 can be configured as a high voltage DAC, with an output voltage as high as 33 V. The circuit is shown in Figure 51. The output is