# 8-/10-/12-Bit High Bandwidth **Multiplying DACs with Serial Interface**

**Data Sheet**

# AD5426/AD5432/AD5443

### **FEATURES**

2.5 V to 5.5 V supply operation 50 MHz serial interface 10 MHz multiplying bandwidth 2.5 MSPS update rate INL of ±1 LSB for 12-bit DAC ±10 V reference input Low glitch energy < 2 nV-s Extended temperature range -40°C to +125°C **10-lead MSOP package** Pin-compatible 8-, 10-, and 12-bit current output DACs **Guaranteed monotonic** 4-quadrant multiplication Power-on reset with brownout detection **Daisy-chain mode Readback function** 0.4 µA typical power consumption

### **APPLICATIONS**

Portable battery-powered applications Waveform generators **Analog processing** Instrumentation **Programmable amplifiers and attenuators Digitally controlled calibration Programmable filters and oscillators Composite video** Ultrasound Gain, offset, and voltage trimming

### **GENERAL DESCRIPTION**

The AD5426/AD5432/AD54431 are CMOS 8-, 10-, and 12-bit current output digital-to-analog converters (DACs), respectively. These devices operate from a 2.5 V to 5.5 V power supply, making them suitable for battery-powered applications and many other applications.

These DACs use a double buffered, 3-wire serial interface that is compatible with SPI, QSPI<sup>™</sup>, MICROWIRE<sup>™</sup>, and most DSP interface standards. In addition, a serial data out pin (SDO) allows for daisy-chaining when multiple packages are used. Data readback allows the user to read the contents of the DAC register via the SDO pin. On power-up, the internal shift register and latches are filled with 0s and the DAC outputs are at zero scale.

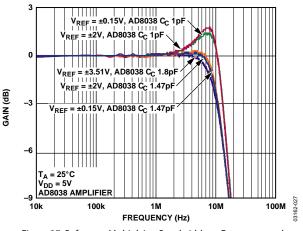

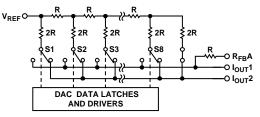

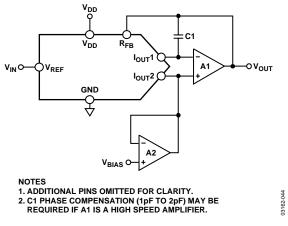

As a result of manufacturing on a CMOS submicron process, the parts offer excellent 4-quadrant multiplication characteristics with large signal multiplying bandwidths of 10 MHz. The applied external reference input voltage,  $V_{\text{REF}}$ , determines the full-scale output current. An integrated feedback resistor, R<sub>FB</sub>, provides temperature tracking and full-scale voltage output when combined with an external current to voltage precision amplifier.

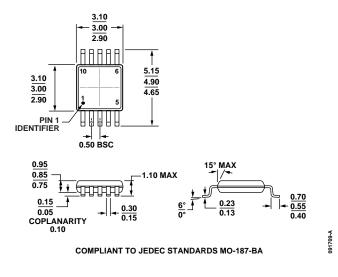

The AD5426/AD5432/AD5443 DACs are available in small, 10-lead MSOP packages.

The EV-AD5443/46/53SDZ evaluation board is available for evaluating DAC performance. For more information, see the UG-327 evaluation board user guide.

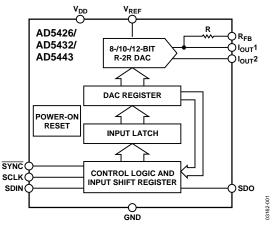

### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

<sup>1</sup> U.S. Patent No. 5,689,257.

Rev. G

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2004–2013 Analog Devices, Inc. All rights reserved. **Technical Support** www.analog.com

# IMPORTANT LINKS for the AD5426 5432 5443\*

Last content update 10/06/2013 09:35 pm

#### **PRODUCT RECOMMENDATIONS & REFERENCE DESIGNS** PARAMETRIC SELECTION TABLES Find Similar Products By Operating Parameters **CN-0151:** Versatile High Precision Programmable Current Sources Using DACs, Op Amps, and MOSFET Transistors Data Converters: Overview of AD54xx Devices **CN-0143:** Single-Ended-to-Differential Converters for Voltage Output and Current Output DACs Using the AD8042 Op Amp CN-0038: Programmable Gain Element Using the AD5426/AD5432/AD5443 Current Output DACs DOCUMENTATION AN-1231: AC Signal Processing Using the AD5426/AD5432/AD5443 **CN-0036:** Precision, Bipolar Configuration for the Current Output DACs AD5426/AD5432/AD5443 8-Bit to12-Bit DACs AN-912: Driving a Center-Tapped Transformer with a Balanced **CN-0034:** Unipolar, Precision DC Digital-to-Analog Conversion Using Current-Output DAC the AD5426/AD5432/AD5443 8-Bit to12-Bit DACs AN-320A: CMOS Multiplying DACs and Op Amps Combine to Build Programmable Gain Amplifier, Part 1 AN-137: A Digitally Programmable Gain and Attenuation Amplifier Design **DESIGN COLLABORATION COMMUNITY CN-0038:** Programmable Gain Element Using the AD5426/AD5432/AD5443 Current Output DACs SUPPORT engineer zone CN-0036: Precision, Bipolar Configuration for the Collaborate Online with the ADI support team and other designers AD5426/AD5432/AD5443 8-Bit to12-Bit DACs about select ADI products. CN-0034: Unipolar, Precision DC Digital-to-Analog Conversion Using Follow us on Twitter: www.twitter.com/ADI News the AD5426/AD5432/AD5443 8-Bit to12-Bit DACs Like us on Facebook: www.facebook.com/AnalogDevicesInc Digital to Analog Converters ICs Solutions Bulletin 4-Quadrant Multiplying D/A Converters FOR THE AD5443 **DESIGN SUPPORT** UG-327: Evaluating the AD5443, AD5446, and AD5453 Current Output/Serial Input DACs Submit your support request here: Linear and Data Converters Embedded Processing and DSP Telephone our Customer Interaction Centers toll free: **DESIGN TOOLS, MODELS, DRIVERS & SOFTWARE** 1-800-262-5643 Americas: BeMicro FPGA Project for AD5443 with Nios driver Europe: 00800-266-822-82 China: 4006-100-006 AD5443 FMC-SDP Interposer & Evaluation Board / Xilinx KC705 India: 1800-419-0108 Reference Design 8-800-555-45-90 Russia: AD5449 IIO DAC Linux Driver **Quality and Reliability** AD5443 - Microcontroller No-OS Driver Lead(Pb)-Free Data AD5443 IBIS Model **SAMPLE & BUY EVALUATION KITS & SYMBOLS & FOOTPRINTS** View the Evaluation Boards and Kits page for documentation and AD5426 purchasing AD5432 Symbols and Footprints for the AD5426 AD5443 Symbols and Footprints for the AD5432 View Price & Packaging Symbols and Footprints for the AD5443 Request Evaluation Board • Request Samples Check Inventory & Purchase **Find Local Distributors** \* This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page (labeled 'Important Links') does not

constitute a change to the revision number of the product data sheet. This content may be frequently modified.

### **TABLE OF CONTENTS**

| Features                                     |

|----------------------------------------------|

| Applications1                                |

| General Description                          |

| Functional Block Diagram1                    |

| Revision History                             |

| Specifications                               |

| Timing Characteristics                       |

| Absolute Maximum Ratings                     |

| ESD Caution                                  |

| Pin Configuration and Function Descriptions7 |

| Typical Performance Characteristics          |

| Terminology14                                |

| Theory of Operation                          |

### **REVISION HISTORY**

| 6/13—Rev. F to Rev. G                 |   |

|---------------------------------------|---|

| Change to General Description Section | l |

| Changes to Ordering Guide 24          | ł |

#### 7/12-Rev. E to Rev. F

| No Change to Content, Changed $V_{DD}$ Values in 7/12 Revision |

|----------------------------------------------------------------|

| History Only                                                   |

#### 7/12-Rev. D to Rev. E

| Changed $V_{DD} = 3 \text{ V}$ to $V_{DD} = 2.5 \text{ V}$ | . Throughout |

|------------------------------------------------------------|--------------|

| Changes to Table 2                                         |              |

| Changes to Table 4                                         |              |

| Change to Daisy-Chain Mode Section                         |              |

| Change to Ordering Guide                                   |              |

### 4/12-Rev. C to Rev. D

| Changed $V_{DD}$ = 2.5 V to $V_{DD}$ = 3 V Throughout                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Changes to General Description Section1                                                                                                                                |

| Deleted Microprocessor Interface Section, ADSP-21xx to                                                                                                                 |

| AD5426/AD5432/AD5443 Interface Section, Figure 51,                                                                                                                     |

| Figure 52, Table 11, ADSP-BF5x to AD5426/AD5432/AD5443                                                                                                                 |

| Interface Section, Figure 53 and Figure 54; Renumbered                                                                                                                 |

|                                                                                                                                                                        |

| Sequentially                                                                                                                                                           |

| Sequentially                                                                                                                                                           |

|                                                                                                                                                                        |

| Deleted 80C51/80L51 to AD5426/AD5432/AD5443 Interface                                                                                                                  |

| Deleted 80C51/80L51 to AD5426/AD5432/AD5443 Interface<br>Section, Figure 55, MC68HC11 Interface to AD5426/AD5432/                                                      |

| Deleted 80C51/80L51 to AD5426/AD5432/AD5443 Interface<br>Section, Figure 55, MC68HC11 Interface to AD5426/AD5432/<br>AD5443 Interface Section, Figure 56, MICROWIRE to |

| Circuit Operation1                                    | 5  |

|-------------------------------------------------------|----|

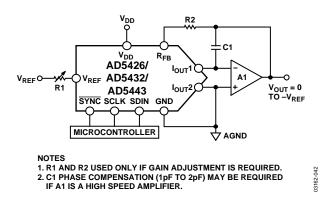

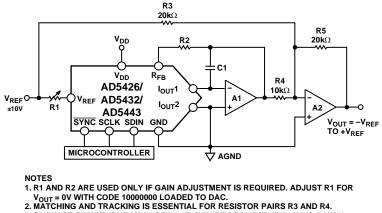

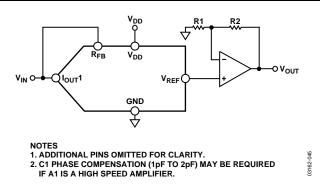

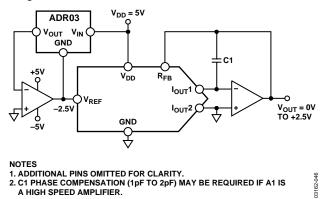

| Single-Supply Applications1                           | 7  |

| Positive Output Voltage1                              | 7  |

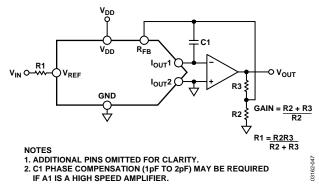

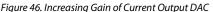

| Adding Gain1                                          | 8  |

| DACs Used as a Divider or Programmable Gain Element 1 | 8  |

| Reference Selection 1                                 | 8  |

| Amplifier Selection1                                  | 8  |

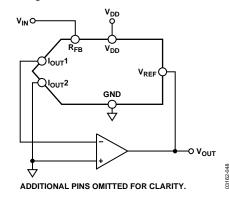

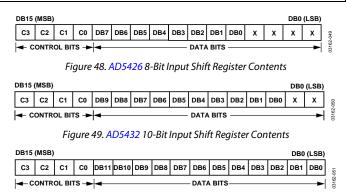

| Serial Interface                                      | 20 |

| PCB Layout and Power Supply Decoupling 2              | 22 |

| Overview of AD54xx and AD55xx Devices 2               | 23 |

| Outline Dimensions                                    | 24 |

| Ordering Guide 2                                      | 24 |

|                                                       |    |

###

#### 2/09—Rev. B to Rev. C

| Changes to Low Power Serial Interface Section and Daisy- |    |

|----------------------------------------------------------|----|

| Chain Mode Section                                       | 20 |

| Updated Outline Dimensions                               | 28 |

#### 11/08—Rev. A to Rev. B

| Changes to | Ordering | Guide | 28 |

|------------|----------|-------|----|

|------------|----------|-------|----|

### 5/05—Rev. 0 to Rev. A

| Updated Format                                | Universal |

|-----------------------------------------------|-----------|

| Changes to Specifications                     | 3         |

| Changes to Figure 42                          |           |

| Change to Figure 45                           |           |

| Change to Figure 46                           |           |

| Changes to Table 7, Table 8, and Table 9      |           |

| Additions to Microprocessor Interface Section |           |

#### 2/04—Revision 0: Initial Version

## **SPECIFICATIONS**

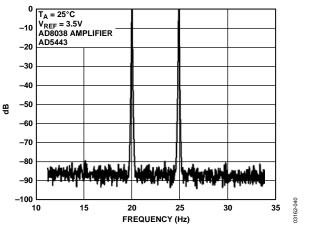

$V_{DD} = 2.5 \text{ V}$  to 5.5 V,  $V_{REF} = 10 \text{ V}$ ,  $I_{OUT}2 = 0 \text{ V}$ ; temperature range for Y version:  $-40^{\circ}$ C to  $+125^{\circ}$ C; all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted; dc performance measured with OP177; ac performance with AD8038, unless otherwise noted.

| Parameter                                       | Min                   | Тур | Max       | Unit       | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------|-----------------------|-----|-----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STATIC PERFORMANCE                              |                       | .76 |           |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| AD5426                                          |                       |     |           |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Resolution                                      |                       |     | 8         | Bits       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Relative Accuracy                               |                       |     | ±0.25     | LSB        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Differential Nonlinearity                       |                       |     | ±0.5      | LSB        | Guaranteed monotonic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AD5432                                          |                       |     | _0.5      | 250        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Resolution                                      |                       |     | 10        | Bits       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Relative Accuracy                               |                       |     | ±0.5      | LSB        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Differential Nonlinearity                       |                       |     | ±1        | LSB        | Guaranteed monotonic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AD5443                                          |                       |     |           |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Resolution                                      |                       |     | 12        | Bits       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Relative Accuracy                               |                       |     | ±1        | LSB        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Differential Nonlinearity                       |                       |     | <br>_1/+2 | LSB        | Guaranteed monotonic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Gain Error                                      |                       |     | ±10       | mV         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Gain Error Temperature Coefficient <sup>1</sup> |                       | ±5  |           | ppm FSR/°C |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Output Leakage Current                          |                       |     | ±10       | nA         | Data = $0x0000$ , $T_A = 25^{\circ}C$ , $I_{OUT}1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                 |                       |     | ±20       | nA         | Data = $0x0000$ , T = $-40^{\circ}$ C to $125^{\circ}$ C, lout 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| REFERENCE INPUT <sup>1</sup>                    |                       |     |           |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Reference Input Range                           |                       | ±10 |           | v          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>REF</sub> Input Resistance               | 8                     | 10  | 12        | kΩ         | Input resistance TC = -50 ppm/°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| R <sub>FB</sub> Resistance                      | 8                     | 10  | 12        | kΩ         | Input resistance TC = $-50 \text{ ppm/}^{\circ}\text{C}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Input Capacitance                               | -                     |     |           |            | The second |

| Code Zero Scale                                 |                       | 3   | 6         | рF         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Code Full Scale                                 |                       | 5   | 8         | pF         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DIGITAL INPUT/OUTPUT <sup>1</sup>               |                       | -   | -         |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Input High Voltage, V⊮                          | 1.7                   |     |           | v          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Input Low Voltage, V <sub>L</sub>               |                       |     | 0.6       | V          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Output High Voltage, Vон                        | V <sub>DD</sub> – 1   |     |           | V          | $V_{DD} = 4.5 \text{ V to } 5 \text{ V}, \text{ I}_{SOURCE} = 200 \ \mu\text{A}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                 | $V_{\text{DD}} - 0.5$ |     |           | V          | $V_{DD} = 2.5 \text{ V to } 3.6 \text{ V}, \text{ I}_{SOURCE} = 200 \mu\text{A}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Output Low Voltage, Vo∟                         |                       |     | 0.4       | V          | $V_{DD} = 4.5 \text{ V to } 5 \text{ V}, \text{ I}_{SINK} = 200 \mu\text{A}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                 |                       |     | 0.4       | V          | $V_{DD} = 2.5 \text{ V to } 3.6 \text{ V}, \text{ I}_{SINK} = 200 \mu\text{A}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Input Leakage Current, I <sub>I</sub>           |                       |     | 1         | μA         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

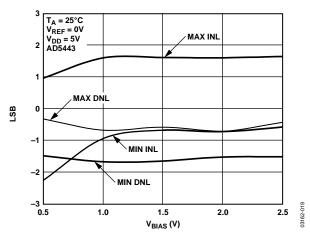

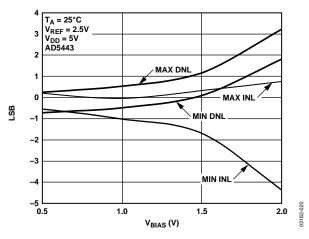

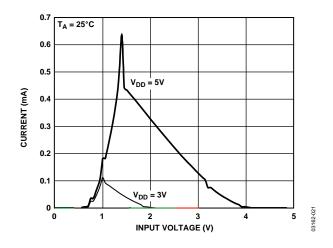

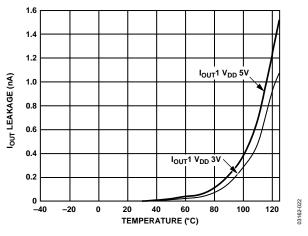

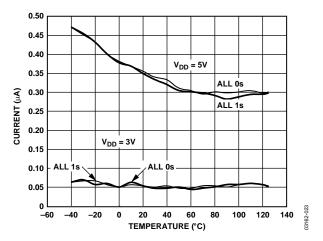

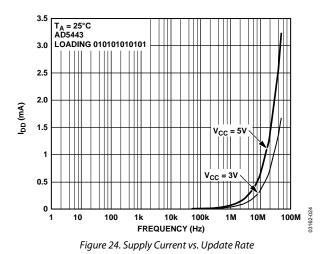

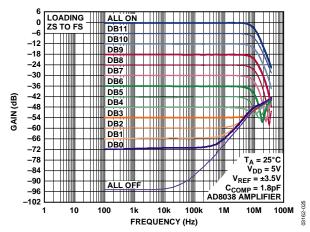

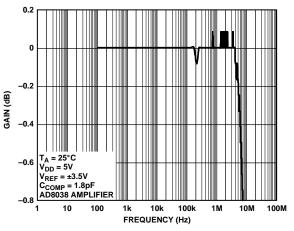

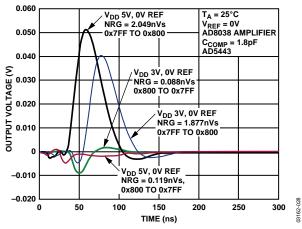

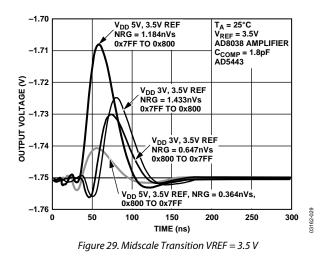

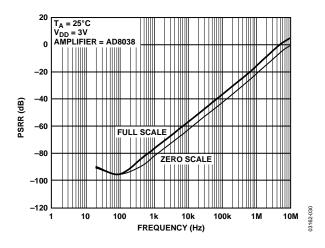

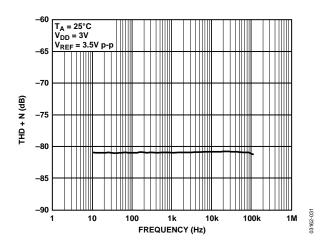

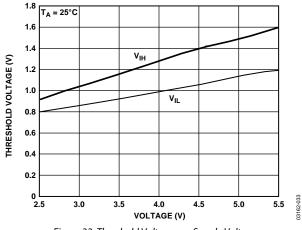

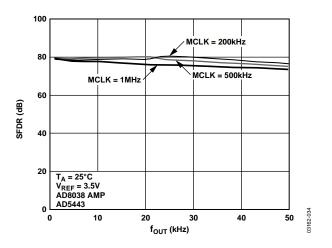

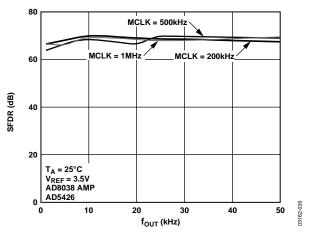

| Input Capacitance                               |                       | 4   | 10        | pF         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |