# 8-BIT LOW COST SIGNAL CONDITIONING ADC

AD670

## 1.0 SCOPE

This specification documents the detail requirements for space qualified product manufactured on Analog Devices, Inc.'s QML certified line per MIL-PRF-38535 Level V except as modified herein. The manufacturing flow described in the STANDARD SPACE LEVEL PRODUCTS PROGRAM brochure is to be considered a part of this specification. <a href="http://www.analog.com/aerospace">http://www.analog.com/aerospace</a>. This data sheet specifically details the space grade version of this product. A more detailed operational description and a complete data sheet for commercial product grades can be found at <a href="https://www.analog.com/AD670">www.analog.com/AD670</a>.

# **2.0 Part Number**. The complete part number(s) of this specification follow:

Part Number Description

AD670-703D 8-Bit low cost signal conditioning ADC

# 2.1 Case Outline.

<u>Letter</u> <u>Descriptive designator</u> <u>Case Outline (Lead Finish per MIL-PRF-38535)</u>

D CDIP2-T20 <u>Case Outline (Lead Finish per MIL-PRF-38535)</u>

20-Lead ceramic, metal sealed, side-brazed leads

# **3.0** Absolute Maximum Ratings. (TA = 25°C, unless otherwise noted)

| V <sub>CC</sub> to ground              | 0V to +7.5V                        |

|----------------------------------------|------------------------------------|

| Digital inputs (Pins 11-15)            | 0.5V to V <sub>CC</sub> +0.5V      |

| Digital outputs (Pins 1-9)             | . Momentary short to VCD or ground |

| Analog inputs (Pins 16-19)             | ±30V                               |

| Power dissipation                      | 450mW                              |

| Storage temperature range              | 65°C to +150°C                     |

| Lead temperature range (soldering)     | +300°C                             |

| Operating temperature range            | 55°C to +125°C                     |

| Junction Temperature (T <sub>J</sub> ) | 150°C                              |

# 3.1 Thermal Characteristics:

Thermal Resistance, Sidebrazed (D) Package Junction-to-Case ( $\Theta$ JC) = 25°C/W Max Junction-to-Ambient ( $\Theta$ JA) = 85°C/W Max

| Terminal | Function          |

|----------|-------------------|

| 1        | DBO LSB           |

| 2        | DB1               |

| 3        | DB2               |

| 4        | DB3               |

| 5        | DB4               |

| 6        | DB5               |

| 7        | DB6               |

| 8        | DB7 MSB           |

| 9        | Status output     |

| 10       | Power ground      |

| 11       | BPO/ UPO          |

| 12       | Format (See note) |

| 13       | R/W               |

| 14       | CS                |

| 15       | CE                |

| 16       | -VIN High         |

| 17       | -VIN Low          |

| 18       | +VIN High         |

| 19       | +VIN Low          |

| 20       | VCC               |

NOTE: Twos complement or straightbinary .

Figure 1 - <u>Terminal connections</u>.

| R/W | <del>C</del> S | <del>CE</del> | Operation                  | Output      |

|-----|----------------|---------------|----------------------------|-------------|

| X   | Χ              | X             | Converting (see note 1)    | Three-state |

| 0   | 0              | 0             | Write/convert (see note 2) | Three-state |

| 1   | 0              | 0             | Read (see note 2)          | Data valid  |

| X   | Χ              | 1             | None (see note 3)          | Three-state |

| X   | 1              | Χ             | None (see note 3)          | Three-state |

- NOTES: 1. Status output high. 2. Status output low 3. Status output don't care

Figure 2. Control signal truth table.

| Mode     | Range | Min   | Max   | Unit |

|----------|-------|-------|-------|------|

| Unipolar | Low   | 0     | 255   | mV   |

| Unipolar | High  | 0     | 2.55  | V    |

| Bipolar  | Low   | -128  | +127  | mV   |

| Bipolar  | High  | -1.28 | +1.27 | V    |

Figure 3. <u>Differential input signal range truth table</u>.

| BPO/ UPO | Format | Input range/output format |

|----------|--------|---------------------------|

| 0        | 0      | Unipolar/straight binary  |

| 1        | 0      | Bipolar/offset binary     |

| 0        | 1      | Unipolar/2's complement   |

| 1        | 1      | Bipolar/2's complement    |

Figure 4. <u>Input selection/output format truth table</u>.

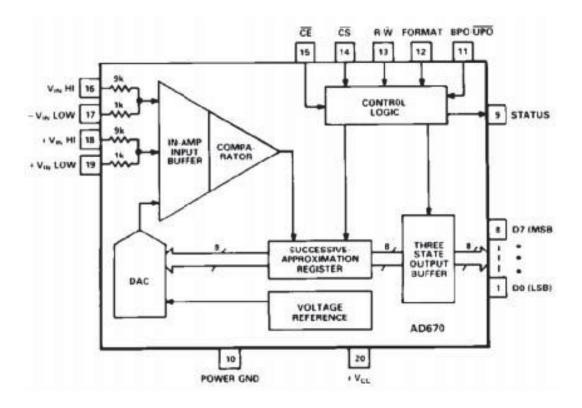

Figure 5. Block diagram.

# **AD670**

# 4.0 Electrical Table:

|                                                    |                        | Table I                                                                                      |               |              |                        |                                       |

|----------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------|---------------|--------------|------------------------|---------------------------------------|

| Parameter<br>See notes at end of table             | Symbol                 | Conditions<br>V <sub>CC</sub> = +5V                                                          | Sub-<br>group | Limit<br>Min | Limit<br>Max           | Units                                 |

| Relative accuracy 1/                               | RA                     |                                                                                              | 1             |              | ±½                     | LSB                                   |

|                                                    |                        |                                                                                              | 2, 3          |              | ±1                     |                                       |

| Differential nonlinearity 2/ 3/                    | DNL                    |                                                                                              | 1, 2, 3       | 8            |                        | Bits                                  |

| Gain Error 1/                                      | AE                     |                                                                                              | 1             |              | ±1.5                   | LSB                                   |

|                                                    |                        |                                                                                              | 2, 3          |              | ±2.5                   |                                       |

| Unipolar offset error                              | OE                     | 0V to +2.55V input range FS                                                                  | 1             |              | ±1                     |                                       |

|                                                    |                        |                                                                                              | 2,3           |              | ±2                     |                                       |

| Bipolar Zero Error                                 | BPZE                   | -1.28V to +1.27V FS                                                                          | 1             |              | ±1                     |                                       |

|                                                    |                        |                                                                                              | 2, 3          |              | ±2                     |                                       |

| Input resistance 3/                                | R <sub>IN</sub>        | 2.55V input range                                                                            | 1             | 8            | 12                     | KΩ                                    |

| Input bias current 3/                              | IB                     | 255 mV input range                                                                           | 1, 2, 3       |              | ±750                   | nA                                    |

| Input offset current 3/                            | los                    | 255 mV input range                                                                           | 1, 2, 3       |              | ±200                   |                                       |

| Absolute input signal range                        | Vabs                   | Low range                                                                                    | 1             | -0.34        | Vcc-3.3V               | V                                     |

| 3/ 4/ 5/                                           |                        |                                                                                              | 2, 3          | 15           | V <sub>CC</sub> ~ 3.5V |                                       |

|                                                    |                        | High range                                                                                   | 1             | -3.4         | Vcc                    |                                       |

|                                                    |                        |                                                                                              | 2, 3          | -1.5         | Vcc                    |                                       |

| Power supply rejection ratio                       | PSRR                   | 2.55V FS, V <sub>CC</sub> ≈ +4.75V to +5.5V                                                  | 1, 2, 3       |              | ±0.015                 | %FS/%                                 |

| Power supply current                               | lcc                    | V <sub>CC</sub> = 5.5V (DBO-DB7, R/W - high);<br>(STATUS, CE, CS, FORMAT, BPO,<br>UPO - LOW) | 1, 2, 3       |              | 45                     | mA                                    |

| Digital input high voltage 3/                      | V <sub>IH</sub>        |                                                                                              | 1, 2, 3       | 2.0          |                        | V                                     |

| Digital input low voltage 3/                       | VIL                    |                                                                                              | 1             |              | 0.8                    |                                       |

|                                                    |                        |                                                                                              | 2, 3          |              | 0.7                    |                                       |

| Digital input high current 3/                      | Iн                     | V <sub>IH</sub> = 5V                                                                         | 1, 2, 3       |              | 100                    | μA                                    |

| Digital input low current 3/                       | IIL                    | $V_{IL} = 0V$                                                                                | 1, 2, 3       |              | -100                   |                                       |

| Digital output low voltage                         | Vol                    | $I_{OL} = 1.6 \text{mA}, V_{CC} = 5.5 \text{V}$                                              | 1, 2, 3       |              | 0.4                    | V                                     |

| Digital output high voltage                        | Vон                    | $I_{OH} \approx 0.5 \text{mA}, V_{CC} \approx 4.5 \text{V}$                                  | 1, 2, 3       | 2.4          |                        |                                       |

| Digital output low current                         | I <sub>OL</sub>        | $V_{OL} = 0.4V, V_{CC} = 5.5V$                                                               | 1, 2, 3       | -1.6         |                        | mA                                    |

| Digital output high current                        | Іон                    | $V_{OH} = 2.4V, V_{CC} = 4.5V$                                                               | 1, 2, 3       | 0.5          |                        |                                       |

| Common mode rejection ratio                        | CMRR                   | $V_{CM} = -0.34V$ to $(V_{CC} - 3.6V)$                                                       | 1             |              | ±1                     | LSB                                   |

| <u>3/</u> <u>7/</u>                                |                        | $V_{CM} \approx -0.15V \text{ to } (V_{CC} - 3.8V)$                                          | 2, 3          |              | ±2                     |                                       |

| Three-state leakage current 3/                     | loz                    | V <sub>applied</sub> = 0V & 5V                                                               | 1, 2, 3       |              | ±40                    | μ <b>A</b>                            |

| Functional tests 8/                                |                        |                                                                                              | 7, 8          |              |                        | · · · · · · · · · · · · · · · · · · · |

| Bus access time 3/                                 | <b>t</b> TD            | See fig. 5, $R_L = 3K\Omega$ , $C_L = 90pF$                                                  | 9             | 250          | nS                     |                                       |

| Output float delay 3/                              | <b>t</b> <sub>DT</sub> | See fig. 5, $R_L = 3K\Omega$                                                                 | 1             |              | 150                    |                                       |

| Write/start pulse width 3/                         | tw                     | See fig. 6, $R_L = 3K\Omega$ , $C_L = 90pF$                                                  |               | 300          |                        |                                       |

| Input data setup time                              | t <sub>DS</sub>        | 6/                                                                                           |               |              | 200                    |                                       |

| Input data hold time                               | t <sub>DH</sub>        |                                                                                              | †             |              | 10                     |                                       |

| R/W setup before control                           | t <sub>RWC</sub>       |                                                                                              |               |              | 0                      |                                       |

| Delay to convert start                             | toc                    |                                                                                              | †             |              | ,                      | 700                                   |

| Delay from STATUS OUTPUT to data read              | t <sub>SD</sub>        |                                                                                              |               |              |                        | 250                                   |

| Data hold time                                     | <b>t</b> <sub>DH</sub> |                                                                                              | 1             |              | 25                     |                                       |

| Conversion time 3/                                 | Tc                     | $V_{cc} = +5V$                                                                               | 9             |              | 10                     | μS                                    |

| A Lineary Lakes 2000 (2004) (Chicky of Modelli C.) |                        | 6/                                                                                           | 10,11         |              | 13                     | F-0                                   |

### TABLE I NOTES:

- Tested on both 2.55V full scale and -1.28V to 1.27V full scale.

- Minimum resolution for which there are no missing codes.

- Parameter is tested at  $V_{CC} = +5V$ , but is guaranteed from  $V_{CC} = 4.5V$  to  $V_{CC} = 5.5V$

- 3/ 4/ The absolute input signal range defines the limits of input signal value from either the (+) or (-) input to ground (as a function of V<sub>CC</sub>) over which the device will produce distinct output codes.

- 5/ The differential input signal range defines the input signal span over which distinct output codes are produced. As this range is exceeded, the device ceases to change output state (see fig. 4).

- Guaranteed, if not tested, to the specified limits.

- 7/ 255 mV range. CMRR tested with 0V and full scale applied to analog inputs output change measured from 0 to VCM maximum and 0 to VCM minimum and will not exceed specified limits.

- Subgroups 7 and 8 shall include verification of the truth table. (Fig. 3 and Fig. 4)

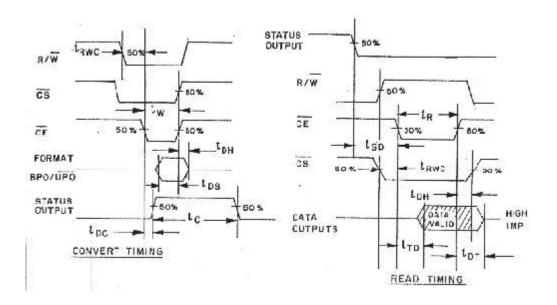

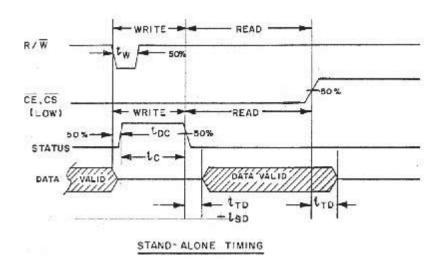

Figure 6. Timing diagram.

### **Electrical Test Requirements:** 4.1

| Table II                                |                                                         |  |  |

|-----------------------------------------|---------------------------------------------------------|--|--|

| Test Requirements                       | Subgroups (in accordance with MIL-PRF-38535, Table III) |  |  |

| Interim Electrical Parameters           | 1                                                       |  |  |

| Final Electrical Parameters             | 1, 2, 3, 7, 8, 9 <u>1/</u> <u>2/</u>                    |  |  |

| Group A Test Requirements               | 1, 2, 3, 7, 8, 9                                        |  |  |

| Group C end-point electrical parameters | 1 <u>2/</u>                                             |  |  |

| Group D end-point electrical parameters | 1                                                       |  |  |

| Group E end-point electrical parameters | 1                                                       |  |  |

### 4.2 Table III. Lifetest / Burn-in delta limits.

|                  |                     | Table III            |                |       |

|------------------|---------------------|----------------------|----------------|-------|

| TEST<br>TITLE    | BURN-IN<br>ENDPOINT | LIFETEST<br>ENDPOINT | DELTA<br>LIMIT | UNITS |

| AE               | ±1.5                | ±1.5                 | ±1.5           | LSB   |

| Vos              | ±1                  | ±1                   | ±1             | LSB   |

| B <sub>PZE</sub> | ±1                  | ±1                   | ±1             | LSB   |

### 5.0 Life Test/Burn-In Circuit:

- HTRB is not applicable for this drawing.

- 5.2 Burn-in is per MIL-STD-883 Method 1015 test condition D.

- 5.3 Steady state life test is per MIL-STD-883 Method 1005.

PDA applies to Subgroup 1. Delta's excluded from PDA. See Table III for delta parameters. See table I for conditions.

| Rev | Description of Change                                                                                                     | Date       |

|-----|---------------------------------------------------------------------------------------------------------------------------|------------|

| Α   | Initiate                                                                                                                  | 8/9/2000   |

| В   | Various corrections made to Table I to make compatible with 883. SMD has errors. Correct BI to dynamic. Update Table III. | 9/18/2001  |

| C   | Update web address, BI condition is D                                                                                     | 1/25/2002  |

| D   | Change BP2E to BPZE on table III (typo) Change Table I BOE to BPZE                                                        | 11/27/2002 |

| E   | Update web address. Delete burn-in circuit                                                                                | 6/20/2003  |

| F   | Update header/footer & add to 1.0 Scope description.                                                                      | 2/25/2008  |

| G   | Add Junction Temperature (TJ)150°C to 3.0 Absolute Max. Ratings                                                           | 3/28/2008  |

| Н   | Remove obsolete part numbers and update ASD to ADI standard                                                               | 11/21/2011 |

|     |                                                                                                                           |            |

|     |                                                                                                                           |            |

|     |                                                                                                                           |            |